# M95128-A125 M95128-A145

Datasheet - production data

# Automotive 128-Kbit serial SPI bus EEPROMs with high-speed clock

# Features

- Compatible with the Serial Peripheral Interface (SPI) bus

- Memory array

- 128 Kbit (16 Kbyte) of EEPROM

- Page size: 64 byte

- Write protection by block: 1/4, 1/2 or whole memory

- Additional Write lockable Page (Identification page)

- Extended temperature and voltage ranges

- Up to 125  $^{\circ}$ C (V<sub>CC</sub> from 1.7 V to 5.5 V)

- Up to 145 °C (V\_{CC} from 2.5 V to 5.5 V)

- High speed clock frequency

- 20 MHz for V<sub>CC</sub>  $\ge$  4.5 V

- 10 MHz for  $V_{CC} \geq 2.5 \mbox{ V}$

- 5 MHz for  $V_{CC} \ge 1.7 \text{ V}$

- Schmitt trigger inputs for noise filtering

- Short Write cycle time

- Byte Write within 4 ms

- Page Write within 4 ms

- Write cycle endurance

- 4 million Write cycles at 25 °C

- 1.2 million Write cycles at 85 °C

- 600 k Write cycles at 125 °C

- 400 k Write cycles at 145 °C

- Data retention

- 50 years at 125 °C

- 100 years at 25 °C

- ESD Protection (Human Body Model)

4000 V

- Packages

- RoHS-compliant and halogen-free (ECOPACK2<sup>®</sup>)

January 2016

DocID023103 Rev 8

This is information on a product in full production.

# Contents

| 1 | Desci  | ription                                   | 6  |

|---|--------|-------------------------------------------|----|

| 2 | Signa  | Il description                            | 8  |

|   | 2.1    | Serial Data output (Q)                    | 8  |

|   | 2.2    | Serial Data input (D)                     | 8  |

|   | 2.3    | Serial Clock (C)                          | 8  |

|   | 2.4    | Chip Select (S)                           | 8  |

|   | 2.5    | Hold (HOLD)                               | 8  |

|   | 2.6    | Write Protect (W)                         | 8  |

|   | 2.7    | V <sub>SS</sub> ground                    | 8  |

|   | 2.8    | V <sub>CC</sub> supply voltage            | 9  |

| 3 | Opera  | ating features                            | 10 |

|   | 3.1    | Active power and Standby power modes      | 10 |

|   | 3.2    | SPI modes                                 | 10 |

|   | 3.3    | Hold mode                                 | 11 |

|   | 3.4    | Protocol control and data protection      | 11 |

|   |        | 3.4.1 Protocol control                    | 11 |

|   |        | 3.4.2 Status Register and data protection |    |

|   | 3.5    | Identification page                       | 13 |

| 4 | Instru | ictions                                   | 15 |

|   | 4.1    | Write Enable (WREN)                       | 16 |

|   | 4.2    | Write Disable (WRDI)                      | 16 |

|   | 4.3    | Read Status Register (RDSR)               | 17 |

|   | 4.4    | Write Status Register (WRSR)              | 18 |

|   | 4.5    | Read from Memory Array (READ)             | 19 |

|   | 4.6    | Write to Memory Array (WRITE)             | 20 |

|   | 4.7    | Read Identification Page (RDID)           | 22 |

|   | 4.8    | Write Identification Page (WRID)          | 23 |

|   | 4.9    | Read Lock Status (RDLS)                   | 23 |

|   | 4.10   | Lock Identification Page (LID)            | 24 |

DocID023103 Rev 8

2/43

| 5  | Application design recommendations |           |                                             |  |  |

|----|------------------------------------|-----------|---------------------------------------------|--|--|

|    | 5.1                                | Supply vo | oltage (V <sub>CC</sub> )                   |  |  |

|    |                                    | 5.1.1 (   | Dperating supply voltage (V <sub>CC</sub> ) |  |  |

|    |                                    | 5.1.2 F   | Power-up conditions                         |  |  |

|    |                                    | 5.1.3 F   | Power-down                                  |  |  |

|    | 5.2                                | Implemer  | nting devices on SPI bus 27                 |  |  |

|    | 5.3                                | Cycling w | ith Error Correction Code (ECC) 28          |  |  |

| 6  | Delive                             | ery state |                                             |  |  |

| 7  | Absol                              | lute maxi | mum ratings 29                              |  |  |

| 8  | DC ar                              | nd AC pa  | rameters                                    |  |  |

| 9  | Packa                              | age mech  | anical data                                 |  |  |

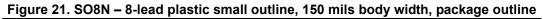

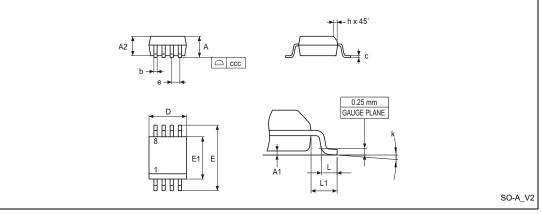

|    | 9.1                                | SO8N pa   | ckage information                           |  |  |

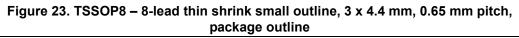

|    | 9.2                                | TSSOP8    | package information                         |  |  |

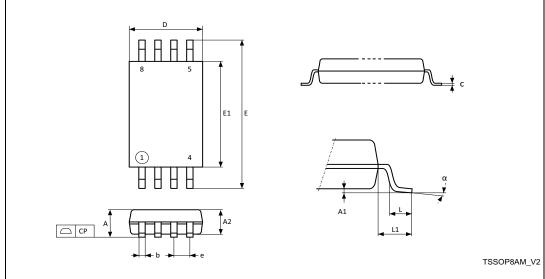

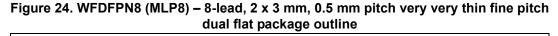

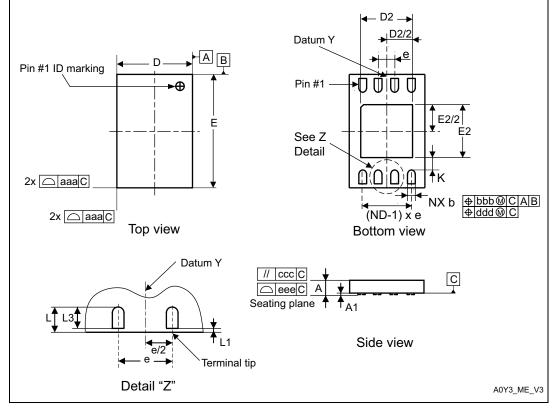

|    | 9.3                                | WFDFPN    | 8 package information                       |  |  |

| 10 | Part n                             | umberin   | g 41                                        |  |  |

| 11 | Revis                              | ion histo | ry                                          |  |  |

# List of tables

| Table 2.Status Register format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Table 1.  | Signal names                                                            | 7  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-------------------------------------------------------------------------|----|

| Table 4.Protection modes13Table 5.Device identification bytes14Table 6.Instruction set14Table 7.Significant bits within the two address bytes14Table 8.Absolute maximum ratings29Table 9.Cycling performance by groups of 4 byte30Table 10.Operating conditions (voltage range W, temperature range 4)30Table 12.Operating conditions (voltage range R, temperature range 3)30Table 13.DC characteristics (voltage range W, temperature range 4)30Table 14.DC characteristics (voltage range R, temperature range 4)30Table 13.DC characteristics (voltage range R, temperature range 4)31Table 14.DC characteristics (voltage range R, temperature range 3)32Table 15.AC characteristics33Table 16.SO8N – 8-lead plastic small outline, 150 mils body width,<br>package mechanical data36Table 17.TSSOP8 – 8-lead thin shrink small outline, 3 x 4.4 mm, 0.65 mm pitch,<br>package mechanical data36Table 18.WFPN8 (MLP8) – 8-lead, 2 x 3 mm, 0.5 mm pitch very very thin fine pitch<br>dual flat package mechanical data40                                                                                                                                 | Table 2.  | -                                                                       |    |

| Table 5.Device identification bytes14Table 6.Instruction set14Table 7.Significant bits within the two address bytes14Table 8.Absolute maximum ratings29Table 9.Cycling performance by groups of 4 byte30Table 10.Operating conditions (voltage range W, temperature range 4)30Table 11.Operating conditions (voltage range R, temperature range 3)30Table 12.Operating conditions (voltage range R, temperature range 3)30Table 13.DC characteristics (voltage range W, temperature range 4)31Table 14.DC characteristics (voltage range R, temperature range 3)32Table 15.AC characteristics (voltage range R, temperature range 3)33Table 16.SO8N – 8-lead plastic small outline, 150 mils body width,<br>package mechanical data36Table 17.TSSOP8 – 8-lead thin shrink small outline, 3 x 4.4 mm, 0.65 mm pitch,<br>package mechanical data36Table 18.WFPN8 (MLP8) – 8-lead, 2 x 3 mm, 0.5 mm pitch very very thin fine pitch<br>dual flat package mechanical data40                                                                                                                                                                                      | Table 3.  | Write-protected block size                                              | 13 |

| Table 6.Instruction set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Table 4.  | Protection modes                                                        | 13 |

| Table 7.Significant bits within the two address bytes14Table 8.Absolute maximum ratings29Table 9.Cycling performance by groups of 4 byte30Table 10.Operating conditions (voltage range W, temperature range 4).30Table 11.Operating conditions (voltage range R, temperature range 3)30Table 12.Operating conditions (voltage range R, temperature range 3)30Table 13.DC characteristics (voltage range W, temperature range 4).31Table 14.DC characteristics (voltage range R, temperature range 4).32Table 15.AC characteristics (voltage range R, temperature range 3)32Table 15.AC characteristics (voltage range R, temperature range 3)32Table 16.SO8N – 8-lead plastic small outline, 150 mils body width,<br>package mechanical data36Table 17.TSSOP8 – 8-lead thin shrink small outline, 3 x 4.4 mm, 0.65 mm pitch,<br>package mechanical data36Table 18.WFPN8 (MLP8) – 8-lead, 2 x 3 mm, 0.5 mm pitch very very thin fine pitch<br>dual flat package mechanical data40                                                                                                                                                                             | Table 5.  | Device identification bytes                                             | 14 |

| Table 8.Absolute maximum ratings29Table 9.Cycling performance by groups of 4 byte30Table 10.Operating conditions (voltage range W, temperature range 4)30Table 11.Operating conditions (voltage range R, temperature range 3)30Table 12.Operating conditions (voltage range R, temperature range 3)30Table 13.DC characteristics (voltage range W, temperature range 4)30Table 14.DC characteristics (voltage range R, temperature range 4)31Table 15.AC characteristics (voltage range R, temperature range 3)32Table 16.SO8N – 8-lead plastic small outline, 150 mils body width,<br>package mechanical data36Table 17.TSSOP8 – 8-lead thin shrink small outline, 3 x 4.4 mm, 0.65 mm pitch,<br>package mechanical data36Table 18.WFPN8 (MLP8) – 8-lead, 2 x 3 mm, 0.5 mm pitch very very thin fine pitch<br>dual flat package mechanical data40                                                                                                                                                                                                                                                                                                           | Table 6.  | Instruction set                                                         | 15 |

| Table 9.       Cycling performance by groups of 4 byte       30         Table 10.       Operating conditions (voltage range W, temperature range 4).       30         Table 11.       Operating conditions (voltage range R, temperature range 3)       30         Table 12.       Operating conditions (voltage range R, temperature range 3)       30         Table 13.       DC characteristics (voltage range R, temperature range 4)       31         Table 13.       DC characteristics (voltage range W, temperature range 4)       31         Table 14.       DC characteristics (voltage range R, temperature range 3)       32         Table 15.       AC characteristics (voltage range R, temperature range 3)       32         Table 16.       SO8N – 8-lead plastic small outline, 150 mils body width, package mechanical data       36         Table 17.       TSSOP8 – 8-lead thin shrink small outline, 3 x 4.4 mm, 0.65 mm pitch, package mechanical data       36         Table 18.       WFPN8 (MLP8) – 8-lead, 2 x 3 mm, 0.5 mm pitch very very thin fine pitch dual flat package mechanical data       40                             | Table 7.  | Significant bits within the two address bytes                           | 15 |

| Table 10.       Operating conditions (voltage range W, temperature range 4).       30         Table 11.       Operating conditions (voltage range R, temperature range 3)       30         Table 12.       Operating conditions (voltage range R, temperature range 3)       30         Table 12.       Operating conditions (voltage range R, temperature range 3)       30         Table 13.       DC characteristics (voltage range W, temperature range 4).       31         Table 13.       DC characteristics (voltage range W, temperature range 4).       31         Table 14.       DC characteristics (voltage range R, temperature range 3).       32         Table 15.       AC characteristics (voltage range R, temperature range 3).       32         Table 16.       SO8N – 8-lead plastic small outline, 150 mils body width, package mechanical data.       36         Table 17.       TSSOP8 – 8-lead thin shrink small outline, 3 x 4.4 mm, 0.65 mm pitch, package mechanical data.       36         Table 18.       WFPN8 (MLP8) – 8-lead, 2 x 3 mm, 0.5 mm pitch very very thin fine pitch dual flat package mechanical data.       40 | Table 8.  | Absolute maximum ratings                                                |    |

| Table 11.       Operating conditions (voltage range R, temperature range 3)       30         Table 12.       Operating conditions (voltage range R, temperature range 3)       30         Table 12.       Operating conditions (voltage range R, temperature range 3)       30         Table 13.       DC characteristics (voltage range W, temperature range 4)       31         Table 14.       DC characteristics (voltage range R, temperature range 3)       32         Table 15.       AC characteristics.       33         Table 15.       AC characteristics.       33         Table 16.       SO8N – 8-lead plastic small outline, 150 mils body width, package mechanical data       36         Table 17.       TSSOP8 – 8-lead thin shrink small outline, 3 x 4.4 mm, 0.65 mm pitch, package mechanical data       36         Table 18.       WFPN8 (MLP8) – 8-lead, 2 x 3 mm, 0.5 mm pitch very very thin fine pitch dual flat package mechanical data       40                                                                                                                                                                                  | Table 9.  | Cycling performance by groups of 4 byte                                 | 30 |

| Table 12.       Operating conditions (voltage range R, temperature range 3)         for high-speed communications       30         Table 13.       DC characteristics (voltage range W, temperature range 4).       31         Table 14.       DC characteristics (voltage range R, temperature range 3)       32         Table 14.       DC characteristics (voltage range R, temperature range 3)       32         Table 15.       AC characteristics.       33         Table 15.       AC characteristics.       33         Table 16.       SO8N – 8-lead plastic small outline, 150 mils body width, package mechanical data       36         Table 17.       TSSOP8 – 8-lead thin shrink small outline, 3 x 4.4 mm, 0.65 mm pitch, package mechanical data       36         Table 18.       WFPN8 (MLP8) – 8-lead, 2 x 3 mm, 0.5 mm pitch very very thin fine pitch dual flat package mechanical data       40                                                                                                                                                                                                                                          | Table 10. | Operating conditions (voltage range W, temperature range 4)             | 30 |

| for high-speed communications       30         Table 13.       DC characteristics (voltage range W, temperature range 4).       31         Table 14.       DC characteristics (voltage range R, temperature range 3).       32         Table 15.       AC characteristics.       33         Table 16.       SO8N – 8-lead plastic small outline, 150 mils body width, package mechanical data       36         Table 17.       TSSOP8 – 8-lead thin shrink small outline, 3 x 4.4 mm, 0.65 mm pitch, package mechanical data       36         Table 18.       WFPN8 (MLP8) – 8-lead, 2 x 3 mm, 0.5 mm pitch very very thin fine pitch dual flat package mechanical data       40                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Table 11. |                                                                         | 30 |

| Table 13.       DC characteristics (voltage range W, temperature range 4).       37         Table 14.       DC characteristics (voltage range R, temperature range 3).       32         Table 15.       AC characteristics.       33         Table 16.       SO8N – 8-lead plastic small outline, 150 mils body width, package mechanical data.       36         Table 17.       TSSOP8 – 8-lead thin shrink small outline, 3 x 4.4 mm, 0.65 mm pitch, package mechanical data.       36         Table 18.       WFPN8 (MLP8) – 8-lead, 2 x 3 mm, 0.5 mm pitch very very thin fine pitch dual flat package mechanical data.       40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Table 12. |                                                                         |    |

| Table 14.       DC characteristics (voltage range R, temperature range 3)       32         Table 15.       AC characteristics       33         Table 15.       SO8N – 8-lead plastic small outline, 150 mils body width, package mechanical data       36         Table 17.       TSSOP8 – 8-lead thin shrink small outline, 3 x 4.4 mm, 0.65 mm pitch, package mechanical data       36         Table 18.       WFPN8 (MLP8) – 8-lead, 2 x 3 mm, 0.5 mm pitch very very thin fine pitch dual flat package mechanical data       40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |           |                                                                         |    |

| Table 15.       AC characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Table 13. | DC characteristics (voltage range W, temperature range 4)               | 31 |

| Table 16.       SO8N – 8-lead plastic small outline, 150 mils body width, package mechanical data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Table 14. |                                                                         |    |

| package mechanical data       36         Table 17.       TSSOP8 – 8-lead thin shrink small outline, 3 x 4.4 mm, 0.65 mm pitch, package mechanical data       38         Table 18.       WFPN8 (MLP8) – 8-lead, 2 x 3 mm, 0.5 mm pitch very very thin fine pitch dual flat package mechanical data       40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Table 15. | AC characteristics                                                      | 33 |

| Table 17.TSSOP8 – 8-lead thin shrink small outline, 3 x 4.4 mm, 0.65 mm pitch,<br>package mechanical data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Table 16. |                                                                         |    |

| package mechanical data       38         Table 18.       WFPN8 (MLP8) – 8-lead, 2 x 3 mm, 0.5 mm pitch very very thin fine pitch dual flat package mechanical data       40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |           |                                                                         | 36 |

| Table 18.       WFPN8 (MLP8) – 8-lead, 2 x 3 mm, 0.5 mm pitch very very thin fine pitch dual flat package mechanical data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Table 17. |                                                                         |    |

| dual flat package mechanical data 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |           |                                                                         | 38 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Table 18. | WFPN8 (MLP8) – 8-lead, 2 x 3 mm, 0.5 mm pitch very very thin fine pitch |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |           | dual flat package mechanical data                                       | 40 |

| Table 19. Ordering information scheme                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Table 19. | Ordering information scheme                                             | 41 |

| Table 20.    Document revision history    42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Table 20. | Document revision history                                               | 42 |

# List of figures

| Figure 1.  | Logic diagram                                                             | 6    |

|------------|---------------------------------------------------------------------------|------|

| Figure 2.  | 8-pin package connections                                                 | 7    |

| Figure 3.  | SPI modes supported                                                       | . 10 |

| Figure 4.  | Hold mode activation                                                      | . 11 |

| Figure 5.  | Write Enable (WREN) sequence                                              | . 16 |

| Figure 6.  | Write Disable (WRDI) sequence                                             | . 16 |

| Figure 7.  | Read Status Register (RDSR) sequence                                      |      |

| Figure 8.  | Write Status Register (WRSR) sequence                                     |      |

| Figure 9.  | Read from Memory Array (READ) sequence                                    |      |

| Figure 10. | Byte Write (WRITE) sequence                                               |      |

| Figure 11. | Page Write (WRITE) sequence                                               |      |

| Figure 12. | Read Identification Page sequence                                         |      |

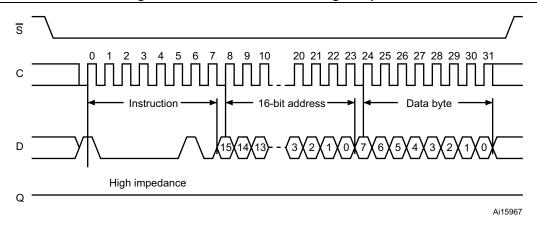

| Figure 13. | Write Identification Page sequence                                        |      |

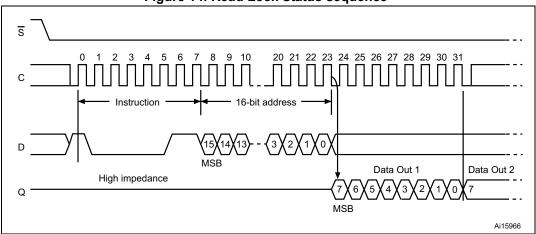

| Figure 14. | Read Lock Status sequence                                                 |      |

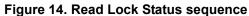

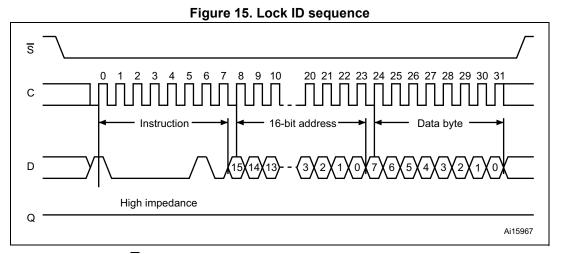

| Figure 15. | Lock ID sequence                                                          |      |

| Figure 16. | Bus master and memory devices on the SPI bus                              |      |

| Figure 17. | AC measurement I/O waveform                                               |      |

| Figure 18. | Serial input timing                                                       |      |

| Figure 19. | Hold timing                                                               |      |

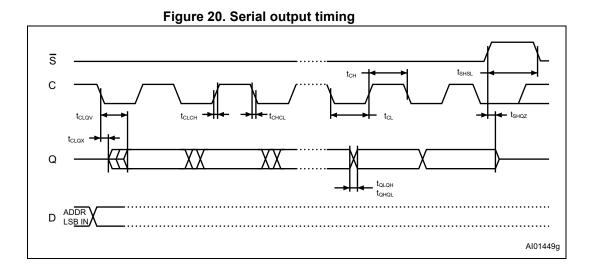

| Figure 20. | Serial output timing                                                      |      |

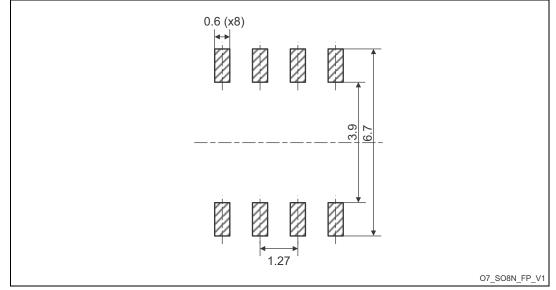

| Figure 21. | SO8N – 8-lead plastic small outline, 150 mils body width, package outline | . 36 |

| Figure 22. | SO8N – 8-lead plastic small outline, 150 mils body width,                 |      |

|            | package recommended footprint                                             | . 37 |

| Figure 23. | TSSOP8 – 8-lead thin shrink small outline, 3 x 4.4 mm, 0.65 mm pitch,     |      |

|            | package outline                                                           | . 38 |

| Figure 24. | WFDFPN8 (MLP8) – 8-lead, 2 x 3 mm, 0.5 mm pitch very very thin fine pitch |      |

|            | dual flat package outline                                                 | . 39 |

|            |                                                                           |      |

### 1 Description

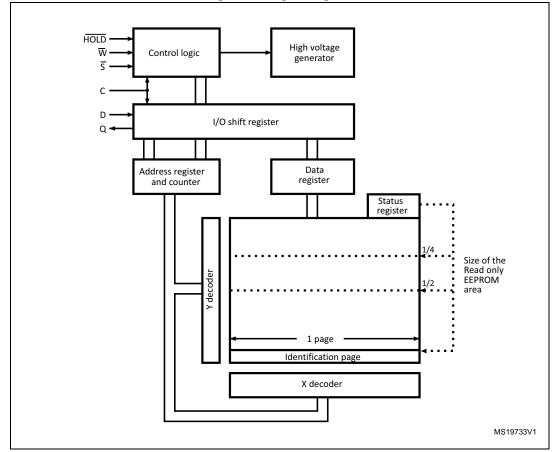

The M95128-A125 and M95128-A145 are 128-Kbit serial EEPROM Automotive grade devices operating up to 145°C. They are compliant with the very high level of reliability defined by the Automotive standard AEC-Q100 grade 0.

The devices are accessed by a simple serial SPI compatible interface running up to 20 MHz.

The memory array is based on advanced true EEPROM technology (Electrically Erasable PROgrammable Memory). The M95128-A125 and M95128-A145 are byte-alterable memories (16384 × 8 bits) organized as 256 pages of 64 byte in which the data integrity is significantly improved with an embedded Error Correction Code logic.

The M95128-A125 and M95128-A145 offer an additional Identification Page (64 byte) in which the ST device identification can be read. This page can also be used to store sensitive application parameters which can be later permanently locked in read-only mode.

Figure 1. Logic diagram

| M95xxx |                                         |                                               |          |  |

|--------|-----------------------------------------|-----------------------------------------------|----------|--|

|        | S[1<br>Q[2<br>W[3<br>V <sub>SS</sub> [4 | 8] V <sub>CC</sub><br>7] HOLD<br>6] C<br>5] D |          |  |

|        |                                         |                                               | AI01790D |  |

| Figure 2 | 8-pin | package | connections |

|----------|-------|---------|-------------|

|----------|-------|---------|-------------|

1. See Package mechanical data section for package dimensions and how to identify pin-1.

| Signal name     | Description        |

|-----------------|--------------------|

| С               | Serial Clock       |

| D               | Serial data input  |

| Q               | Serial data output |

| S               | Chip Select        |

| W               | Write Protect      |

| HOLD            | Hold               |

| V <sub>CC</sub> | Supply voltage     |

| V <sub>SS</sub> | Ground             |

#### Table 1. Signal names

### 2 Signal description

All input signals must be held high or low (according to voltages of  $V_{IH}$  or  $V_{IL}$ , as specified in *Table 13* and *Table 14*). These signals are described below.

### 2.1 Serial Data output (Q)

This output signal is used to transfer data serially out of the device during a Read operation. Data is shifted out on the falling edge of Serial Clock (C), most significant bit (MSB) first. In all other cases, the Serial Data output is in high impedance.

### 2.2 Serial Data input (D)

This input signal is used to transfer data serially into the device. D input receives instructions, addresses, and the data to be written. Values are latched on the rising edge of Serial Clock (C), most significant bit (MSB) first.

### 2.3 Serial Clock (C)

This input signal allows to synchronize the timing of the serial interface. Instructions, addresses, or data present at Serial Data Input (D) are latched on the rising edge of Serial Clock (C). Data on Serial Data Output (Q) changes after the falling edge of Serial Clock (C).

### 2.4 Chip Select (S)

Driving Chip Select  $(\overline{S})$  low selects the device in order to start communication. Driving Chip Select  $(\overline{S})$  high deselects the device and Serial Data output (Q) enters the high impedance state.

### 2.5 Hold (HOLD)

The Hold ( $\overline{\text{HOLD}}$ ) signal is used to pause any serial communications with the device without deselecting the device.

### 2.6 Write Protect (W)

This pin is used to write-protect the Status Register.

### 2.7 V<sub>SS</sub> ground

$\mathsf{V}_{SS}$  is the reference for all signals, including the  $\mathsf{V}_{CC}$  supply voltage.

### 2.8 V<sub>CC</sub> supply voltage

V<sub>CC</sub> is the supply voltage pin. Refer to *Section 3.1: Active power and Standby power modes* and to *Section 5.1: Supply voltage (VCC)*.

### **3 Operating features**

#### 3.1 Active power and Standby power modes

When Chip Select  $(\overline{S})$  is low, the device is selected and in the Active power mode.

When Chip Select  $(\overline{S})$  is high, the device is deselected. If a Write cycle is not currently in progress, the device then goes in to the Standby power mode, and the device consumption drops to  $I_{CC1}$ , as specified in *Table 13* and *Table 14*.

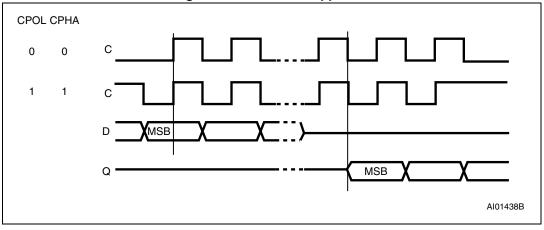

#### 3.2 SPI modes

The device can be driven by a microcontroller with its SPI peripheral running in either of the two following modes:

- CPOL=0, CPHA=0

- CPOL=1, CPHA=1

For these two modes, input data is latched in on the rising edge of Serial Clock (C), and output data is available from the falling edge of Serial Clock (C).

The difference between the two modes, as shown in *Figure 3*, is the clock polarity when the bus master is in Stand-by mode and not transferring data:

- C remains at 0 for (CPOL=0, CPHA=0)

- C remains at 1 for (CPOL=1, CPHA=1)

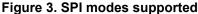

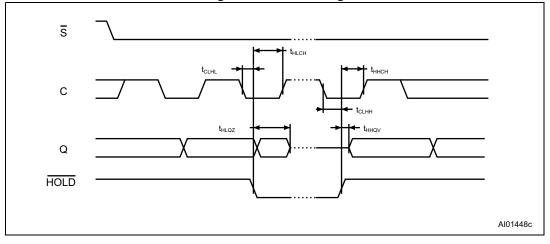

#### 3.3 Hold mode

The Hold (HOLD) signal is used to pause any serial communications with the device without resetting the clocking sequence.

The Hold mode starts when the Hold ( $\overline{HOLD}$ ) signal is driven low and the Serial Clock (C) is low (as shown in *Figure 4*). During the Hold mode, the Serial Data output (Q) is high impedance, and the signals present on Serial Data input (D) and Serial Clock (C) are not decoded. The Hold mode ends when the Hold (HOLD) signal is driven high and the Serial Clock (C) is or becomes low.

Figure 4. Hold mode activation

Deselecting the device while it is in Hold mode resets the paused communication.

#### 3.4 **Protocol control and data protection**

#### 3.4.1 **Protocol control**

The Chip Select  $(\overline{S})$  input offers a built-in safety feature, as the  $\overline{S}$  input is edge-sensitive as well as level-sensitive: after power-up, the device is not selected until a falling edge has first been detected on Chip Select  $(\overline{S})$ . This ensures that Chip Select  $(\overline{S})$  must have been high prior to going low, in order to start the first operation.

For Write commands (WRITE, WRSR, WRID, LID) to be accepted and executed:

- the Write Enable Latch (WEL) bit must be set by a Write Enable (WREN) instruction

- a falling edge and a low state on Chip Select (S) during the whole command must be decoded

- instruction, address and input data must be sent as multiple of eight bits

- the command must include at least one data byte

- Chip Select (S) must be driven high exactly after a data byte boundary

Write command can be discarded at any time by a rising edge on Chip Select ( $\overline{S}$ ) outside of a byte boundary.

To execute Read commands (READ, RDSR, RDID, RDLS), the device must decode:

- a falling edge and a low level on Chip Select (S) during the whole command

- instruction and address as multiples of eight bits (byte)

From this step, data bits are shifted out until the rising edge on Chip Select  $(\overline{S})$ .

#### 3.4.2 Status Register and data protection

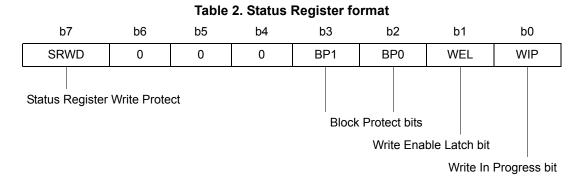

The Status Register format is shown in *Table 2* and the status and control bits of the Status Register are as follows:

Note: Bits b6, b5, b4 are always read as 0.

#### WIP bit

The WIP bit (Write In Progress) is a read-only flag that indicates the Ready/Busy state of the device. When a Write command (WRITE, WRSR, WRID, LID) has been decoded and a Write cycle ( $t_W$ ) is in progress, the device is busy and the WIP bit is set to 1. When WIP=0, the device is ready to decode a new command.

During a Write cycle, reading continuously the WIP bit allows to detect when the device becomes ready (WIP=0) to decode a new command.

#### WEL bit

The WEL bit (Write Enable Latch) bit is a flag that indicates the status of the internal Write Enable Latch. When WEL is set to 1, the Write instructions (WRITE, WRSR, WRID, LID) are executed; when WEL is set to 0, any decoded Write instruction is not executed.

The WEL bit is set to 1 with the WREN instruction. The WEL bit is reset to 0 after the following events:

- Write Disable (WRDI) instruction completion

- Write instructions (WRITE, WRSR, WRID, LID) completion including the write cycle time  $t_{\rm W}$

- Power-up

#### BP1, BP0 bits

The Block Protect bits (BP1, BP0) are non-volatile. BP1,BP0 bits define the size of the memory block to be protected against write instructions, as defined in *Table 2*. These bits are written with the Write Status Register (WRSR) instruction, provided that the Status Register is not protected (refer to "*SRWD bit and W input signal*", *on page 13*).

| Status Register bits |     | Protected block | Protected array addresses              |  |  |

|----------------------|-----|-----------------|----------------------------------------|--|--|

| BP1                  | BP0 | Protected block | Frolected array addresses              |  |  |

| 0                    | 0   | None            | None                                   |  |  |

| 0                    | 1   | Upper quarter   | 3000h-3FFFh                            |  |  |

| 1                    | 0   | Upper half      | 2000h-3FFFh                            |  |  |

| 1                    | 1   | Whole memory    | 0000h - 3FFFh plus Identification page |  |  |

Table 3. Write-protected block size

#### SRWD bit and $\overline{W}$ input signal

The Status Register Write Disable (SRWD) bit is operated in conjunction with the Write Protect pin  $(\overline{W})$  signal. When the SRWD bit is written to 0, it is possible to write the Status Register, regardless of whether the pin Write Protect  $(\overline{W})$  is driven high or low.

When the SRWD bit is written to 1, two cases have to be considered, depending on the state of the  $\overline{W}$  input pin:

- Case 1: if pin  $\overline{W}$  is driven high, it is possible to write the Status Register.

- Case 2: if pin W is driven low, it is not possible to write the Status Register (WRSR is discarded) and therefore SRWD,BP1,BP0 bits cannot be changed (the size of the protected memory block defined by BP1,BP0 bits is frozen).

Case 2 can be entered in either sequence:

- Writing SRWD bit to 1 after driving pin  $\overline{W}$  low, or

- Driving pin W low after writing SRWD bit to 1.

The only way to exit Case 2 is to pull pin  $\overline{W}$  high.

Note: if pin  $\overline{W}$  is permanently tied high, the Status Register cannot be write-protected.

The protection features of the device are summarized in Table 4.

| Table 4. | Protection | modes |

|----------|------------|-------|

|----------|------------|-------|

| SRWD bit | W signal | Status                              |  |

|----------|----------|-------------------------------------|--|

| 0        | Х        | Status Register is writable.        |  |

| 1        | 1        |                                     |  |

| 1        | 0        | Status Register is write-protected. |  |

#### 3.5 Identification page

The M95128-A125 and M95128-A145 offer an Identification page (64 byte) in addition to the 128 Kbit memory. The Identification page contains two fields:

- Device identification: the three first byte are programmed by STMicroelectronics with the Device identification code, as shown in *Table 5*.

- Application parameters: the bytes after the Device identification code are available for application specific data.

Note: If the end application does not need to read the Device identification code, this field can be overwritten and used to store application-specific data. Once the application-specific data are written in the Identification page, the whole Identification page should be permanently locked in Read-only mode.

The Read, Write, Lock Identification Page instructions are detailed in Section 4: Instructions.

| Address in<br>Identification page | Content              | Value          |

|-----------------------------------|----------------------|----------------|

| 00h                               | ST Manufacturer code | 20h            |

| 01h                               | SPI Family code      | 00h            |

| 02h                               | Memory Density code  | 0Eh (128 Kbit) |

#### Table 5. Device identification bytes

### 4 Instructions

Each command is composed of bytes (MSBit transmitted first), initiated with the instruction byte, as summarized in *Table 6*.

If an invalid instruction is sent (one not contained in *Table 6*), the device automatically enters a Wait state until deselected.

| Instruction | Description                                      | Instruction<br>format |

|-------------|--------------------------------------------------|-----------------------|

| WREN        | Write Enable                                     | 0000 0110             |

| WRDI        | Write Disable                                    | 0000 0100             |

| RDSR        | Read Status Register                             | 0000 0101             |

| WRSR        | Write Status Register                            | 0000 0001             |

| READ        | Read from Memory Array                           | 0000 0011             |

| WRITE       | Write to Memory Array                            | 0000 0010             |

| RDID        | Read Identification Page                         | 1000 0011             |

| WRID        | Write Identification Page                        | 1000 0010             |

| RDLS        | Reads the Identification Page lock status.       | 1000 0011             |

| LID         | Locks the Identification page in read-only mode. | 1000 0010             |

| Table | 6. | Instruction | set |

|-------|----|-------------|-----|

|-------|----|-------------|-----|

For read and write commands to memory array and Identification Page, the address is defined by two bytes as explained in *Table 7*.

| Instructions     | MSB Address byte |     |     |     | LSB Address byte |     |    |    |    |    |    |    |    |    |    |    |

|------------------|------------------|-----|-----|-----|------------------|-----|----|----|----|----|----|----|----|----|----|----|

| Instructions     | b15              | b14 | b13 | b12 | b11              | b10 | b9 | b8 | b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0 |

| READ or<br>WRITE | x                | x   | A13 | A12 | A11              | A10 | A9 | A8 | A7 | A6 | A5 | A4 | A3 | A2 | A1 | A0 |

| RDID or<br>WRID  | 0                | 0   | 0   | 0   | 0                | 0   | 0  | 0  | 0  | 0  | A5 | A4 | A3 | A2 | A1 | A0 |

| RDLS or<br>LID   | 0                | 0   | 0   | 0   | 0                | 1   | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

Table 7. Significant bits within the two address bytes<sup>(1)</sup>

1. A: Significant address bit.

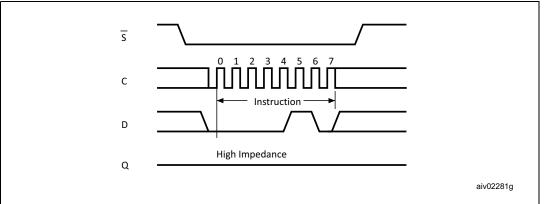

### 4.1 Write Enable (WREN)

The WREN instruction must be decoded by the device before a write instruction (WRITE, WRSR, WRID or LID).

As shown in *Figure 5*, to send this instruction to the device, Chip Select  $(\overline{S})$  is driven low, the bits of the instruction byte are shifted in (MSB first) on Serial Data Input (D) after what the Chip Select  $(\overline{S})$  input is driven high and the WEL bit is set (Status Register bit).

Figure 5. Write Enable (WREN) sequence

### 4.2 Write Disable (WRDI)

One way of resetting the WEL bit (in the Status Register) is to send a Write Disable instruction to the device.

As shown in *Figure 6*, to send this instruction to the device, Chip Select  $(\overline{S})$  is driven low, and the bits of the instruction byte are shifted in (MSB first), on Serial Data Input (D), after what the Chip Select  $(\overline{S})$  input is driven high and the WEL bit is reset (Status Register bit).

If a Write cycle is currently in progress, the WRDI instruction is decoded and executed and the WEL bit is reset to 0 with no effect on the ongoing Write cycle.

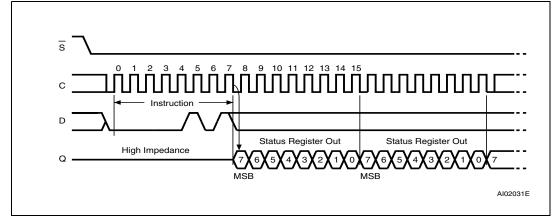

### 4.3 Read Status Register (RDSR)

The Read Status Register (RDSR) instruction is used to read the content of the Status Register.

As shown in *Figure* 7, to send this instruction to the device, Chip Select  $(\overline{S})$  is first driven low. The bits of the instruction byte are shifted in (MSB first) on Serial Data Input (D), the Status Register content is then shifted out (MSB first) on Serial Data Output (Q).

If Chip Select  $(\overline{S})$  continues to be driven low, the Status Register content is continuously shifted out.

The Status Register can always be read, even if a Write cycle  $(t_W)$  is in progress. The Status Register functionality is detailed in *Section 3.4.2: Status Register and data protection*.

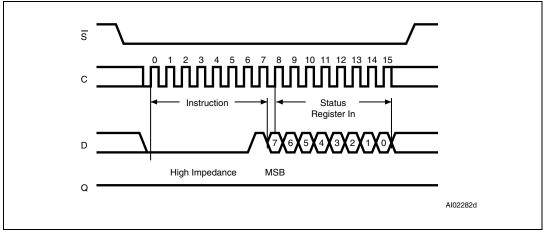

#### 4.4 Write Status Register (WRSR)

The Write Status Register (WRSR) instruction allows new values to be written to the Status Register. Before it can be accepted, a Write Enable (WREN) instruction must previously have been executed.

The Write Status Register (WRSR) instruction is entered (MSB first) by driving Chip Select  $(\overline{S})$  low, sending the instruction code followed by the data byte on Serial Data input (D), and driving the Chip Select  $(\overline{S})$  signal high.

The contents of the SRWD and BP1, BP0 bits are updated after the completion of the WRSR instruction, including the Write cycle ( $t_W$ ).

The Write Status Register (WRSR) instruction has no effect on the b6, b5, b4, b1 and b0 bits in the Status Register (see *Table 2: Status Register format*).

The Status Register functionality is detailed in *Section 3.4.2: Status Register and data protection*.

The instruction is not accepted, and is not executed, if a Write cycle is currently in progress.

#### Figure 8. Write Status Register (WRSR) sequence

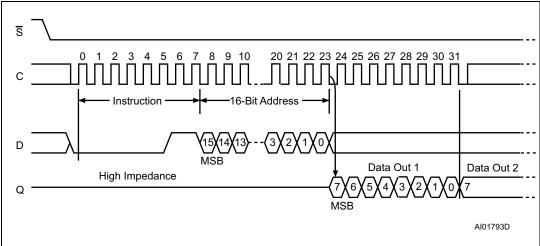

#### 4.5 Read from Memory Array (READ)

The READ instruction is used to read the content of the memory.

As shown in *Figure 9*, to send this instruction to the device, Chip Select  $(\overline{S})$  is first driven low.

The bits of the instruction byte and address bytes are shifted in (MSB first) on Serial Data Input (D) and the addressed data byte is then shifted out (MSB first) on Serial Data Output (Q). The first addressed byte can be any byte within any page.

If Chip Select  $(\overline{S})$  continues to be driven low, the internal address register is automatically incremented, and the next byte of data is shifted out. The whole memory can therefore be read with a single READ instruction.

When the highest address is reached, the address counter rolls over to zero, allowing the Read cycle to be continued indefinitely.

The Read cycle is terminated by driving Chip Select  $(\overline{S})$  high at any time when the data bits are shifted out on Serial Data Output (Q).

The instruction is not accepted, and is not executed, if a Write cycle is currently in progress.

#### Figure 9. Read from Memory Array (READ) sequence

1. Depending on the memory size, as shown in *Table* 7, the most significant address bits are Don't Care.

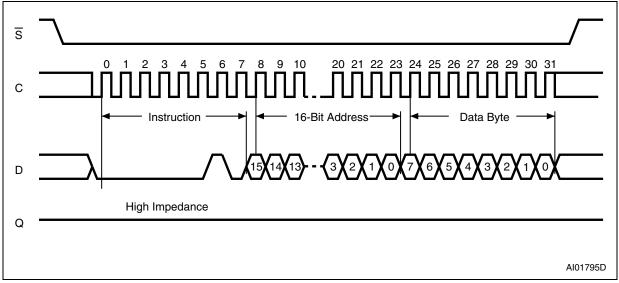

#### 4.6 Write to Memory Array (WRITE)

The WRITE instruction is used to write new data in the memory.

As shown in *Figure 10*, to send this instruction to the device, Chip Select  $(\overline{S})$  is first driven low. The bits of the instruction byte, address bytes, and at least one data byte are then shifted in (MSB first), on Serial Data Input (D). The instruction is terminated by driving Chip Select  $(\overline{S})$  high at a data byte boundary. *Figure 10* shows a single byte write.

#### Figure 10. Byte Write (WRITE) sequence

1. Depending on the memory size, as shown in *Table 7*, the most significant address bits are Don't Care.

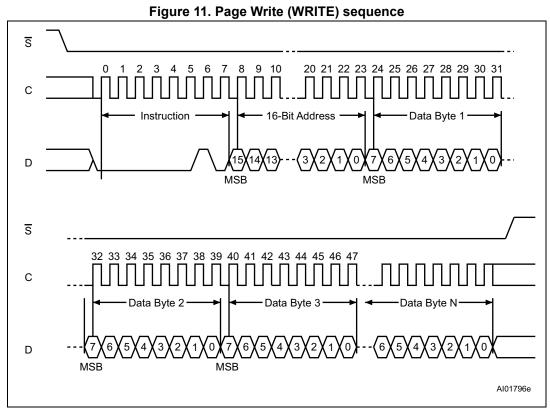

A Page write is used to write several bytes inside a page, with a single internal Write cycle.

For a Page write, Chip Select  $(\overline{S})$  has to remain low, as shown in *Figure 11*, so that the next data bytes are shifted in. Each time a new data byte is shifted in, the least significant bits of the internal address counter are incremented. If the address counter exceeds the page boundary (the page size is 64 byte), the internal address pointer rolls over to the beginning of the same page where next data bytes will be written. If more than 64 byte are received, only the last 64 byte are written.

For both Byte write and Page write, the self-timed Write cycle starts from the rising edge of Chip Select ( $\overline{S}$ ), and continues for a period t<sub>W</sub> (as specified in *Table 15*).

The instruction is discarded, and is not executed, under the following conditions:

- if a Write cycle is already in progress

- if the addressed page is in the region protected by the Block Protect (BP1 and BP0) bits

- if one of the conditions defined in Section 3.4.1 is not satisfied

Note: The self-timed Write cycle  $t_W$  is internally executed as a sequence of two consecutive events: [Erase addressed byte(s)], followed by [Program addressed byte(s)]. An erased bit is read as "0" and a programmed bit is read as "1".

1. Depending on the memory size, as shown in *Table 7*, the most significant address bits are Don't Care.

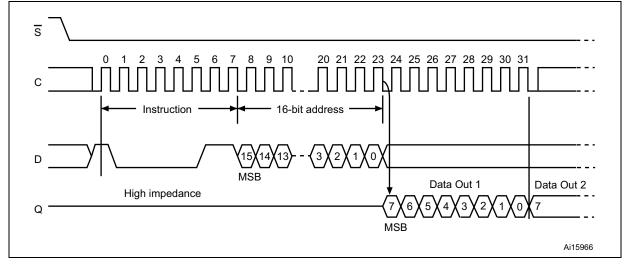

### 4.7 Read Identification Page (RDID)

The Read Identification Page instruction is used to read the Identification Page (additional page of 64 byte which can be written and later permanently locked in Read-only mode).

The Chip Select  $(\overline{S})$  signal is first driven low, the bits of the instruction byte and address bytes are then shifted in (MSB first) on Serial Data input (D). Address bit A10 must be 0 and the other upper address bits are Don't Care (it might be easier to define these bits as 0, as shown in *Table 7*). The data byte pointed to by the lower address bits [A5:A0] is shifted out (MSB first) on Serial Data output (Q).

The first byte addressed can be any byte within the identification page.

If Chip Select  $(\overline{S})$  continues to be driven low, the internal address register is automatically incremented and the byte of data at the new address is shifted out.

Note that there is no roll over feature in the Identification Page. The address of bytes to read must not exceed the page boundary.

The read cycle is terminated by driving Chip Select  $(\overline{S})$  high. The rising edge of the Chip Select  $(\overline{S})$  signal can occur at any time when the data bits are shifted out.

The instruction is not accepted, and is not executed, if a Write cycle is currently in progress.

#### Figure 12. Read Identification Page sequence

The first three bytes of the Identification page offer information about the device itself. Please refer to *Section 3.5: Identification page* for more information.

#### 4.8 Write Identification Page (WRID)

The Write Identification Page instruction is used to write the Identification Page (additional page of 64 byte which can also be permanently locked in Read-only mode).

The Chip Select signal  $(\overline{S})$  is first driven low, and then the bits of the instruction byte, address bytes, and at least one data byte are shifted in (MSB first) on Serial Data input (D). Address bit A10 must be 0 and the other upper address bits are Don't Care (it might be easier to define these bits as 0, as shown in *Table 7*). The lower address bits [A5:A0] define the byte address inside the identification page.

The self-timed Write cycle starts from the rising edge of Chip Select ( $\overline{S}$ ), and continues for a period t<sub>W</sub> (as specified in *Table 15*).

Note:

The first three bytes of the Identification page offer the Device Identification code (Please refer to Section 3.5: Identification page for more information). Using the WRID command on these first three bytes overwrites the Device Identification code.

The instruction is discarded, and is not executed, under the following conditions:

- If a Write cycle is already in progress

- If the Block Protect bits (BP1,BP0) = (1,1)

- If one of the conditions defined in Section 3.4.1: Protocol control is not satisfied.

### 4.9 Read Lock Status (RDLS)

The Read Lock Status instruction is used to read the lock status.

To send this instruction to the device, Chip Select  $(\overline{S})$  first has to be driven low. The bits of the instruction byte and address bytes are then shifted in (MSB first) on Serial Data input (D). Address bit A10 must be 1; all other address bits are Don't Care (it might be easier to define these bits as 0, as shown in *Table 7*). The Lock bit is the LSB (Least Significant Bit) of the byte read on Serial Data output (Q). It is at '1' when the lock is active and at '0' when the lock is not active. If Chip Select ( $\overline{S}$ ) continues to be driven low, the same data byte is shifted out.

The read cycle is terminated by driving Chip Select  $(\overline{S})$  high. The instruction sequence is shown in *Figure 14*.

The Read Lock Status instruction is not accepted and not executed if a Write cycle is currently in progress.

### 4.10 Lock Identification Page (LID)

The Lock Identification Page (LID) command is used to permanently lock the Identification Page in Read-only mode.

The LID instruction is issued by driving Chip Select (S) low, sending (MSB first) the instruction code, the address and a data byte on Serial Data input (D), and driving Chip Select (S) high. In the address sent, A10 must be equal to 1. All other address bits are Don't Care (it might be easier to define these bits as 0, as shown in *Table 7*). The data byte sent must be equal to the binary value xxxx xx1x, where x = Don't Care. The LID instruction is terminated by driving Chip Select (S) high at a data byte boundary, otherwise, the instruction is not executed.

Driving Chip Select (S) high at a byte boundary of the input data triggers the self-timed Write cycle which duration is  $t_W$  (specified in *Table 15*). The instruction sequence is shown in *Figure 15*.

The instruction is discarded, and is not executed, under the following conditions:

- If a Write cycle is already in progress

- If the Block Protect bits (BP1,BP0) = (1,1)

- If one of the conditions defined in Section 3.4.1: Protocol control is not satisfied.

### 5 Application design recommendations

### 5.1 Supply voltage (V<sub>CC</sub>)

#### 5.1.1 Operating supply voltage (V<sub>CC</sub>)

Prior to selecting the memory and issuing instructions to it, a valid and stable  $V_{CC}$  voltage within the specified [ $V_{CC(min)}$ ,  $V_{CC(max)}$ ] range must be applied (see *Table 10* and *Table 11*).

This voltage must remain stable and valid until the end of the transmission of the instruction and, for a Write instruction, until the completion of the internal Write cycle ( $t_W$ ). In order to secure a stable DC supply voltage, it is recommended to decouple the V<sub>CC</sub> line with a suitable capacitor (usually of the order of 10 nF to 100 nF) close to the V<sub>CC</sub>/V<sub>SS</sub> package pins.

#### 5.1.2 Power-up conditions

When the power supply is turned on,  $V_{CC}$  continuously rises from  $V_{SS}$  to  $V_{CC}$ . During this time, the Chip Select (S) line is not allowed to float but should follow the  $V_{CC}$  voltage. It is therefore recommended to connect the S line to  $V_{CC}$  via a suitable pull-up resistor (see *Figure 16*).

The V<sub>CC</sub> voltage has to rise continuously from 0 V up to the minimum V<sub>CC</sub> operating voltage defined in *Table 13* and *Table 14*.

In order to prevent inadvertent write operations during power-up, a power-on-reset (POR) circuit is included.

At power-up, the device does not respond to any instruction until  $V_{CC}$  reaches the internal threshold voltage (this threshold is defined in the DC characteristics tables 13 and 14 as VRES).

When V<sub>CC</sub> passes over the POR threshold, the device is reset and in the following state:

- in the Standby power mode

- deselected

- Status register values:

- Write Enable Latch (WEL) bit is reset to 0.

- Write In Progress (WIP) bit is reset to 0.

- SRWD, BP1 and BP0 bits remain unchanged (non-volatile bits).

- not in the Hold condition

As soon as the V<sub>CC</sub> voltage has reached a stable value within [V<sub>CC</sub>(min), V<sub>CC</sub>(max)] range, the device is ready for operation.

#### 5.1.3 Power-down

During power-down (continuous decrease in the  $V_{CC}$  supply voltage below the minimum  $V_{CC}$  operating voltage defined in *Table 13* and *Table 14*), the device must be:

- deselected (Chip Select ( $\overline{S}$ ) should be allowed to follow the voltage applied on V<sub>CC</sub>),

- in Standby power mode (there should not be any internal Write cycle in progress).

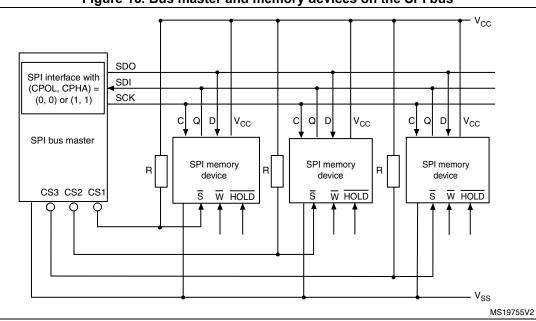

#### 5.2 Implementing devices on SPI bus

*Figure 16* shows an example of three devices, connected to the SPI bus master. Only one device is selected at a time, so that only the selected device drives the Serial Data output (Q) line. All the other devices outputs are then in high impedance.

Figure 16. Bus master and memory devices on the SPI bus

1. The Write Protect ( $\overline{W}$ ) and Hold ( $\overline{HOLD}$ ) signals must be driven high or low as appropriate.

A pull-up resistor connected on each  $\overline{/S}$  input (represented in *Figure 16*) ensures that each device is not selected if the bus master leaves the  $\overline{/S}$  line in the high impedance state.

#### 5.3 Cycling with Error Correction Code (ECC)

The Error Correction Code (ECC) is an internal logic function which is transparent for the SPI communication protocol.

The ECC logic is implemented on each group of four EEPROM bytes<sup>(a)</sup>. Inside a group, if a single bit out of the four bytes happens to be erroneous during a Read operation, the ECC detects this bit and replaces it with the correct value. The read reliability is therefore much improved.

Even if the ECC function is performed on groups of four bytes, a single byte can be written/cycled independently. In this case, the ECC function also writes/cycles the three other bytes located in the same group<sup>(a)</sup>. As a consequence, the maximum cycling budget is defined at group level and the cycling can be distributed over the 4 bytes of the group: the sum of the cycles seen by byte0, byte1, byte2 and byte3 of the same group must remain below the maximum value defined in *Table 9: Cycling performance by groups of 4 byte*.

#### Example1: maximum cycling limit reached with 1 million cycles per byte

Each byte of a group can be equally cycled 1 million times (at 25 °C) so that the group cycling budget is 4 million cycles.

#### Example2: maximum cycling limit reached with unequal byte cycling

Inside a group, byte0 can be cycled 2 million times, byte1 can be cycled 1 million times, byte2 and byte3 can be cycled 500,000 times, so that the group cycling budget is 4 million cycles.

a. A group of four bytes is located at addresses [4\*N, 4\*N+1, 4\*N+2, 4\*N+3], where N is an integer.

### 6 Delivery state

The device is delivered with:

- the memory array set to all 1s (each byte = FFh),

- Status register: bit SRWD =0, BP1 =0 and BP0 =0,

- Identification page: the first three bytes define the Device identification code (value defined in *Table 5*). The content of the following bytes is Don't Care.

### 7 Absolute maximum ratings

Stressing the device outside the ratings listed in *Table 8* may cause permanent damage to the device. These are stress ratings only, and operation of the device at these, or any other conditions outside those indicated in the operating sections of this specification, is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

| Symbol            | Parameter                                             | Min.                    | Max.                 | Unit |

|-------------------|-------------------------------------------------------|-------------------------|----------------------|------|

| T <sub>STG</sub>  | Storage temperature                                   | -65                     | 150                  | °C   |

| T <sub>AMR</sub>  | Ambient operating temperature                         |                         | 150                  | °C   |

| T <sub>LEAD</sub> | Lead temperature during soldering                     | See note <sup>(1)</sup> |                      | °C   |

| V <sub>O</sub>    | Voltage on Q pin                                      | -0.50                   | V <sub>CC</sub> +0.6 | V    |

| VI                | Input voltage                                         | -0.50                   | 6.5                  | V    |

| I <sub>OL</sub>   | DC output current (Q = 0)                             | -                       | 5                    | mA   |

| I <sub>OH</sub>   | DC output current (Q = 1)                             | -                       | 5                    | mA   |

| V <sub>CC</sub>   | Supply voltage                                        | -0.50                   | 6.5                  | V    |

| V <sub>ESD</sub>  | Electrostatic pulse (Human Body Model) <sup>(2)</sup> | -                       | 4000                 | V    |

Compliant with JEDEC Std J-STD-020D (for small body, Sn-Pb or Pb-free assembly), the ST ECOPACK<sup>®</sup> 7191395 specification, and the European directive on Restrictions of Hazardous Substances (RoHS directive 2011/65/EU of July 2011).

2. Positive and negative pulses applied on pin pairs, in accordance with AEC-Q100-002 (compliant with ANSI/ESDA/JEDEC JS-001-2012, C1=100 pF, R1=1500  $\Omega$ , R2=500  $\Omega$ )

### 8 DC and AC parameters

This section summarizes the operating conditions and the DC/AC characteristics of the device.

| Symbol             | Parameter                            | Test condition                                               | Min. | Max.      | Unit                 |

|--------------------|--------------------------------------|--------------------------------------------------------------|------|-----------|----------------------|

| Ncycle Write cycle | Write cycle endurance <sup>(1)</sup> | TA $\leq$ 25 °C, 1.7 V < V <sub>CC</sub> < 5.5 V             | -    | 4,000,000 |                      |

|                    |                                      | TA = 85 °C, 1.7 V < V <sub>CC</sub> < 5.5 V                  | -    | 1,200,000 | Write                |

|                    |                                      | TA = 125 °C, 1.7 V < V <sub>CC</sub> < 5.5 V                 | -    | 600,000   | cycle <sup>(2)</sup> |

|                    |                                      | TA = 145 °C <sup>(3)</sup> , 2.5 V < V <sub>CC</sub> < 5.5 V | -    | 400,000   |                      |

| Table 9. Cycling performanc | e by groups of 4 byte |

|-----------------------------|-----------------------|

|-----------------------------|-----------------------|

The Write cycle endurance is defined for groups of four data bytes located at addresses [4\*N, 4\*N+1, 4\*N+2, 4\*N+3] where N is an integer, or for the status register byte (refer also to Section 5.3: Cycling with Error Correction Code (ECC)). The Write cycle endurance is defined by characterization and qualification.

A Write cycle is executed when either a Page Write, a Byte Write, a WRSR, a WRID or an LID instruction is decoded. When using the Byte Write, the Page Write or the WRID, refer also to Section 5.3: Cycling with Error Correction Code (ECC).

3. For temperature range 4 only.

#### Table 10. Operating conditions (voltage range W, temperature range 4)

| Symbol          | Parameter                     | Conditions                                                                    | Min. | Max. | Unit |

|-----------------|-------------------------------|-------------------------------------------------------------------------------|------|------|------|

| V <sub>CC</sub> | Supply voltage                | -                                                                             | 2.5  | 5.5  | V    |

| T <sub>A</sub>  | Ambient operating temperature | -                                                                             | -40  | 145  | °C   |

| f <sub>C</sub>  | Operating clock frequency     | 5.5 V $\ge$ V <sub>CC</sub> $\ge$ 2.5 V, capacitive load on Q pin $\le$ 100pF | -    | 10   | MHz  |

#### Table 11. Operating conditions (voltage range R, temperature range 3)

| Symbol          | Parameter                     | Conditions                                                                |     | Max. | Unit   |

|-----------------|-------------------------------|---------------------------------------------------------------------------|-----|------|--------|

| V <sub>CC</sub> | Supply voltage                | -                                                                         | 1.7 | 5.5  | V      |

| T <sub>A</sub>  | Ambient operating temperature | -                                                                         | -40 | 125  | °C     |

| f               | Operating clock frequency     | $V_{CC} \ge 2.5$ V, capacitive load on Q pin $\le 100 \text{pF}$          | -   | 10   | MHz    |

| f <sub>C</sub>  |                               | $V_{CC} \ge 1.7 \text{ V}$ , capacitive load on Q pin $\le 100 \text{pF}$ | -   | 5    | IVITIZ |

# Table 12. Operating conditions (voltage range R, temperature range 3) for high-speed communications

| Symbol          | Parameter                     | Conditions                                                      | Min. | Max. | Unit |

|-----------------|-------------------------------|-----------------------------------------------------------------|------|------|------|

| V <sub>CC</sub> | Supply voltage                | -                                                               | 4.5  | 5.5  | V    |

| T <sub>A</sub>  | Ambient operating temperature | -                                                               | -40  | 85   | °C   |

| f <sub>C</sub>  | Operating clock frequency     | $V_{CC} \ge 4.5$ V, capacitive load on Q pin $\le 60~\text{pF}$ | -    | 20   | MHz  |

30/43

| Symbol                          | Parameter                              | Specific test conditions<br>(in addition to conditions specified in<br><i>Table 10</i> )                                          | Min.                | Max.                | Unit       |  |

|---------------------------------|----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|---------------------|---------------------|------------|--|

| C <sub>OUT</sub> <sup>(2)</sup> | Output capacitance (Q)                 | V <sub>OUT</sub> = 0 V                                                                                                            | -                   | 8                   | ~ <b>F</b> |  |

| C <sub>IN</sub> <sup>(2)</sup>  | Input capacitance                      | V <sub>IN</sub> = 0 V                                                                                                             | -                   | 6                   | pF         |  |

| I <sub>LI</sub>                 | Input leakage current                  | $V_{IN} = V_{SS} \text{ or } V_{CC}$                                                                                              | -                   | 2                   |            |  |