# TDA7449

# Digital tone control audio processor

#### Datasheet - production data

## Features

- Input multiplexer

- Two stereo inputs

- Selectable input gain for optimal adaptation to different sources

- One stereo output

- Treble and bass control in 2.0 db steps

- Volume control in 1.0 db steps

- Two speaker attenuators:

- Two independent speaker controls in 1.0 db steps to facilitate balance

- Independent mute function

- All functions are programmable via serial bus

# Description

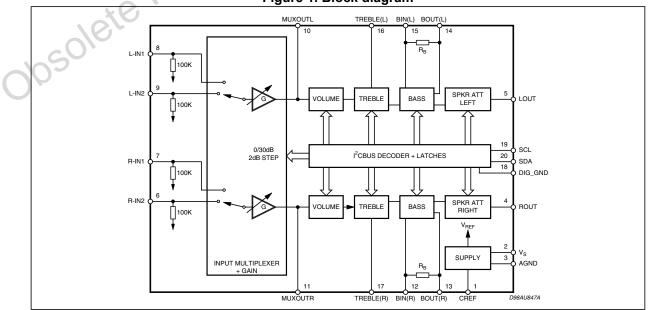

The TDA7449 is a volume tone (bass and treble) balance (left/right) processor for quality audio applications in TV systems. Selectable input gain is provided. A serial bus controls all functions.

The AC signal setting is obtained by resistor networks and switches combined with operational amplifiers.

Bipolar/CMOS technology used allows obtaining low distortion, low noise and DC stepping.

### Table 1. Device summary

| Order code   | Package | Packing       |

|--------------|---------|---------------|

| TDA7449D13TR | SO20    | Tape and reel |

### Figure 1. Block diagram

#### September 2014

DocID006317 Rev 5

This is information on a product in full production.

# Contents

| 1    | Over               | view                                                 |

|------|--------------------|------------------------------------------------------|

| 2    | Elect              | rical characteristics and test circuit               |

| 3    | Appli              | cation recommendations7                              |

|      | 3.1                | Bass, stages                                         |

|      | 3.2                | Treble stage                                         |

|      | 3.3                | Treble stage         7           CREF         8      |

| 4    | l <sup>2</sup> C b | us interface                                         |

|      | 4.1                | Data validity                                        |

|      | 4.2                | Start and stop conditions                            |

|      | 4.3                | Start and stop conditions    9      Byte format    9 |

|      | 4.4                | Acknowledge                                          |

|      | 4.5                | Transmission without acknowledge9                    |

| 5    | Softw              | vare specifications                                  |

|      | 5.1                | Interface protocol                                   |

| 6    | Exan               | nples                                                |

|      | 6.1                | No incremental bus                                   |

| 019  | 6.2                | Incremental bus                                      |

| NS C | Data               | bytes                                                |

| 8    | Pack               | age information                                      |

| 9    | Revis              | sion history                                         |

#### **Overview** 1

| Symbol           | Parameter                     | Value      | Unit |

|------------------|-------------------------------|------------|------|

| V <sub>S</sub>   | Operating supply voltage      | 10.5       | V    |

| T <sub>amb</sub> | Operating ambient temperature | 0 to 70    | °C   |

| T <sub>stg</sub> | Storage temperature range     | -55 to 150 | °C   |

| Figu             | ure 2. Pin cor | nnections      |

|------------------|----------------|----------------|

| CREF [           |                | 20 🗆 SDA       |

| V <sub>S</sub> [ | 2              | 19 SCL         |

| PGND [           | 3              | 18 DIG_GND     |

| ROUT [           | 4              | 17 TREBLE(R)   |

| LOUT [           | 5              | 16 TREBLE(L)   |

| R_IN2 [          | 6              | 15 🗍 BIN(L)    |

| R_IN1 [          | 7              | 14 🔲 BOUT(L)   |

| L_IN1 [          | 8              | 13 🔲 BOUT(R)   |

| L_IN2 [          | 9              | 12 🔲 BIN(R)    |

| MUXOUT(L)        | 10             | 11 🔲 MUXOUT(R) |

|                  | D98AU848       |                |

#### Table 2. Absolute maximum ratings

## Table 3. Thermal data

| Symbol                | Parameter                        | Value | Unit |

|-----------------------|----------------------------------|-------|------|

| R <sub>th j-pin</sub> | Thermal resistance junction pins | 85    | °C/W |

#### Table 4. Quick reference data

|     | R <sub>th j-pin</sub> | Thermal resistance junction pins                             |      |      | °C/W |                  |

|-----|-----------------------|--------------------------------------------------------------|------|------|------|------------------|

|     | xeP                   | Table 4. Quick reference data                                |      |      |      |                  |

| 26  | Symbol                | Parameter                                                    | Min. | Тур. | Max. | Unit             |

| SO  | V <sub>S</sub>        | Supply voltage                                               | 6    | 9    | 10.2 | V                |

| 00- | V <sub>CL</sub>       | Max input signal handling                                    | 2    |      |      | V <sub>RMS</sub> |

|     | THD                   | Total harmonic distortion V = 0.1 Vrms f = 1 kHz             |      | 0.01 | 0.1  | %                |

|     | S/N                   | Signal-to-noise ratio V <sub>out</sub> = 1 Vrms (mode = OFF) |      | 106  |      | dB               |

|     | S <sub>C</sub>        | Channel separation f = 1 KHz                                 |      | 90   |      | dB               |

|     |                       | Input gain (2 dB step)                                       | 0    |      | 30   | dB               |

|     |                       | Volume control (1 dB step)                                   | -47  |      | 0    | dB               |

|     |                       | Treble control (2 dB step)                                   | -14  |      | 14   | dB               |

|     |                       | Bass control (2 dB step)                                     | -14  |      | 14   | dB               |

|     |                       | Balance control 1 dB step                                    | -79  |      | 0    | dB               |

|     |                       | Mute attenuation                                             |      | 100  |      | dB               |

2

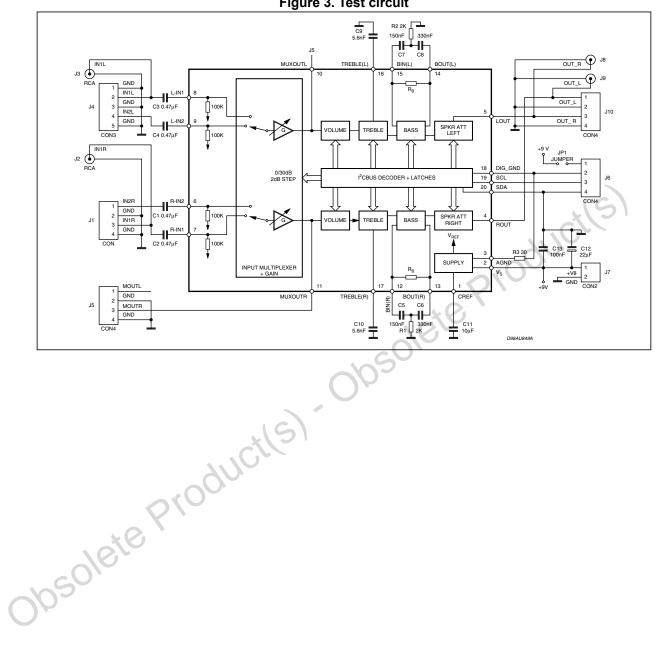

| Table 5. Electrical characteristics (refer to the test circuit $T_{arr}$                | <sub>1b</sub> = 25 °C, V <sub>S</sub> = 9 V, |

|-----------------------------------------------------------------------------------------|----------------------------------------------|

| $R_L$ = 10 k $\Omega$ , $R_G$ = 600 $\Omega$ , all controls flat (G = 0 dB), unless oth | nerwise specified)                           |

| Symbol             | Parameter                    | Test Condition                                           | Min.  | Тур.  | Max.  | Unit |

|--------------------|------------------------------|----------------------------------------------------------|-------|-------|-------|------|

| Supply             |                              |                                                          |       | 1     |       |      |

| V <sub>S</sub>     | Supply voltage               |                                                          | 6     | 9     | 10.2  | V    |

| ۱ <sub>S</sub>     | Supply current               |                                                          |       | 7     |       | mA   |

| SVR                | Ripple rejection             |                                                          | 60    | 90    | 10    | dB   |

| Input stage        | -                            |                                                          |       |       | d     | 51   |

| R <sub>IN</sub>    | Input resistance             |                                                          |       | 100   |       | kΩ   |

| V <sub>CL</sub>    | Clipping level               | THD = 0.3%                                               | 2     | 2.5   |       | Vrms |

| S <sub>IN</sub>    | Input separation             | The selected input is grounded through a 2.2 µ capacitor | 80    | 100   |       | dB   |

| G <sub>inmin</sub> | Minimum input gain           |                                                          | -1    | 0     | 1     | dB   |

| G <sub>inman</sub> | Maximum input gain           | 05                                                       |       | 30    |       | dB   |

| G <sub>step</sub>  | Step resolution              | 06                                                       |       | 2     |       | dB   |

| Volume contro      |                              |                                                          |       |       | •     |      |

| C <sub>RANGE</sub> | Control range                |                                                          | 45    | 47    | 49    | dB   |

| A <sub>VMAX</sub>  | Max. attenuation             |                                                          | 45    | 47    | 49    | dB   |

| A <sub>STEP</sub>  | Step resolution              |                                                          | 0.5   | 1     | 1.5   | dB   |

| E                  | Attenuation set error        | A <sub>V</sub> = 0 to -24 dB                             | -1.0  | 0     | 1.0   | dB   |

| E <sub>A</sub>     | Allendalion set enor         | A <sub>V</sub> = -24 to -47 dB                           | -1.5  | 0     | 1.5   | dB   |

| -16/               | Tracking error               | A <sub>V</sub> = 0 to -24 dB                             |       | 0     | 1     | dB   |

| ET                 |                              | A <sub>V</sub> = -24 to -47 dB                           |       | 0     | 2     | dB   |

| V <sub>DC</sub>    | DC step                      | adjacent attenuation steps                               |       | 0     | 3     | mV   |

| • DC               |                              | from 0 dB to A <sub>V</sub> max                          |       | 0.5   |       | mV   |

| A <sub>mute</sub>  | Mute attenuation             |                                                          | 80    | 100   |       | dB   |

| Bass control (1    | )                            |                                                          |       |       |       |      |

| Gb                 | Control range                | Max. boost/cut                                           | +12.0 | +14.0 | +16.0 | dB   |

| B <sub>STEP</sub>  | Step resolution              |                                                          | 1     | 2     | 3     | dB   |

| R <sub>B</sub>     | Internal feedback resistance |                                                          | 18.75 | 25    | 31.25 | KΩ   |

| Treble control     | (1)                          |                                                          |       |       |       |      |

| Gt                 | Control range                | Max. boost/cut                                           | +13.0 | +14.0 | +15.0 | dB   |

| T <sub>STEP</sub>  | Step resolution              |                                                          | 1     | 2     | 3     | dB   |

| Symbol             | Parameter                         | Test condition                              | Min. | Тур. | Max. | Unit             |

|--------------------|-----------------------------------|---------------------------------------------|------|------|------|------------------|

| Speaker atten      | uators                            |                                             |      |      |      | 1                |

| C <sub>RANGE</sub> | Control range                     |                                             |      | 76   |      | dB               |

| S <sub>STEP</sub>  | Step resolution                   |                                             | 0.5  | 1    | 1.5  | dB               |

|                    | Attenuetien oot error             | A <sub>V</sub> = 0 to -20 dB                | -1.5 | 0    | 1.5  | dB               |

| E <sub>A</sub>     | Attenuation set error             | A <sub>V</sub> = -20 to -56 dB              | -2   | 0    | 2    | dB               |

| V <sub>DC</sub>    | DC Step                           | adjacent attenuation steps                  |      | 0    | 3    | mV               |

| A <sub>mute</sub>  | Mute attenuation                  |                                             | 80   | 100  | 210  | dB               |

| Audio outputs      | 5                                 |                                             |      |      | Cr   |                  |

| V <sub>CLIP</sub>  | Clipping level                    | d = 0.3%                                    | 2.1  | 2.6  | P*   | V <sub>RMS</sub> |

| RL                 | Output load resistance            |                                             | 2    | 9    |      | kΩ               |

| R <sub>O</sub>     | Output impedance                  | . 0.                                        | 10   | 40   | 70   | W                |

| V <sub>DC</sub>    | DC voltage level                  | 1010                                        |      | 3.8  |      | V                |

| General            |                                   | SOL                                         |      |      | •    |                  |

| E <sub>NO</sub>    | Output noise                      | All gains = 0dB;<br>BW = 20Hz to 20KHz flat |      | 5    | 15   | μV               |

| F                  | Total tracking error              | A <sub>V</sub> = 0 to -24dB                 |      | 0    | 1    | dB               |

| Et                 | Total tracking error              | A <sub>V</sub> = -24 to -47dB               |      | 0    | 2    | dB               |

| S/N                | Signal-to-Noise ratio             | All gains 0dB; $V_0 = 1V_{RMS}$ ;           |      | 106  |      | dB               |

| S <sub>C</sub>     | Channel separation left/right     |                                             | 80   | 100  |      | dB               |

| d                  | Distortion                        | $A_V = 0; V_I = 1V_{RMS};$                  |      | 0.01 | 0.08 | %                |

| Bus input 🖕        | 0                                 |                                             |      |      |      |                  |

| VIL                | Input low voltage                 |                                             |      |      | 1    | V                |

| <b>V</b> IH        | Input high voltage                |                                             | 3    |      |      | V                |

| I <sub>IN</sub>    | Input current                     | V <sub>IN</sub> = 0.4 V                     | -5   |      | 5    | μA               |

| V <sub>O</sub>     | Output voltage SDA<br>acknowledge | I <sub>O</sub> = 1.6 mA                     |      | 0.4  | 0.8  | V                |

**Table 5. Electrical characteristics** (refer to the test circuit  $T_{amb} = 25$  °C,  $V_S = 9$  V,  $R_L = 10 \text{ k}\Omega$ ,  $R_G = 600 \Omega$ , all controls flat (G = 0 dB), unless otherwise specified) (continued)

Note:

1. The device is functionally good at Vs = 5 V. A step down on Vs to 4 V doesn't reset the device.

2. Bass and treble response: the center frequency and the response quality can be chosen by the external circuitry.

# 3 Application recommendations

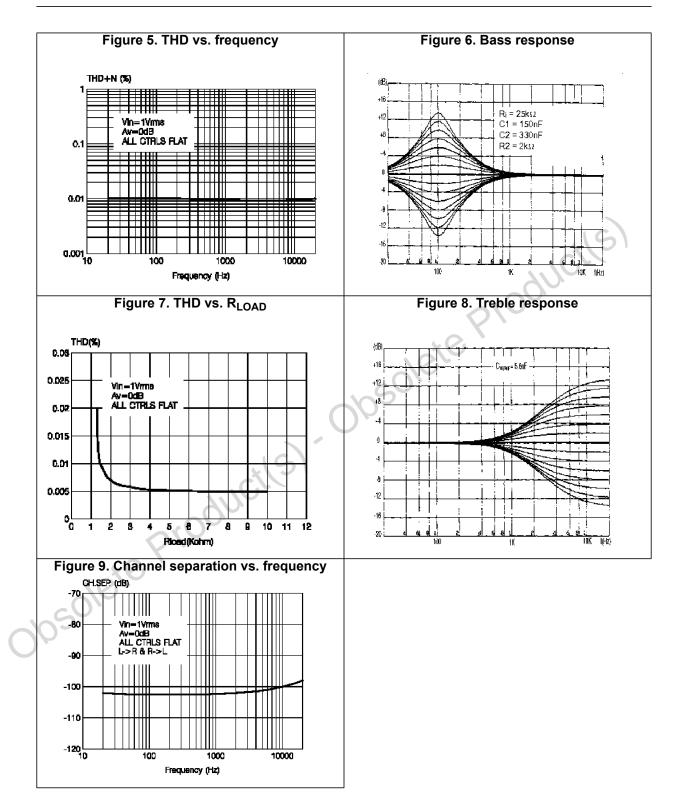

The first and the last stages are volume control blocks. The control range is 0 to -47 dB (mute) for the first one and 0 to -79 dB (mute) for the last one. Both of them have 1 dB step resolution. The very high resolution allows the implementation of systems free from any noisy acoustical effect. The TDA7449 audio processor provides dual-band tone control. Typical responses are shown in *Figure 5* through *9*.

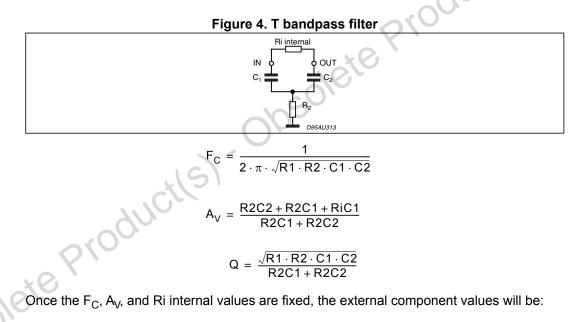

# 3.1 Bass stage

The bass cell has an internal resistor Ri = 25 k $\Omega$  typical. Several filter types can be implemented, connecting external components to the bass IN and OUT pins. *Figure 4* refers to a basic T-type bandpass filter. The filter component values R1 internal F<sub>C</sub>, the gain A<sub>V</sub> at max. boost and the filter Q factor are calculated as given below.

$$C1 = \frac{A_V - 1}{2 \cdot \pi \cdot Fc \cdot Ri \cdot Q}$$

$$C2 = \frac{Q^2 \cdot C1}{A_V - 1 - Q^2}$$

$$R2 = \frac{A_V - 1 - Q^2}{2 \cdot \pi \cdot C1 \cdot Fc \cdot (A_V - 1) \cdot Q}$$

# 3.2 Treble stage

The treble stage is a high-pass filter whose time constant is fixed by an internal resistor (25 k $\Omega$  typical) and an external capacitor connected between the treble pins and ground.

# 3.3 CREF

The recommended 10  $\mu$ F reference capacitor (CREF) value can be reduced to 4.7  $\mu$ F if the application requires faster power ON.

# 4 I<sup>2</sup>C bus interface

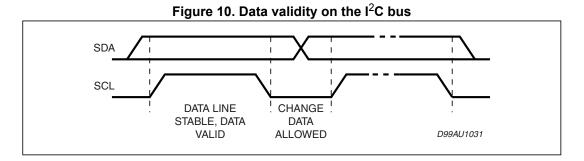

Data transmission from the microprocessor to the TDA7449 and vice versa takes place through the 2-wire  $I^2C$  bus interface, consisting of the two lines SDA and SCL (pull-up resistors to the positive supply voltage must be connected).

## 4.1 Data validity

As shown in *Figure 10*, the data on the SDA line must be stable during the high period of the clock. The HIGH and LOW state of the data line can only change when the clock signal on the SCL line is LOW.

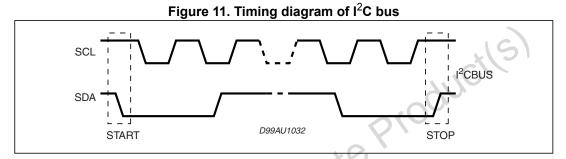

## 4.2 Start and stop conditions

As shown in *Figure 11*, a start condition is a HIGH-to-LOW transition of the SDA line while SCL is HIGH. The stop condition is a LOW-to-HIGH transition of the SDA line while SCL is HIGH.

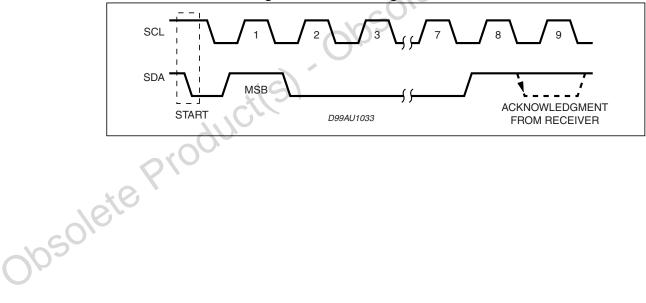

## 4.3 Byte format

Every byte transferred on the SDA line must contain 8 bits. Each byte must be followed by an acknowledge bit. The MSB is transferred first.

# 4.4 Acknowledge

The master ( $\mu$ P) puts a resistive HIGH level on the SDA line during the acknowledge clock pulse (see *Figure 12*). The peripheral (audio processor) that acknowledges has to pull down (LOW) the SDA line during this clock pulse.

The audio processor which has been addressed has to generate an acknowledge after the reception of each byte, otherwise the SDA line remains at the HIGH level during the ninth clock pulse time. In this case the master transmitter can generate the STOP information in order to abort the transfer.

### 4.5

### Transmission without acknowledge

Instead of detecting the acknowledge from the audio processor, the  $\mu P$  can use a simpler transmission which is to simply wait one clock pulse without checking the slave acknowledge and send the new data.

This is of course a riskier approach.

#### Software specifications 5

#### 5.1 Interface protocol

The interface protocol comprises:

- A start condition (S) •

- A chip address byte, containing the TDA7449 address •

- A subaddress byte •

- A sequence of data (N byte + acknowledge)

- A stop condition (P)

|        |                    | Figure  | 13. Interface     | protocol   | atle   |

|--------|--------------------|---------|-------------------|------------|--------|

|        | CHIP ADDRESS       | SUB     | ADDRESS           | DATA 1 to  | DATA n |

|        | MSB                | LSB MSB | LSB               | MSB        | LSB    |

|        | ·                  |         | B DATA AC         |            |        |

|        | D96AU420           |         | I                 |            |        |

|        | ACK = Acknowledge  |         |                   | <u> 10</u> |        |

|        | S = Start          |         | ~1050H            | 6          |        |

|        | P = Stop           |         | ~10 <sup>50</sup> |            |        |

|        | A = Address        |         |                   |            |        |

|        | B = Auto-increment |         |                   |            |        |

| obsole | B = Auto-increment |         |                   |            |        |

#### **Examples** 6

#### 6.1 No incremental bus

The TDA7449 receives a start condition, the correct chip address, a subaddress with B = 0 (no incremental bus), N-data (all these data concern the subaddress selected), a stop condition.

Figure 14. No incremental bus (B = 0)

| CHIP ADDRESS       SUBADDRESS       DATA         MSB       LSB       MSB       LSB         S       1       0       0       ACK       X       X       0       D3       D2       D1       D0       ACK       P         D96AU421       D96AU421       D       D       ACK       P       D       D       C       C       D       C       C       P       D       D       C       C       P       D       D       C       D       C       D       C       D       C       D       C       D       C       D       C       D       C       D       C       D       C       D       C       D       C       D       C       D       C       D       C       D       C       D       D       C       D       D       C       D       D       C       D       D       C       D       D       C       D       D       C       D       D       D       D       D       D       D       D       D       D       D       D       D       D       D       D       D       D       D       D       D <td< th=""><th></th><th></th><th></th><th></th><th></th><th></th><th></th><th></th><th></th><th></th><th>_</th><th></th><th></th><th></th><th></th><th></th><th></th><th></th><th></th><th></th><th>•</th><th>,</th><th></th><th></th><th></th><th></th><th></th><th></th><th></th><th></th></td<> |    |          |   |                |      |          |      |   |     |     | _   |   |    |     |    |     |    |     |     |          | • | ,   |     |   |   |     |     |     |    |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|----------|---|----------------|------|----------|------|---|-----|-----|-----|---|----|-----|----|-----|----|-----|-----|----------|---|-----|-----|---|---|-----|-----|-----|----|--|

| S       1       0       0       0       ACK       X       X       0       D3       D2       D1       D0       ACK       ACK       P         D96AU421                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |          |   | СНІ            | P AI | DDF      | RESS | 3 |     |     |     |   | SU | BAD | DR | ESS |    |     |     |          |   | DAT | A   |   |   |     |     |     |    |  |

| D96AU421                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    | l<br>MSE | 3 |                |      |          |      |   | LSB |     | MSE | 3 |    |     |    |     | I  | LSB |     | I<br>MSB |   |     |     |   |   | LSB | 1   |     | ~  |  |

| duces                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | s  | 1        | 0 | 0              | 0    | 1        | 0    | 0 | 0   | ACK | Х   | Х | Х  | 0   | D3 | D2  | D1 | D0  | ACK |          |   | DAT | A   |   |   |     | ACK | ( P | 51 |  |

| Incremental hus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |          |   | D96,           | AU42 | 1        |      |   |     |     |     |   |    |     |    |     |    |     |     |          |   |     |     |   |   |     | C   | 2   |    |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | In | ۰r       |   | m              | ٥r   | nte      | al   | h | e   | •   |     |   |    |     |    |     |    |     |     |          |   |     | . ( | 5 | 9 |     |     |     |    |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    | -        |   | ۰ <del>-</del> |      | <b>`</b> |      | • |     | 4 - |     |   |    |     |    |     |    |     |     |          | 1 |     | -   |   |   |     |     |     |    |  |

#### 6.2 Incremental bus

The TDA7449 receives a start condition, the correct chip address, a subaddress with B = 1 (incremental bus): now it is in a loop condition with an autoincrease of the subaddress whereas SUBADDRESS from "XXX1000" to "XXX1111" of DATA are ignored.

DATA 1 concern the subaddress sent, and DATA 2 concerns the subaddress sent plus one in the loop etc, and at the end it receives the stop condition.

| CHIP ADDRESS            | SUBADDRESS        | DATA 1 to DAT | An    |

|-------------------------|-------------------|---------------|-------|

| MSB LSB MSB             | LSB               | MSB           | LSB   |

| S 1 0 0 0 1 0 0 0 ACK X | X X 1 D3 D2 D1 D0 | ACK DATA      | ACK P |

| D96AU422                |                   |               |       |

|      | Table 6. Power-on reset | condition |

|------|-------------------------|-----------|

| 3    | Input selection         | IN2       |

| 10   | Input gain              | 28 dB     |

| c0'  | Volume                  | Mute      |

| 0/05 | Bass                    | 0 dB      |

|      | Treble                  | 2 dB      |

|      | Speaker                 | Mute      |

### Table 6 Power-on reset condition

#### Data bytes 7

Address = 88 hex (Addr: OPEN)

|          | LSB    |          |      |    |     |      |    | Subaddroos            |  |  |

|----------|--------|----------|------|----|-----|------|----|-----------------------|--|--|

| D7       | D6     | D5       | D4   | D3 | D2  | D1   | D0 | Subaddress            |  |  |

| Х        | Х      | Х        | В    | 0  | 0   | 0    | 0  | Input select          |  |  |

| Х        | Х      | Х        | В    | 0  | 0   | 0    | 1  | Input gain            |  |  |

| Х        | Х      | Х        | В    | 0  | 0   | 1    | 0  | Volume                |  |  |

| Х        | Х      | Х        | В    | 0  | 0   | 1    | 1  | Not allowed           |  |  |

| Х        | Х      | Х        | В    | 0  | 1   | 0    | 0  | Bass                  |  |  |

| Х        | Х      | Х        | В    | 0  | 1   | 0    | 1  | Treble                |  |  |

| Х        | Х      | Х        | В    | 0  | 1   | 1    | 0  | Speaker attenuate "R" |  |  |

| Х        | Х      | Х        | В    | 0  | 1   | 10   | 1  | Speaker attenuate "L" |  |  |

| 1: incre | ementa | l bus ac | tive | C  | 105 | ,0,- |    |                       |  |  |

### Table 7. Function selection: first byte (subaddress)

X = don't care

|     | MSB | .0 | 30 |    |    |    |    | Input multiplexer |                   |

|-----|-----|----|----|----|----|----|----|-------------------|-------------------|

|     | D7  | D6 | D5 | D4 | D3 | D2 | D1 | D0                | input multiplexer |

|     | X   | Х  | Х  | Х  | Х  | X  | 0  | 0                 | Not allowed       |

| 76  | Х   | Х  | Х  | Х  | Х  | Х  | 0  | 1                 | Not allowed       |

| SO. | Х   | Х  | Х  | Х  | Х  | X  | 1  | 0                 | IN2               |

| 005 | Х   | Х  | Х  | Х  | Х  | Х  | 1  | 1                 | IN1               |

|     |     |    |    |    |    |    |    |                   |                   |

#### Table 8. Input selection

1

| MSB |    | LSB | Input gain |    |    |    |    |            |

|-----|----|-----|------------|----|----|----|----|------------|

| D7  | D6 | D5  | D4         | D3 | D2 | D1 | D0 | 2 dB steps |

|     |    |     |            | 0  | 0  | 0  | 0  | 0 dB       |

|     |    |     |            | 0  | 0  | 0  | 1  | 2 dB       |

|     |    |     |            | 0  | 0  | 1  | 0  | 4 dB       |

|     |    |     |            | 0  | 0  | 1  | 1  | 6 dB       |

|     |    |     |            | 0  | 1  | 0  | 0  | 8 dB       |

|     |    |     |            | 0  | 1  | 0  | 1  | 10 dB      |

|     |    |     |            | 0  | 1  | 1  | 0  | 12 dB      |

|     |    |     |            | 0  | 1  | 1  | 1  | 14 dB      |

|     |    |     |            | 1  | 0  | 0  | 0  | 16 dB      |

|     |    |     |            | 1  | 0  | 0  | 1  | 18 dB      |

|     |    |     |            | 1  | 0  | 1  | 0  | 20 dB      |

|     |    |     |            | 1  | 0  | 1  | 71 | 22 dB      |

|     |    |     |            | 1  | 1  | 0  | 0  | 24 dB      |

|     |    |     |            | 1  | 1  | 0  | 1  | 26 dB      |

|     |    |     |            | 1  | 1  | 1  | 0  | 28 dB      |

|     |    |     |            | 1  | 51 | 1  | 1  | 30 dB      |

|     |    |     |            | O, |    |    |    |            |

| Table 9. I | nput ga | in selecti | on |

|------------|---------|------------|----|

|------------|---------|------------|----|

Gain = 0 to 30 dB

|       | MSB  |    | $\cdot 0$ |    |    |    | LSB | Volume |            |  |

|-------|------|----|-----------|----|----|----|-----|--------|------------|--|

|       | D7   | D6 | D5        | D4 | D3 | D2 | D1  | D0     | 1 dB steps |  |

|       |      |    |           |    |    | 0  | 0   | 0      | 0 dB       |  |

|       |      |    |           |    |    | 0  | 0   | 1      | -1 dB      |  |

|       | KO I |    |           |    |    | 0  | 1   | 0      | -2 dB      |  |

| de    |      |    |           |    |    | 0  | 1   | 1      | -3 dB      |  |

| 00501 |      |    |           |    |    | 1  | 0   | 0      | -4 dB      |  |

|       |      |    |           |    |    | 1  | 0   | 1      | -5 dB      |  |

|       |      |    |           |    |    | 1  | 1   | 0      | -6 dB      |  |

|       |      |    |           |    |    | 1  | 1   | 1      | -7 dB      |  |

|       |      | 0  | 0         | 0  | 0  |    |     |        | 0 dB       |  |

|       |      | 0  | 0         | 0  | 1  |    |     |        | -8 dB      |  |

|       |      | 0  | 0         | 1  | 0  |    |     |        | -16 dB     |  |

|       |      | 0  | 0         | 1  | 1  |    |     |        | -24 dB     |  |

|       |      | 0  | 1         | 0  | 0  |    |     |        | -32 dB     |  |

|       |      | 0  | 1         | 0  | 1  |    |     |        | -40 dB     |  |

|       |      | Х  | 1         | 1  | 1  | Х  | Х   | X      | Mute       |  |

## Table 10. Volume selection

Volume = 0 to 47dB/mute

| MSB |    |    |    |    |    |     | LSB | Bass       |

|-----|----|----|----|----|----|-----|-----|------------|

| D7  | D6 | D5 | D4 | D3 | D2 | D1  | D0  | 2 dB steps |

|     |    |    |    | 0  | 0  | 0   | 0   | -14 dB     |

|     |    |    |    | 0  | 0  | 0   | 1   | -12 dB     |

|     |    |    |    | 0  | 0  | 1   | 0   | -10 dB     |

|     |    |    |    | 0  | 0  | 1   | 1   | -8 dB      |

|     |    |    |    | 0  | 1  | 0   | 0   | -6 dB      |

|     |    |    |    | 0  | 1  | 0   | 1   | -4 dB      |

|     |    |    |    | 0  | 1  | 1   | 0   | -2 dB      |

|     |    |    |    | 0  | 1  | 1   | 1   | 0 dB       |

|     |    |    |    | 1  | 1  | 1   | 1   | 0 dB       |

|     |    |    |    | 1  | 1  | 1   | 0   | 2 dB       |

|     |    |    |    | 1  | 1  | 0   |     | 4 dB       |

|     |    |    |    | 1  | 1  | 0   | 0   | 6 dB       |

|     |    |    |    | 1  | 0  | T I | 1   | 8 dB       |

|     |    |    |    | 1  | 0  | 1   | 0   | 10 dB      |

|     |    |    |    | 1  | 0  | 0   | 1   | 12 dB      |

|     |    |    |    | 1  | 0  | 0   | 0   | 14 dB      |

Table 11. Bass selection

### Table 12. Treble selection

|             | MSB |    | , C) |    |    |    |    | LSB | Treble     |

|-------------|-----|----|------|----|----|----|----|-----|------------|

|             | D7  | D6 | D5   | D4 | D3 | D2 | D1 | D0  | 2 dB steps |

|             |     | 3  |      |    | 0  | 0  | 0  | 0   | -14 dB     |

|             | X   |    |      |    | 0  | 0  | 0  | 1   | -12 dB     |

|             | Ś   |    |      |    | 0  | 0  | 1  | 0   | -10 dB     |

| obsole      |     |    |      |    | 0  | 0  | 1  | 1   | -8 dB      |

| SO          |     |    |      |    | 0  | 1  | 0  | 0   | -6 dB      |

| $0^{0^{2}}$ |     |    |      |    | 0  | 1  | 0  | 1   | -4 dB      |

| U           |     |    |      |    | 0  | 1  | 1  | 0   | -2 dB      |

|             |     |    |      |    | 0  | 1  | 1  | 1   | 0 dB       |

|             |     |    |      |    | 1  | 1  | 1  | 1   | 0 dB       |

|             |     |    |      |    | 1  | 1  | 1  | 0   | 2 dB       |

|             |     |    |      |    | 1  | 1  | 0  | 1   | 4 dB       |

|             |     |    |      |    | 1  | 1  | 0  | 0   | 6 dB       |

|             |     |    |      |    | 1  | 0  | 1  | 1   | 8 dB       |

|             |     |    |      |    | 1  | 0  | 1  | 0   | 10 dB      |

|             |     |    |      |    | 1  | 0  | 0  | 1   | 12 dB      |

|             |     |    |      |    | 1  | 0  | 0  | 0   | 14 dB      |

| M | SB |            |    |     |    |    |    | LSB | Speaker attenuation |  |

|---|----|------------|----|-----|----|----|----|-----|---------------------|--|

| D | 7  | D6         | D5 | D4  | D3 | D2 | D1 | D0  | 1 dB                |  |

|   |    |            |    |     |    | 0  | 0  | 0   | 0 dB                |  |

|   |    |            |    |     |    | 0  | 0  | 1   | -1 dB               |  |

|   |    |            |    |     |    | 0  | 1  | 0   | -2 dB               |  |

|   |    |            |    |     |    | 0  | 1  | 1   | -3 dB               |  |

|   |    |            |    |     |    | 1  | 0  | 0   | -4 dB               |  |

|   |    |            |    |     |    | 1  | 0  | 1   | -5 dB               |  |

|   |    |            |    |     |    | 1  | 1  | 0   | -6 dB               |  |

|   |    |            |    |     |    | 1  | 1  | 1   | -7 dB               |  |

|   |    |            |    |     |    |    |    | 0   | 0                   |  |

|   |    | 0          | 0  | 0   | 0  |    |    | X   | 0 dB                |  |

|   |    | 0          | 0  | 0   | 1  |    |    | 0   | -8 dB               |  |

|   |    | 0          | 0  | 1   | 0  |    |    |     | -16 dB              |  |

|   |    | 0          | 0  | 1   | 1  | S  |    |     | -24 dB              |  |

|   |    | 0          | 1  | 0   | 0  | )  |    |     | -32 dB              |  |

|   |    | 0          | 1  | 0   | 1  |    |    |     | -40 dB              |  |

|   |    | 0          | 1  | (6) | 0  |    |    |     | -48 dB              |  |

|   |    | 0          | 10 | 1   | 1  |    |    |     | -56 dB              |  |

|   |    | 1          | 0  | 0   | 0  |    |    |     | -64 dB              |  |

|   |    | <b>1</b> 0 | 0  | 0   | 1  |    |    |     | -72 dB              |  |

|   |    | 1          | 1  | 1   | 1  | Х  | Х  | Х   | Mute                |  |

Table 13. Speaker attenuation selection

16/21

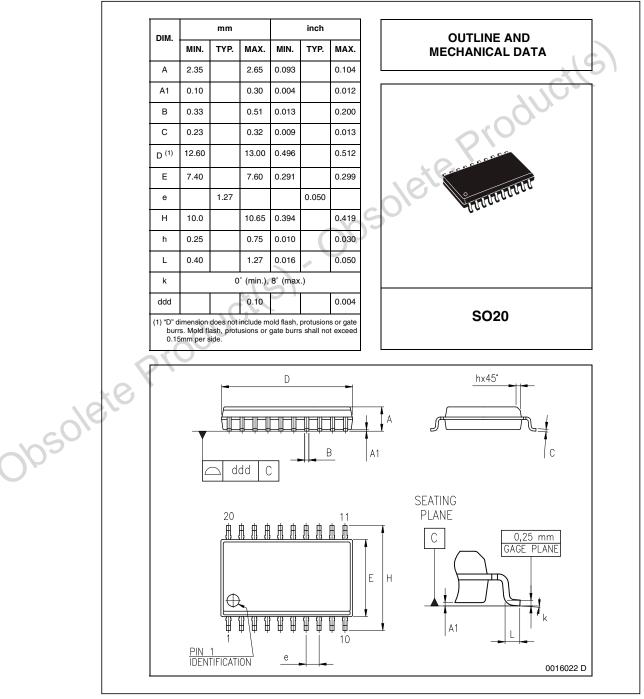

# 8 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK<sup>®</sup> packages, depending on their level of environmental compliance. ECOPACK<sup>®</sup> specifications, grade definitions and product status are available at: *www.st.com*. ECOPACK<sup>®</sup> is an ST trademark.

Figure 25. SO20 mechanical data & package dimensions

# 9 Revision history

### Table 14. Document revision history

|        | Date        | Revision | Changes                                                                                                                                                               |

|--------|-------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        | 03-Sep-2014 | 5        | Removed DIP20 package option<br>Updated <i>Table 1: Device summary</i><br>Revised document presentation along with minor textual<br>updates and modification of title |

| 005018 | te Prodi    | ucils    | absolete Product(s)                                                                                                                                                   |

20/21

#### IMPORTANT NOTICE - PLEASE READ CAREFULLY

obsolete Product(s)

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2014 STMicroelectronics – All rights reserved