# LPS27HHTW

## Datasheet

# MEMS pressure sensor: 260-1260 hPa absolute digital output barometer with embedded temperature sensor in water-resistant package

Pressure sensor with water-resistant package

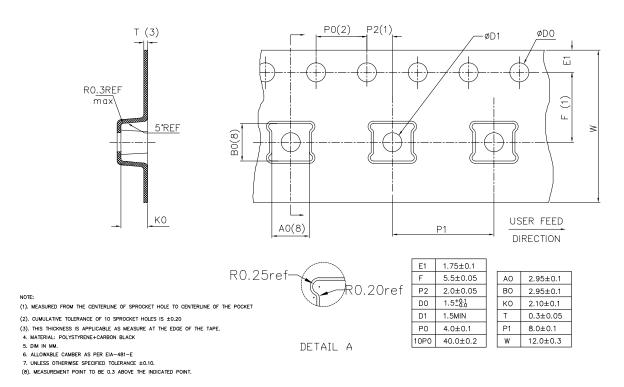

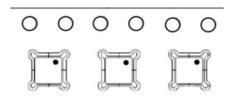

CCLGA 10L 2.7 x 2.7 x 1.7 mm

| / |  |  |

|---|--|--|

|   |  |  |

|   |  |  |

- 260 to 1260 hPa absolute pressure range

- Current consumption down to 4 µA

- Absolute pressure accuracy: 0.5 hPa

Potting gel and grounded metal cap

- Low pressure sensor noise: 0.7 Pa

- Temperature accuracy: ±1.5 °C

- Embedded temperature compensation

- 24-bit pressure data output

- ODR from 1 Hz to 200 Hz

- SPI, I<sup>2</sup>C or MIPI I3C<sup>SM</sup> interfaces

- Embedded FIFO

**Features**

- Interrupt functions: Data-Ready, FIFO flags, pressure thresholds

- Supply voltage: 1.7 to 3.6 V

- ECOPACK lead-free compliant

## **Applications**

- Altimeters and barometers for portable devices

- **GPS** applications

- Weather station equipment

- Sport watches

- e-cigarettes

- Water depth monitoring

- Gas metering

# **Description**

lectronics sales office

The LPS27HHTW is an ultra-compact piezoresistive absolute pressure sensor which functions as a digital output barometer. The device also embeds a temperature sensor to monitor ambient temperature. The LPS27HHTW comprises a sensing element and an IC interface which communicates through I<sup>2</sup>C, MIPI I3C<sup>SM</sup> or SPI from the sensing element to the application.

The sensing element, which detects absolute pressure, consists of a suspended membrane manufactured using a dedicated process developed by ST.

The LPS27HHTW is available in a ceramic LGA package with metal lid. It is guaranteed to operate over a temperature range extending from -40 °C to +85 °C. The package is holed to allow external pressure to reach the sensing element. Gel inside the IC protects the electrical components from water and the metal cap is grounded electrically for better ESD robustness.

| Product status link   |              |  |  |  |

|-----------------------|--------------|--|--|--|

| LPS27HHTW             |              |  |  |  |

| Product summary       |              |  |  |  |

| Order code            | LPS27HHTWTR  |  |  |  |

| Temp. range [°C]      | -40 to +85°C |  |  |  |

| Package               | CCLGA-10L    |  |  |  |

| Packing Tape and reel |              |  |  |  |

|                       | *<br>        |  |  |  |

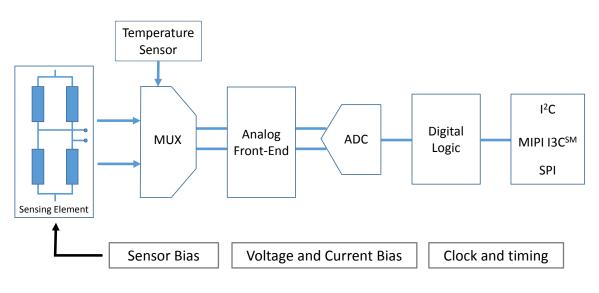

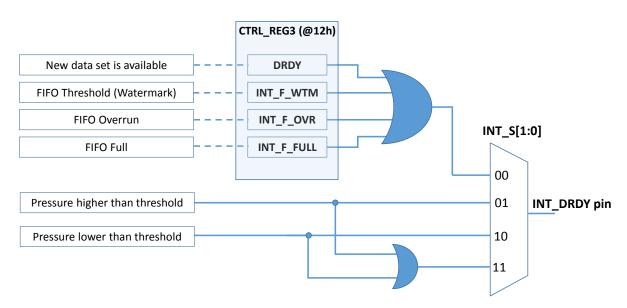

# 1 Block diagrams

57

### Figure 2. Digital logic

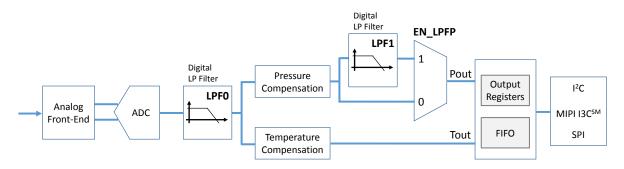

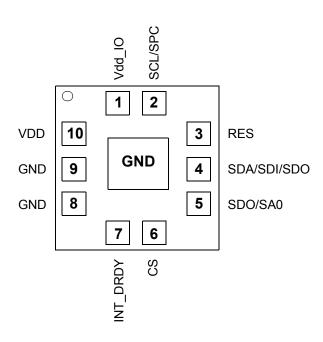

# 2 Pin description

57

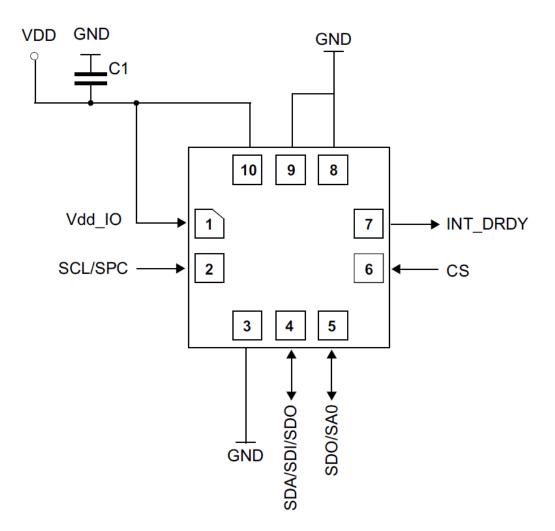

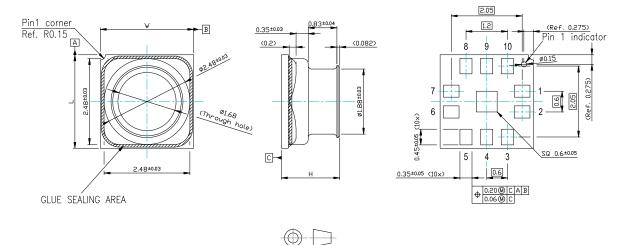

### Figure 3. Pin connections (bottom view)

### Table 1. Pin description

| Pin number | Name       | Function                                                                               |

|------------|------------|----------------------------------------------------------------------------------------|

| 1          | Vdd_IO     | Power supply for I/O pins                                                              |

| 2          | SCL        | I <sup>2</sup> C / MIPI I3C <sup>SM</sup> serial clock (SCL)                           |

| 2          | SPC        | SPI serial port clock (SPC)                                                            |

| 3          | Reserved   | Connect to GND                                                                         |

|            | SDA        | I <sup>2</sup> C / MIPI I3C <sup>SM</sup> serial data (SDA)                            |

| 4          | SDI        | 4-wire SPI serial data input (SDI)                                                     |

|            | SDI/SDO    | 3-wire serial data input/output (SDI/SDO)                                              |

|            | SDO        | 4-wire SPI serial data output (SDO)                                                    |

| 5          | SDO<br>SA0 | I <sup>2</sup> C least significant bit of the device address (SA0)                     |

|            | OAU        | MIPI I3C <sup>SM</sup> least significant bit of the static address (SA0)               |

|            |            | SPI enable                                                                             |

| 6          | CS         | I <sup>2</sup> C and MIPI I3C <sup>SM</sup> / SPI mode selection                       |

| 0          | 00         | (1: SPI idle mode / I <sup>2</sup> C and MIPI I3C <sup>SM</sup> communication enabled; |

|            |            | 0: SPI communication mode / I <sup>2</sup> C and MIPI I3C <sup>SM</sup> disabled)      |

| 7          | INT_DRDY   | Interrupt or Data-Ready                                                                |

| 8          | GND        | 0 V supply                                                                             |

| 9          | GND        | 0 V supply                                                                             |

| 10         | VDD        | Power supply                                                                           |

## 3.1 Mechanical characteristics

57

VDD = 1.8 V, T = 25  $^{\circ}$ C, unless otherwise noted.

#### Table 2. Pressure and temperature sensor characteristics

| Symbol              | Parameter                                 | Test condition                        | Min. | Typ. <sup>(1)</sup>                     | Max. | Unit     |

|---------------------|-------------------------------------------|---------------------------------------|------|-----------------------------------------|------|----------|

| Pressure sen        | sor characteristics                       |                                       |      |                                         |      |          |

| PT <sub>op</sub>    | Operating temperature range               |                                       | -40  |                                         | +85  | °C       |

| Pop                 | Operating pressure range                  |                                       | 260  |                                         | 1260 | hPa      |

| P <sub>bits</sub>   | Pressure output data                      |                                       |      | 24                                      |      | bits     |

| P <sub>sens</sub>   | Pressure sensitivity                      |                                       |      | 4096                                    |      | LSB/hPa  |

| P <sub>AccRel</sub> | Relative accuracy over pressure (2)       | P= 800 - 1100 hPa, T = 25 °C          |      | ±0.025                                  |      | hPa      |

| D                   |                                           | P = 860 ~ 1160 hPa, T = 25 ~ 65°C     |      | ±0.5                                    |      | h D -    |

| P <sub>AccT</sub>   | Absolute accuracy over temperature        | P = 260 ~ 1260 hPa, T = 0 ~ 65 °C     |      | ±1                                      |      | hPa      |

| P <sub>noise</sub>  | RMS pressure sensing noise <sup>(3)</sup> | with embedded filter and at T = 25 °C |      | 0.007                                   |      | hPa RMS  |

| ODR <sub>Pres</sub> | Pressure output data rate (4)             |                                       |      | 1<br>10<br>25<br>50<br>75<br>100<br>200 |      | Hz       |

| тсо                 | Temperature coefficient offset            | P = 860 ~ 1160 hPa, T = -20 ~ +65 °C  |      | 0.75                                    |      | Pa/°C    |

| P_longterm          | Pressure accuracy, long-term stability    |                                       |      | 1                                       |      | hPa/year |

| P_drift             | Soldering drift                           |                                       |      | ±0.5                                    |      | hPa      |

| Temperature s       | sensor characteristics                    |                                       |      | 1                                       | 1    |          |

| Т <sub>ор</sub>     | Operating temperature range               |                                       | -40  |                                         | +85  | °C       |

| T <sub>acc</sub>    | Temperature absolute accuracy             | 25 ~ 65 °C                            |      | ±1.5                                    |      | °C       |

| T <sub>sens</sub>   | Temperature sensitivity                   |                                       |      | 100                                     |      | LSB/°C   |

| ODR <sub>T</sub>    | Temperature output data rate              |                                       |      | 1<br>10<br>25<br>50<br>75<br>100        |      | Hz       |

1. Typical specifications are not guaranteed.

2. By design, the typ. value is defined based characterization data with 10 hPa pressure interval.

3. Pressure noise RMS evaluated in a controlled environment, based on the average standard deviation of 50 measurements with LOW\_NOISE\_EN = 1, EN\_LPFP = 1, LPFP\_CFG = 1.

4. Output data rate is configured acting on ODR[2:0] in CTRL\_REG1 (10h).

# 3.2 Electrical characteristics

VDD = 1.8 V, T = 25  $^{\circ}$ C, unless otherwise noted.

### Table 3. Electrical characteristics

| Symbol | Parameter                         | Test condition                 | Min. | Typ. <sup>(1)</sup> | Max.    | Unit |

|--------|-----------------------------------|--------------------------------|------|---------------------|---------|------|

| VDD    | Supply voltage                    |                                | 1.7  |                     | 3.6     | V    |

| Vdd_IO | IO supply voltage                 |                                | 1.7  |                     | Vdd+0.1 | V    |

| ldd    |                                   | @ ODR 1 Hz<br>LOW_NOISE_EN = 0 |      | 4                   |         |      |

| laa    | Supply current                    | @ ODR 1 Hz<br>LOW_NOISE_EN = 1 |      | 12                  |         | μA   |

| lddPdn | Supply current in power-down mode |                                |      | 0.9                 |         | μA   |

1. Typical specifications are not guaranteed.

### Table 4. DC characteristics

| Symbol     | Parameter                                 | Condition | Min.      | Тур. | Max.      | Unit |

|------------|-------------------------------------------|-----------|-----------|------|-----------|------|

| DC input c | haracteristics                            |           |           |      |           |      |

| Vil        | Low-level input voltage (Schmitt buffer)  |           |           |      | 0.3 * Vdd | V    |

| Vih        | High-level input voltage (Schmitt buffer) |           | 0.7 * Vdd |      |           | V    |

| DC output  | characteristics                           |           |           |      |           |      |

| Vol        | Low-level output voltage                  |           |           |      | 0.2       | V    |

| Voh        | High-level output voltage                 |           | Vdd - 0.2 |      |           | V    |

# 3.3 Communication interface characteristics

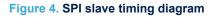

## 3.3.1 SPI - serial peripheral interface

57

Subject to general operating conditions for Vdd and  $\ensuremath{\mathsf{T}_{\mathsf{OP}}}$  .

| Symbol               | Parameter               | Value <sup>(1)</sup> |                   | Unit |

|----------------------|-------------------------|----------------------|-------------------|------|

| Symbol               |                         | Min.                 | Max.              |      |

| t <sub>c(SPC)</sub>  | SPI clock cycle         | 100                  |                   | ns   |

| f <sub>c(SPC)</sub>  | SPI clock frequency     |                      | 10 <sup>(2)</sup> | MHz  |

| t <sub>su(CS)</sub>  | CS setup time           | 6                    |                   |      |

| t <sub>h(CS)</sub>   | CS hold time            | 8                    |                   | -    |

| t <sub>su(SI)</sub>  | SDI input setup time    | 5                    |                   | -    |

| t <sub>h(SI)</sub>   | SDI input hold time     | 15                   |                   | ns   |

| t <sub>v(SO)</sub>   | SDO valid output time   |                      | 50                | -    |

| t <sub>h(SO)</sub>   | SDO output hold time    | 9                    |                   | 1    |

| t <sub>dis(SO)</sub> | SDO output disable time |                      | 50                |      |

#### Table 5. SPI slave timing values

1. Values are guaranteed at 10 MHz clock frequency for SPI with both 4 and 3 wires, based on characterization results, not tested in production.

2. Recommended to set max SPI clock 8 MHz to ≤50 Hz ODR.

Note: Measurement points are done at 0.3.Vdd\_IO and 0.7.Vdd\_IO for both ports.

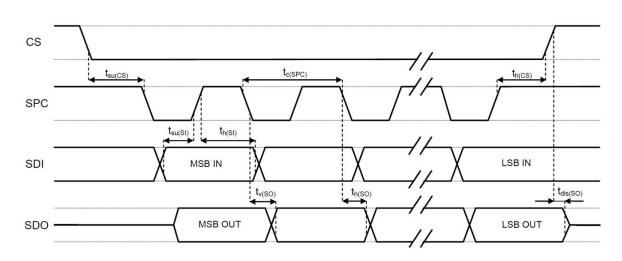

### 3.3.2 I<sup>2</sup>C - inter-IC control interface

Subject to general operating conditions for Vdd and  $T_{\mbox{\scriptsize OP}}.$

| Symbol                | Parameter                                      | I <sup>2</sup> C standa | ard mode <sup>(1)</sup> | d mode <sup>(1)</sup> I <sup>2</sup> C fast mode <sup>(1)</sup> | Unit    |     |

|-----------------------|------------------------------------------------|-------------------------|-------------------------|-----------------------------------------------------------------|---------|-----|

|                       | Farameter                                      | Min.                    | Max                     | Min.                                                            | n. Max. |     |

| f <sub>(SCL)</sub>    | SCL clock frequency                            | 0                       | 100                     | 0                                                               | 400     | kHz |

| t <sub>w(SCLL)</sub>  | SCL clock low time                             | 4.7                     |                         | 1.3                                                             |         |     |

| t <sub>w(SCLH)</sub>  | SCL clock high time                            | 4.0                     |                         | 0.6                                                             |         | μs  |

| t <sub>su(SDA)</sub>  | SDA setup time                                 | 250                     |                         | 100                                                             |         | ns  |

| t <sub>h(SDA)</sub>   | SDA data hold time                             | 0                       | 3.45                    | 0                                                               | 0.9     | μs  |

| t <sub>h(ST)</sub>    | START condition hold time                      | 4                       |                         | 0.6                                                             |         |     |

| t <sub>su(SR)</sub>   | Repeated START condition setup time            | 4.7                     |                         | 0.6                                                             |         |     |

| t <sub>su(SP)</sub>   | STOP condition setup time                      | 4                       |                         | 0.6                                                             |         | μs  |

| t <sub>w(SP:SR)</sub> | Bus free time between STOP and START condition | 4.7                     |                         | 1.3                                                             |         |     |

### Table 6. I<sup>2</sup>C slave timing values

1. Data based on standard I<sup>2</sup>C protocol requirement, not tested in production.

### Figure 5. I<sup>2</sup>C slave timing diagram

Note: Measurement points are done at 0.3·Vdd\_IO and 0.7·Vdd\_IO for both ports.

## 3.4 Absolute maximum ratings

Stress above those listed as "Absolute maximum ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device under these conditions is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

| Symbol               | Ratings                            | Maximum value       | Unit |

|----------------------|------------------------------------|---------------------|------|

| Vdd                  | Supply voltage                     | -0.3 to 4.8         | V    |

| Vdd_IO               | I/O pins supply voltage            | -0.3 to 4.8         | V    |

| Vin                  | Input voltage on any control pin   | -0.3 to Vdd_IO +0.3 | V    |

| P <sub>(water)</sub> | Overpressure                       | 1                   | MPa  |

| T <sub>STG</sub>     | Storage temperature range          | -40 to +125         | °C   |

| ESD                  | Electrostatic discharge protection | 2 (HBM)             | kV   |

#### Table 7. Absolute maximum ratings

Note: Supply voltage on any pin should never exceed 4.8 V.

This device is sensitive to mechanical shock, improper handling can cause permanent damage to the part.

This device is sensitive to electrostatic discharge (ESD), improper handling can cause permanent damage to the part.

# 4 Functionality

The LPS27HHTW is a high-resolution, digital output pressure sensor packaged in a CCLGA package with metal lid. The complete device includes a sensing element based on a piezoresistive Wheatstone bridge approach, and an IC interface which communicates a digital signal from the sensing element to the application.

## 4.1 Sensing element

An ST proprietary process is used to obtain a silicon membrane for MEMS pressure sensors. When pressure is applied, the membrane deflection induces an imbalance in the Wheatstone bridge piezoresistances whose output signal is converted by the IC interface.

### 4.2 IC interface

The complete measurement chain is composed of a low-noise amplifier which converts the resistance unbalance of the MEMS sensors (pressure and temperature) into an analog voltage using an analog-to-digital converter.

The pressure and temperature data may be accessed through an I<sup>2</sup>C/MIPI I3C<sup>SM</sup>/SPI interface thus making the device particularly suitable for direct interfacing with a microcontroller.

The LPS27HHTW features a Data-Ready signal which indicates when a new set of measured pressure and temperature data are available, thus simplifying data synchronization in the digital system that uses the device.

## 4.3 Factory calibration

The trimming values are stored inside the device in a non-volatile structure. When the device is turned on, the trimming parameters are downloaded into the registers to be employed during the normal operation which allows the device to be used without requiring any further calibration.

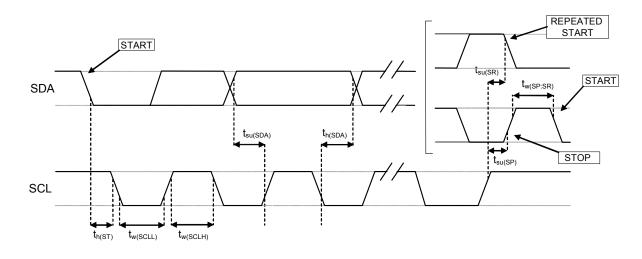

## 4.4 Device structure

57

The LPS27HHTW has a unique cylindrical package solution with a full metal lid assembled on ceramic substrate and this cylindrical package provides an easy assembly with O-rings in the end user's application.

This structure (Figure 6) is designed and verified to resist water pressure up to 10 ATM and the potting gel in the LPS27HHTW has been proven to protect electronic components from long-term exposure to harsh environments such as water mixed with chlorine, bromine, commercial washing detergent and fuels, solvents and chemicals. It also provides excellent low-stress encapsulation performance for sensitive electronic components from severe environmental conditions such as high temperature and humidity, refer to the properties of the gel which are given in the following table.

#### Table 8. Potting gel properties

| Properties                                 | Potting gel        |

|--------------------------------------------|--------------------|

| Permeability g/m <sup>2</sup> ·24 hr       | 7                  |

| Hardness (penetration) based on ASTM D1403 | 70                 |

| Ultra-low Young's modulus                  | Less than 0.01 GPa |

| TCE (Thermal Coefficient of Expansion)     | 300 ppm/°C         |

## 4.5 Interpreting pressure readings

The pressure data are stored in 3 registers: PRESS\_OUT\_H (2Ah), PRESS\_OUT\_L (29h), and PRESS\_OUT\_XL (28h). The value is expressed as a 24-bit signed number (in 2's complement).

To obtain the pressure in hPa, take the complete 24-bit word and then divide by the sensitivity 4096 LSB/ hPa. This same interpretation is applied to pressure readings when FIFO is enabled and the pressure data are stored in 3 registers: FIFO\_DATA\_OUT\_PRESS\_XL (78h), FIFO\_DATA\_OUT\_PRESS\_L (79h), and FIFO\_DATA\_OUT\_PRESS\_H (7Ah).

#### Figure 7. Pressure readings

| Pressure Value (LSB) = PRESS_OUT_H (2Ah) & PRESS_OUT_L (29h) & PRESS_OUT_XL (28h) = 3FF58Dh = 4191629 LSB (signed decimal) | (1) |

|----------------------------------------------------------------------------------------------------------------------------|-----|

| $Pressure\left(hPa\right) = \frac{Pressure\ Value\ (LSB)}{Sensitivity} = \frac{4191629\ LSB}{4096\ LSB/hPA} = \ 1023\ hPa$ | (2) |

### 4.6 Interpreting temperature readings

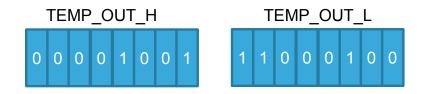

The temperature data are stored in 2 registers: TEMP\_OUT\_H (2Ch) and TEMP\_OUT\_L (2Bh). The value is expressed as 2's complement. To obtain the temperature in °C, take the two's complement of the complete 16-bit word and then divide by the sensitivity 100 LSB/°C. This same interpretation is applied to temperature readings when FIFO is enabled and the temperature data are stored in 2 registers: FIFO\_DATA\_OUT\_TEMP\_H (7Ch) and FIFO\_DATA\_OUT\_TEMP\_L (7Bh).

#### Figure 8. Temperature readings

Temperature Value (LSB) = TEMP\_OUT\_H (2Ch) & TEMP\_OUT\_L (2Bh) = 09C4 = 2500 LSB (decimal signed)

Temperature (°C) =  $\frac{\text{Temperature Value (LSB)}}{\text{Sensitivity}} = \frac{2500 \text{ LSB}}{100 \text{ LSB/°C}} = 25.00^{\circ}\text{C}$

# 5 FIFO

The LPS27HHTW embeds 128 slots of 40-bit data FIFO to store the pressure and temperature output values. This allows consistent power saving for the system, since the host processor does not need to continuously poll data from the sensor, but it can wake up only when needed and burst the significant data out from the FIFO. This buffer can work according to six different modes:

- Bypass mode

- FIFO mode

- Continuous (Dynamic-Stream) mode

- Continuous (Dynamic-Stream)-to-FIFO mode

- Bypass-to-Continuous (Dynamic-Stream)

- Bypass-to-FIFO mode

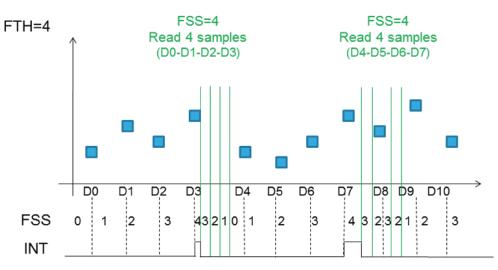

The FIFO buffer is enabled when a configuration different from all bits '0' are written in FIFO\_CTRL (13h) and each mode is selected by the TRIG\_MODES bit and F\_MODE[1:0] bits in FIFO\_CTRL (13h). Programmable FIFO threshold status, FIFO overrun events and the number of unread samples stored are available in the FIFO\_STATUS1 (25h) and FIFO\_STATUS2 (26h) registers and can be set to generate dedicated interrupts on the INT\_DRDY pad using the CTRL\_REG3 (12h) register.

FIFO\_STATUS2 (26h)(FIFO\_WTM\_IA) goes to '1' when the number of unread samples (FIFO\_STATUS1 (25h) (FSS[7:0]) is greater than or equal to WTM[6:0] in FIFO\_WTM (14h). If FIFO\_WTM (14h)(WTM[6:0]) is equal to 0, FIFO\_STATUS2 (26h)(FIFO\_WTM\_IA) stays at '0'.

FIFO\_STATUS2 (26h)(FIFO\_OVR\_IA) is equal to '1' if a FIFO slot is overwritten.

FIFO\_STATUS1 (25h)(FSS[7:0]) contains stored data levels of unread samples; when FSS[7:0] is equal to '00000000', FIFO is empty; when FSS[7:0] is equal to '10000000', FIFO is full and the unread samples are 128.

57

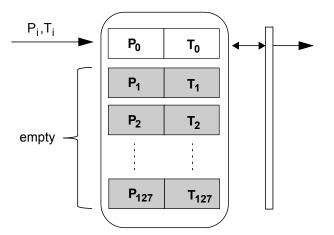

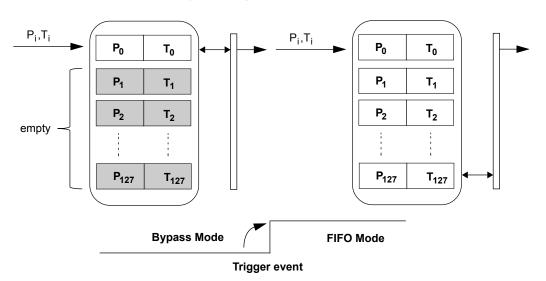

In Bypass mode (FIFO\_CTRL (13h)(TRIG\_MODES and F\_MODE[1:0] = '000' or '100'), the FIFO is not operational and it remains empty.

Switching to Bypass mode is also used to reset the FIFO. Passing through Bypass mode is mandatory when switching between different FIFO buffer operating modes.

As described in the next figure, for each channel only the first address is used. When new data is available, the older data is overwritten.

#### Figure 9. Bypass mode

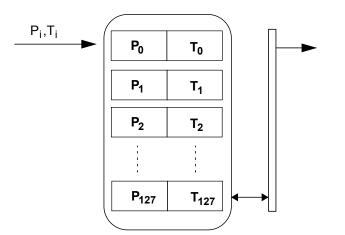

### 5.2 FIFO mode

57

In FIFO mode (FIFO\_CTRL (13h)(TRIG\_MODES and F\_MODE[1:0] = '001') data from the output PRESS\_OUT\_XL (28h), PRESS\_OUT\_L (29h), PRESS\_OUT\_H (2Ah), TEMP\_OUT\_L (2Bh), and TEMP\_OUT\_H (2Ch) are stored in the FIFO until it is full.

To reset FIFO content, in order to select Bypass mode the value '000' must be written in FIFO\_CTRL (13h) (TRIG\_MODE & F\_MODE[1:0]). After this reset command it is possible to restart FIFO mode by writing the value '001' in FIFO\_CTRL (13h)(TRIG\_MODE & F\_MODE[1:0]).

The FIFO buffer memorizes 128 levels of data, but the depth of the FIFO can be resized/reduced by setting the FIFO\_CTRL (13h)(STOP\_ON\_WTM) bit. If the STOP\_ON\_WTM bit is set to '1', FIFO depth is limited to FIFO\_WTM (14h)(WTM[6:0]) data.

Figure 10. FIFO mode

# 5.3 Continuous (Dynamic-Stream) mode

In Continuous (Dynamic-Stream) mode (FIFO\_CTRL (13h)(TRIG\_MODES and F\_MODE[1:0] = '011') after emptying the FIFO, the first new sample that arrives becomes the first to be read in a subsequent read burst. In this way, the number of new data available in FIFO does not depend on the previous read.

In Continuous (Dynamic-Stream) mode FIFO\_STATUS1 (25h)(FSS[7:0]) is the number of new pressure and temperature samples available in the FIFO buffer.

Continuous (Dynamic-Stream) is intended to be used to read FIFO\_STATUS1 (25h)(FSS[7:0]) samples when it is not possible to guarantee reading data within 1/ODR time period.

Also, a FIFO threshold interrupt on the INT\_DRDY pad through CTRL\_REG3 (12h)(INT\_F\_WTM) can be enabled in order to read data from the FIFO and leave free memory slots for incoming data.

#### Figure 11. Continuous (Dynamic-Stream) mode

## 5.4 Bypass-to-FIFO mode

In Bypass-to-FIFO mode (FIFO\_CTRL (13h)(TRIG\_MODES and F\_MODE[1:0] = '101'), FIFO behavior switches when the INT\_SOURCE (24h)(IA) bit rises for the first time. When the INT\_SOURCE (24h)(IA) bit is equal to '0', FIFO behaves like in Bypass mode. Once the INT\_SOURCE (24h)(IA) bit rises to '1', FIFO behavior switches and keeps behaving like in FIFO mode.

An interrupt generator has to be set to the desired configuration through INTERRUPT\_CFG (0Bh).

#### Figure 12. Bypass-to-FIFO mode

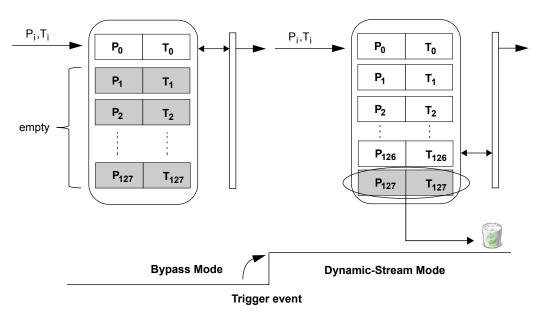

# 5.5 Bypass-to-Continuous (Dynamic-Stream) mode

57

In Bypass-to-Continuous (Dynamic-Stream) mode (FIFO\_CTRL (13h)(TRIG\_MODES and F\_MODE[1:0] = '110'), FIFO operates in Bypass mode until it switches to Continuous (Dynamic-Stream) mode behavior when INT\_SOURCE (24h)(IA) rises to '1', then FIFO behavior keeps behaving like in Continuous (Dynamic-Stream) mode.

An interrupt generator has to be set to the desired configuration through INTERRUPT\_CFG (0Bh).

#### Figure 13. Bypass-to-Continuous (Dynamic-Stream) mode

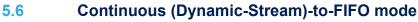

57/

In Continuous (Dynamic-Stream)-to-FIFO mode (FIFO\_CTRL (13h)(TRIG\_MODES and F\_MODE[1:0] = '111'), data are stored in FIFO and FIFO operates in Continuous (Dynamic-Stream) mode behavior until it switches to FIFO mode behavior when INT\_SOURCE (24h)(IA) rises to '1'.

An interrupt generator has to be set to the desired configuration through INTERRUPT\_CFG (0Bh).

## 5.7 Retrieving data from FIFO

FIFO data is read through FIFO\_DATA\_OUT\_PRESS (78h, 79h and 7Ah) and FIFO\_DATA\_OUT\_TEMP (7Bh, 7Ch).

The read address is automatically updated by the device and it rolls back to 78h when register 7Ch is reached. In order to read all FIFO levels in a multiple byte read, 640 bytes (5 output registers by 128 levels) must be read.

# 6 Application hints

57/

The device power supply must be provided through the VDD line; a power supply decoupling capacitor C1 (100 nF) must be placed as near as possible to the supply pads of the device. The C1 capacitor can be tied to VDD and Vdd\_IO, but it is recommended to use 2 capacitors, one on each VDD and Vdd\_IO line, in case VDD are Vdd\_IO are separate. Depending on the application, an additional capacitor of 4.7  $\mu$ F could be placed on the VDD line.

The functionality of the device and the measured data outputs are selectable and accessible through the I<sup>2</sup>C, MIPI I3C<sup>SM</sup>, SPI interface. When using the I<sup>2</sup>C and MIPI I3C<sup>SM</sup>, CS must be tied to Vdd\_IO.

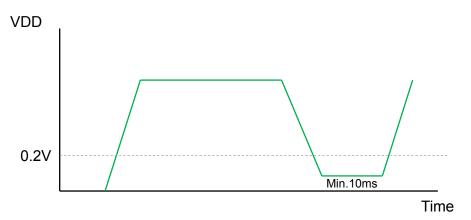

All the voltage and ground supplies must be present at the same time to have proper behavior of the IC (refer to Figure 15). It is possible to remove VDD while maintaining Vdd\_IO without blocking the communication bus, in this condition the measurement chain is powered off.

Note: To guarantee proper power-off of the device, it is recommended to maintain the duration of the VDD line to GND for at least 10 ms.

- •

- VDD Rising / Falling time : 10  $\mu s$  ~ 100 ms VDD must be lower than 0.2 V for at least 10 ms during power-off sequence for correct POR .

#### **Soldering information** 6.1

The CCLGA package is compliant with the ECOPACK standard and it is qualified for soldering heat resistance according to JEDEC J-STD-020.

# 7 Digital interfaces

### 7.1 Serial interfaces

The registers embedded in the LPS27HHTW may be accessed through either the I<sup>2</sup>C, MIPI I3C<sup>SM</sup> or SPI serial interfaces. The latter may be SW configured to operate either in 3-wire or 4-wire interface mode. The serial interfaces are mapped onto the same pads. To select/exploit the I<sup>2</sup>C interface, the CS line must be tied high (i.e. connected to Vdd\_IO).

| Pin name | Pin description                                                                                                    |

|----------|--------------------------------------------------------------------------------------------------------------------|

|          | SPI enable                                                                                                         |

| CS       | I <sup>2</sup> C/SPI mode selection                                                                                |

|          | (1: SPI idle mode / I <sup>2</sup> C communication enabled; 0: SPI communication mode / I <sup>2</sup> C disabled) |

| SCL/SPC  | I <sup>2</sup> C serial clock (SCL)                                                                                |

| SUL/SPU  | SPI serial port clock (SPC)                                                                                        |

| SDA      | I <sup>2</sup> C serial data (SDA)                                                                                 |

| SDI      | 4-wire SPI serial data input (SDI)                                                                                 |

| SDI/SDO  | 3-wire serial data input /output (SDI/SDO)                                                                         |

| SDO      | SPI serial data output (SDO)                                                                                       |

| SA0      | I <sup>2</sup> C less significant bit of the device address (SA0)                                                  |

#### Table 9. Serial interface pin description

### 7.2 I<sup>2</sup>C serial interface (CS = high)

The LPS27HHTW I<sup>2</sup>C is a bus slave. The I<sup>2</sup>C is employed to write data into registers whose content can also be read back.

The relevant I<sup>2</sup>C terminology is given in the following table.

#### Table 10. I<sup>2</sup>C terminology

| Term        | Description                                                                              |

|-------------|------------------------------------------------------------------------------------------|

| Transmitter | The device which sends data to the bus                                                   |

| Receiver    | The device which receives data from the bus                                              |

| Master      | The device which initiates a transfer, generates clock signals and terminates a transfer |

| Slave       | The device addressed by the master                                                       |

There are two signals associated with the I<sup>2</sup>C bus: the serial clock line (SCL) and the serial data line (SDA). The latter is a bidirectional line used for sending and receiving the data to/from the interface. Both lines have to be connected to Vdd\_IO through pull-up resistors.

The I<sup>2</sup>C interface is compliant with fast mode (400 kHz) I<sup>2</sup>C standards as well as with the normal mode.

### 7.2.1 I<sup>2</sup>C operation

The transaction on the bus is started through a START (ST) signal. A start condition is defined as a HIGH-to-LOW transition on the data line while the SCL line is held HIGH. After the master has transmitted this, the bus is considered busy. The next data byte transmitted after the start condition contains the address of the slave in the first 7 bits and the eighth bit tells whether the master is receiving data from the slave or transmitting data to the slave. When an address is sent, each device in the system compares the first seven bits after a start condition with its address. If they match, the device considers itself addressed by the master.

The 7-bit slave address (SAD) associated to the LPS27HHTW is 101110xb. The **SDO/SA0** pad can be used to modify the less significant bit of the device address. If the SA0 pad is connected to voltage supply, LSb is '1' (7-bit address 1011101b=5Dh), otherwise if the SA0 pad is connected to ground, the LSb value is '0' (7-bit address 1011100b=5Ch). This solution permits connecting and addressing two different LPS27HHTW devices to the same I<sup>2</sup>C lines.

Data transfer with acknowledge is mandatory. The transmitter must release the SDA line during the acknowledge pulse. The receiver must then pull the data line LOW so that it remains stable low during the HIGH period of the acknowledge clock pulse. A receiver which has been addressed is obliged to generate an acknowledge after each byte of data received.

The I<sup>2</sup>C embedded inside the ASIC behaves like a slave device and the following protocol must be adhered to. After the start condition (ST) a slave address is sent, once a slave acknowledge has been returned (SAK), an 8-bit sub-address will be transmitted (SUB): the 7 LSB represent the actual register address while the MSB has no meaning. The IF\_ADD\_INC bit in CTRL\_REG2 (11h) enables sub-address auto increment (IF\_ADD\_INC is '1' by default), so if IF\_ADD\_INC = '1' the SUB (sub-address) will be automatically increased to allow multiple data read/write.

The slave address is completed with a Read/Write bit. If the bit is '1' (Read), a repeated START (SR) condition must be issued after the two sub-address bytes; if the bit is '0' (Write) the master will transmit to the slave with direction unchanged. Table 11 explains how the SAD+read/write bit pattern is composed, listing all the possible configurations.

#### Table 11. SAD+Read/Write patterns

| Command | SAD[6:1] | SAD[0] = SA0 | R/W | SAD+R/W        |

|---------|----------|--------------|-----|----------------|

| Read    | 101110   | 0            | 1   | 10111001 (B9h) |

| Write   | 101110   | 0            | 0   | 10111000 (B8h) |

| Read    | 101110   | 1            | 1   | 10111011 (BBh) |

| Write   | 101110   | 1            | 0   | 10111010 (BAh) |

#### Table 12. Transfer when master is writing one byte to slave

| Master | ST | SAD + W |     | SUB |     | DATA |     | SP |

|--------|----|---------|-----|-----|-----|------|-----|----|

| Slave  |    |         | SAK |     | SAK |      | SAK |    |

#### Table 13. Transfer when master is writing multiple bytes to slave

| Master | ST | SAD + W |     | SUB |     | DATA |     | DATA |     | SP |

|--------|----|---------|-----|-----|-----|------|-----|------|-----|----|

| Slave  |    |         | SAK |     | SAK |      | SAK |      | SAK |    |

#### Table 14. Transfer when master is receiving (reading) one byte of data from slave

| Master | ST | SAD + W |     | SUB |     | SR | SAD + R |     |      | NMAK | SP |

|--------|----|---------|-----|-----|-----|----|---------|-----|------|------|----|

| Slave  |    |         | SAK |     | SAK |    |         | SAK | DATA |      |    |

| Table 15. Transfer when meeter is receiving | (reading) multiple bytes of data from alove |

|---------------------------------------------|---------------------------------------------|

| Table 15. Transfer when master is receiving | (reading) multiple bytes of data nom slave  |

| Master | ST | SAD+W |     | SUB |     | SR | SAD+R |     |      | MAK |      | MAK |      | NMAK | SP |

|--------|----|-------|-----|-----|-----|----|-------|-----|------|-----|------|-----|------|------|----|

| Slave  |    |       | SAK |     | SAK |    |       | SAK | DATA |     | DATA |     | DATA |      |    |

Data are transmitted in byte format (DATA). Each data transfer contains 8 bits. The number of bytes transferred per transfer is unlimited. Data is transferred with the most significant bit (MSb) first. If a slave receiver does not acknowledge the slave address (i.e. it is not able to receive because it is performing some real-time function), the data line must be kept HIGH by the slave. The master can then abort the transfer. A LOW-to-HIGH transition on the SDA line while the SCL line is HIGH is defined as a STOP condition. Each data transfer must be terminated by the generation of a STOP (SP) condition.

In the presented communication format MAK is Master acknowledge and NMAK is no master acknowledge.

### 7.3 SPI bus interface (CS = low)

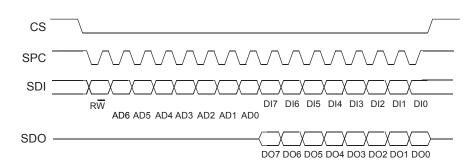

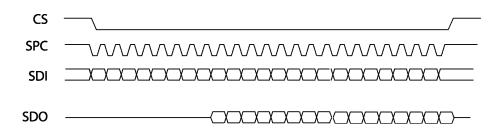

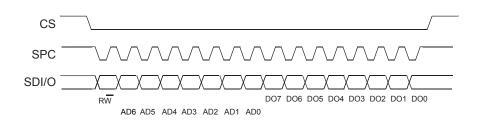

The LPS27HHTW SPI is a bus slave. The SPI allows writing to and reading from the registers of the device. The serial interface interacts with the application using 4 wires: **CS**, **SPC**, **SDI** and **SDO**.

#### Figure 17. Read and write protocol

**CS** is the serial port enable and it is controlled by the SPI master. It goes low at the start of the transmission and returns to high at the end. **SPC** is the serial port clock and it is controlled by the SPI master. It is stopped high when **CS** is high (no transmission). **SDI** and **SDO** are respectively the serial port data input and output. Those lines are driven at the falling edge of **SPC** and should be captured at the rising edge of **SPC**.

Both the read register and write register commands are completed in 16 clock pulses or multiples of 8 in the case of multiple read/write bytes. Bit duration is the time between two falling edges of SPC. The first bit (bit 0) starts at the first falling edge of SPC after the falling edge of CS while the last bit (bit 15, bit 23,...) starts at the last falling edge of SPC just before the rising edge of CS.

*bit 0*: RW bit. When 0, the data DI(7:0) is written into the device. When 1, the data DO(7:0) from the device is read. In the latter case, the chip will drive SDO at the start of bit 8.

bit 1-7: address AD(6:0). This is the address field of the indexed register.

*bit 8-15*: data DI(7:0) (write mode). This is the data that is written into the device (MSb first). bit 8-15: data DO(7:0) (read mode). This is the data that is read from the device (MSb first). In multiple read/write commands further blocks of 8 clock periods are added. When the IF\_ADD\_INC bit is 0, the address used to read/write data remains the same for every block. When the IF\_ADD\_INC bit is 1, the address used to read/write data is incremented at every block.

The function and the behavior of SDI and SDO remain unchanged.

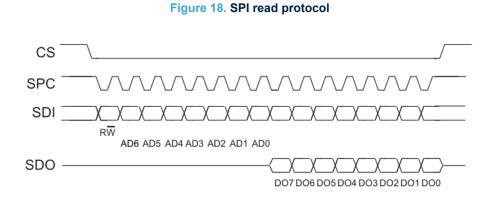

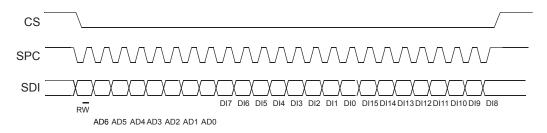

### 7.3.1 SPI read

57/

The SPI read command is performed with 16 clock pulses. The multiple byte read command is performed by adding blocks of 8 clock pulses to the previous one.

*bit 0*: READ bit. The value is 1.

bit 1-7: address AD(6:0). This is the address field of the indexed register.

*bit 8-15*: data DO(7:0) (read mode). This is the data that is read from the device (MSb first). *bit 16-...*: data DO(...-8). Further data in multiple byte reads.

Figure 19. Multiple byte SPI read protocol (2-byte example)

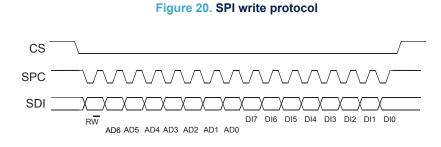

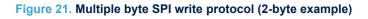

### 7.3.2 SPI write

57/

The SPI write command is performed with 16 clock pulses. The multiple byte write command is performed by adding blocks of 8 clock pulses to the previous one.

*bit 0*: WRITE bit. The value is 0.

*bit* **1-7**: address AD(6:0). This is the address field of the indexed register.

*bit 8-15*: data DI(7:0) (write mode). This is the data that is written in the device (MSb first). *bit 16-...*: data DI(...-8). Further data in multiple byte writes.

### 7.3.3 SPI read in 3-wire mode

A 3-wire mode is entered by setting bit SIM to '1' (SPI serial interface mode selection) in CTRL\_REG1 (10h).

#### Figure 22. SPI read protocol in 3-wire mode

The SPI read command is performed with 16 clock pulses:

bit 0: READ bit. The value is 1.

bit 1-7: address AD(6:0). This is the address field of the indexed register.

*bit 8-15*: data DO(7:0) (read mode). This is the data that is read from the device (MSb first). A multiple read command is also available in 3-wire mode.

# 7.4 MIPI I3C<sup>SM</sup> slave interface

The LPS27HHTW interface includes a MIPI I3C<sup>SM</sup> SDR only slave interface with MIPI I3C<sup>SM</sup> SDR embedded features:

- CCC command

- Direct CCC communication (SET and GET)

- Broadcast CCC communication

- Private communications

- Private read and write for single byte

- Multiple read and write

- In-band interrupt and hot-join requests

## 7.4.1 MIPI I3C<sup>SM</sup> CCC supported commands

The list of MIPI I3C<sup>SM</sup> CCC commands supported by the device is detailed in the following table.

### Table 16. MIPI I3C<sup>SM</sup> CCC commands

| Command   | Command code | Default                                      | Description                                                                        |

|-----------|--------------|----------------------------------------------|------------------------------------------------------------------------------------|

| ENEC      | 0x80 / 0x00  |                                              | Slave activity control (direct and broadcast)                                      |

| RSTDAA    | 0x86 / 0x06  |                                              | Reset the assigned dynamic address (direct and broadcast)                          |

| DISEC     | 0x81/ 0x01   |                                              | Slave activity control (direct and broadcast)                                      |

| ENTAS0    | 0x82 / 0x02  |                                              | Enter activity state (direct and broadcast)                                        |

| ENTAS1    | 0x83 / 0x03  |                                              | Enter activity state (direct and broadcast)                                        |

| ENTAS2    | 0x84 / 0x04  |                                              | Enter activity state (direct and broadcast)                                        |

| ENTAS3    | 0x85 / 0x05  |                                              | Enter activity state (direct and broadcast)                                        |

| SETMWL    | 0x89 / 0x08  | 0x00<br>0x08                                 | Define maximum write length during private write (direct and broadcast)            |

| SETMRL    | 0x8A / 0x09  | 0x00<br>0x10<br>0x04                         | Define maximum read length during private read (direct and broadcast)              |

| SETDASA   | 0x87         |                                              | Assign dynamic address using static address (0x5C/0x5D depending on the SDO level) |

| SETNEWDA  | 0x88         |                                              | Change dynamic address                                                             |

| GETMWL    | 0x8B         | 0x00<br>0x08                                 | Get maximum write length during private write                                      |

| GETMRL    | 0x8C         | 0x00<br>0x10<br>0x04                         | Get maximum read length during private read                                        |

| GETPID    | 0x8D         | 0x02<br>0x08<br>0x00<br>0xB3<br>0x00<br>0x00 | Device ID register                                                                 |

| GETBCR    | 0x8E         | 0x07                                         | Bus characteristics register                                                       |

| GETDCR    | 0x8F         | 0x62                                         | DCR                                                                                |

| GETSTATUS | 0x90         |                                              | Status register                                                                    |

| Command      | Command code | Default | Description                   |  |

|--------------|--------------|---------|-------------------------------|--|

| GETMXDS      | 0x94         | 0x00    | Return max data speed         |  |

| GETMADS 0X94 |              | 0x20    | Telum max uala speeu          |  |

|              |              | 0x07    |                               |  |

| CETYTIME     | 0x99         | 0x04    | Cat evolution information     |  |

| GETXTIME     |              | 0x0A    | Get exchange time information |  |

|              |              | 0x64    |                               |  |

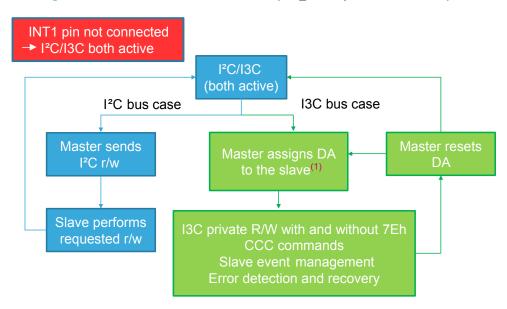

# 7.5 I<sup>2</sup>C/MIPI I3C<sup>SM</sup> coexistence in LPS27HHTW

In the LPS27HHTW, the SDA and SCL lines are common to both I<sup>2</sup>C and MIPI I3C<sup>SM</sup>. The I<sup>2</sup>C bus requires anti-spike filters on the SDA and SCL pins that are not compatible with MIPI I3C<sup>SM</sup> timing.

The device can be connected to both I<sup>2</sup>C and MIPI I3C<sup>SM</sup> or only to the MIPI I3C<sup>SM</sup> bus depending on the connection of the INT1 pin when the device is powered up:

- INT\_DRDY pin floating (internal pull-down): I<sup>2</sup>C/MIPI I3C<sup>SM</sup> both active, see Figure 23

- I<sup>2</sup>C case: INT\_DRDY pin is by default an input with pull-down. If I<sup>2</sup>C is used, INT\_DRDY must be left unconnected or eventually pulled down during device initialization. After power-on, during device configuration, the INT\_DRDY pin can be programmed as an interrupt output pin and it is recommended to set bit I3C\_disable to '1'.

- I3C case: INT\_DRDY pin is by default an input with pull-down. If I3C is used and the INT\_DRDY pin is unconnected, dynamic address assignment must be performed using I<sup>2</sup>C Fast Mode Plus Timing (max 1 MHz clock). After dynamic address assignment, I3C can be used in full speed mode.

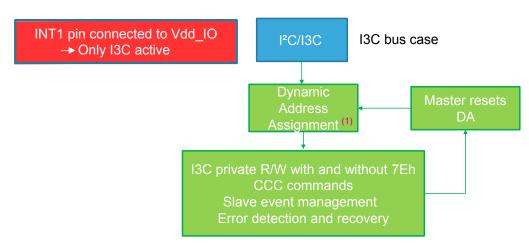

- INT\_DRDY pin connected to Vdd\_IO: only MIPI I3C<sup>SM</sup> active, see Figure 24

- Only I3C: INT\_DRDY pin is by default an input with pull-down. If INT\_DRDY is set to Vdd\_IO, I3C slave is selected and device can be initialized at full speed through the SETDASA command. If the I3C bus is available for more than 10 msec and the device is not yet addressed, a hot join request is performed (SDA line kept to ground from slave) and the master must manage the request. After device address assignment, a private write can be performed to disconnect the INT\_DRDY pull-down.

### Figure 23. I<sup>2</sup>C and MIPI I3C<sup>SM</sup> both active (INT\_DRDY pin not connected)

1. Address assignment (SETDASA) must be performed with I<sup>2</sup>C Fast Mode Plus Timing. When the slave is addressed, the I<sup>2</sup>C slave is disabled and the timing is compatible with MIPI I3C<sup>SM</sup> specifications.

# Figure 24. Only MIPI I3C<sup>SM</sup> active (INT\_DRDY pin connected to Vdd\_IO)

When the slave is MIPI I3C<sup>SM</sup> only, the I<sup>2</sup>C slave is always disabled. The address can be assigned using MIPI I3C<sup>SM</sup> SDR timing.

# 8 Register mapping

57

The following table provides a quick overview of the 8-bit registers embedded in the device.

| Name                   | Туре | Register<br>Address | Default  | Function and comment              |  |  |

|------------------------|------|---------------------|----------|-----------------------------------|--|--|

|                        |      | Hex                 | Binary   |                                   |  |  |

| Reserved               |      | 00 - 0A             | -        | Reserved                          |  |  |

| INTERRUPT_CFG          | R/W  | 0B                  | 0000000  | Interrupt register                |  |  |

| THS_P_L                | R/W  | 0C                  | 0000000  |                                   |  |  |

| THS_P_H                | R/W  | 0D                  | 0000000  | Pressure threshold registers      |  |  |

| IF_CTRL                | R/W  | 0E                  | 0000000  | Interface control register        |  |  |

| WHO_AM_I               | R    | 0F                  | 10110011 | Who am I                          |  |  |

| CTRL_REG1              | R/W  | 10                  | 0000000  |                                   |  |  |

| CTRL_REG2              | R/W  | 11                  | 00010000 | Control registers                 |  |  |

| CTRL_REG3              | R/W  | 12                  | 0000000  |                                   |  |  |

| FIFO_CTRL              | R/W  | 13                  | 0000000  | FIFO configuration register       |  |  |

| FIFO_WTM               | R/W  | 14                  | 0000000  |                                   |  |  |

| REF_P_L                | R/W  | 15                  | 0000000  | D.f.                              |  |  |

| REF_P_H                | R/W  | 16                  | 0000000  | Reference pressure registers      |  |  |

| Reserved               |      | 17                  | -        |                                   |  |  |

| RPDS_L                 | R/W  | 18                  | 00000000 |                                   |  |  |

| RPDS_H                 | R/W  | 19                  | 0000000  | Pressure offset registers         |  |  |

| Reserved               |      | 1A - 23             | -        | Reserved                          |  |  |

| INT_SOURCE             | R    | 24                  | Output   | Interrupt register                |  |  |

| FIFO_STATUS1           | R    | 25                  | Output   |                                   |  |  |

| FIFO_STATUS2           | R    | 26                  | Output   | FIFO status registers             |  |  |

| STATUS                 | R    | 27                  | Output   | Status register                   |  |  |

| PRESS_OUT_XL           | R    | 28                  | Output   |                                   |  |  |

| PRESS_OUT_L            | R    | 29                  | Output   | Pressure output registers         |  |  |

| PRESS_OUT_H            | R    | 2A                  | Output   |                                   |  |  |

| TEMP_OUT_L             | R    | 2B                  | Output   | Tomporative autout assisters      |  |  |

| TEMP_OUT_H             | R    | 2C                  | Output   | Temperature output registers      |  |  |

| Reserved               |      | 2D - 3B             | -        | Reserved                          |  |  |

| LPFP_RES               | R    | 3C                  | Output   | Low-pass filter reset register    |  |  |

| Reserved               |      | 3D - 77             | -        | Reserved                          |  |  |

| FIFO_DATA_OUT_PRESS_XL | R    | 78                  | Output   |                                   |  |  |

| FIFO_DATA_OUT_PRESS_L  | R    | 79                  | Output   | FIFO pressure output registers    |  |  |

| FIFO_DATA_OUT_PRESS_H  | R    | 7A                  | Output   |                                   |  |  |

| FIFO_DATA_OUT_TEMP_L   | R    | 7B                  | Output   |                                   |  |  |

| FIFO_DATA_OUT_TEMP_H   | R    | 7C                  | Output   | FIFO temperature output registers |  |  |

### Table 17. Registers address map

Registers marked as Reserved must not be changed. Writing to those registers may cause permanent damage to the device.

To guarantee the proper behavior of the device, all register addresses not listed in the above table must not be accessed and the content stored in those registers must not be changed.

The content of the registers that are loaded at boot should not be changed. They contain the factory calibration values. Their content is automatically restored when the device is powered up.

# 9 **Register description**

57/

The device contains a set of registers which are used to control its behavior and to retrieve pressure and temperature data. The register address, made up of 7 bits, is used to identify them and to read/write the data through the serial interface.

# 9.1 INTERRUPT\_CFG (0Bh)

Interrupt mode for pressure acquisition configuration (R/W)

| 7        | 6         | 5        | 4        | 3       | 2   | 1   | 0   |

|----------|-----------|----------|----------|---------|-----|-----|-----|

| AUTOREFP | RESET_ARP | AUTOZERO | RESET_AZ | DIFF_EN | LIR | PLE | PHE |

| AUTOREFPEnable AUTOREFP function. Default value: 0<br>(: normal mode; 1: AUTOREFP enabled)RESET_ARPReset AUTOREFP function. Default value: 0<br>(: normal mode; 1: reset AUTOREFP function)AUTOZEROEnable AUTOZERO function. Default value: 0<br>(: normal mode; 1: AUTOZERO enabled)RESET_AZReset AUTOZERO function. Default value: 0<br>(: normal mode; 1: AUTOZERO function. Default value: 0<br>(: normal mode; 1: reset AUTOZERO function)DIF_ENReset AUTOZERO function. Default value: 0<br>(: normal mode; 1: reset AUTOZERO function)LRLatch interrupt generation. Default value: 0<br>(: normal mode; 1: reset AUTOZERO function)LRLatch interrupt generation on pressure low event. Default value: 0<br>(: interrupt request;<br>1: enable interrupt generation on pressure low event. Default value: 0<br>(: disable interrupt generation on pressure high event. Default value: 0<br>(: disable interrupt generation on pressure high event. Default value: 0<br>(: disable interrupt request;<br>1: enable inte                                                                                                                                                                                                                   |           |                                                                             |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-----------------------------------------------------------------------------|

| Initial Constraint(0: normal mode; 1: AUTOREFP enabled)RESET_ARPReset AUTOREFP function. Default value: 0<br>(0: normal mode; 1: reset AUTOREFP function)AUTOZEROEnable AUTOZERO function. Default value: 0<br>(0: normal mode; 1: AUTOZERO enabled)RESET_AZReset AUTOZERO function. Default value: 0<br>(0: normal mode; 1: reset AUTOZERO function)DIFF_ENEnable interrupt generation. Default value: 0<br>(0: interrupt generation disabled; 1: interrupt generation enabled)LIRLatch interrupt request to the INT_SOURCE (24h) register. Default value: 0<br>(0: interrupt request not latched; 1: interrupt request latched)PLEEnable interrupt generation on pressure low event. Default value: 0<br>(0: disable interrupt request;<br>1: enable interrupt generation on pressure value lower than preset threshold)PHEEnable interrupt generation on pressure high event. Default value: 0<br>(0: disable interrupt generation on pressure high event. Default value: 0<br>(0: disable interrupt request;<br>(1: enable interrupt generation on pressure value lower than preset threshold)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | AUTOREEP  | Enable AUTOREFP function. Default value: 0                                  |

| RESET_ARP(0: normal mode; 1: reset AUTOREFP function)AUTOZEROEnable AUTOZERO function. Default value: 0<br>(0: normal mode; 1: AUTOZERO enabled)RESET_AZReset AUTOZERO function. Default value: 0<br>(0: normal mode; 1: reset AUTOZERO function)DIFF_ENEnable interrupt generation. Default value: 0<br>(0: interrupt generation disabled; 1: interrupt generation enabled)LIRLatch interrupt request to the INT_SOURCE (24h) register. Default value: 0<br>(0: interrupt request not latched; 1: interrupt request latched)PLEEnable interrupt generation on pressure low event. Default value: 0<br>(0: disable interrupt request;<br>1: enable interrupt request;<br>1: enable interrupt generation on pressure high event. Default value: 0<br>(0: disable interrupt request;<br>1: enable interrupt generation on pressure high event. Default value: 0<br>(0: disable interrupt request;<br>1: enable interrupt request;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | AUTOILEIT | (0: normal mode; 1: AUTOREFP enabled)                                       |

| Constraint(0: normal mode; 1: reset AUTOREFP function)AUTOZEROEnable AUTOZERO function. Default value: 0<br>(0: normal mode; 1: AUTOZERO enabled)RESET_AZReset AUTOZERO function. Default value: 0<br>(0: normal mode; 1: reset AUTOZERO function)DIFF_ENEnable interrupt generation. Default value: 0<br>(0: interrupt generation disabled; 1: interrupt generation enabled)LIRLatch interrupt request to the INT_SOURCE (24h) register. Default value: 0<br>(0: interrupt request not latched; 1: interrupt request latched)PLEEnable interrupt generation on pressure low event. Default value: 0<br>(0: disable interrupt request;<br>1: enable interrupt generation on pressure value lower than preset threshold)PHEEnable interrupt generation on pressure high event. Default value: 0<br>(0: disable interrupt generation on pressure high event. Default value: 0<br>(0: disable interrupt generation on pressure high event. Default value: 0<br>(0: disable interrupt generation on pressure high event. Default value: 0<br>(0: disable interrupt generation on pressure value lower than preset threshold)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | DESET ADD | Reset AUTOREFP function. Default value: 0                                   |

| AUTOZERO(0: normal mode; 1: AUTOZERO enabled)RESET_AZReset AUTOZERO function. Default value: 0<br>(0: normal mode; 1: reset AUTOZERO function)DIFF_ENEnable interrupt generation. Default value: 0<br>(0: interrupt generation disabled; 1: interrupt generation enabled)LIRLatch interrupt request to the INT_SOURCE (24h) register. Default value: 0<br>(0: interrupt request not latched; 1: interrupt request latched)PLEEnable interrupt generation on pressure low event. Default value: 0<br>(0: disable interrupt request;<br>1: enable interrupt request;<br>1: enable interrupt generation on pressure value lower than preset threshold)PHEEnable interrupt generation on pressure high event. Default value: 0<br>(0: disable interrupt request;<br>1: enable interrupt request;<br>1: enable interrupt generation on pressure high event. Default value: 0<br>(0: disable interrupt request;<br>1: enable interrupt request;<br>1: enable interrupt generation on pressure high event. Default value: 0<br>(0: disable interrupt request;<br>1: enable interrupt generation on pressure high event. Default value: 0<br>(0: disable interrupt request;<br>1: enable interrupt generation on pressure high event. Default value: 0<br>(0: disable interrupt request;<br>1: enable interrupt request;<br>1: enable interrupt request;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | RESET_ARE | (0: normal mode; 1: reset AUTOREFP function)                                |

| (0: normal mode; 1: AUTOZERO enabled)RESET_AZReset AUTOZERO function. Default value: 0<br>(0: normal mode; 1: reset AUTOZERO function)DIFF_ENEnable interrupt generation. Default value: 0<br>(0: interrupt generation disabled; 1: interrupt generation enabled)LIRLatch interrupt request to the INT_SOURCE (24h) register. Default value: 0<br>(0: interrupt request not latched; 1: interrupt request latched)PLEEnable interrupt generation on pressure low event. Default value: 0<br>(0: disable interrupt request;<br>1: enable interrupt request on pressure value lower than preset threshold)PHEEnable interrupt generation on pressure high event. Default value: 0<br>(0: disable interrupt generation on pressure high event. Default value: 0<br>(0: disable interrupt generation on pressure high event. Default value: 0<br>(0: disable interrupt generation on pressure high event. Default value: 0<br>(0: disable interrupt generation on pressure high event. Default value: 0<br>(0: disable interrupt generation on pressure high event. Default value: 0<br>(0: disable interrupt generation on pressure high event. Default value: 0<br>(0: disable interrupt generation on pressure high event. Default value: 0<br>(0: disable interrupt generation on pressure high event. Default value: 0<br>(0: disable interrupt request;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |           | Enable AUTOZERO function. Default value: 0                                  |

| RESET_AZ(0: normal mode; 1: reset AUTOZERO function)DIFF_ENEnable interrupt generation. Default value: 0<br>(0: interrupt generation disabled; 1: interrupt generation enabled)LIRLatch interrupt request to the INT_SOURCE (24h) register. Default value: 0<br>(0: interrupt request not latched; 1: interrupt request latched)PLEEnable interrupt generation on pressure low event. Default value: 0<br>(0: disable interrupt request;<br>1: enable interrupt request on pressure value lower than preset threshold)PHEEnable interrupt generation on pressure high event. Default value: 0<br>(0: disable interrupt generation on pressure high event. Default value: 0<br>(0: disable interrupt generation on pressure high event. Default value: 0<br>(0: disable interrupt request;<br>1: enable interrupt generation on pressure high event. Default value: 0<br>(0: disable interrupt request;<br>(0: disable interrupt generation on pressure high event. Default value: 0<br>(0: disable interrupt request;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | AUTOZERO  | (0: normal mode; 1: AUTOZERO enabled)                                       |

| Image: Constraint of the interrupt generation is a constraint of the interrupt generation. Default value: 0<br>(0: interrupt generation disabled; 1: interrupt generation enabled)DIFF_ENEnable interrupt generation disabled; 1: interrupt generation enabled)LIRLatch interrupt request to the INT_SOURCE (24h) register. Default value: 0<br>(0: interrupt request not latched; 1: interrupt request latched)PLEEnable interrupt generation on pressure low event. Default value: 0<br>(0: disable interrupt request;<br>1: enable interrupt request;<br>1: enable interrupt generation on pressure value lower than preset threshold)PHEEnable interrupt generation on pressure high event. Default value: 0<br>(0: disable interrupt request;<br>1: enable interrupt generation on pressure high event. Default value: 0<br>(0: disable interrupt request;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | DESET A7  | Reset AUTOZERO function. Default value: 0                                   |

| DIFF_EN   (0: interrupt generation disabled; 1: interrupt generation enabled)     LIR   Latch interrupt request to the INT_SOURCE (24h) register. Default value: 0     (0: interrupt request not latched; 1: interrupt request latched)     PLE   Enable interrupt generation on pressure low event. Default value: 0     (0: disable interrupt request;     1: enable interrupt request on pressure value lower than preset threshold)     PHE     (0: disable interrupt generation on pressure high event. Default value: 0     (0: disable interrupt request;     1: enable interrupt request on pressure high event. Default value: 0     (0: disable interrupt generation on pressure high event. Default value: 0     (0: disable interrupt request;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | RESET_AZ  | (0: normal mode; 1: reset AUTOZERO function)                                |

| Construct a co |           | Enable interrupt generation. Default value: 0                               |

| LIR   (0: interrupt request not latched; 1: interrupt request latched)     PLE   Enable interrupt generation on pressure low event. Default value: 0     (0: disable interrupt request;   1: enable interrupt request on pressure value lower than preset threshold)     PHE   Enable interrupt generation on pressure high event. Default value: 0     (0: disable interrupt request;   0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | DIFF_EN   | (0: interrupt generation disabled; 1: interrupt generation enabled)         |

| (0: interrupt request not latched; 1: interrupt request latched)     PLE   Enable interrupt generation on pressure low event. Default value: 0     (0: disable interrupt request;     1: enable interrupt request on pressure value lower than preset threshold)     PHE     (0: disable interrupt request;     (0: disable interrupt request on pressure value lower than preset threshold)     (0: disable interrupt generation on pressure high event. Default value: 0     (0: disable interrupt request;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |           | Latch interrupt request to the INT_SOURCE (24h) register. Default value: 0  |