# ST4300

## Hot swappable 2-wire bidirectional bus buffer

## Features

- Bidirectional I<sup>2</sup>C buffer

- Live board insertion and removal without SCL and SDA corruption

- Compatible with I<sup>2</sup>C<sup>TM</sup> and SMBus (up to 400 kHz)

- Low current consumption in disabled mode:

I<sub>CC</sub> < 1 μA</li>

- 1 V precharge on SDA and SCL lines

- Supports clock stretching, arbitration and synchronization

- Power down protection, SDA and SCL line goes to high impedance when V<sub>CC</sub> = 0 V

- Available in a small MSOP-8L package

## Applications

- Hot board insertion

- Buffer/bus extenders

- Desktop computers

- Servers

## Description

The ST4300 hot swappable 2-wire bus buffer provides bidirectional buffering for 2-wire open drain systems such as  $I^2C$  and SMBus, which isolates the capacitance of input and output side.

When connected, a one-shot circuit in the ST4300 accelerates the rise time allowing the use of a weaker pull-up while still meeting the rise-time requirements.

During live insertion, the ST4300 I/O is precharged to 1 V through a 100 k $\Omega$  resistor. When a Stop or Idle bus is detected, the I/O are connected to the buffer circuit, this procedure prevents data corruption in the bus. The V<sub>CC2</sub> enables the device to become a level translator, both V<sub>CC</sub> and V<sub>CC2</sub> can be supplied by voltage ranging from 2.7 V to 5.5 V with no constraint which supply is higher.

The ST4300 includes a digital ENABLE input pin which forces the device to shutdown completely and put the I/O into Hi-Z mode.

| Table 1. | Device | summarv |

|----------|--------|---------|

|          | Device | Summary |

| Order code | Package | Packaging     |

|------------|---------|---------------|

| ST4300TTR  | MSOP-8L | Tape and reel |

April 2009

Doc ID 14721 Rev 2

www.st.com

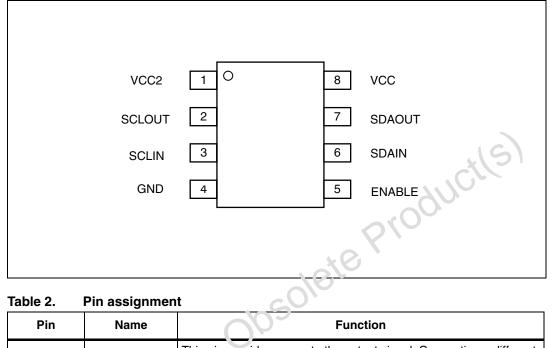

### **Pin configuration** 1

#### Figure 1. **Pin description**

#### Table 2. Pin assignment

|                 | Pin | Name             | Function                                                                                                                                                                                                                                                           |

|-----------------|-----|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                 | 1   | V <sub>CC2</sub> | This pin provides power to the output signal. Connecting a different voltage to this pin (compared to $V_{CC}$ ) results in a level translating from tion between the input and output. Pull-up resistors for $I^2C$ OUTPUT should be pulled to this supply level. |

|                 | 2   | SCLOUΓ           | Serial clock output                                                                                                                                                                                                                                                |

|                 | 3   | SCLIN            | Serial clock input                                                                                                                                                                                                                                                 |

|                 | 4   | GND              | Ground                                                                                                                                                                                                                                                             |

| 18              | 5   | ENABLE           | '0' set the device into low current mode. Input is isolated from output<br>'1' set the device into normal operation                                                                                                                                                |

| 50 <sup>1</sup> | 6   | SDAIN            | Serial data input                                                                                                                                                                                                                                                  |

| 002             | 7   | SDAOUT           | Serial data output                                                                                                                                                                                                                                                 |

| U               | 8   | V <sub>CC</sub>  | Main power supply                                                                                                                                                                                                                                                  |

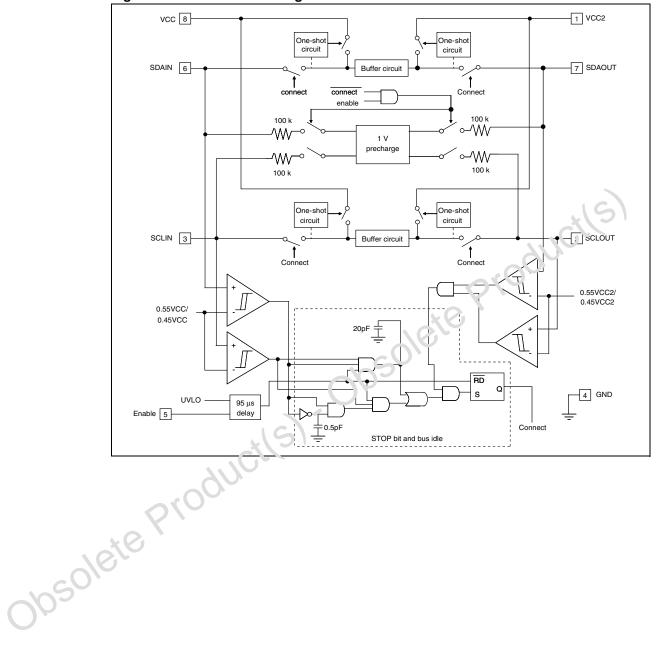

Figure 2. ST4300 block diagram

#### Operation 2

#### 2.1 Start up

When the ST4300 receives power on its power supply pin  $V_{CC}$ , the under voltage lockout (UVLO) circuit starts to work and detects whether the supply voltage is enough for the device's safe operation. In UVLO state, any activity on the SDA or SCL (I/O pins) is ignored. At the same time, the precharge circuit is charging the I/O lines to 1 V through a 100 k $\Omega$ resistor, to minimize any worst-case voltage difference during the connection, hence reducing disturbance in the active line.

Once the ST4300 exits from the UVLO state, it scans the SDA and SCL buses for either a Stop bit or bus Idle state, and also ensures that the SDA and SCL lines are HIGH, before it connects the buffer circuits to the I/O lines.

#### 2.2 **Buffer circuit**

The buffer circuit provides bidirectional buffering which separate the capacitance of input and output. If any of the pins, input or output, is pulled LCW, both pins are pulled LOW.

Only when both input and output are HIGH then the outfur circuit releases the line allowing the pull-up resistor to pull up the line HIGH. This teature allows to separate the input and output capacitance and at the same time succon clock stretching, clock arbitration and the acknowledgement protocol to work.

#### Input/output offset 2.3

When the SDA or SCL input/output pins are driven low (VI OW1), the ST4300 regulates the voltage at the other is de (V<sub>LOW2</sub>) to a slightly higher voltage.

This is describe a in the following expression:

$$V_{LOW2} = V_{LOW1} + 75mV + (V_{CC}/R) \times 100$$

)bsolete where R is the bus pull-up resistor value in ohms.

### 2.4 Pull-up resistor selection

As mentioned above, the offset between input and output is affected by the pull-up resistor chosen. The pull-up resistor must be chosen so that the output is still in valid range of LOW state or lower than V<sub>IL</sub> specification. Based on the I<sup>2</sup>C specification version 2.1 (*Table 3*), the V<sub>OL</sub> of I<sup>2</sup>C device must be able to provide 0.4 V maximum low level voltage with 3 mA pull-up current, and V<sub>IL</sub> of I<sup>2</sup>C device must be at least 0.3 V<sub>CC</sub>. The V<sub>IL</sub> of ST4300 is 0.6 V which is above the V<sub>OL</sub> of I<sup>2</sup>C device, it guarantees that the ST4300 is compatible with I<sup>2</sup>C low level signal.

| Table 3. | l <sup>2</sup> C s | pecification |

|----------|--------------------|--------------|

|----------|--------------------|--------------|

| Parameter                                   | Symbol          | Standar            | rd mode            | Fast mode          |                    |  |

|---------------------------------------------|-----------------|--------------------|--------------------|--------------------|--------------------|--|

| Faiametei                                   | Min             |                    | Max                | Min                |                    |  |

| Low input voltage                           | V <sub>IL</sub> | —                  | 0.3V <sub>CC</sub> | J.,                | 0.3V <sub>CC</sub> |  |

| High input voltage                          | V <sub>IH</sub> | 0.7V <sub>CC</sub> | -                  | 0.7√ <sub>CC</sub> | _                  |  |

| Low output voltage, at 3 mA pull-up current | V <sub>OL</sub> | 0                  | (1.4 V             | 0                  | 0.4 V              |  |

At the input of ST4300 (which is output of the I<sup>2</sup>C device most or slave), a pull-up resistor must be chosen so that the pull-up current is not exceeding 3 mA. This is to ensure that the level LOW state voltage level is not higher than 0.4 mV. The minimum value of the pull-up resistor is 1000  $\Omega$  at 2.7 V V<sub>CC</sub>, and 1900  $\Omega$  at 5.5 V V<sub>CC</sub>.

When the ST4300's input voltage is at the worst case of 0.4 V (V<sub>OL</sub> of I<sup>2</sup>C device), assuming the pull-up resistor (at the output) is 1 k $\Omega$  and V<sub>CC</sub> = 2.7 V, the output voltage will be 745 mV which is lower than the V<sub>I</sub> or I<sup>2</sup>C device (0.3 V<sub>CC</sub> = 810 mV).

For the correct ST4300's operation and to increase the noise margin, the minimum value of 6.8 kΩ pull-up resistor at input/output is recommended.

#### 2.5 **SMBus**

The same rule applies for the SMBus system, minimum value of 15 k $\Omega$  and 6.8 k $\Omega$  pull-up resistor is recommended for low power and high power SMBus system respectively.

In order to activate the one-shot circuit, the pull-up resistor must be able to provide a slew rate of 1.25 V/µs. The formula below can be used to determine the maximum value of pullup resistor:

$R \le (V_{CC(MIN)} - 0.6) \times (800,000)/C$

But, the start-up circuitry needs high voltage at SDA and SCL pins and the pull-up resistor must be able to override the pre-charge voltage. So, regardless of the capacitive load, a pullup resistor must be chosen as shown below respectively for  $V_{CC} = 5.5$  V: R≤ 24k3 ete Product

and for  $V_{CC} = 3.6$  V:

SMBus specification Table 4.

| Parameter                                          | Symbol          | Low power |       | High power |       |

|----------------------------------------------------|-----------------|-----------|-------|------------|-------|

| Falameter                                          | Symbol Min      |           | Max   | Min        | Max   |

| Low input voltage                                  | V <sub>IL</sub> | _         | 0.8 V | _          | 0.8 V |

| High input vo'ເa્າહ                                | V <sub>IH</sub> | 2.1 V     | _     | 2.1 V      | _     |

| Low output voltage at max 350 uA pull-up current   | V <sub>OL</sub> | 0         | 0.4 V | _          | _     |

| Low output voltage, at min<br>4 mA pull-up current | V <sub>OL</sub> | _         | _     | 0          | 0.4V  |

2.6

## **One-shot circuit**

This circuit will provide a low resistance path from I/O to V<sub>CC</sub> during the transition from LOW to HIGH to help pulling the SCL/SDA bus HIGH. It allows user to use weak pull-up resistance while still meeting rise time requirements.

The one-shot circuit is designed to be triggered only when both input and output are released by external driver, this is to ensure clock synchronization and acknowledgement procedure work properly. Once the one-shot is triggered, it pulls both input and output to V<sub>CC</sub>/V<sub>CC2</sub> fast, and it will be turned OFF when the input/output reach voltage near V<sub>CC</sub>/V<sub>CC2</sub>. But, in the event where one-shot is turned ON and at the same time external driver is pulling LOW (which might cause the voltage level stuck in the middle of GND and V<sub>CC</sub>), one-shot circuit will be automatically turned OFF after 400 ns. This feature is to prevent high current flows for long period.

### 2.7 ENABLE pin

Setting the ENABLE pin LOW will put ST4300 in low current state where the buffer circuit is disconnected, one-shot circuit is disabled, the pre-charge circuit is turned OFF. If the ENABLE pin is set HIGH after LOW, the start-up sequence as mentioned in *Section 2.1* is executed.

obsolete Product(s)- Obsolete Product(s)

## 3 Maximum rating

Stressing the device above the rating listed in the "Absolute maximum ratings" table may cause permanent damage to the device. These are stress ratings only, and operation of the device at these or any other conditions above those indicated in the operating sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. Refer also to the STMicroelectronics SURE Program and other relevant quality documents.

| Symbol           | Parameter                                | Value        | Unit |

|------------------|------------------------------------------|--------------|------|

| V <sub>CC</sub>  | Supply voltage                           | -0.3 to 6    | V    |

| V <sub>CC2</sub> | Supply voltage                           | -0.3 to 6.0  | V    |

| I/O              | Input/output voltage                     | -0 C +C 6.J  | V    |

| T <sub>STG</sub> | Storage temperature range                | -6:) to +125 | °C   |

| ESD              | Electrostatic discharge protection (HBM) | ±2           | kV   |

|                  | XU                                       |              |      |

Table 5. Absolute maximum ratings

### 3.1 Recommended operating conditions

### Table 6. Recommended operating conditions

|                  | 1 3                   |     |     |     |      |

|------------------|-----------------------|-----|-----|-----|------|

| Symbol           | Parameter             | Min | Тур | Мах | Unit |

| V <sub>CC</sub>  | Supply voltage        | 2.7 | —   | 5.5 | V    |

| V <sub>CC2</sub> | Supply voltage        | 2.7 | —   | 5.5 | V    |

| EN               | Device shable pin     | 0   | _   | 5.5 | V    |

| I/O              | lr.ب/output pins      | 0   | _   | 5.5 | V    |

| T <sub>OP</sub>  | Operating temperature | -40 | —   | 85  | °C   |

|                  |                       |     |     |     |      |

## 4 Electrical characteristics

Over recommended operating conditions unless otherwise noted. All typical values are at T\_A = 25 °C, V\_{CC} = V\_{CC2} = 5.5 V

| Symbol           | Parameter                         | Test conditions                                   | Т   | Unit |     |    |

|------------------|-----------------------------------|---------------------------------------------------|-----|------|-----|----|

|                  |                                   |                                                   | Min | Тур  | Max |    |

| I <sub>SD</sub>  | Shutdown current                  | V <sub>EN</sub> = 0 V                             | —   | 0.1  | 10  | A  |

| I <sub>CC</sub>  | Supply current of V <sub>CC</sub> | $V_{CC} = V_{CC2} = 5.5 V$<br>SDAIN = SCLIN = 0 V | _   | 3.0  | 4.1 | mA |

| I <sub>CC2</sub> | Supply current of $V_{CC2}$       |                                                   | -   | 2.1  | 2.9 | mA |

Table 7.Supply specifications

Table 8.Start-up circuit

|       |                    | otart up onoun                               |                                   | <u></u>             |           |                    |      |  |

|-------|--------------------|----------------------------------------------|-----------------------------------|---------------------|-----------|--------------------|------|--|

|       |                    |                                              | 10                                |                     | Value     |                    |      |  |

|       | Symbol             | Parameter                                    | Test conditions                   | Т                   | A = 25 °C | ;                  | Unit |  |

|       |                    |                                              | 002                               | Min                 | Тур       | Мах                |      |  |

|       | V <sub>PRE</sub>   | Pre-charge voltage                           | I/O floating                      | 0.8                 | 1.0       | 1.2                | V    |  |

|       | T <sub>IDLE</sub>  | Bus idle time                                |                                   | 50                  | 95        | 150                | μs   |  |

|       | V <sub>IL-EN</sub> | Low level anave<br>volte g.a                 |                                   | _                   | _         | 0.3V <sub>CC</sub> | V    |  |

|       | V <sub>IH-EN</sub> | רו, אין evel enable<br>voitage               |                                   | 0.45V <sub>CC</sub> | _         | -                  | V    |  |

|       | I <sub>EN</sub>    | Input current to EN pin                      | $V_{EN} = 0 V \text{ or } V_{CC}$ | -                   | ±0.1      | ±1.0               | μA   |  |

| 10    | і — т              | Enable delay, on-off                         |                                   | _                   | 10        | _                  | ns   |  |

| colle | T <sub>P-EN</sub>  | Enable delay, off-on                         |                                   | _                   | 95        | _                  | μs   |  |

| 05    |                    | UVLO threshold of $\mathrm{V}_{\mathrm{CC}}$ |                                   | -                   | 2.5       | _                  | V    |  |

| 0     | UVLO               | UVLO threshold of $V_{CC2}$                  |                                   | _                   | 2.0       | _                  | V    |  |

|                       |                   |                                                                            |     | Value     |     |      |  |

|-----------------------|-------------------|----------------------------------------------------------------------------|-----|-----------|-----|------|--|

| Symbol                | Parameter         | Test conditions                                                            | Т   | A = 25 °C | ;   | Unit |  |

|                       |                   |                                                                            | Min | Тур       | Max |      |  |

| I <sub>ONE-SHOT</sub> | One-short current | Positive transition,<br>$V_{CC} = V_{CC2} = 2.7 V$<br>guaranteed by design | _   | 2         | _   | mA   |  |

### Table 10.Buffer circuit

| SymbolParameterTest conditionsValue $V_{IL}$ Low level input voltage $V_{CC}$ and $V_{CC2}$ range =<br>$2.7$ V to $5.5$ V $  0.6$ $V_{IL}$ Low level input voltage $V_{CC}$ and $V_{CC2}$ range =<br>$2.7$ V to $5.5$ V $  0.6$ $V_{IH}$ High level input voltage $V_{CC}$ and $V_{CC2}$ range =<br>$2.7$ V to $5.5$ V $  0.6$ $V_{IH}$ High level input voltage $V_{CC}$ and $V_{CC2}$ range =<br>$2.7$ V to $5.5$ V $  0.6$ $V_{IH}$ High level input voltage $V_{CC}$ and $V_{CC2}$ range =<br>$2.7$ V to $5.5$ V $  0.6$ $V_{OL_{I/O}}$ Input-output offset<br>voltage $10$ K $\Omega$ pull un<br>$V_{C} = (1.3)$ V<br>$V_{L} = (0.2)$ V $ 100$ $175$ $V_{OL_{I/O}}$ Output low volta in<br>$V_{C} = V_{CC2} = 2.7$ V $0$ $ 0.4$ |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MinTypMax $V_{IL}$ Low level input voltage $V_{CC}$ and $V_{CC2}$ range =<br>2.7 V to 5.5 V0.6 $V_{IH}$ High level input voltage $V_{CC}$ and $V_{CC2}$ range =<br>2.7 V to 5.5 V2.1 $V_{OS\_I/O}$ Input-output offset<br>voltage10 K $\Omega$ pull un<br>$V_{CC}$ = (1.3 V<br>$V_{I,i}$ = (1.2 V)-100175 $V_{OL\_I/O}$ Output low volta reSDA, SCL pins,<br>I_SINK = 2 mA,0-0.4                                                                                                                                                                                                                                                                                                                                                     |

| $V_{IL}$ Low level input voltage $V_{CC}$ and $V_{CC2}$ range =<br>2.7 V to 5.5 V $  0.6$ $V_{IH}$ High level input voltage $V_{CC}$ and $V_{CC2}$ range =<br>2.7 V to 5.5 V $2.1$ $  V_{OS\_I/O}$ Input-output offset<br>voltage $10 \text{ K}\Omega \text{ pull un}$<br>$V_{CC} = 1.3 \text{ V}$<br>$V_{I,1} = 0.2 \text{ V}$ $ 100$ $175$ $V_{OL\_I/O}$ Output low voltageSDA, SCL pins,<br>I_{SINK} = 2 mA, $0$ $ 0.4$                                                                                                                                                                                                                                                                                                           |

| VILLow level input voltage2.7 V to 5.5 V0.0VIHHigh level input voltage $V_{CC}$ and $V_{CC2}$ range -<br>2.7 V to 5.5 V2.1VOS_I/OInput-output offset<br>voltage10 K\Omega pull un<br>$V_{CC} = (1.3 V)$ -100175VOS_I/OOutput low voltageSDA, SCL pins,<br>ISINK = 2 mA,0-0.4                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| VIAHigh level input voltage2.7 V to 5.5 V2.1- $V_{OS_I/O}$ Input-output offset<br>voltage10 K $\Omega$ pull uo<br>$V_{C_C} = (1.3) V$<br>$V_{I,1} = (1.2) V$ -100175 $V_{OL_I/O}$ Output low voltageSDA, SCL pins,<br>ISINK = 2 mA,0-0.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| $V_{OS_I/O}$ Input-output offset<br>voltage $V_{CC} = (1.3 V)$<br>$V_{I,1} = 0.2 V$ -100175 $V_{OL_I/O}$ Output low voltageSDA, SCL pins,<br>$I_{SINK} = 2 mA,$ 0-0.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| $V_{OL I/O}$ Output low voltage $I_{SINK} = 2 \text{ mA},$ 0 – 0.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 00 002                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| f <sub>SCL, SDA</sub> Operating frequency Guaranteed by design - 400                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| C <sub>IN</sub> มีวิทาวนt capacitance Guaranteed by design 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| $I_{I/C} I/O \text{ leakage current} \qquad SDA, SCL = V_{CC} = 5.5 V \pm 10$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| MinTypMax $f_{I2C}$ $I^{2C}$ operating<br>frequencyGuaranteed by design0400k $f_{I2C}$ $I^{2C}$ operating<br>frequencyGuaranteed by design0400k $t_{BUF}$ Bus free time between<br>stop and start conditionGuaranteed by design1.3 $t_{hD,STA}$ Hold time after<br>(repeated) start<br>conditionGuaranteed by design0.6 $t_{su,STA}$ Repeated start setup<br>timeGuaranteed by design0.6 $t_{su,STA}$ Stop condition setup<br>timeGuaranteed by design0.6 $t_{su,STO}$ Stop condition setup<br>timeGuaranteed by design30.7 $t_{hD,DAT}$ Data hold timeGuaranteed by design100 $t_{su,DAT}$ Data setup timeGuaranteed by design1.3 $t_{HIGH}$ Clock high periodGuaranteed by design0.6 $t_{HIGH}$ Clock high periodGuaranteed by design30.0 $t_{HIGH}$ Clock high periodGuaranteed by design0.6 $t_{HIGH}$ Clock high periodGuaranteed by design <td< th=""><th></th><th></th><th></th><th colspan="3">Value</th><th></th></td<> |                     |                   |                                           | Value      |     |          |      |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-------------------|-------------------------------------------|------------|-----|----------|------|

| fl2CI²C operating<br>frequencyGuaranteed by design0-400ktBUFBus free time between<br>stop and start conditionGuaranteed by design1.3thD,STAHold time after<br>(repeated) start<br>conditionGuaranteed by design0.6tsu,STARepeated start setup<br>timeGuaranteed by design0.6tsu,STARepeated start setup<br>timeGuaranteed by design0.6tsu,STOStop condition setup<br>timeGuaranteed by design0.6tsu,DATData hold timeGuaranteed by design30.0tLOWClock low periodGuaranteed by design1.3tHIGHClock high periodGuaranteed by design0.6tauBisa timeGuaranteed by design10.0tauRepeated timeGuaranteed by design1.3tauData setup timeGuaranteed by design1.3tauStop conditionGuaranteed by design0.6tauData setup timeGuaranteed by design1.3tauClock high periodGuaranteed by design0.6tauStop conditionGuaranteed by design0.6tauData setup time<                                                                                                                                                                                                                                             | Symbol              | Parameter         | Test conditions                           | TA = 25 °C |     | ;        | Unit |

| I <sub>12C</sub> frequencyGuaranteed by design0-400R $t_{BUF}$ Bus free time between<br>stop and start conditionGuaranteed by design1.3 $t_{hD,STA}$ Hold time after<br>(repeated) start<br>conditionGuaranteed by design0.6 $t_{su,STA}$ Repeated start setup<br>timeGuaranteed by design0.6 $t_{su,STA}$ Stop condition setup<br>timeGuaranteed by design0.6 $t_{su,STO}$ Stop condition setup<br>timeGuaranteed by design0.6 $t_{su,STO}$ Data hold timeGuaranteed by design0.6 $t_{hD,DAT}$ Data setup timeGuaranteed by design100 $t_{LOW}$ Clock low periodGuaranteed by design0.6 $t_{HIGH}$ Clock high periodGuaranteed by design0.6 $t_{HIGH}$ Stop timeGuaranteed by design0.6 $t_{HIGH}$ Clock high periodGuaranteed by design0.6 $t_{HIGH}$ Clock high periodGuaranteed by design0.6 $t_{HIGH}$ Stop timeGuaranteed by design0.6 $t_{HIGH}$ Clock high periodGuaranteed by design0.6 $t_{HIGH}$ Clock high periodGuaranteed                                                                                                                                                      |                     |                   |                                           | Min        | Тур | Мах      |      |

| tBUFstop and start conditionGuaranteed by design1.3thD,STAHold time after<br>(repeated) start<br>conditionGuaranteed by design0.6tsu,STARepeated start setup<br>timeGuaranteed by design0.6tsu,STAStop condition setup<br>timeGuaranteed by design0.6tsu,STOStop condition setup<br>timeGuaranteed by design0.6tsu,STOData hold timeGuaranteed by design30.7thD,DATData setup timeGuaranteed by design100tLOWClock low periodGuaranteed ty design1.3tHIGHClock high periodGuaranteed ty design0.6tableStop conditionGuaranteed by design1.3tableData setup timeGuaranteed by design1.00tableClock low periodGuaranteed ty design0.6tableStop conditionGuaranteed ty design1.3tableClock high periodGuaranteed ty design0.6tableStop conditionGuaranteed ty design0.6tableClock high periodGuaranteed ty design0.6tableStop conditionGuaranteed ty design0.6tableStop conditionGuaranteed ty design0.6 <td>f<sub>I2C</sub></td> <td></td> <td>Guaranteed by design</td> <td>0</td> <td>_</td> <td>400</td> <td>kHz</td>                                                                       | f <sub>I2C</sub>    |                   | Guaranteed by design                      | 0          | _   | 400      | kHz  |

| thD,STA(repeated) start<br>conditionGuaranteed by design0.6tsu,STARepeated start setup<br>timeGuaranteed by design0.6tsu,STAStop condition setup<br>timeGuaranteed by design0.6tsu,STOStop condition setup<br>timeGuaranteed by design0.6tsu,STOData hold timeGuaranteed by design30.7thD,DATData setup timeGuaranteed by design100tsu,DATData setup timeGuaranteed by design1.3tLOWClock low periodGuaranteed by design0.6tHIGHClock high periodGuaranteed by design0.6tsuBise time10 kΩ pull-up,300                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | t <sub>BUF</sub>    |                   | Guaranteed by design                      | 1.3        | _   | _        | μs   |

| $t_{su,STA}$ timeGuaranteed by design0.6- $t_{su,STO}$ Stop condition setup<br>timeGuaranteed by design0.6 $t_{hD,DAT}$ Data hold timeGuaranteed by design30.7 $t_{su,DAT}$ Data setup timeGuaranteed by design100 $t_{LOW}$ Clock low periodGuaranteed by design1.3 $t_{HIGH}$ Clock high periodGuaranteed by design0.6 $t_{HIGH}$ Clock high periodGuaranteed by design0.6 $t_{end}$ $t_{end}$ $t_{end}$ $t_{end}$ $t_{end}$ $t_{end}$ $t_{end}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | <sup>t</sup> hD,STA | (repeated) start  | Guaranteed by design                      | 0.6        | _   | .10      | μs   |

| $t_{su,STO}$ timeGuaranteed by design $0.6$ $  t_{hD,DAT}$ Data hold timeGuaranteed by design $30.7$ $  t_{su,DAT}$ Data setup timeGuaranteed by design $100$ $  t_{LOW}$ Clock low periodGuaranteed by design $1.3$ $  t_{HIGH}$ Clock high periodGuaranteed by design $0.6$ $ -$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | t <sub>su,STA</sub> |                   | Guaranteed by design                      | 0.6        | _   | <u>C</u> | μs   |

| tsu,DAT     Data setup time     Guaranteed by design     100     -     -       tLOW     Clock low period     Guaranteed by design     1.3     -     -       tHIGH     Clock high period     Guaranteed by design     0.6     -     -       tHIGH     Clock high period     Guaranteed by design     0.6     -     -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | t <sub>su,STO</sub> |                   | Guaranteed by design                      | 0.6        | 00, | -        | μs   |

| $t_{LOW}$ Clock low periodGuaranteed by design1.3- $t_{HIGH}$ Clock high periodGuaranteed by design0.6- $t_{max}$ Bise time10 kΩ pull-up,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | t <sub>hD,DAT</sub> | Data hold time    | Guaranteed by design                      | 30.7       |     | _        | μs   |

| t     Clock high period     Guaraniend by design     0.6     -       t     Bise time $10 k\Omega$ pull-up,     -     -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | t <sub>su,DAT</sub> | Data setup time   | Guaranteed by design                      | 100        | _   | _        | μs   |

| t Bise time $10 \text{ k}\Omega$ pull-up, $ -$ 300                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | t <sub>LOW</sub>    | Clock low period  | Guaranteed by cleargn                     | 1.3        | _   | _        | μs   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | t <sub>HIGH</sub>   | Clock high period | Guaraniend by design                      | 0.6        | _   | _        | μs   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | t <sub>R</sub>      | Rise time         | 10 kΩ oull-up,<br>V <sub>CC</sub> = 5.5 V | _          | _   | 300      | μs   |

| t <sub>F</sub> Fall time 10 kΩ pull-up,<br>V <sub>CC</sub> = 5.5 V 300                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                     |                   |                                           | _          | _   | 300      | μs   |

Table 11. Timing characteristics

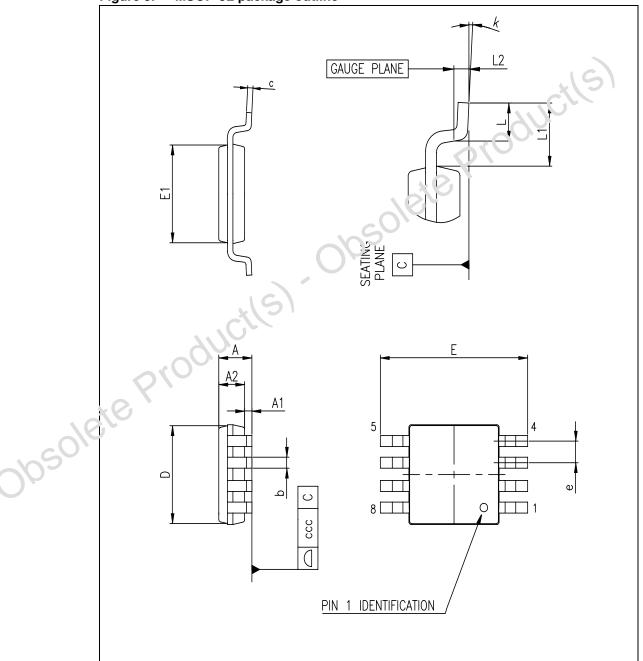

## 5 Package mechanical data

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK<sup>®</sup> packages, depending on their level of environmental compliance. ECOPACK<sup>®</sup> specifications, grade definitions and product status are available at: www.st.com. ECOPACK<sup>®</sup> is an ST trademark.

Figure 3. MSOP-8L package outline

Doc ID 14721 Rev 2

| SymbolAA1A2bCDEE1            | Min<br><br>0<br>0.75<br>0.22<br>0.08<br>2.80 | Typ           -           -           0.85           -           -           - | Max<br>1.10<br>0.15<br>0.95<br>0.40 |

|------------------------------|----------------------------------------------|--------------------------------------------------------------------------------|-------------------------------------|

| A1<br>A2<br>b<br>C<br>D<br>E | 0<br>0.75<br>0.22<br>0.08<br>2.80            | <br>0.85<br>                                                                   | 0.15<br>0.95<br>0.40                |

| A2<br>b<br>C<br>D<br>E       | 0.75<br>0.22<br>0.08<br>2.80                 | 0.85                                                                           | 0.95<br>0.40                        |

| b<br>c<br>D<br>E             | 0.22<br>0.08<br>2.80                         | -                                                                              | 0.40                                |

| C D E                        | 0.08<br>2.80                                 |                                                                                |                                     |

| D<br>E                       | 2.80                                         | -                                                                              | 0.00                                |

| E                            |                                              |                                                                                | 0.23                                |

|                              |                                              | 3.00                                                                           | 3.20                                |

| E1                           | 4.65                                         | 4.90                                                                           | 5.15                                |

|                              | 2.80                                         | 3.00                                                                           | 3.10                                |

| е                            | _                                            | 0.65                                                                           | - 0                                 |

| L                            | 0.40                                         | 0.60                                                                           | 0.80                                |

| L1                           | _                                            | 0.9:                                                                           | _                                   |

| L2                           | _                                            | C.25                                                                           | _                                   |

| К                            | 0 <sup>0</sup>                               | -                                                                              | 8 <sup>0</sup>                      |

| CCC                          |                                              | - 1                                                                            | 0.10                                |

| oleteProducti                | 5)                                           |                                                                                |                                     |

Table 12. MSOP-8L mechanical data

## 6 Applications examples

### 6.1 Live insertion and capacitance buffering

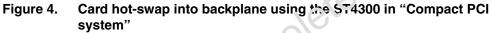

*Figure 4* and *Figure 5* show some examples of applications implementing the ST4300 features of hot swap control and capacitance buffer. In a bus where all the cards are connected directly, the backplane must drive the capacitive load of all the cards, which may be quite significant or even higher than the I<sup>2</sup>C/SMBUS specification. By placing the ST4300 device on every card, the backplane now can only see the capacitance of the ST4300 I/O, which is less than 10 pF on every card, while the whole capacitive loads at the card side is driven by the ST4300. This method increases the number of cards which can be driven by the backplane.

The ST4300 may be used also for applications as shown in *Figure 4*. V<sub>CC</sub> and V<sub>CC2</sub> r hight have different values and the ST4300 acts as a level translator. Both V<sub>CC</sub> pins are connected first before SDAIN, SCLIN and ENABLE by a longer connector to ensure SDAIN and SCLIN is biased to 1 V before these are connected to the backplane bus. The ENABLE pin is pulled LOW by a resistor and having a shorter connector to disable the ST4300 until all other pins are connected and the transient is settled.

Doc ID 14721 Rev 2

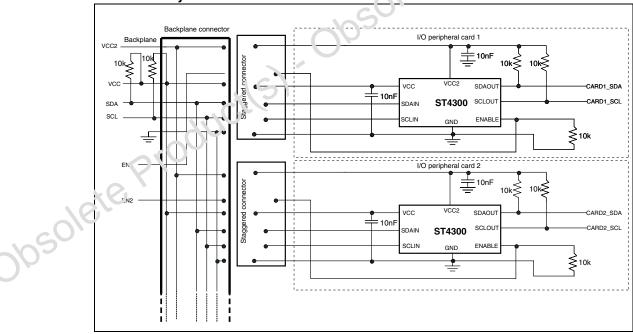

*Figure 5* shows a system with two different types of slaves. The first type has higher speed and lower input capacitance while the other type is compatible with lower speed and has higher input capacitance. The ST4300 can be used to isolate the lower speed slave if the host only needs to communicate with the higher speed device and at the same time reduce the capacitance loading at the bus. At the same time, the ST4300 device can operate as a level translator if the power supply to any of the slaves is different from the host.

Figure 5. Buffer/bus extender and level translator application

# 7 Revision history

|        | Date        | Revision | Changes                                                                                        |

|--------|-------------|----------|------------------------------------------------------------------------------------------------|

|        | 21-May-2008 | 1        | Initial release.                                                                               |

|        | 30-Apr-2009 | 2        | Document status promoted from Preliminary data to datasheet.<br>Modified: ECOPACK information. |

| obsole | tepro       | Juctl    | Modified: ECOPACK information.                                                                 |

### Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidia ris s (SI") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.

All ST products are sold pursuant to ST's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property ignts is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warpency covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein or considered as a warpency covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein or considered the service of services or services or any intellectual property contained the service of services or services or any intellectual property contained the service of services or services or any intellectual property contained the service of services or services or services or any intellectual property contained the service of services or services or services or any intellectual property contained the service of services or services or any intellectual property contained the service of services or services or any intellectual property contained the service of services or services or any intellectual property contained the service of services or services or services or any intellectual property contained the service of service of service or services or services or services or service of service or service of service or service of service or service of service or se

UNLESS OTHERWISE SET FORTH IN ST'S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS EXPRESSLY APPROVED IN VM: ING BY AN AUTHORIZED ST REPRESENTATIVE, ST PRODUCTS ARE NOT RECOMMENDED, AUTHORIZED OR W.N. ANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS, NOR IN PRODUCTE OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY, DEATH, OR SEVERE PROFENTIOR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE GRADE" MAY ONLY BE VISED IN AUTOMOTIVE APPLICATIONS AT USER'S OWN RISK.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warran. Y granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2009 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan -Malaysia - Malta - Morocco - Philippines - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com

Doc ID 14721 Rev 2