for available offerings.

# **DDR3 SDRAM Data Sheet Addendum**

MT41J512M4 - 64 Meg x 4 x 8 Banks MT41J256M8 - 32 Meg x 8 x 8 Banks MT41J128M16 - 16 Meg x 16 x 8 Banks

## - 4

| Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Options <sup>1</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Marking |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| • $V_{DD} = V_{DDQ} = 1.5V \pm 0.075V$<br>• 1.5V center-terminated push/pull I/O<br>• Differential bidirectional data strobe<br>• $8n$ -bit prefetch architecture<br>• Differential clock inputs (CK, CK#)<br>• 8 internal banks<br>• Nominal and dynamic on-die termination (ODT)<br>for data, strobe, and mask signals<br>• Programmable CAS READ latency (CL)<br>• Posted CAS additive latency (AL)<br>• Programmable CAS WRITE latency (CWL) based on<br>${}^{t}CK$<br>• Fixed burst length (BL) of 8 and burst chop (BC) of 4<br>(via the mode register set [MRS])<br>• Selectable BC4 or BL8 on-the-fly (OTF)<br>• Self refresh mode<br>• $T_{C}$ of 0°C to 95°C<br>- 64ms, 8192 cycle refresh at 0°C to 85°C<br>- 32ms, 8192 cycle refresh at 85°C to 95°C<br>• Self refresh temperature (SRT)<br>• Write leveling<br>• Multipurpose register<br>• Output driver calibration | • Configuration<br>- 512 Meg x 4<br>- 256 Meg x 8<br>- 128 Meg x 16<br>• FBGA package (Pb-free) – x4, x8<br>- 78-ball (8mm x 10.5mm) Rev. M, K<br>- 78-ball (9mm x 11.5mm) Rev. D<br>• FBGA package (Pb-free) – x16<br>- 96-ball (9mm x 14mm) Rev. D<br>- 96-ball (8mm x 14mm) Rev. K<br>• Timing – cycle time<br>- 938ps @ CL = 14 (DDR3-2133)<br>- 1.071ns @ CL = 13 (DDR3-1866)<br>- 1.25ns @ CL = 11 (DDR3-1600)<br>- 1.5ns @ CL = 9 (DDR3-1333)<br>- 1.87ns @ CL = 7 (DDR3-1066)<br>• Special Options<br>- Premium Lifecycle Product (PLP)<br>• Operating temperature<br>- Commercial (0°C $\leq T_C \leq +95^{\circ}$ C)<br>- Industrial (-40°C $\leq T_C \leq +95^{\circ}$ C)<br>• Revision<br>Note: 1. Not all options listed can be co |         |

| Output driver calibration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Note: 1. Not all options listed can be combined to<br>define an offered product. Use the part<br>catalog search on http://www.micron.com                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |

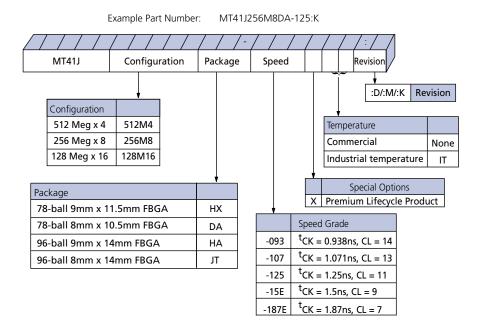

#### Figure 1: DDR3 Part Numbers

Note: 1. Not all options listed can be combined to define an offered product. Use the part catalog search on http://www.micron.com for available offerings.

#### **FBGA Part Marking Decoder**

Due to space limitations, FBGA-packaged components have an abbreviated part marking that is different from the part number. For a quick conversion of an FBGA code, see the FBGA Part Marking Decoder on Micron's Web site: http://www.micron.com.

### **Revision History**

Rev. A - 11/13

• Initial release based on the 2Gb x4, x8, x16 DDR3 SDRAM, Rev. Q 04/13 data sheet

8000 S. Federal Way, P.O. Box 6, Boise, ID 83707-0006, Tel: 208-368-3900 www.micron.com/productsupport Customer Comment Line: 800-932-4992 Micron and the Micron logo are trademarks of Micron Technology, Inc. All other trademarks are the property of their respective owners. This data sheet contains minimum and maximum limits specified over the power supply and temperature range set forth herein.

Although considered final, these specifications are subject to change, as further product development and data characterization sometimes occur.