# **Phase Locked Loop**

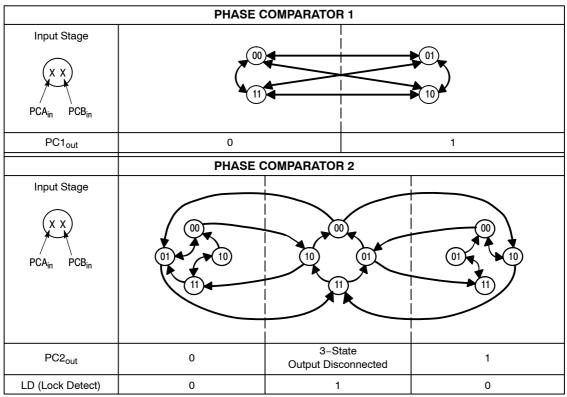

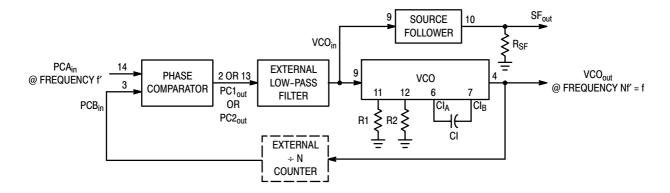

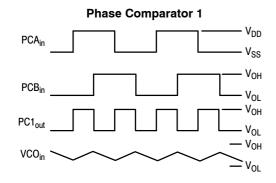

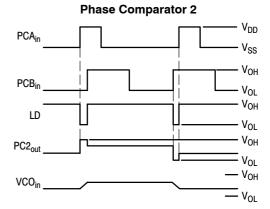

The MC14046B phase locked loop contains two phase comparators, a voltage-controlled oscillator (VCO), source follower, and zener diode. The comparators have two common signal inputs, PCA<sub>in</sub> and PCB<sub>in</sub>. Input PCA<sub>in</sub> can be used directly coupled to large voltage signals, or indirectly coupled (with a series capacitor) to small voltage signals. The self-bias circuit adjusts small voltage signals in the linear region of the amplifier. Phase comparator 1 (an exclusive OR gate) provides a digital error signal PC1<sub>out</sub>, and maintains 90° phase shift at the center frequency between PCA<sub>in</sub> and PCB<sub>in</sub> signals (both at 50% duty cycle). Phase comparator 2 (with leading edge sensing logic) provides digital error signals, PC2out and LD, and maintains a 0° phase shift between PCAin and PCBin signals (duty cycle is immaterial). The linear VCO produces an output signal VCOout whose frequency is determined by the voltage of input VCO<sub>in</sub> and the capacitor and resistors connected to pins C1<sub>A</sub>, C1<sub>B</sub>, R1, and R2. The source-follower output SFout with an external resistor is used where the VCO<sub>in</sub> signal is needed but no loading can be tolerated. The inhibit input Inh, when high, disables the VCO and source follower to minimize standby power consumption. The zener diode can be used to assist in power supply regulation.

Applications include FM and FSK modulation and demodulation, frequency synthesis and multiplication, frequency discrimination, tone decoding, data synchronization and conditioning, voltage-to-frequency conversion and motor speed control.

## **Features**

- Buffered Outputs Compatible with Low-Power TTL

- Diode Protection on All Inputs

- Supply Voltage Range = 3.0 to 18 V

- Pin-for-Pin Replacement for CD4046B

- Phase Comparator 1 is an Exclusive OR Gate and is Duty Cycle Limited

- Phase Comparator 2 Switches on Rising Edges and is not Duty Cycle Limited

- These Devices are Pb-Free and are RoHS Compliant

#### MAXIMUM RATINGS (Voltages Referenced to VSS)

| Symbol           | Parameter                               | Value                         | Unit |

|------------------|-----------------------------------------|-------------------------------|------|

| V <sub>DD</sub>  | DC Supply Voltage Range                 | -0.5 to +18.0                 | V    |

| V <sub>in</sub>  | Input Voltage Range (All Inputs)        | -0.5 to V <sub>DD</sub> + 0.5 | V    |

| I <sub>in</sub>  | DC Input Current, per Pin               | ±10                           | mA   |

| P <sub>D</sub>   | Power Dissipation, per Package (Note 1) | 500                           | mW   |

| T <sub>A</sub>   | Operating Temperature Range             | -55 to +125                   | °C   |

| T <sub>stg</sub> | Storage Temperature Range               | -65 to +150                   | °C   |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

1. Temperature Derating:

Plastic "P and D/DW" Packages: - 7.0 mW/°C From 65°C To 125°C

## ON Semiconductor®

http://onsemi.com

## MARKING DIAGRAMS

PDIP-16 P SUFFIX CASE 648 16<mark><u>ሴ ሉ ሉ ሉ ሉ ሉ ሉ</u> ለ MC14046BCP</mark> o AWLYYWWG 1 **ፓ** ତ ତ ତ ତ ତ ତ

SOIC-16 WB DW SUFFIX CASE 751G

SOEIAJ-16 F SUFFIX CASE 966

A = Assembly Location

$\begin{array}{lll} WL,\,L &= \mbox{Wafer Lot} \\ YY,\,Y &= \mbox{Year} \\ WW,\,W &= \mbox{Work Week} \\ G &= \mbox{Pb-Free Indicator} \\ \end{array}$

## **ORDERING INFORMATION**

See detailed ordering and shipping information in the package dimensions section on page 4 of this data sheet.

This device contains protection circuitry to guard against damage due to high static voltages or electric fields. However, precautions must be taken to avoid applications of any voltage higher than maximum rated voltages to this high–impedance circuit. For proper operation,  $V_{in}$  and  $V_{out}$  should be constrained to the range  $V_{SS} \leq (V_{in} \text{ or } V_{out}) \leq V_{DD}$ .

Unused inputs must always be tied to an appropriate logic voltage level (e.g., either V<sub>SS</sub> or V<sub>DD</sub>). Unused outputs must be left open.

#### **BLOCK DIAGRAM**

#### SELF BIAS PHASE O 2 PC1<sub>out</sub> CIRCUIT **COMPARATOR 1** -o 13 PC2<sub>out</sub> PHASE 3 C **COMPARATOR 2** -01 LD VCO<sub>out</sub> **-0**4 VOLTAGE VCO<sub>in</sub> 9 o + 0 11 R1 CONTROLLED 12 R2 V<sub>DD</sub> = PIN 16 **OSCILLATOR** -06 C1<sub>A</sub> -07 C1<sub>B</sub> (VCO) V<sub>SS</sub> = PIN 8 -o 10 SF<sub>out</sub> SOURCE FOLLOWER INH 5 c o 15 ZENER V<sub>SS</sub> o

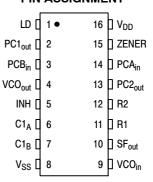

## PIN ASSIGNMENT

## **ELECTRICAL CHARACTERISTICS** (Voltages Referenced to V<sub>SS</sub>)

|                                                      |                                        |                 | V <sub>DD</sub> | - 55   | 5°C   |              | 25°C        |                     | 125    | 5°C   |      |

|------------------------------------------------------|----------------------------------------|-----------------|-----------------|--------|-------|--------------|-------------|---------------------|--------|-------|------|

| Characteristic                                       |                                        | Symbol          | Vdc             | Min    | Max   | Min          | Тур         | Max                 | Min    | Max   | Unit |

| Output Voltage                                       | "0" Level                              | V <sub>OL</sub> | 5.0             | -      | 0.05  | -            | 0           | 0.05                | -      | 0.05  | Vdc  |

| $V_{in} = V_{DD}$ or 0                               |                                        |                 | 10              | -      | 0.05  | -            | 0           | 0.05                | _      | 0.05  |      |

|                                                      |                                        |                 | 15              | _      | 0.05  | -            | 0           | 0.05                | _      | 0.05  |      |

|                                                      | "1" Level                              | V <sub>OH</sub> | 5.0             | 4.95   | -     | 4.95         | 5.0         | _                   | 4.95   | _     | Vdc  |

| $V_{in} = 0$ or $V_{DD}$                             |                                        |                 | 10              | 9.95   | -     | 9.95         | 10          | -                   | 9.95   | -     |      |

|                                                      |                                        |                 | 15              | 14.95  | _     | 14.95        | 15          | -                   | 14.95  | -     |      |

| Input Voltage (Note 2)                               | "0" Level                              | V <sub>IL</sub> |                 |        |       |              |             |                     |        |       | Vdc  |

| $(V_O = 4.5 \text{ or } 0.5 \text{ Vdc})$            |                                        |                 | 5.0             | _      | 1.5   | -            | 2.25        | 1.5                 | _      | 1.5   |      |

| $(V_O = 9.0 \text{ or } 1.0 \text{ Vdc})$            |                                        |                 | 10              | -      | 3.0   | -            | 4.50        | 3.0                 | -      | 3.0   |      |

| $(V_O = 13.5 \text{ or } 1.5 \text{ Vdc})$           |                                        |                 | 15              | -      | 4.0   | -            | 6.75        | 4.0                 | -      | 4.0   |      |

| $(V_O = 0.5 \text{ or } 4.5 \text{ Vdc})$            | "1" Level                              | V <sub>IH</sub> | 5.0             | 3.5    | -     | 3.5          | 2.75        | -                   | 3.5    | -     | Vdc  |

| $(V_O = 1.0 \text{ or } 9.0 \text{ Vdc})$            |                                        |                 | 10              | 7.0    | _     | 7.0          | 5.50        | -                   | 7.0    | _     |      |

| $(V_O = 1.5 \text{ or } 13.5 \text{ Vdc})$           |                                        |                 | 15              | 11     | _     | 11           | 8.25        | -                   | 11     | _     |      |

| Output Drive Current                                 |                                        | I <sub>OH</sub> |                 |        |       |              |             |                     |        |       | mAdc |

| $(V_{OH} = 2.5 \text{ Vdc})$                         | Source                                 |                 | 5.0             | - 1.2  | _     | - 1.0        | - 1.7       | -                   | - 0.7  | _     |      |

| (V <sub>OH</sub> = 4.6 Vdc)                          |                                        |                 | 5.0             | - 0.25 | -     | - 0.2        | - 0.36      | -                   | - 0.14 | _     |      |

| (V <sub>OH</sub> = 9.5 Vdc)                          |                                        |                 | 10              | - 0.62 | -     | - 0.5        | - 0.9       | -                   | -0.35  | _     |      |

| $(V_{OH} = 13.5 \text{ Vdc})$                        |                                        |                 | 15              | - 1.8  | _     | - 1.5        | - 3.5       | -                   | - 1.1  | _     |      |

| $(V_{OL} = 0.4 \text{ Vdc})$                         | Sink                                   | l <sub>OL</sub> | 5.0             | 0.64   | -     | 0.51         | 0.88        | -                   | 0.36   | _     | mAdc |

| $(V_{OL} = 0.5 \text{ Vdc})$                         |                                        |                 | 10              | 1.6    | _     | 1.3          | 2.25        | -                   | 0.9    | _     |      |

| $(V_{OL} = 1.5 \text{ Vdc})$                         |                                        |                 | 15              | 4.2    | _     | 3.4          | 8.8         | -                   | 2.4    | -     |      |

| Input Current                                        |                                        | l <sub>in</sub> | 15              | -      | ± 0.1 | -            | ±0.00001    | ± 0.1               | -      | ± 1.0 | μAdc |

| Input Capacitance                                    |                                        | C <sub>in</sub> | _               | -      | -     | -            | 5.0         | 7.5                 | -      | -     | pF   |

| Quiescent Current                                    |                                        | I <sub>DD</sub> | 5.0             | _      | 5.0   | -            | 0.005       | 5.0                 | -      | 150   | μAdc |

| (Per Package) Inh = PCA                              | $\lambda_{\text{in}} = V_{\text{DD}},$ |                 | 10              | _      | 10    | -            | 0.010       | 10                  | -      | 300   |      |

| Zener = VCO <sub>in</sub> = 0 V, PC                  | $B_{in} = V_{DD}$                      |                 | 15              | _      | 20    | -            | 0.015       | 20                  | -      | 600   |      |

| or 0 V, $I_{out} = 0 \mu A$                          |                                        |                 |                 |        |       |              |             |                     |        |       |      |

| Total Supply Current (Note 3)                        |                                        | I <sub>T</sub>  | 5.0             |        |       |              | .46 μA/kHz) |                     |        |       | mAdc |

| (Inh = "0", $f_0$ = 10 kHz, $C_L$ = 50 pF,           |                                        |                 | 10              |        |       | $I_{T} = (2$ | 91 μA/kHz)  | f + I <sub>DD</sub> |        |       |      |

| $R1 = 1.0 M\Omega$ , $R2 = \infty R_{SF} = \infty$ , |                                        |                 | 15              |        |       | $I_{T} = (4$ | .37 μA/kHz) | f + I <sub>DD</sub> |        |       |      |

| and 50% Duty Cycle)                                  |                                        |                 |                 |        |       |              |             |                     |        |       |      |

2. Noise immunity specified for worst-case input combination.

Noise Margin for both "1" and "0" level =  $1.0 \text{ Vdc min } @ \text{V}_{DD} = 5.0 \text{ Vdc}$  $2.0 \text{ Vdc min } @ \text{V}_{DD} = 10 \text{ Vdc}$

2.5 Vdc min @ V<sub>DD</sub> = 15 Vdc

3. To Calculate Total Current in General:

$$I_{T} \approx \, 2.2 \, x \, V_{DD} \Big( \frac{VCO_{in} - 1.65}{R1} \, + \, \frac{V_{DD} - 1.35}{R2} \Big)^{3/4} \, + 1.6 \, x \Big( \frac{VCO_{in} - 1.65}{R_{SF}} \Big)^{3/4} \, + 1 \, x \, 10^{-3} \, \big( C_{L} + 9 \big) \, V_{DD} \, f \, + 1 \, x \, 10^{-3} \, \big( C_{L} + 9 \big) \, V_{DD} \, f \, + 1 \, x \, 10^{-3} \, \big( C_{L} + 9 \big) \, V_{DD} \, f \, + 1 \, x \, 10^{-3} \, \big( C_{L} + 9 \big) \, V_{DD} \, f \, + 1 \, x \, 10^{-3} \, \big( C_{L} + 9 \big) \, V_{DD} \, f \, + 1 \, x \, 10^{-3} \, \big( C_{L} + 9 \big) \, V_{DD} \, f \, + 1 \, x \, 10^{-3} \, \big( C_{L} + 9 \big) \, V_{DD} \, f \, + 1 \, x \, 10^{-3} \, \big( C_{L} + 9 \big) \, V_{DD} \, f \, + 1 \, x \, 10^{-3} \, \big( C_{L} + 9 \big) \, V_{DD} \, f \, + 1 \, x \, 10^{-3} \, \big( C_{L} + 9 \big) \, V_{DD} \, f \, + 1 \, x \, 10^{-3} \, \big( C_{L} + 9 \big) \, V_{DD} \, f \, + 1 \, x \, 10^{-3} \, \big( C_{L} + 9 \big) \, V_{DD} \, f \, + 1 \, x \, 10^{-3} \, \big( C_{L} + 9 \big) \, V_{DD} \, f \, + 1 \, x \, 10^{-3} \, \big( C_{L} + 9 \big) \, V_{DD} \, f \, + 1 \, x \, 10^{-3} \, \big( C_{L} + 9 \big) \, V_{DD} \, f \, + 1 \, x \, 10^{-3} \, \big( C_{L} + 9 \big) \, V_{DD} \, f \, + 1 \, x \, 10^{-3} \, \big( C_{L} + 9 \big) \, V_{DD} \, f \, + 1 \, x \, 10^{-3} \, \big( C_{L} + 9 \big) \, V_{DD} \, f \, + 1 \, x \, 10^{-3} \, \big( C_{L} + 9 \big) \, V_{DD} \, f \, + 1 \, x \, 10^{-3} \, \big( C_{L} + 9 \big) \, V_{DD} \, f \, + 1 \, x \, 10^{-3} \, \big( C_{L} + 9 \big) \, V_{DD} \, f \, + 1 \, x \, 10^{-3} \, \big( C_{L} + 9 \big) \, V_{DD} \, f \, + 1 \, x \, 10^{-3} \, \big( C_{L} + 9 \big) \, V_{DD} \, f \, + 1 \, x \, 10^{-3} \, \big( C_{L} + 9 \big) \, V_{DD} \, f \, + 1 \, x \, 10^{-3} \, \big( C_{L} + 9 \big) \, V_{DD} \, f \, + 1 \, x \, 10^{-3} \, \big( C_{L} + 9 \big) \, V_{DD} \, f \, + 1 \, x \, 10^{-3} \, \big( C_{L} + 9 \big) \, V_{DD} \, f \, + 1 \, x \, 10^{-3} \, \big( C_{L} + 9 \big) \, V_{DD} \, f \, + 1 \, x \, 10^{-3} \, \big( C_{L} + 9 \big) \, V_{DD} \, f \, + 1 \, x \, 10^{-3} \, \big( C_{L} + 9 \big) \, V_{DD} \, f \, + 1 \, x \, 10^{-3} \, \big( C_{L} + 9 \big) \, V_{DD} \, f \, + 1 \, x \, 10^{-3} \, \big( C_{L} + 9 \big) \, V_{DD} \, f \, + 1 \, x \, 10^{-3} \, \big( C_{L} + 9 \big) \, V_{DD} \, f \, + 1 \, x \, 10^{-3} \, \big( C_{L} + 9 \big) \, V_{DD} \, f \, + 1 \, x \, 10^{-3} \, \big( C_{L} + 9 \big) \, V_{DD} \, f \, + 1 \, x \, 10^{-3} \, \big( C_{L} + 9 \big) \, V_{DD} \, f \, + 1 \, x \, 10^{-3} \, \big( C_{L} + 9 \big) \, V_{DD} \, f \, + 1 \, x \, 10^{-$$

$$1\times10^{-1}~V_{DD}^2~\left(\frac{100\%~Duty~Cycle~of~PCA_{in}}{100}~\right) + I_Q~~where:~~I_T~in~\mu\text{A},~C_L~in~p\text{F},~VCO_{in},~V_{DD}~in~Vdc,~f~in~k\text{Hz},~and~R1,~R2,~R_{SF}~in~M\Omega,~C_L~on~VCO_{out}.$$

## **ELECTRICAL CHARACTERISTICS** (Note 4) ( $C_L = 50 \text{ pF}, T_A = 25^{\circ}\text{C}$ )

| , , , , ,                                                                   |                  | V                      | Minimum |              | Maximum |           |

|-----------------------------------------------------------------------------|------------------|------------------------|---------|--------------|---------|-----------|

| Characteristic                                                              | Symbol           | V <sub>DD</sub><br>Vdc | Device  | Typical      | Device  | Units     |

| Output Rise Time                                                            | t <sub>TLH</sub> |                        |         |              |         | ns        |

| $t_{TLH} = (3.0 \text{ ns/pF}) C_L + 30 \text{ ns}$                         |                  | 5.0                    | -       | 180          | 350     |           |

| $t_{TLH} = (1.5 \text{ ns/pF}) C_L + 15 \text{ ns}$                         |                  | 10                     | _       | 90           | 150     |           |

| $t_{TLH} = (1.1 \text{ ns/pF}) C_L + 10 \text{ ns}$                         |                  | 15                     | _       | 65           | 110     |           |

| Output Fall Time                                                            | t <sub>THL</sub> |                        |         |              |         | ns        |

| $t_{THL} = (1.5 \text{ ns/pF}) C_L + 25 \text{ ns}$                         |                  | 5.0                    | -       | 100          | 175     |           |

| $t_{THL} = (0.75 \text{ ns/pF}) C_L + 12.5 \text{ ns}$                      |                  | 10                     | _       | 50           | 75      |           |

| $t_{THL} = (0.55 \text{ ns/pF}) C_L + 9.5 \text{ ns}$                       |                  | 15                     | _       | 37           | 55      |           |

| PHASE COMPARATORS 1 and 2                                                   |                  |                        |         |              |         |           |

| Input Resistance - PCA <sub>in</sub>                                        | R <sub>in</sub>  | 5.0                    | 1.0     | 2.0          | -       | $M\Omega$ |

|                                                                             |                  | 10                     | 0.2     | 0.4          | _       |           |

|                                                                             |                  | 15                     | 0.1     | 0.2          | -       |           |

| – PCB <sub>in</sub>                                                         | R <sub>in</sub>  | 15                     | 150     | 1500         | -       | МΩ        |

| Minimum Input Se-sitivity                                                   | $V_{in}$         | 5.0                    | _       | 200          | 300     | mV p–p    |

| AC Coupled — PCA <sub>in</sub>                                              |                  | 10                     | -       | 400          | 600     |           |

| C series = 1000 pF, f = 50 kHz                                              |                  | 15                     | -       | 700          | 1050    |           |

| DC Coupled – PCA <sub>in</sub> , PCB <sub>in</sub>                          | _                | 5 to 15                | See     | e Noise Immu | ınity   |           |

| VOLTAGE CONTROLLED OSCILLATOR (VCO)                                         |                  |                        |         |              |         |           |

| Maximum Frequency                                                           | f <sub>max</sub> | 5.0                    | 0.5     | 0.7          | _       | MHz       |

| $(VCO_{in} = V_{DD}, C1 = 50 pF$                                            |                  | 10                     | 1.0     | 1.4          | _       |           |

| R1 = 5.0 kΩ, and R2 = $\infty$ )                                            |                  | 15                     | 1.4     | 1.9          | -       |           |

| Temperature – Frequency Stability                                           | _                | 5.0                    | _       | 0.12         | _       | %/°C      |

| (R2 = ∞ )                                                                   |                  | 10                     | _       | 0.04         | _       |           |

|                                                                             |                  | 15                     | _       | 0.015        | -       |           |

| Linearity (R2 = ∞)                                                          | -                |                        |         |              |         | %         |

| $(VCO_{in}$ = 2.5 V $\pm$ 0.3 V, R1 > 10 k $\Omega$ )                       |                  | 5.0                    | -       | 1.0          | _       |           |

| $(VCO_{in} = 5.0 \text{ V} \pm 2.5 \text{ V}, R1 > 400 \text{ k}\Omega)$    |                  | 10                     | -       | 1.0          | _       |           |

| $(VCO_{in} = 7.5 V \pm 5.0 V, R1 \ge 1000 kΩ)$                              |                  | 15                     | _       | 1.0          | _       |           |

| Output Duty Cycle                                                           | -                | 5 to 15                | _       | 50           | -       | %         |

| Input Resistance – VCO <sub>in</sub>                                        | R <sub>in</sub>  | 15                     | 150     | 1500         | -       | MΩ        |

| SOURCE-FOLLOWER                                                             |                  |                        |         |              |         |           |

| Offset Voltage                                                              | -                | 5.0                    | -       | 1.65         | 2.2     | V         |

| (VCO <sub>in</sub> minus SF <sub>out</sub> , RSF > 500 k $\Omega$ )         |                  | 10                     | -       | 1.65         | 2.2     |           |

|                                                                             |                  | 15                     | _       | 1.65         | 2.2     |           |

| Linearity                                                                   | -                |                        |         |              |         | %         |

| $(VCO_{in} = 2.5 V \pm 0.3 V, R_{SF} > 50 k\Omega)$                         |                  | 5.0                    | _       | 0.1          | _       |           |

| $(VCO_{in} = 5.0 \text{ V} \pm 2.5 \text{ V}, R_{SF} > 50 \text{ k}\Omega)$ |                  | 10                     | -       | 0.6          | _       |           |

| $(VCO_{in} = 7.5 \text{ V} \pm 5.0 \text{ V}, R_{SF} > 50 \text{ k}\Omega)$ |                  | 15                     | _       | 0.8          | _       |           |

| ZENER DIODE                                                                 | 1                |                        | 1       | T            |         |           |

| Zener Voltage (I <sub>z</sub> = 50 μA)                                      | V <sub>Z</sub>   | -                      | 6.7     | 7.0          | 7.3     | V         |

| Dynamic Resistance ( $I_z = 1.0 \text{ mA}$ )                               | $R_Z$            | -                      | _       | 100          | -       | Ω         |

|                                                                             |                  |                        |         |              |         |           |

<sup>4.</sup> The formula given is for the typical characteristics only.

## **ORDERING INFORMATION**

| Device        | Package                 | Shipping <sup>†</sup>    |

|---------------|-------------------------|--------------------------|

| MC14046BCPG   | PDIP-16<br>(Pb-Free)    | 500 Units / Rail         |

| MC14046BDWG   | SOIC-16 WB<br>(Pb-Free) | 47 Units / Tube          |

| MC14046BDWR2G | SOIC-16 WB<br>(Pb-Free) | 1000 Units / Tape & Reel |

| MC14046BFELG  | SOEIAJ-16<br>(Pb-Free)  | 2000 Units / Tape & Reel |

| MC14046BFG    | SOEIAJ-16<br>(Pb-Free)  | 50 Units / Rail          |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

Refer to Waveforms in Figure 3.

Figure 1. Phase Comparators State Diagrams

| Characteristic                                                                                                                                                                                                                                                                                         | Using Phase Comparator 1                                                                                                                                                             | Using Phase Comparator 2                                            |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|--|

| No signal on input PCA <sub>in</sub> .                                                                                                                                                                                                                                                                 | VCO in PLL system adjusts to center frequency (f <sub>0</sub> ).                                                                                                                     | VCO in PLL system adjusts to minimum frequency (f <sub>min</sub> ). |  |

| Phase angle between PCA <sub>in</sub> and PCB <sub>in</sub> .                                                                                                                                                                                                                                          | 90° at center frequency (f <sub>0</sub> ), approaching 0° and 180° at ends of lock range (2f <sub>L</sub> )                                                                          | Always 0° in lock (positive rising edges).                          |  |

| Locks on harmonics of center frequency.                                                                                                                                                                                                                                                                | Yes                                                                                                                                                                                  | No                                                                  |  |

| Signal input noise rejection.                                                                                                                                                                                                                                                                          | High                                                                                                                                                                                 | Low                                                                 |  |

| Lock frequency range (2f <sub>L</sub> ).                                                                                                                                                                                                                                                               | The frequency range of the input signal on which the loop will stay locked if it was initially in lock; $2f_L = \text{full VCO frequency range} = f_{\text{max}} - f_{\text{min}}$ . |                                                                     |  |

| Capture frequency range (2f <sub>C</sub> ).                                                                                                                                                                                                                                                            | The frequency range of the input signal on which the loop will lock if it was initially out of lock.                                                                                 |                                                                     |  |

|                                                                                                                                                                                                                                                                                                        | Depends on low–pass filter characteristics (see Figure 3). $f_C \le f_L$                                                                                                             | $f_C = f_L$                                                         |  |

| Center frequency (f <sub>0</sub> ).                                                                                                                                                                                                                                                                    | The frequency of VCO <sub>out</sub> , when VCO <sub>in</sub> = 1/2                                                                                                                   | V <sub>DD</sub>                                                     |  |

| VCO output frequency (f).                                                                                                                                                                                                                                                                              | $f_{min} = \frac{1}{R_2(C_1 + 32 \text{ pF})}$ (Vo                                                                                                                                   | CO input = V <sub>SS</sub> )                                        |  |

| Note: These equations are intended to be a design guide. Since calculated component values may be in error by as much as a factor of 4, laboratory experimentation may be required for fixed designs. Part to part frequency variation with identical passive components is typically less than ± 20%. | $f_{max} = \frac{1}{R_1(C_1 + 32 \text{ pF})} + f_{min} \qquad (V_0)$ Where: $10K \le R_1 \le 1 \text{ M}$ $10K \le R_2 \le 1 \text{ M}$ $100\text{pF} \le C_1 \le .01 \mu\text{F}$  | <sub>CO</sub> input = V <sub>DD</sub> )                             |  |

Figure 2. Design Information

Typically:

$$\begin{aligned} &R_4\,C_2 &= \frac{6N}{f_{max}} - \frac{N}{2\,\pi\,\Delta\,f} \\ &(R_3\,+\,3,000\Omega)\,C_2 &= \frac{100N\Delta f}{f_{max}2} - R_4\,C_2 \\ &\Delta\,f = f_{max} - f_{min} \end{aligned}$$

NOTE: Sometimes R3 is split into two series resistors each R3  $\div$  2. A capacitor  $C_C$  is then placed from the midpoint to ground. The value for  $C_C$  should be such that the corner frequency of this network does not significantly affect  $\Omega_n$ . In Figure B, the ratio of R3 to R4 sets the damping, R4  $\cong$  (0.1)(R3) for optimum results.

Definitions: N = Total division ratio in feedback loop

$K\phi = V_{DD}/\pi$  for Phase Comparator 1  $K\phi = V_{DD}/4$   $\pi$  for Phase Comparator 2

$$\begin{split} \text{K}_{VCO} &= \frac{2 \, \pi \, \Delta \, \text{f}_{VCO}}{\text{V}_{DD} - 2 \, \text{V}} \\ \text{for a typical design } \Omega_n &\cong \frac{2 \, \pi \, \text{f}_r}{10} \quad \text{(at phase detector input)} \\ \zeta &\cong 0.707 \end{split}$$

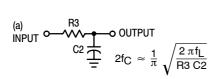

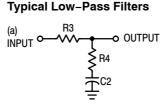

### I OW-PASS FILTER

| LOW-I AGG I ILI LII                                       |                                                                                                                |  |  |  |

|-----------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|--|--|--|

| Filter A                                                  | Filter B                                                                                                       |  |  |  |

| $\omega_{n} = \sqrt{\frac{K_{\varphi}KVCO}{NR_{3}C_{2}}}$ | $\omega_{n} = \sqrt{\frac{K_{\varphi}KVCO}{NC_{2}(R_{3} + R_{4})}}$                                            |  |  |  |

| $\zeta = \frac{N\omega_n}{2K_{\varphi}K_{VCO}}$           | $\zeta = 0.5 \omega_{\text{n}} (\text{R}_3\text{C}_2 + \frac{\text{N}}{\text{K}_{\phi}\text{K}_{\text{VCO}}})$ |  |  |  |

| $F(s) = \frac{1}{R_3 C_2 S + 1}$                          | $F(s) = \frac{R_3C_2S + 1}{S(R_3C_2 + R_4C_2) + 1}$                                                            |  |  |  |

### Waveforms

Note: for further information, see:

- (1) F. Gardner, "Phase-Lock Techniques", John Wiley and Son, New York, 1966.

- (2) G. S. Moschytz, "Miniature RC Filters Using Phase-Locked Loop", BSTJ, May, 1965.

- (3) Garth Nash, "Phase-Lock Loop Design Fundamentals", AN-535, Motorola Inc.

- (4) A. B. Przedpelski, "Phase-Locked Loop Design Articles", AR254, reprinted by Motorola Inc.

Figure 3. General Phase-Locked Loop Connections and Waveforms

#### PACKAGE DIMENSIONS

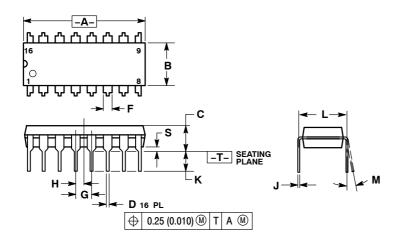

## PDIP-16 **P SUFFIX** PLASTIC DIP PACKAGE CASE 648-08 ISSUE T

#### NOTES:

- DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982. CONTROLLING DIMENSION: INCH. DIMENSION L TO CENTER OF LEADS WHEN FORMED PARALLEL.

- DIMENSION B DOES NOT INCLUDE MOLD FLASH.

- ROUNDED CORNERS OPTIONAL.

|     | INC   | HES   | MILLIMETER |       |

|-----|-------|-------|------------|-------|

| DIM | MIN   | MAX   | MIN        | MAX   |

| Α   | 0.740 | 0.770 | 18.80      | 19.55 |

| В   | 0.250 | 0.270 | 6.35       | 6.85  |

| С   | 0.145 | 0.175 | 3.69       | 4.44  |

| D   | 0.015 | 0.021 | 0.39       | 0.53  |

| F   | 0.040 | 0.70  | 1.02       | 1.77  |

| G   | 0.100 | BSC   | 2.54 BSC   |       |

| Н   | 0.050 | BSC   | 1.27 BSC   |       |

| J   | 0.008 | 0.015 | 0.21       | 0.38  |

| K   | 0.110 | 0.130 | 2.80       | 3.30  |

| L   | 0.295 | 0.305 | 7.50       | 7.74  |

| М   | 0°    | 10 °  | 0°         | 10 °  |

| S   | 0.020 | 0.040 | 0.51       | 1.01  |

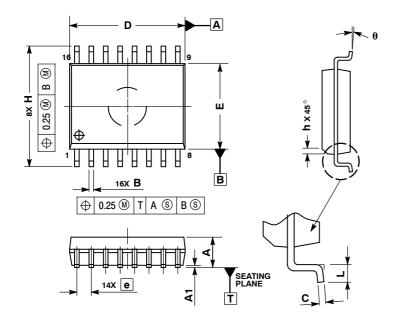

## SOIC-16 WB **DW SUFFIX** PLASTIC SOIC PACKAGE CASE 751G-03 ISSUE C

- NOTES:

1. DIMENSIONS ARE IN MILLIMETERS.

2. INTERPRET DIMENSIONS AND TOLERANCES PER ASME Y14.5M, 1994.

3. DIMENSIONS D AND E DO NOT INLCUDE MOLD PROTRUSION.

4. MAXIMUM MOLD PROTRUSION 0.15 PER SIDE.

- MAXIMUM MOLD PHOTH RUSION 0.15 PER 1984

DIMENSION B DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.13 TOTAL IN EXCESS OF THE B DIMENSION AT MAXIMUM MATERIAL CONDITION.

|     | MILLIMETERS |       |  |  |

|-----|-------------|-------|--|--|

| DIM | MIN         | MAX   |  |  |

| Α   | 2.35        | 2.65  |  |  |

| A1  | 0.10        | 0.25  |  |  |

| В   | 0.35        | 0.49  |  |  |

| С   | 0.23        | 0.32  |  |  |

| D   | 10.15       | 10.45 |  |  |

| Е   | 7.40        | 7.60  |  |  |

| е   | 1.27        | BSC   |  |  |

| Н   | 10.05       | 10.55 |  |  |

| h   | 0.25        | 0.75  |  |  |

| L   | 0.50        | 0.90  |  |  |

| a   | 0 °         | 7 °   |  |  |

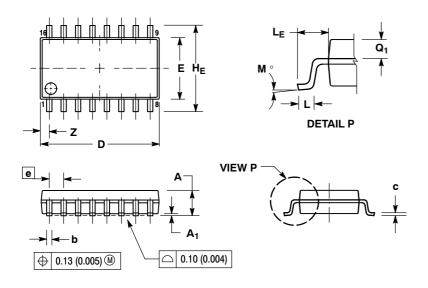

## PACKAGE DIMENSIONS

SOEIAJ-16 **F SUFFIX** CASE 966-01 **ISSUE A**

- DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

- CONTROLLING DIMENSION: MILLIMETER DIMENSIONS D AND E DO NOT INCLUDE MOLD FLASH OR PROTRUSIONS AND ARE

MEASURED AT THE PARTING LINE. MOLD FLASH

OR PROTRUSIONS SHALL NOT EXCEED 0.15

(0.006) PER SIDE.

- TERMINAL NUMBERS ARE SHOWN FOR REFERENCE ONLY.

- i. THE LEAD WIDTH DIMENSION (b) DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.08 (0.003) TOTAL IN EXCESS OF THE LEAD WIDTH

DIMENSION AT MAXIMUM MATERIAL CONDITION. DAMBAR CANNOT BE LOCATED ON THE LOWER RADIUS OR THE FOOT. MINIMUM SPACE BETWEEN PROTRUSIONS AND ADJACENT LEAD TO BE 0.46 ( 0.018).

|                | MILLIN | IETERS | INC   | HES   |

|----------------|--------|--------|-------|-------|

| DIM            | MIN    | MAX    | MIN   | MAX   |

| Α              |        | 2.05   |       | 0.081 |

| A <sub>1</sub> | 0.05   | 0.20   | 0.002 | 0.008 |

| b              | 0.35   | 0.50   | 0.014 | 0.020 |

| C              | 0.10   | 0.20   | 0.007 | 0.011 |

| D              | 9.90   | 10.50  | 0.390 | 0.413 |

| Ε              | 5.10   | 5.45   | 0.201 | 0.215 |

| е              | 1.27   | BSC    | 0.050 | BSC   |

| HE             | 7.40   | 8.20   | 0.291 | 0.323 |

| L              | 0.50   | 0.85   | 0.020 | 0.033 |

| LE             | 1.10   | 1.50   | 0.043 | 0.059 |

| M              | 0 °    | 10°    | 0 °   | 10 °  |

| $Q_1$          | 0.70   | 0.90   | 0.028 | 0.035 |

| Z              |        | 0.78   |       | 0.031 |

ON Semiconductor and un are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice on semiconductor and are registered readerlands of semiconductor Components industries, Ite (SCILLC) and the series are injected to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

### **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA **Phone**: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com

N. American Technical Support: 800-282-9855 Toll Free USA/Canada

Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910

Japan Customer Focus Center Phone: 81-3-5773-3850

ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative

MC14046B/D