# Is Now Part of

# ON Semiconductor®

# To learn more about ON Semiconductor, please visit our website at www.onsemi.com

Please note: As part of the Fairchild Semiconductor integration, some of the Fairchild orderable part numbers will need to change in order to meet ON Semiconductor's system requirements. Since the ON Semiconductor product management systems do not have the ability to manage part nomenclature that utilizes an underscore (\_), the underscore (\_) in the Fairchild part numbers will be changed to a dash (-). This document may contain device numbers with an underscore (\_). Please check the ON Semiconductor website to verify the updated device numbers. The most current and up-to-date ordering information can be found at <a href="www.onsemi.com">www.onsemi.com</a>. Please email any questions regarding the system integration to <a href="mailto:Fairchild\_questions@onsemi.com">Fairchild\_questions@onsemi.com</a>.

ON Semiconductor and the ON Semiconductor logo are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officers, employees

March 2013

# FSA9280A USB Port Multimedia Switch Featuring Automatic Select and Accessory Detection

#### **Features**

| Signals          | Audio, USB, UART, USB Charging     |  |  |  |  |  |  |

|------------------|------------------------------------|--|--|--|--|--|--|

| Switch           | Automatic Switching with           |  |  |  |  |  |  |

| Mechanism        | Available Interrupt                |  |  |  |  |  |  |

|                  | Headsets (Headphone/MIC/Remote)    |  |  |  |  |  |  |

|                  | USB Data Port (SDP)                |  |  |  |  |  |  |

| Accessory        | UART Serial Link                   |  |  |  |  |  |  |

| Detection        | USB Chargers (Car-Kit, CDP, DCP)   |  |  |  |  |  |  |

|                  | Factory-Mode                       |  |  |  |  |  |  |

|                  | TTY Converter                      |  |  |  |  |  |  |

| USB              | FS and HS 2.0 Compliant            |  |  |  |  |  |  |

|                  | Battery Charging 1.1 Compliant     |  |  |  |  |  |  |

|                  | (Including Optional DCD)           |  |  |  |  |  |  |

| USB Charging     | Integrated Power FET               |  |  |  |  |  |  |

| oob onarging     | Over-Voltage Tolerance (OVT) 28V   |  |  |  |  |  |  |

|                  | Over-Current Protection (OCP) 1.5A |  |  |  |  |  |  |

|                  | Over-Voltage Protection (OVP) 6.8V |  |  |  |  |  |  |

| Audio            | Left, Right, MIC, TTY              |  |  |  |  |  |  |

| V <sub>BAT</sub> | 3 to 4.4V                          |  |  |  |  |  |  |

| Programmability  | I <sup>2</sup> C                   |  |  |  |  |  |  |

| ESD              | 15kV IEC 61000-4-2 Air Gap         |  |  |  |  |  |  |

| Dookogo          | 20-Lead UMLP                       |  |  |  |  |  |  |

| Package          | (3 x 4 x 0.55mm, 0.5mm Pitch)      |  |  |  |  |  |  |

| Ordering         | FSA9280AUMX                        |  |  |  |  |  |  |

| Information      | 1 5/15250A0WIX                     |  |  |  |  |  |  |

# **Description**

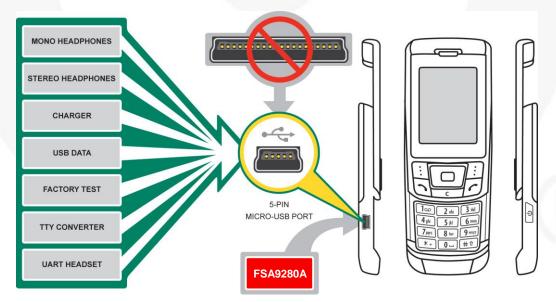

The FSA9280A is a high-performance multimedia switch featuring automatic switching and accessory detection for the USB port. This switch allows sharing of a common USB port to pass audio, USB data / charging, as well as factory programmability. In addition, the FSA9280A integrates detection of accessories; such as headphones, headsets (MIC / button), car chargers, USB chargers, and UART data cables; with the ability to use a common USB connector. The FSA9280A can be programmed for manual or automatic switching of data paths based on accessory detected. FSA9280A includes an integrated 28V over-voltage and 1.5A over-current protected FET.

# **Applications**

Mobile Phones & Portable Media Players

#### **Related Resources**

- FSA9280A Evaluation Board

- Evaluation Board Users Guide

- For samples, questions or board requests; please contact analogswitch @fairchildsemi.com

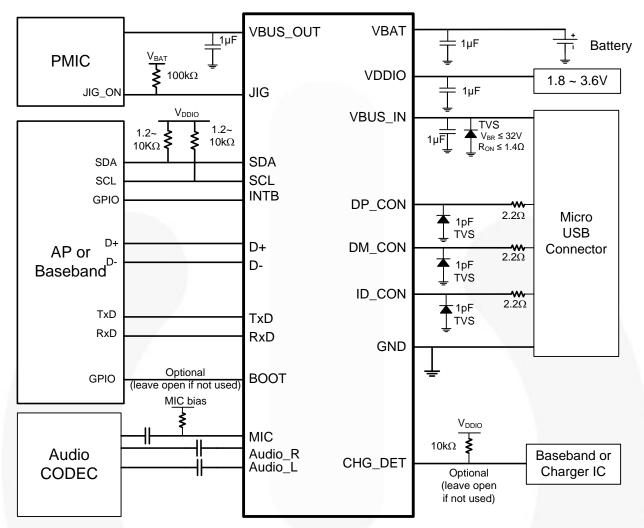

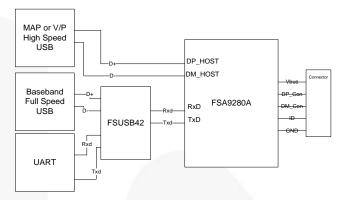

Figure 1. Typical Application

# **Table of Contents**

| Fea | itures.          |                                                               | 1  |

|-----|------------------|---------------------------------------------------------------|----|

| Des | criptio          | n                                                             | 1  |

| App | olication        | ns                                                            | 1  |

| Rel | ated R           | esources                                                      | 1  |

| Tab | le of C          | Contents                                                      | 2  |

| Blo | ck Diag          | gram                                                          | 3  |

| Pin | Config           | juration                                                      | 3  |

| Pin | Descri           | ptions                                                        | 4  |

| 1.  | Funct            | ionality                                                      | 5  |

|     | 1.1.             | Functional Overview                                           | 5  |

| 2.  | Powe             | r-up & Reset                                                  | 6  |

|     | 2.1.             | Reset                                                         | 6  |

|     |                  | 2.1.1. Hardware Reset                                         | 6  |

|     |                  | 2.1.2. Software Reset                                         | 6  |

| 3.  | I <sup>2</sup> C |                                                               | 7  |

| 4.  | Confi            | guration                                                      | 8  |

| 5.  | Detec            | etion                                                         | 8  |

|     | 5.1.             | USB Port Detection                                            | 10 |

|     | 5.2.             | Audio Accessory Detection                                     | 12 |

|     | 5.3.             | OCP and OVP Detection                                         | 13 |

| 6.  | Proce            | essor Communication                                           | 13 |

| 7.  | Switc            | h Configuration                                               | 13 |

|     | 7.1.             | Manual Switching                                              | 14 |

| 8.  | Active           | e Signal Performance                                          | 15 |

|     | 8.1.             | USB Data                                                      | 15 |

|     | 8.2.             | FS USB                                                        | 15 |

|     | 8.3.             | Audio                                                         | 15 |

| 9.  | Electr           | rical Specifications                                          | 16 |

|     | 9.1.             | Absolute Maximum Ratings                                      | 16 |

|     | 9.2.             | Recommended Operating Conditions                              | 16 |

|     | 9.3.             | Switch Path DC Electrical Characteristics                     | 16 |

|     | 9.4.             | Capacitance                                                   | 18 |

|     | 9.5.             | Switch Path AC Electrical Characteristics                     | 18 |

|     | 9.6.             | I <sup>2</sup> C Controller DC Characteristics                | 19 |

|     | 9.7.             | I <sup>2</sup> C AC Electrical Characteristics & Register Map | 19 |

|     | 9.8.             | Factory Modes                                                 | 23 |

|     |                  | 9.8.1. Factory-Mode Accessory Detection                       | 23 |

| 10. | Refer            | ence Schematic                                                | 26 |

| 11. | Layou            | ut Guidelines                                                 | 27 |

|     | 11.1.            | PCB Layout Guidelines for High-Speed USB Signal Integrity     | 27 |

|     | 11.2.            | Layout for GSM/TDMA Buzz Reduction                            | 27 |

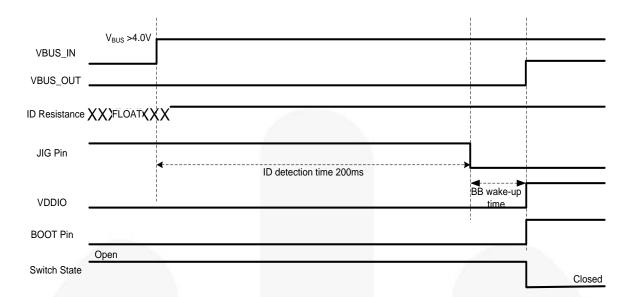

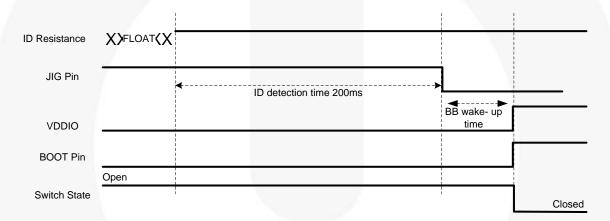

|     | 11.3.            | V <sub>BUS_OUT</sub> Load Timing Requirements                 | 27 |

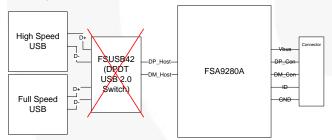

|     | 11.4.            | Systems with Multiple USB Controllers                         | 28 |

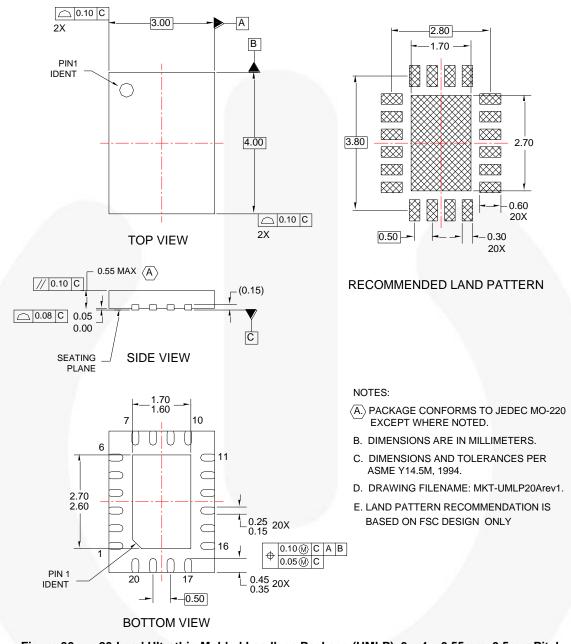

| Phy | sical E          | Dimensions                                                    | 29 |

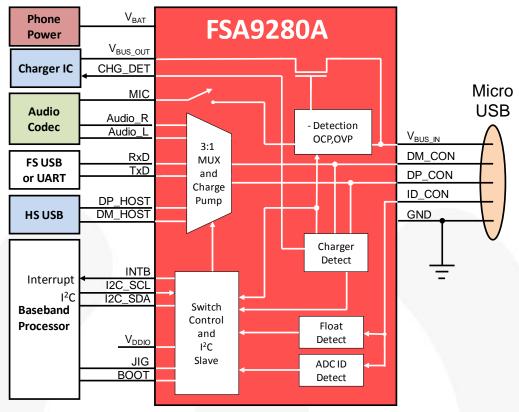

# **Block Diagram**

Figure 2. Block Diagram

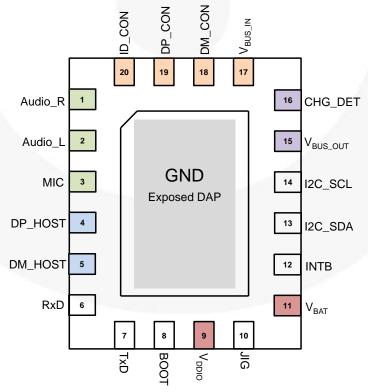

# **Pin Configuration**

Figure 3. Pin Assignments (Top View)

# **Pin Descriptions**

| Name                       | Pin #                    | Туре                 | Default<br>State | Description                                                                                                                                                                            |

|----------------------------|--------------------------|----------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| USB Interfac               | е                        |                      |                  |                                                                                                                                                                                        |

| DP_HOST                    | 4                        | Signal Path          | Open             | D+ signal switch path, dedicated USB port to be connected to the resident USB transceiver on the phone                                                                                 |

| DM_HOST                    | 5                        | Signal Path          | Open             | D- signal switch path, dedicated USB port to be connected to the resident USB transceiver on the phone                                                                                 |

| Audio Interfa              | ace                      |                      |                  |                                                                                                                                                                                        |

| Audio_L                    | 2                        | Signal Path          | Open             | Left audio channel from mobile phone audio-out CODEC                                                                                                                                   |

| Audio_R                    | 1                        | Signal Path          | Open             | Right audio channel from mobile phone audio-out CODEC                                                                                                                                  |

| MIC                        | 3                        | Signal Path          | Open             | Connected to the mobile phone audio CODEC MIC input pin                                                                                                                                |

| UART Interfa               | ice                      |                      |                  |                                                                                                                                                                                        |

| TxD                        | 7                        | Signal Path          | Open             | Transmitter (Tx) from resident UART on the mobile phone                                                                                                                                |

| RxD                        | 6                        | Signal Path          | Open             | Receiver (Rx) from resident UART on the mobile phone                                                                                                                                   |

| Connector Ir               | nterface                 |                      |                  |                                                                                                                                                                                        |

| ID_CON                     | 20                       | Signal Path          | Open             | Connected to the USB connector ID pin and used for detecting accessories or button presses                                                                                             |

| DP_CON                     | 19                       | Signal Path          | Open             | Connected to the USB connector D+ pin; depending on the signaling mode, this pin can be switched to DP_HOST, Audio_R, or RxD pins                                                      |

| DM_CON                     | 18                       | Signal Path          | Open             | Connected to the USB connector D- pin; depending on the signaling mode, this pin can switched to DM_HOST, Audio_L, or TxD pins                                                         |

| V <sub>BUS_IN</sub>        | 17                       | Power Path           | N/A              | Input voltage supply pin to be connected to the V <sub>BUS</sub> pin of the USB connector                                                                                              |

| Power Interf               | ace                      |                      |                  |                                                                                                                                                                                        |

| V <sub>BAT</sub>           | 11                       | Power                | N/A              | Input voltage supply pin to be connected to the mobile phone battery output or to an internal regulator on the phone                                                                   |

| $V_{DDIO}$                 | 9                        | Power                | N/A              | Baseband processor interface I/O supply pin                                                                                                                                            |

| GND                        | Exposed<br>Center<br>Pad | Ground               | N/A              | Ground (center ground pad of package makes electrical contact)                                                                                                                         |

| Charger Inte               | rface                    |                      |                  |                                                                                                                                                                                        |

| V <sub>BUS_OUT</sub>       | 15                       | Power Path           | N/A              | Output voltage supply pin to be connected to the source voltage pin on the charger IC                                                                                                  |

| CHG_DET                    | 16                       | Open-Drain<br>Output | Hi-Z             | Open-drain active LOW output, used to signal the charger IC that a charger has been attached                                                                                           |

| Factory Inter              | face                     |                      |                  |                                                                                                                                                                                        |

| JIG                        | 10                       | Open-Drain<br>Output | Hi-Z             | Output control signal driven by the FSA9280A and used by the processor for factory test modes                                                                                          |

| воот                       | 8                        | CMOS<br>Output       | LOW              | Output control signal driven by the FSA9280A and used by the processor for factory test modes                                                                                          |

| I <sup>2</sup> C Interface |                          |                      |                  |                                                                                                                                                                                        |

| I2C_SCL                    | 14                       | Input                | Hi-Z             | I <sup>2</sup> C serial clock signal to be connected to the phone-based I <sup>2</sup> C master                                                                                        |

| I2C_SDA                    | 13                       | Open-Drain<br>I/O    | Hi-Z             | I <sup>2</sup> C serial data signal to be connected to the phone-based I <sup>2</sup> C master                                                                                         |

| INTB                       | 12                       | CMOS<br>Output       | LOW              | Interrupt active LOW output used to prompt the phone baseband processor to read the I <sup>2</sup> C register bits, indicates a change in ID_CON pin status or accessory attach status |

# 1. Functionality

The FSA9280A offers a complete solution for a single 5-pin USB interface. Through built-in detection algorithms that monitor the ID and  $V_{\text{BUS}}$  pins of the USB interface, the FSA9280A allows seamless sharing of the interface between HS USB, FS USB or UART, and audio sources. The FSA9280A also offers a complete solution for multiple types of USB chargers. The FSA9280A detects different USB charger types and has a dedicated charger IC interface to allow charging through the devices and dynamic current control by the charger IC based on the type of charger detected. Additional over-current protection (OCP) and up to 28V over-voltage tolerance (OVT) is provided.

The detection features are capable of monitoring the ID pin of the USB interface to detect a full array of USB accessories, including audio accessories with up to 12 buttons.

#### 1.1. Functional Overview

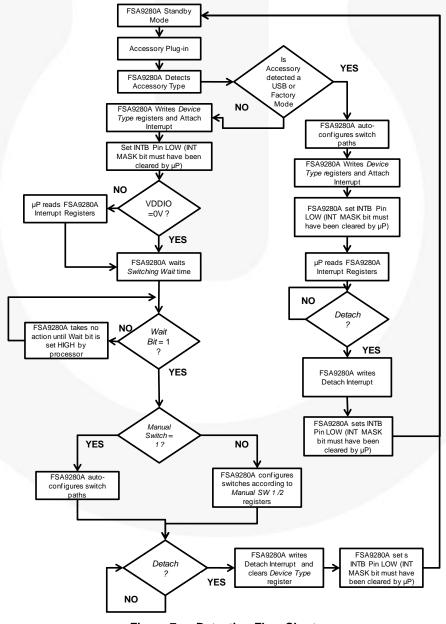

The FSA9280A is designed for minimal software requirements for proper operation. The flow diagram below shows the basic steps of operation and contains references to more detailed information.

|   | Flow Diagram                                          |  | State                      | Datasheet<br>Section | Description                                                                                                       |

|---|-------------------------------------------------------|--|----------------------------|----------------------|-------------------------------------------------------------------------------------------------------------------|

|   | Power-up & Reset                                      |  | Power-up & Reset           | Section 2            | Applying power to the device and reset states of the device.                                                      |

|   | I <sup>2</sup> C                                      |  | I <sup>2</sup> C           | Section 3            | Communication with device through I <sup>2</sup> C (which can be bypassed during power-up).                       |

| _ | Configuration  Accessory Plug-in                      |  | Configuration              | Section 4            | Configuring the device using I <sup>2</sup> C and the internal registers (which can be bypassed during power-up). |

|   | Detection                                             |  | Detection                  | Section 5            | How the detection of the accessory is done including attachment and detachment.                                   |

|   | Processor<br>Communication<br>Switch<br>Configuration |  | Processor<br>Communication | Section 6            | How the detection of the accessory is indicated to the processor.                                                 |

|   | Active Signals                                        |  | Switch<br>Configuration    | Section 7            | Configuration of switches based on detection.                                                                     |

|   | Accessory<br>Detached                                 |  | Active Signal              | Section 8            | Signal performance of selected configuration                                                                      |

# 2. Power-up & Reset

The FSA9280A does not need special power sequencing for correct operation. The main power of the device is provided by either  $V_{\text{BUS\_IN}}$  or  $V_{\text{BAT}}$ . If  $V_{\text{BUS\_IN}}$  is not present and  $V_{\text{BAT}}$  is applied,  $V_{\text{BAT}}$  is used to power the device.  $V_{\text{DDIO}}$  is only used for I<sup>2</sup>C interface and interrupt processing.

Table 1 summarizes the enabled features of each power state of the FSA9280A. The valid voltages levels for each power supply can be found in Section 9.2.

Table 1 - Power States Summary

| Valid                        | Valid            | Valid                            | Power                            | Enabled Functionality |                                                         |           |  |  |

|------------------------------|------------------|----------------------------------|----------------------------------|-----------------------|---------------------------------------------------------|-----------|--|--|

| Valid<br>V <sub>BUS_IN</sub> | V <sub>BAT</sub> | V <sub>DDIO</sub> <sup>(1)</sup> | State                            | Charging through FET  | Processor Communication (I <sup>2</sup> C & Interrupts) | Detection |  |  |

| NO                           | NO               | NO                               | Power Down                       | NO                    | NO                                                      | NO        |  |  |

| NO                           | NO               | YES <sup>(2)</sup>               |                                  | ILLEGAL STATE         |                                                         |           |  |  |

| NO                           | YES              | NO                               | Powered from V <sub>BAT</sub>    | NO                    | NO                                                      | YES       |  |  |

| NO                           | YES              | YES                              | Powered from V <sub>BAT</sub>    | NO                    | YES                                                     | YES       |  |  |

| YES                          | NO               | NO                               | Powered from V <sub>BUS_IN</sub> | Yes                   | NO                                                      | YES       |  |  |

| YES                          | YES              | NO                               | Powered from V <sub>BAT</sub>    | YES                   | NO                                                      | YES       |  |  |

| YES                          | NO               | YES <sup>(2)</sup>               | Powered from V <sub>BUS_IN</sub> | YES                   | YES                                                     | YES       |  |  |

| YES                          | YES              | YES                              | Powered from V <sub>BAT</sub>    | YES                   | YES                                                     | YES       |  |  |

#### Notes:

- 1. V<sub>DDIO</sub> is expected to be the same supply used by the baseband I/O's.

- This is not a typical state: both V<sub>BAT</sub> and V<sub>DDIO</sub> are typically provided simultaneously.

#### 2.1. Reset

When the device is reset, all the registers are initialized to the default values shown in Table 7 and all switch paths are open. After reset or power up, the FSA9280A enters Standby Mode and is ready to detect accessories sensed on its  $V_{\text{BUS\_IN}}$  and / or ID\_CON pins.

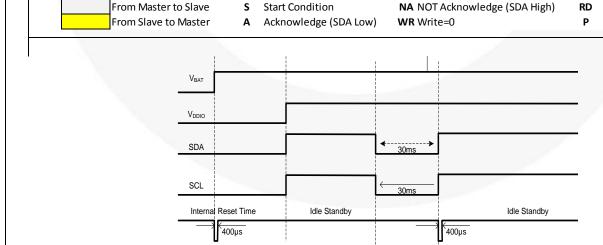

#### 2.1.1. Hardware Reset

There are three hardware reset mechanisms:

- Power-on reset caused by the initial rising edge of V<sub>BUS</sub> or V<sub>BAT</sub>

- The falling edge of V<sub>DDIO</sub>.

With V<sub>DDIO</sub> valid, driving both I2C\_SDA and I2C\_SCL signals LOW for at least 30ms.

#### Note:

I<sup>2</sup>C controllers that implement clock stretching could cause reset. In this case, GPIOs could be used for the I<sup>2</sup>C interface.

#### 2.1.2. Software Reset

The device can be reset through software by writing to the Reset bit in the Register (1BH).

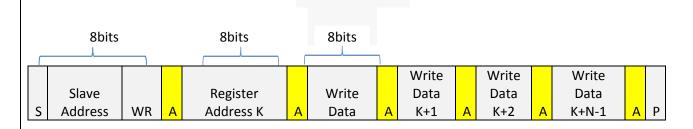

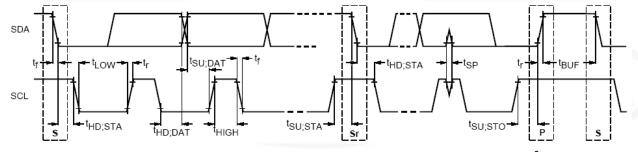

# 3. I<sup>2</sup>C

The FSA9280A integrates a fast-mode  $I^2C$  slave controller compliant with the  $I^2C$  specification version 2.1 requirements. The FSA9280A  $I^2C$  interface runs up to 400KHz.

The slave address is shown in Table 2. Status information and configuration occurs via the I<sup>2</sup>C interface.

Please see Section 9.7 for more information.

Table 2 - I<sup>2</sup>C Slave Address

| Name          | Size (Bits) | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0        |

|---------------|-------------|-------|-------|-------|-------|-------|-------|-------|--------------|

| Slave Address | 8           | 0     | 1     | 0     | 0     | 1     | 0     | 1     | Read / Write |

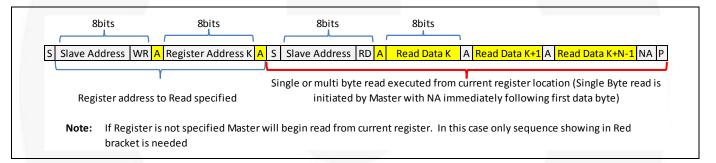

**Note:** Single Byte write is initiated by Master with P immediately following first data byte.

Figure 4. I<sup>2</sup>C Write Sequence

Figure 6. I<sup>2</sup>C Reset Mode Timing

Read =1

**Stop Condition**

# 4. Configuration

FSA9280A requires minimal configuration for proper detection and reporting. The following steps can be followed for full configuration. In many cases, only Step 5 needs to be implemented for proper operation.

- 1. Write Control register (02h) to configure different switching configurations and wait timing.

- Write Interrupt Mask 1 and 2 registers (05h, 06h) to mask any interrupts not required in the application.

- 3. Write Timing Set 1 (08h) register to program required key-press timing and ADC-detection timing.

- 4. Write Timing Set 2 (09h) register to program required Switching Wait timing and Long Key Press timing.

- 5. Write Control register (02h) to clear INT Mask bit. This enables interrupts to the baseband.

#### 5. Detection

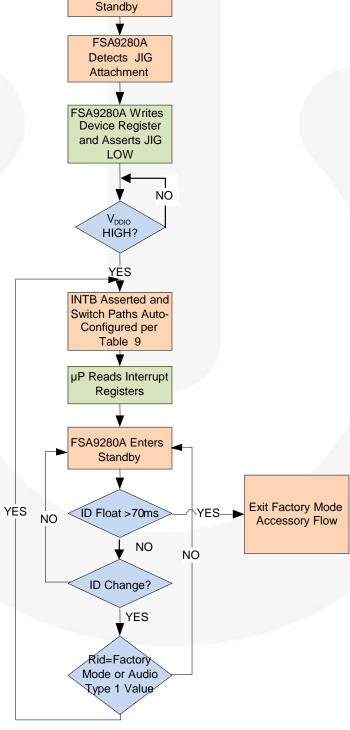

The FSA9280A detection algorithms monitor both the  $V_{\text{BUS}}$  and ID pins of the USB interface. Based on the detection results, multiple registers are updated and the INTB pin is asserted to indicate to the baseband processor that an accessory was detected and to read the registers for the complete information.

The detection algorithm allows the application to control the timing of the detection algorithm and the configuration of the internal switches. The flow diagram in Figure 7 shows the operation of the detection algorithm.

Figure 7. Detection Flow Chart

The FSA9280A monitors both  $V_{BUS\_IN}$  and ID\_CON to detect accessories. The ID\_CON detection is a "resistive detection" that detects the resistance to GND on the ID\_CON pin to

determine which accessory is attached. Table 3 shows the assignment of accessories based on resistor values.

Table 3. ID\_CON Accessory Detection

| Binary Value <sup>(4)</sup> | ID_CO                      | N Resistance t      | o GND   | Accessory Detected <sup>(5)</sup>             |

|-----------------------------|----------------------------|---------------------|---------|-----------------------------------------------|

| Diliary Value               | Min.                       | Тур.                | Max.    | Accessory Detected                            |

| 00000                       | GND                        | GND                 | GND     | DO NOT USE                                    |

| 00001                       | 1.9kΩ                      | 2.0kΩ               | 2.1kΩ   | Audio Send/End Button                         |

| 00010                       | 2.470kΩ                    | 2.604kΩ             | 2.730kΩ | Audio Remote S1 Button <sup>(6)</sup>         |

| 00011                       | 3.050kΩ                    | 3.208kΩ             | 3.370kΩ | Audio Remote S2 Button <sup>(6)</sup>         |

| 00100                       | 3.810kΩ                    | 4.014kΩ             | 4.210kΩ | Audio Remote S3 Button <sup>(6)</sup>         |

| 00101                       | 4.58kΩ                     | 4.82kΩ              | 5.06kΩ  | Audio Remote S4 Button <sup>(6)</sup>         |

| 00110                       | 5.73kΩ                     | 6.03kΩ              | 6.33kΩ  | Audio Remote S5 Button <sup>(6)</sup>         |

| 00111                       | 7.63kΩ                     | 8.03kΩ              | 8.43kΩ  | Audio Remote S6 Button <sup>(6)</sup>         |

| 01000                       | 9.53kΩ                     | 10.03kΩ             | 10.53kΩ | Audio Remote S7 Button <sup>(6)</sup>         |

| 01001                       | 11.43kΩ                    | 12.03kΩ             | 12.63kΩ | Audio Remote S8 Button <sup>(6)</sup>         |

| 01010                       | 13.74kΩ                    | 14.46kΩ             | 15.18kΩ | Audio Remote S9 Button <sup>(6)</sup>         |

| 01011                       | 16.40kΩ                    | 17.26kΩ             | 18.12kΩ | Audio Remote S10 Button <sup>(6)</sup>        |

| 01100                       | 19.48kΩ                    | 20.50kΩ             | 21.53kΩ | Audio Remote S11 Button <sup>(6)</sup>        |

| 01101                       | 22.87kΩ                    | 24.07kΩ             | 25.27kΩ | Audio Remote S12 Button <sup>(6)</sup>        |

| 01110                       | 27.27kΩ                    | 28.70kΩ             | 30.14kΩ | Reserved Accessory #1                         |

| 01111                       | 32.3kΩ                     | 34.0kΩ              | 35.7kΩ  | Reserved Accessory #2                         |

| 10000                       | 38.19kΩ                    | 40.20kΩ             | 42.21kΩ | Reserved Accessory #3                         |

| 10001                       | 47.41kΩ                    | 49.90kΩ             | 52.40kΩ | Reserved Accessory #4                         |

| 10010                       | 61.66kΩ                    | 64.90kΩ             | 68.15kΩ | Reserved Accessory #5                         |

| 10011                       | 76.1kΩ                     | 80.7kΩ              | 84.1kΩ  | DO NOT USE                                    |

| 10100                       | 96.9kΩ                     | 102.0kΩ             | 107.1kΩ | DO NOT USE                                    |

| 10101                       | 115kΩ                      | 121kΩ               | 127kΩ   | TTY Converter                                 |

| 10110                       | 143kΩ                      | 150kΩ               | 157kΩ   | UART Cable                                    |

| 10111                       | 190kΩ                      | 200kΩ               | 206kΩ   | USB: See Table 4                              |

| 11000                       | 247.3kΩ                    | 255kΩ               | 262.7kΩ | Factory Mode Boot OFF-USB                     |

| 11001                       | 292kΩ                      | 301kΩ               | 310kΩ   | Factory Mode Boot ON-USB                      |

| 11010                       | 347kΩ                      | 365kΩ               | 383kΩ   | Audio Cradle                                  |

| 11011                       | 428.7kΩ                    | 442.0kΩ             | 455.3kΩ | USB: See Table 4                              |

| 11100                       | 507.3kΩ                    | 523kΩ               | 538.7kΩ | Factory Mode Boot OFF-UART                    |

| 11101                       | 600.4kΩ                    | 619kΩ               | 637.6kΩ | Factory Mode Boot ON-UART                     |

| 44440                       | 750kΩ                      | 1000kΩ              | 1050kΩ  | Audio Type 1 with Remote <sup>(8)</sup>       |

| 11110                       | 750kΩ                      | 1002kΩ              | 1050kΩ  | Audio Type 1 / Only Send-End <sup>(8)</sup>   |

| 11111                       | $20 	extsf{M}\Omega^{(7)}$ | Open <sup>(7)</sup> |         | USB Mode, Dedicated Charger or Accessory Deta |

#### Notes:

- 4. The binary values are reported in the binary register (07h) with each valid accessory detection.

- 5. The accessory type is reported in the Device Type 1 (0Bh), Device Type 2 (0Bh), Button 1 (0Ch), and Button 2 (0Dh) registers with each valid accessory detection.

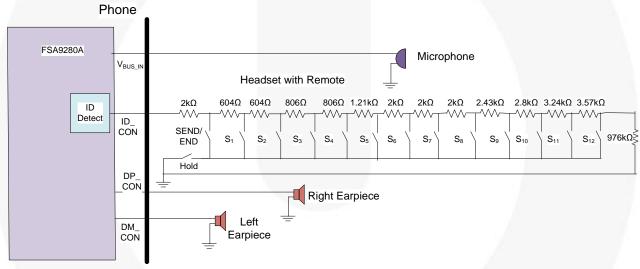

- 6. These resistor values are created by multiple standard resistor values in series to form the button presses on the wired remote (see Figure 12).

- 7. For the ID float, ID "open" is recommended; otherwise, capacitance should be minimized.

- 8. Audio devices with remote and audio devices with only send/end are both reported as Audio Type 1 in the Device Type 1 register (see the Audio Accessory Detection section below). Type 1 is for passive resistor audio accessories and a future Audio Type 2 is designated for active audio accessories.

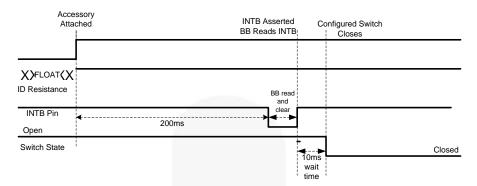

Figure 8. ID-Based Accessories, No V<sub>BUS IN</sub> Attach Timing with Default Switching Wait Bits of 10ms

#### 5.1. USB Port Detection

The multiple types of USB 2.0 ports that the FSA9280A can detect are summarized in Table 4. These devices are unique in that  $V_{\text{BUS}}$  must be present to detect these accessories.

Table 4. ID\_CON and V<sub>BUS IN</sub> Detection for USB Devices

| ADC<br>Value <sup>(9)</sup> | v                   | DP CON | DP CON | ID_CON F | Resistan | ce to GND | Accessory Detected <sup>(10)</sup>                                        |

|-----------------------------|---------------------|--------|--------|----------|----------|-----------|---------------------------------------------------------------------------|

| Value <sup>(9)</sup>        | V <sub>BUS_IN</sub> | DF_CON | DF_CON | Min.     | Тур.     | Max.      | Accessory Detected                                                        |

| 10111                       | 5V                  | X      | Χ      | 190kΩ    | 200kΩ    | 206kΩ     | Car Kit Type 1 Charger <sup>(11)</sup>                                    |

| 11011                       | 5V                  | Х      | Х      | 428.7kΩ  | 442kΩ    | 455.3kΩ   | Car Kit Type 2 Charger <sup>(11)</sup>                                    |

| 11111                       | 5V                  | (12)   | (12)   | 20ΜΩ     | Open     | Open      | USB Dedicated Charging Port, Travel<br>Adapter or Dedicated Charger (DCP) |

| 11111                       | 5V                  | (12)   | (12)   | 20ΜΩ     | Open     | Open      | USB Charging Downstream Port (CDP)                                        |

| 11111                       | 5V                  | (12)   | (12)   | 20ΜΩ     | Open     | Open      | USB Standard Downstream Port (SDP)                                        |

#### Notes:

- 9. The ADC values are reported in the ADC register (07h) with an each valid accessory detection.

- 10. The accessory type is reported in the Device Type 1 (0Bh) and Car Kit Status (0Eh) registers with an each valid accessory detection.

- 11. Follows the ANSI/CEA-936-A USB Car Kit specification.

- 12. The FSA9280A follow the Battery Charging 1.1 specification, which uses DP\_CON and DM\_CON to determine what USB accessory is attached (refer to the specification for details).

Downloaded from Arrow.com.

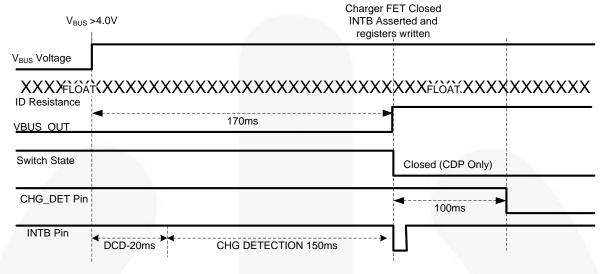

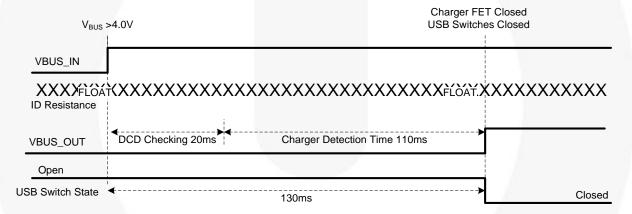

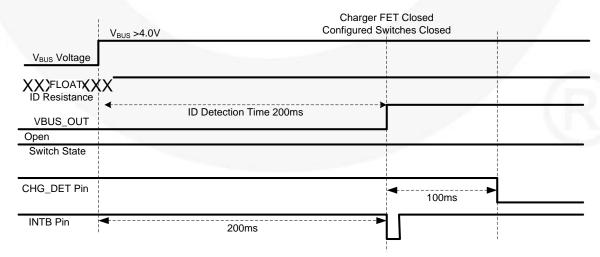

The following figures show the attach timing of the USB accessories and the relationship between the INTB assertion and the CHG\_DET assertion. FSA9280A implements the optional data contact detection (DCD) feature of the USB Battery Charging specification. The DCD detection ensures

proper connection of the DP\_CON and DM\_CON before starting the USB charging detection scheme. This feature allows for shorter attach times by eliminating long wait times to allow full contact of the DP\_CON and DM\_CON pins.

Figure 9. USB Dedicated Charging Port (DCP) or Charging Downstream Port (CDP) Attach Timing

Figure 10. USB Standard Downstream Port Attach Timing

Figure 11. Car Kit Type 1 and 2 Attach Timing

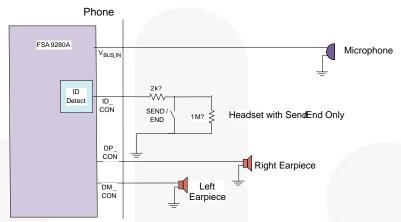

#### 5.2. Audio Accessory Detection

Audio accessories are detected when the ID\_CON pin resistance to GND is approximately  $1M\Omega$ . Configurations for this audio accessory shown in Figure 12 and Figure 13 .

Figure 12. Audio Accessory with Just Send/End Button (1% or 5% Resistors)

Figure 13. Audio Accessory with Full Wired Remote Control (1% Resistors)

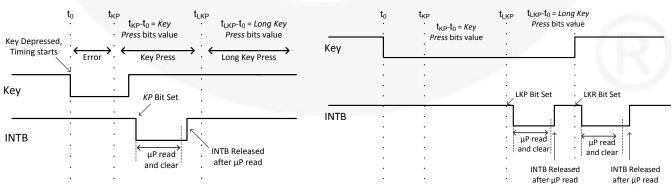

The FSA9280A can detect and differentiate between regular key presses, long key presses, and a stuck key. The definition of the key press timing is user configurable by writing the Timing Set 1 (08h) and Timing Set 2 (09h) registers. Timing diagrams for the key press detection are shown below in Figure 14 and Figure 15.

Figure 14. Regular Key-Press Timing Diagram

Figure 15. Long Key-Press Timing Diagram

#### 5.3. OCP and OVP Detection

With  $V_{BUS\_IN}$  greater than 6.8V,  $V_{BUS\_IN}$  is disconnected, protecting the FSA9280A and all application circuitry from excess voltage. This block is capable of withstanding continuous 28V in Shutdown Mode. Upon entering Shutdown Mode, the OVP\_EN bit in the Interrupt 1 register is set HIGH and an interrupt is sent to the baseband. The Over-Current Protection (OCP) feature limits current through the charger FET to  $\leq$  1.5A. The FSA9280A automatically senses an over-current event, shuts down  $V_{BUSOUT}$ , and reports this to the baseband by asserting OCP\_EN in the Interrupt 1 register. OCP Mode is only implemented when  $V_{BUS\_IN}$  is provided by the attached accessory. Removal of an OVP or OCP condition triggers another interrupt sent to the processor clearing the OCP\_EN and/or the OVP\_EN bits and setting the OCP\_OVP\_DIS bit in the Interrupt 1 register.

#### 6. Processor Communication

Typical communication steps between the processor and the FSA9280A during accessory detection are:

- INTB asserted LOW, indicating change in accessory detection.

- a) CHG\_DET asserted LOW if USB charger detected.

- Processor reads Interrupt registers to determine which event occurred.

- a) Interrupt 1 (03h): Indicates if an attach, detach, key press, long key press, long key release, OVP / OCP event, or OVP / OCP event recovery was detected. Each bit can be masked by setting the corresponding bit in the Interrupt Mask 1 (05h) register.

- b) Interrupt 2 (04h): Indicates if a reserved accessory, ADC change, stuck key, or stuck key recovery was detected. Each bit can be masked by setting the corresponding bit in the Interrupt Mask 2 (06h) register.

- Processor reads Status registers to determine exact accessory detected.

- a) Device Type 1 (0Ah): Indicates which USB, Car Kit UART, or audio accessory was detected.

- Device Type 2 (0Bh): Indicates which factory mode was detected or if a TTY cable was detected.

- Button 1 (0Ch & ODh): Indicates which button press was detected with Audio Type 1 accessories.

- d) Car Kit Status (0Eh): Indicates which type of car kit charger was detected.

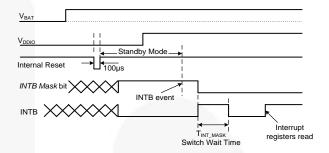

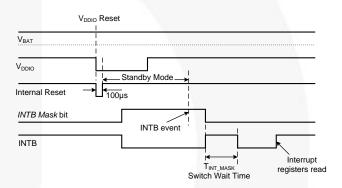

#### 6.1. Interrupts

The baseband processor recognizes interrupt signals by observing the INTB signal, which is active LOW. Interrupts are masked upon reset or power up via the INT Mask register bit (bit 0 of Control register, address 02h in Table 7. Register Map) and INTB pin defaults LOW right after this reset or power up. After the INT Mask bit is cleared by the baseband processor, the INTB pin is driven HIGH in preparation for a future interrupt. When an interruptible event

occurs, INTB transitions LOW and returns HIGH when the processor reads the Interrupt register at address 03h. Subsequent to the initial power up or reset; if the processor writes a "1" to INT Mask bit when the system is already powered up, the INTB pin stays HIGH and ignores all interrupts until the INT Mask bit is cleared. If an event happens that would ordinarily cause an interrupt when the INT Mask bit is set, the INTB pin is LOW for t<sub>INT\_MASK</sub> after the INT Mask bit is cleared.

Figure 16. Power-up Interrupt Timing Diagram

Figure 17. V<sub>DDIO</sub> Reset Interrupt Timing Diagram

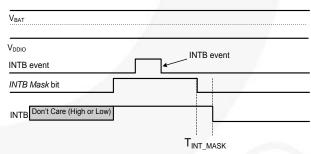

Figure 18. INT Mask to INTB Interrupt Timing Diagram

# 7. Switch Configuration

FSA9280A devices have two modes of operation when configuring the internal switches. The FSA9280A can autoconfigure the switches or the switches can be configured manually by the processor. Typical applications can use the Auto-Configuration Mode and do not require interaction with the baseband to configure the switches correctly.

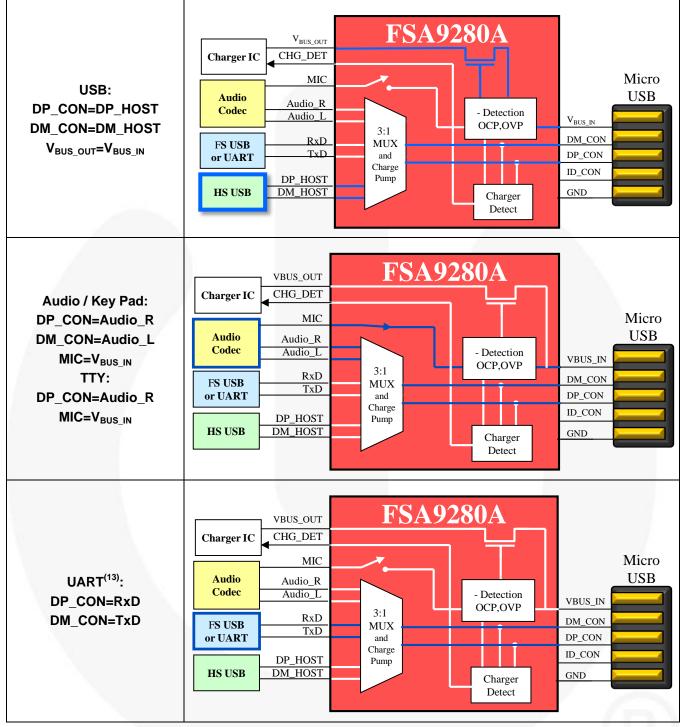

Table 5. Auto-Configurations

#### Note:

13. Use of FS USB on the UART path requires manual switching, as described in Section 11.4 — Systems with Multiple USB Controllers.

#### 7.1. Manual Switching

Manual switching is enabled by writing the following registers:

- Manual Switch 1 (13h): Configures the switches for DM\_CON, DP\_CON, and V<sub>BUS IN</sub>.

- Manual Switch 2 (14h): Configures the CHG\_DET, BOOT, and JIG pins.

# 8. Active Signal Performance

## 8.1. USB Data

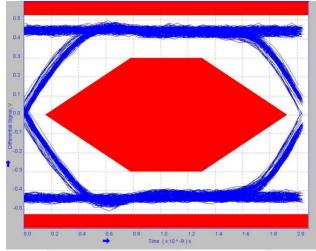

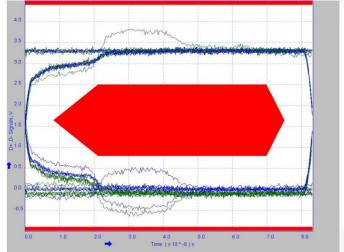

Figure 19. Pass Through Eye Compliance Testing Input Signal

Figure 20. USB 2.0 Eye Compliance Test Results at Output

#### 8.2. FS USB

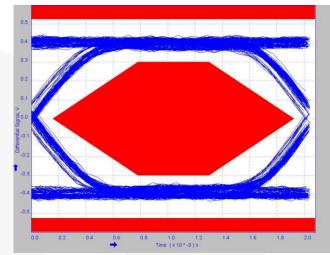

Figure 21. FS USB Eye Compliance for UART Path

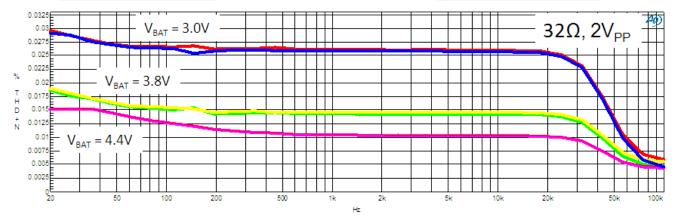

#### 8.3. Audio

Figure 22. THD+N Plot for Audio Channels

# 9. Electrical Specifications

## 9.1. Absolute Maximum Ratings

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be operable above the recommended operating conditions and stressing the parts to these levels is not recommended. In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability. The absolute maximum ratings are stress ratings only.

| Symbol                              | Parameter                              |                                                             |          | Min. | Max.                  | Unit |

|-------------------------------------|----------------------------------------|-------------------------------------------------------------|----------|------|-----------------------|------|

| V <sub>BAT</sub> /V <sub>DDIO</sub> | Supply Voltage from Battery / Bas      | -0.5                                                        | 6.0      | V    |                       |      |

| V <sub>BUS_IN</sub>                 | Supply Voltage from Micro-USB C        | -0.5                                                        | 28.0     | V    |                       |      |

|                                     |                                        | USB                                                         |          | -1.0 | V <sub>BUS</sub> +0.5 |      |

| $V_{SW}$                            | Switch I/O Voltage                     | Stereo / Mono Audio Path Active                             |          | -1.5 | V <sub>BAT</sub> +0.5 | V    |

|                                     |                                        | All Other Channels                                          |          | -0.5 | V <sub>BAT</sub> +0.5 |      |

| $I_{lK}$                            | Input Clamp Diode Current              |                                                             |          | -50  |                       | mA   |

| I <sub>CHG</sub>                    | Charger Detect CHG_DET Pin Cu          | urrent Sink Capability                                      | 1/       |      | 30                    | mA   |

|                                     |                                        | USB                                                         | //       |      | 50                    |      |

| I <sub>SW</sub>                     | Switch I/O Current (Continuous)        | Audio                                                       |          |      | 60                    | mA   |

| - //                                | 7                                      | All Other Channels                                          |          |      | 50                    |      |

|                                     |                                        | USB                                                         |          |      | 150                   | mA   |

| /                                   | Peak Switch Current (Pulsed at         |                                                             |          |      | 150                   | ША   |

| I <sub>SWPEAK</sub>                 | 1ms Duration, <10% Duty Cycle)         | Charger FET                                                 |          | 2    | Α                     |      |

|                                     |                                        | All Other Channels                                          |          |      | 150                   | mA   |

| T <sub>STG</sub>                    | Storage Temperature Range              |                                                             |          | -65  | +150                  | °C   |

| TJ                                  | Maximum Junction Temperature           |                                                             |          |      | +150                  | °C   |

| T <sub>L</sub>                      | Lead Temperature (Soldering, 10        | Seconds)                                                    |          |      | +260                  | °C   |

|                                     | IEC 61000-4-2 System ESD               | USB Connector Pins (DP_CON,                                 | Air Gap  | 15.0 |                       |      |

|                                     | ,                                      | DM_CON, V <sub>BUS_IN</sub> , ID_CON) to GND                | Contact  | 8.0  |                       |      |

| ESD                                 | Lluman Dady Madal                      | JIG, BOOT, INTB                                             | •        | 3.5  |                       | kV   |

|                                     | Human Body Model,<br>JEDEC JESD22-A114 | All Other Pins, Including DP_CON, DM_CON,ID_CON and VBUS_IN |          | 5.0  |                       |      |

|                                     | Charged Device Model, JEDEC J          | ESD22-C101                                                  | All Pins | 2.0  |                       |      |

# 9.2. Recommended Operating Conditions

The Recommended Operating Conditions table defines the conditions for actual device operation. Recommended operating conditions are specified to ensure optimal performance to the datasheet specifications. Fairchild does not recommend exceeding them or designing to Absolute Maximum Ratings.

| Symbol             | Para                                                           | Min. | Max. | Unit |    |

|--------------------|----------------------------------------------------------------|------|------|------|----|

| $V_{BAT}$          | Battery Supply Voltage <sup>(14)</sup>                         |      | 3.0  | 4.4  | V  |

| V <sub>BUSIN</sub> | Supply Voltage from V <sub>BUS_IN</sub> Pin <sup>(15)</sup>    |      | 4.0  | 5.5  | V  |

| $V_{DDIO}$         | Processor Supply Voltage                                       | 1.8  | 3.6  | V    |    |

|                    |                                                                | 0    | 3.6  | ~ J  |    |

| $V_{\text{SW}}$    | Switch I/O Voltage                                             | -1.2 | 1.2  | V    |    |

|                    |                                                                | 0    | 5.0  |      |    |

| ID <sub>CAP</sub>  | Capacitive Load on ID_CON Pin for Reliable Accessory Detection |      |      | 1.0  | nF |

| T <sub>A</sub>     | Operating Temperature                                          |      | -40  | +85  | °C |

#### Note:

- 14. Fairchild does not guarantee operation below 3.0V.

- 15. Between 5.5 to OVP starting voltage, the charger FET is still closed so that charger IC can charge battery even with 5.9~6.0V travel adaptor.

## 9.3. Switch Path DC Electrical Characteristics

All typical values are at T<sub>A</sub>=25°C unless otherwise specified.

| Symbol              | Doromatar                                                                         | V 00                 | Conditions                                                              | <b>T</b> <sub>A</sub> = · | -40 to + | -85°C | Unit |

|---------------------|-----------------------------------------------------------------------------------|----------------------|-------------------------------------------------------------------------|---------------------------|----------|-------|------|

| Symbol              | Parameter                                                                         | V <sub>BAT</sub> (V) | Conditions                                                              | 11C V 5 5                 | Max.     | Uni   |      |

| Host Interfa        | ace Pins (JIG, BOOT, INTB, CHG-I                                                  | DET)                 |                                                                         | •                         |          | •     |      |

| V <sub>OH</sub>     | Output High Voltage <sup>(16)</sup>                                               | 3.0 to 4.4           | I <sub>OH</sub> =2mA                                                    | _                         |          |       | V    |

| V <sub>OL</sub>     | Output Low Voltage                                                                | 3.0 to 4.4           | I <sub>OL</sub> =10mA                                                   |                           |          | 0.4   | V    |

| Switch OF           | F Characteristics                                                                 |                      |                                                                         | •                         |          | •     |      |

| l <sub>OFF</sub>    | Power-Off Leakage Current                                                         | 0                    | All Data Ports Except MIC V <sub>SW</sub> =0V to 4.4V                   |                           |          | 10    | μA   |

| I <sub>NO</sub>     | Switch Open Leakage Current with Device Powered                                   | 3.0 to 4.4           | V <sub>BAT</sub> =4.4V; I/O Pins=0.3V,<br>4.1V, or Floating, Except MIC | -0.100                    | 0.001    | 0.100 | μΑ   |

| I <sub>IDSHRT</sub> | Short-Circuit Current <sup>(17)</sup>                                             | 3.0 to 4.4           | Current Limit if ID_CON=0V                                              |                           | 5        |       | mA   |

| USB Switch          | h ON Path                                                                         |                      |                                                                         |                           |          |       |      |

| USB Analog          | g Signal Range                                                                    | 3.0 to 4.4           |                                                                         | 0                         |          | 3.6   | V    |

| R <sub>ONUSB</sub>  | USB Switch On Resistance <sup>(18)</sup>                                          | 3.0 to 4.4           | V <sub>D+/D-</sub> =0V, 0.4V, I <sub>ON</sub> =8mA                      |                           | 8        | 10    | Ω    |

| Charging F          | ET ON Path                                                                        |                      |                                                                         |                           |          | h     |      |

| V <sub>OVP</sub>    | Over-Voltage Protection (OVP) The                                                 | reshold Volta        | age                                                                     | 6.2                       | 6.8      | 7.2   | V    |

| R <sub>ONFET</sub>  | Charging FET On Resistance <sup>(17)</sup>                                        |                      | V <sub>BUS_IN</sub> =4.2V-5.0V, I <sub>ON</sub> =1A                     |                           | 200      |       | mΩ   |

| I <sub>OCP</sub>    | Over-Current Protection (OCP) The Current <sup>(17)</sup>                         | reshold              | V <sub>BUS_IN</sub> =5.2V                                               | 1.1                       | 1.3      | 1.5   | Α    |

| Audio_R/A           | udio_L Switch ON Paths                                                            |                      |                                                                         |                           |          | ı     |      |

| Audio Analo         | og Signal Range                                                                   | 3.0 to 4.4           |                                                                         | -1.2                      |          | 3.0   | V    |

| Ron                 | Audio Switch On Resistance <sup>(18)</sup>                                        | 3.0 to 4.4           | V <sub>L/R</sub> =-0.8V, 0.8V, I <sub>ON</sub> =30mA,                   |                           |          | 3     | Ω    |

| R <sub>FLAT</sub>   | Audio R <sub>ON</sub> Flatness <sup>(19)</sup>                                    | 3.0 to 4.4           | f=0-470kHz                                                              |                           |          | 0.1   | Ω    |

| MIC and U           | ART Switch ON Paths                                                               |                      |                                                                         |                           |          | ı     |      |

| Analog Sigr         | nal Range <sup>(20)</sup>                                                         | 3.0 to 4.4           |                                                                         | 0                         |          | 5     | V    |

|                     | MIC Path ON Resistance                                                            |                      |                                                                         | 19/1                      | 40       |       |      |

| R <sub>ON</sub>     | UART Path ON Resistance <sup>(17)</sup>                                           | 3.0 to 4.4           | V <sub>SW</sub> =0V, 4.4V, I <sub>ON</sub> =30mA                        | /                         | 25       | 30    | Ω    |

| Total Curre         | ent Consumption                                                                   | 1                    | /                                                                       |                           |          |       |      |

| I <sub>CCSL</sub>   | Battery Supply Standby Mode<br>Current (No Accessory Attached)                    | 3.0 to 4.4           | No Accessory Static Current<br>During Standby Mode                      |                           | 10       | 25    | μA   |

| I <sub>CCSLWA</sub> | Battery Supply Standby Mode<br>Current with Accessory<br>Attached <sup>(21)</sup> | 3.8                  | With Accessory Static Current<br>During Standby Mode                    |                           | 30       | 40    | μΑ   |

#### Notes:

- 16. Does not apply to CHG\_DET or JIG pins because they are open drain.

- 17. Limits based on electrical characterization data.

- 18. On resistance is the voltage drop between the two terminals at the indicated current through the switch.

- 19. Flatness is defined as the difference between the maximum and minimum values of on resistance over the specified range of conditions.

- 20. The MIC bias applied by the baseband should not exceed 2.8V.

- 21. Applies to all accessories except Audio Type 1 and Factory-Mode accessories.

# 9.4. Capacitance

| Symbol             | Parameter                                | V <sub>BAT</sub> | Condition                       | T <sub>A</sub> = | Unit |      |      |

|--------------------|------------------------------------------|------------------|---------------------------------|------------------|------|------|------|

| Syllibol           | Parameter                                | (V)              | Condition                       | Min.             | Тур. | Max. | Onit |

| C <sub>ONUSB</sub> | DP_CON, DM_CON On Capacitance (USB Mode) | 3.8              | V <sub>BIAS</sub> =0.2V, f=1MHz |                  | 8    |      | pF   |

# 9.5. Switch Path AC Electrical Characteristics

All typical values are for V<sub>BAT</sub>=3.8V at T<sub>A</sub>=25°C unless otherwise specified.

| Or seed to a l       | Damana                                                                                                                                               | 4                                                                                                                                           |                                                        | O a malistic m                               | T <sub>A</sub> = -                                                                              | -40 to -                                                                                               | +85°C | 11:4 |  |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|----------------------------------------------|-------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|-------|------|--|

| Symbol               | Parame                                                                                                                                               | ter                                                                                                                                         |                                                        | Condition                                    | Min.                                                                                            | Тур.                                                                                                   | Max.  | Unit |  |

|                      |                                                                                                                                                      | Audio Mode                                                                                                                                  | f=20kHz                                                | , R <sub>T</sub> =32Ω, C <sub>L</sub> =0pF   |                                                                                                 | -50                                                                                                    |       |      |  |

| Xtalk                | Active Channel Crosstalk DP_CON to DM_CON                                                                                                            | LICD Made                                                                                                                                   | $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$ |                                              |                                                                                                 | dB                                                                                                     |       |      |  |

|                      | DI _OOIV IO DIM_OOIV                                                                                                                                 | USB Mode                                                                                                                                    | f=240MH                                                | Iz, R <sub>T</sub> =50Ω, C <sub>L</sub> =0pF | Min. Typ. Max.  -50  -60  -40  -90  -90  -100  0.03  2V  0.05  -1z,  30  10  130  170  200  100 |                                                                                                        |       |      |  |

| 0                    | Off Isolation                                                                                                                                        | Audio Mode                                                                                                                                  | f=20kHz                                                | , R <sub>T</sub> =32Ω, C <sub>L</sub> =0pF   |                                                                                                 | -90                                                                                                    |       | dB   |  |

| O <sub>IRR</sub>     | On isolation                                                                                                                                         | USB Mode                                                                                                                                    | f=1 MHz                                                | , R <sub>T</sub> =50Ω, C <sub>L</sub> =0pF   |                                                                                                 | -90                                                                                                    |       | uБ   |  |

| PSRR                 | Power Supply Rejection Ra                                                                                                                            | tio, MIC on V <sub>BUS_IN</sub>                                                                                                             |                                                        |                                              |                                                                                                 | -100                                                                                                   |       | dB   |  |

| TUD                  | Tatal II amazaia Diatartian (                                                                                                                        | Accelia Dath                                                                                                                                |                                                        |                                              |                                                                                                 | 0.03                                                                                                   |       | %    |  |

| THD                  | Total Harmonic Distortion (A                                                                                                                         | Audio Patn)                                                                                                                                 |                                                        |                                              |                                                                                                 | -50<br>-60<br>-40<br>-90<br>-90<br>-100<br>0.03<br>0.05<br>30<br>10<br>130<br>170<br>170<br>100<br>100 |       |      |  |

| t <sub>SK(P)</sub>   | Skew of Opposite Transitions of the Same<br>Output (USB Mode)                                                                                        |                                                                                                                                             |                                                        |                                              |                                                                                                 | 30                                                                                                     |       | ps   |  |

| t <sub>I2CRST</sub>  | Time When I2C_SDA and I2C_SCL Both LOW to Cause a Reset                                                                                              |                                                                                                                                             |                                                        | See Figure 6                                 | 30                                                                                              |                                                                                                        |       | ms   |  |

| t <sub>INTMASK</sub> | Time after <i>INT Mask</i> Cleared to "0" until INTB Goes LOW to Signal the Interrupt after Interruptible Event while <i>INT Mask</i> Bit Set to "1" |                                                                                                                                             |                                                        | See Figure 18                                |                                                                                                 | 10                                                                                                     |       | ms   |  |

| t <sub>SDPDET</sub>  | Time from V <sub>BUS_IN</sub> Valid to V<br>Charger FET Closed and U<br>for USB Standard Downstre                                                    | SB Switches Closed                                                                                                                          | 347                                                    | See Figure 10                                |                                                                                                 | 130                                                                                                    |       | ms   |  |

| t <sub>CHGOUT</sub>  | Time from V <sub>BUS_IN</sub> Valid to V<br>Charger FET Closed for Bo<br>Ports (CDP and DCP)                                                         |                                                                                                                                             |                                                        | See Figure 9                                 |                                                                                                 | 170                                                                                                    |       | ms   |  |

| t <sub>CARKIT</sub>  | Time from V <sub>BUS_IN</sub> Valid to C<br>Type 2 Charger Detected                                                                                  | Car Kit Type 1 or                                                                                                                           |                                                        | See Figure 11                                |                                                                                                 | 200                                                                                                    |       | ms   |  |

| t <sub>CHGDET</sub>  | Time from V <sub>BUS_OUT</sub> Valid to CHG_DET Output LOW for Both USB Charging Ports (CDP and DCP) and for Car Kit Chargers                        |                                                                                                                                             | See                                                    | e Figure 9, Figure 11                        |                                                                                                 | 100                                                                                                    |       | ms   |  |

| t <sub>IDDET</sub>   | Signal Accessory Attached                                                                                                                            | Time from ID_CON Not Floating to INTB LOW to Signal Accessory Attached that is ID_CON Resistance-Based Only (V <sub>BUS_IN</sub> Not Valid) |                                                        | See Figure 8                                 |                                                                                                 | 200                                                                                                    | 1     | ms   |  |

| tuigvbus             | Time from V <sub>BUS_IN</sub> Valid to J<br>V <sub>BUS_OUT</sub> Valid with Charger<br>Factory Mode Operation with                                   | FET Closed for Both                                                                                                                         |                                                        | See Figure 25                                |                                                                                                 | 200                                                                                                    | Ų.    | ms   |  |

|                      | Time from V <sub>BUS_IN</sub> Valid to J<br>Mode Operation without V <sub>B</sub>                                                                    |                                                                                                                                             |                                                        | See Figure 26                                |                                                                                                 | 200                                                                                                    |       | ms   |  |

# 9.6. I<sup>2</sup>C Controller DC Characteristics

| Cumbal           | Devementer                                                 |                       | Fast N                                                                                                         | Hz)                  |                                       |  |  |

|------------------|------------------------------------------------------------|-----------------------|----------------------------------------------------------------------------------------------------------------|----------------------|---------------------------------------|--|--|

| Symbol           | Parameter                                                  |                       | Min. Max. Units                                                                                                |                      |                                       |  |  |

| V <sub>IL</sub>  | Low-Level Input Voltage                                    | -0.5                  | 0.3V <sub>DDIO</sub>                                                                                           | V                    |                                       |  |  |

| V <sub>IH</sub>  | High-Level Input Voltage                                   | 0.7V <sub>DDIO</sub>  |                                                                                                                | V                    |                                       |  |  |

| \/               | Hyptorogic of Schmitt Trigger Inputs                       | V <sub>DDIO</sub> >2V | 0.05V <sub>DDIO</sub>                                                                                          |                      | \/                                    |  |  |

| $V_{HYS}$        | Hysteresis of Schmitt Trigger Inputs                       | V <sub>DDIO</sub> <2V | Min.         Max.         Units           -0.5         0.3V <sub>DDIO</sub> V           0.7V <sub>DDIO</sub> V | ٧                    |                                       |  |  |

| W                | Low-Level Output Voltage at 3mA Sink Current               | V <sub>DDIO</sub> >2V | 0                                                                                                              | 0.4                  | \/                                    |  |  |

| $V_{OL1}$        | (Open-Drain)                                               | V <sub>DDIO</sub> <2V |                                                                                                                | 0.2V <sub>DDIO</sub> | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ |  |  |

| I <sub>I2C</sub> | Input Current of I2C_SDA and I2C_SCL Pins, Input Voltage C | -10                   | 10                                                                                                             | μA                   |                                       |  |  |

| Cı               | Capacitance for Each I/O Pin                               |                       |                                                                                                                | 10                   | pF                                    |  |  |

# 9.7. I<sup>2</sup>C AC Electrical Characteristics & Register Map

| Cumbal              | Doromotor                                                         | Fast Mode            |      |      |  |

|---------------------|-------------------------------------------------------------------|----------------------|------|------|--|

| Symbol              | Parameter                                                         | Min.                 | Max. | Unit |  |

| f <sub>SCL</sub>    | SCL Clock Frequency                                               | 0                    | 400  | kHz  |  |

| t <sub>HD;STA</sub> | Hold Time (Repeated) START Condition                              | 0.6                  |      | μs   |  |

| t <sub>LOW</sub>    | LOW Period of SCL Clock                                           | 1.3                  |      | μs   |  |

| t <sub>HIGH</sub>   | HIGH Period of SCL Clock                                          | 0.6                  |      | μs   |  |

| t <sub>SU;STA</sub> | Set-up Time for Repeated START Condition                          | 0.6                  |      | μs   |  |

| t <sub>HD;DAT</sub> | Data Hold Time                                                    | 0                    | 0.9  | μs   |  |

| t <sub>SU;DAT</sub> | Data Set-up Time <sup>(22)</sup>                                  | 100                  |      | ns   |  |

| t <sub>r</sub>      | Rise Time of SDA and SCL Signals <sup>(23)</sup>                  | 20+0.1C <sub>b</sub> | 300  | ns   |  |

| t <sub>f</sub>      | Fall Time of SDA and SCL Signals <sup>(23)</sup>                  | 20+0.1C <sub>b</sub> | 300  | ns   |  |

| t <sub>SU;STO</sub> | Set-up Time for STOP Condition                                    | 0.6                  |      | μs   |  |

| t <sub>BUF</sub>    | BUS-Free Time between STOP and START Conditions                   | 1.3                  |      | μs   |  |

| t <sub>SP</sub>     | Pulse Width of Spikes that Must Be Suppressed by the Input Filter | 0                    | 50   | ns   |  |

#### Notes: