# Low Voltage 1:18 Clock Distribution Chip

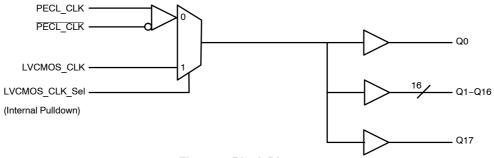

# **Functional Description**

The ASM2I9940L is a 1:18 low Voltage Clock distribution chip with 2.5 V or 3.3 V LVCMOS output capabilities. The device features the capability to select either a differential LVPECL or LVCMOS compatible input. The 18 outputs are 2.5 V or 3.3 V LVCMOS compatible and feature the drive strength to drive 50  $\Omega$  series or parallel terminated transmission lines. With output–to–output skews of 150 pS, the ASM2I9940L is ideal as a clock distribution chip for the most demanding of Synchronous systems. The 2.5 V outputs also make the device ideal for supplying clocks for a high performance microprocessor based design.

With low output impedance ( $\approx$ 20  $\Omega$ ), in both the HIGH and LOW logic states, the output buffers of the ASM2I9940L are ideal for driving series terminated transmission lines. With a 20  $\Omega$  output impedance the ASM2I9940L has the capability of driving two series terminated lines from each output. This gives the device an effective fanout of 1:36.

The differential LVPECL inputs of the ASM2I9940L allow the device to interface directly with a LVPECL fanout buffer to build very wide clock fanout trees or to couple to a high frequency clock source. The LVCMOS input provides a more standard interface for applications requiring only a single clock distribution chip at relatively low frequencies. In addition, the two clock sources can be used to provide for a test clock interface as well as the primary system clock. A logic HIGH on the LVCMOS\_CLK\_Sel pin will select the LVCMOS level clock input. All inputs of the ASM2I9940L have internal pullup/pulldown resistor, so they can be left open if unused.

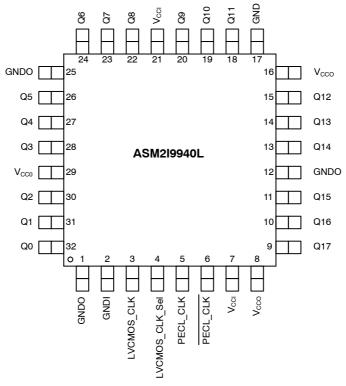

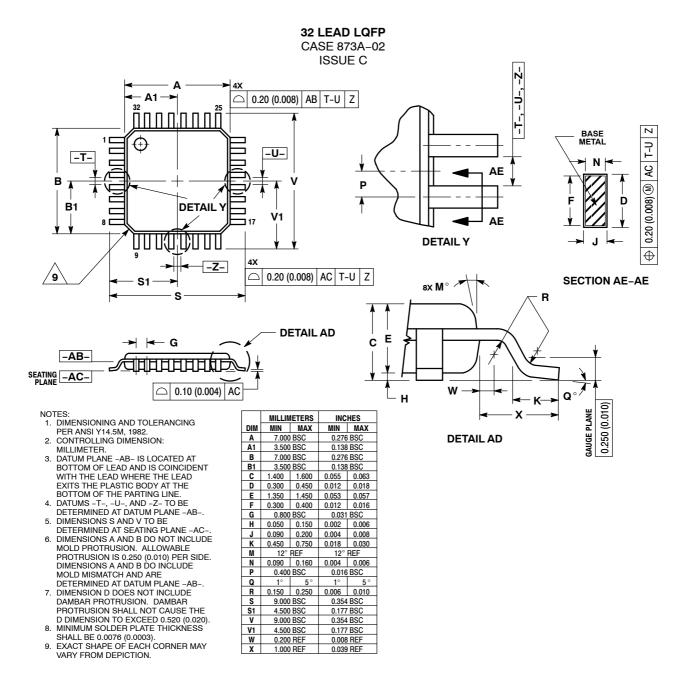

The ASM2I9940L is a single or dual supply device. The device power supply offers a high degree of flexibility. The device can operate with a 3.3 V core and 3.3 V output, a 3.3 V core and 2.5 V outputs as well as a 2.5 V core and 2.5 V outputs. The 32–lead LQFP Package was chosen to optimize performance, board space and cost of the device. The 32–lead LQFP Package has a 7 x 7 mm<sup>2</sup> body size with conservative 0.8 mm pin spacing.

#### **Features**

- LVPECL or LVCMOS Clock Input

- 2.5 V LVCMOS Outputs for Intel® Pentium® II Microprocessor Support

- 150 pS Maximum Output-to-Output Skew

- Maximum Output Frequency of 250 MHz

- 32 Lead LQFP Package

- Dual or Single Supply Device:

# ON Semiconductor®

http://onsemi.com

# MARKING DIAGRAM

LQFP-32 CASE 873A

2l9940L = Specific Device Code

A = Assembly Location

WL = Wafer Lot YY = Year

WW = Work Week

G = Pb-Free Package

#### **ORDERING INFORMATION**

See detailed ordering and shipping information in the package dimensions section on page 9 of this data sheet.

- Dual V<sub>CC</sub> Supply Voltage, 3.3 V Core and 2.5 V Output

- Single 3.3 V V<sub>CC</sub> Supply Voltage for 3.3 V Outputs

- ◆ Single 2.5 V V<sub>CC</sub> Supply Voltage for 2.5 V I/O

- Pin and Function compatible to MPC940L, MPC9109, CY29940 and CY29940-1

- These Devices are Pb–Free, Halogen Free/BFR Free and are RoHS Compliant

Figure 1. Block Diagram

Figure 2. Pin Diagram

**Table 1. FUNCTION TABLE**

| LVCMOS_CLK_Sel | Input      |

|----------------|------------|

| 0              | PECL_CLK   |

| 1              | LVCMOS_CLK |

**Table 2. POWER SUPPLY VOLTAGES**

| Supply Pin       | Voltage Level           |

|------------------|-------------------------|

| V <sub>CCI</sub> | 2.5 V or 3.3 V $\pm$ 5% |

| V <sub>CCO</sub> | 2.5 V or 3.3 V $\pm$ 5% |

**Table 3. PIN CONFIGURATIONS**

| Pin #                                                                 | Pin Name             | I/O    | Туре   | Function                                                 |

|-----------------------------------------------------------------------|----------------------|--------|--------|----------------------------------------------------------|

| 5<br>6                                                                | PECL_CLK<br>PECL_CLK | Input  | LVPECL | LVPECL Clock Inputs                                      |

| 3                                                                     | LVCMOS_CLK           | Input  | LVCMOS | LVCMOS Clock Input                                       |

| 4                                                                     | LVCMOS_CLK_Sel       | Input  | LVCMOS | Selects either LVPECL or LVCMOS input as Clock<br>Source |

| 32, 31, 30, 28, 27, 26, 24, 23, 22, 20, 19, 18, 15, 14, 13, 11, 10, 9 | Q0 – Q17             | Output | LVCMOS | Clock Outputs                                            |

| 2                                                                     | GNDI                 |        | Supply | Core Negative Power Supply                               |

| 1, 12, 17, 25                                                         | GNDO                 |        | Supply | Output Negative Power Supply                             |

| 7, 21                                                                 | V <sub>CCI</sub>     |        | Supply | Core Positive Power Supply                               |

| 8, 16, 29                                                             | V <sub>CCO</sub>     | ·      | Supply | Output Positive Power Supply                             |

**Table 4. ABSOLUTE MAXIMUM RATINGS**

| Symbol            | Parameter                                            | Min  | Max                   | Unit |

|-------------------|------------------------------------------------------|------|-----------------------|------|

| V <sub>CC</sub>   | Supply Voltage                                       | -0.3 | 3.6                   | V    |

| VI                | Input Voltage                                        | -0.3 | V <sub>CC</sub> + 0.3 | V    |

| I <sub>IN</sub>   | Input Current                                        |      | ±20                   | mA   |

| T <sub>Stor</sub> | Storage Temperature Range                            | -40  | 125                   | °C   |

| T <sub>s</sub>    | Max. Soldering Temperature (10 sec)                  |      | 260                   | °C   |

| T <sub>DV</sub>   | Static Discharge Voltage (As per JEDEC STD22-A114-B) |      | 2                     | kV   |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

**Table 5. DC CHARACTERISTICS** ( $T_A$  = 0°C to 70°C,  $V_{CCI}$  = 3.3 V  $\pm$  5%,  $V_{CCO}$  = 3.3 V  $\pm$  5%)

| Symbol           | Characteristic                |          | Condition                | Min                    | Тур | Max                    | Unit |

|------------------|-------------------------------|----------|--------------------------|------------------------|-----|------------------------|------|

| V <sub>IH</sub>  | Input HIGH Voltage            | CMOS_CLK |                          | 2.4                    |     | V <sub>CCI</sub>       | V    |

| V <sub>IL</sub>  | Input LOW Voltage             | CMOS_CLK |                          |                        |     | 0.8                    | V    |

| $V_{PP}$         | Peak-to-Peak Input Voltage    | PECL_CLK |                          | 500                    |     | 1000                   | mV   |

| $V_{CMR}$        | Common Mode Range PECL_CLK    |          |                          | V <sub>CCI</sub> – 1.4 |     | V <sub>CCI</sub> – 0.6 | V    |

| V <sub>OH</sub>  | Output HIGH Voltage           |          | I <sub>OH</sub> = -20 mA | 2.4                    |     |                        | V    |

| $V_{OL}$         | Output LOW Voltage            |          | I <sub>OL</sub> = 20 mA  |                        |     | 0.5                    | V    |

| I <sub>IN</sub>  | Input Current                 |          |                          |                        |     | ±200                   | μΑ   |

| C <sub>IN</sub>  | Input Capacitance             |          |                          |                        | 4.0 |                        | pF   |

| C <sub>pd</sub>  | Power Dissipation Capacitance |          | per output               |                        | 10  |                        | pF   |

| Z <sub>OUT</sub> | Output Impedance              |          |                          | 18                     | 23  | 28                     | Ω    |

| I <sub>CC</sub>  | Maximum Quiescent Supply Co   | urrent   |                          |                        | 0.5 | 1.0                    | mA   |

Table 6. AC CHARACTERISTICS (T<sub>A</sub> = 0°C to 70°C,  $V_{CCI}$  = 3.3 V  $\pm$  5%,  $V_{CCO}$  = 3.3 V  $\pm$  5%)

| Symbol                          | Characteristic                                          |                                                              | Condition                        | Min        | Тур        | Max        | Unit |

|---------------------------------|---------------------------------------------------------|--------------------------------------------------------------|----------------------------------|------------|------------|------------|------|

| F <sub>max</sub>                | Maximum Input Frequency                                 |                                                              |                                  |            |            | 250        | MHz  |

| t <sub>PLH</sub>                | Propagation Delay                                       | PECL_CLK ≤ 150 MHz<br>CMOS_CLK ≤ 150 MHz                     | (Note 1)                         | 2.0<br>1.7 | 2.7<br>2.5 | 3.4<br>3.0 | nS   |

| t <sub>PLH</sub>                | Propagation Delay PECL_CLK > 150 MHz CMOS_CLK > 150 MHz |                                                              |                                  | 2.0<br>1.8 | 2.9<br>2.5 | 3.7<br>3.2 | nS   |

| t <sub>sk(o)</sub>              | Output-to-output Skew                                   | PECL_CLK<br>CMOS_CLK                                         | (Note 1)                         |            |            | 150<br>150 | pS   |

| t <sub>sk(pp)</sub>             | Part-to-Part Skew                                       | PECL_CLK ≤ 150 MHz<br>CMOS_CLK ≤ 150 MHz                     | (Notes 1 and 2)                  |            |            | 1.5<br>1.3 | nS   |

| t <sub>sk(pp)</sub>             | Part-to-Part Skew                                       | PECL_CLK > 150 MHz<br>CMOS_CLK > 150 MHz                     | (Notes 1 and 2)                  |            |            | 1.8<br>1.5 | nS   |

| t <sub>sk(pp)</sub>             | Part-to-Part Skew                                       | PECL_CLK<br>CMOS_CLK                                         | (Notes 1 and 3)                  |            |            | 850<br>750 | pS   |

| DC                              | Output Duty Cycle                                       | $f_{CLK} < 134 \text{ MHz}$<br>$f_{CLK} \le 250 \text{ MHz}$ | Input DC = 50%<br>Input DC = 50% | 45<br>40   | 50<br>50   | 55<br>60   | %    |

| t <sub>r</sub> , t <sub>f</sub> | Output Rise/Fall Time                                   | •                                                            | 0.5 – 2.4 V                      | 0.3        |            | 1.1        | nS   |

<sup>1.</sup> Tested using standard input levels, Production tested @ 150 MHz.

Table 7. DC CHARACTERISTICS (T<sub>A</sub> = 0°C to 70°C, V<sub>CCI</sub> = 3.3 V  $\pm$  5%, V<sub>CCO</sub> = 2.5 V  $\pm$  5%)

| Symbol           | Characteristic                |          | Condition                 | Min                    | Тур | Max                    | Unit |

|------------------|-------------------------------|----------|---------------------------|------------------------|-----|------------------------|------|

| V <sub>IH</sub>  | Input HIGH Voltage CMOS_CLK   |          |                           | 2.4                    |     | V <sub>CCI</sub>       | V    |

| V <sub>IL</sub>  | Input LOW Voltage             | CMOS_CLK |                           |                        |     | 0.8                    | V    |

| V <sub>PP</sub>  | Peak-to-Peak Input Voltage    | PECL_CLK |                           | 500                    |     | 1000                   | mV   |

| V <sub>CMR</sub> | Common Mode Range             | PECL_CLK |                           | V <sub>CCI</sub> – 1.4 |     | V <sub>CCI</sub> – 0.6 | V    |

| V <sub>OH</sub>  | Output HIGH Voltage           |          | $I_{OH} = -12 \text{ mA}$ | 1.8                    |     |                        | V    |

| V <sub>OL</sub>  | Output LOW Voltage            |          | I <sub>OL</sub> = 12 mA   |                        |     | 0.5                    | V    |

| I <sub>IN</sub>  | Input Current                 |          |                           |                        |     | ±200                   | μΑ   |

| C <sub>IN</sub>  | Input Capacitance             |          |                           |                        | 4.0 |                        | pF   |

| C <sub>pd</sub>  | Power Dissipation Capacitance |          | per output                |                        | 10  |                        | pF   |

| Z <sub>OUT</sub> | Output Impedance              |          |                           |                        | 23  |                        | Ω    |

| I <sub>CC</sub>  | Maximum Quiescent Supply C    | urrent   |                           |                        | 0.5 | 1.0                    | mA   |

Across temperature and voltage ranges, includes output skew.

For a specific temperature and voltage, includes output skew.

Table 8. AC CHARACTERISTICS (T<sub>A</sub> = 0°C to 70°C,  $V_{CCI}$  = 3.3 V  $\pm$  5%,  $V_{CCO}$  = 2.5 V  $\pm$  5%)

| Symbol                          | Characteristic          |                                                          | Condition                        | Min        | Тур        | Max        | Unit |

|---------------------------------|-------------------------|----------------------------------------------------------|----------------------------------|------------|------------|------------|------|

| F <sub>max</sub>                | Maximum Input Frequency |                                                          |                                  |            |            | 250        | MHz  |

| t <sub>PLH</sub>                | Propagation Delay       | PECL_CLK ≤ 150 MHz<br>CMOS_CLK ≤ 150 MHz                 | (Note 4)                         | 2.0<br>1.7 | 2.8<br>2.5 | 3.5<br>3.0 | nS   |

| t <sub>PLH</sub>                | Propagation Delay       | PECL_CLK > 150 MHz<br>CMOS_CLK > 150 MHz                 |                                  | 2.0<br>1.8 | 2.9<br>2.5 | 3.8<br>3.3 | nS   |

| t <sub>sk(o)</sub>              | Output-to-output Skew   | PECL_CLK<br>CMOS_CLK                                     | (Note 4)                         |            |            | 150<br>150 | pS   |

| t <sub>sk(pp)</sub>             | Part-to-Part Skew       | PECL_CLK ≤ 150 MHz<br>CMOS_CLK ≤ 150 MHz                 | (Notes 4 and 5)                  |            |            | 1.5<br>1.3 | nS   |

| t <sub>sk(pp)</sub>             | Part-to-Part Skew       | PECL_CLK > 150 MHz<br>CMOS_CLK > 150 MHz                 | (Notes 4 and 5)                  |            |            | 1.8<br>1.5 | nS   |

| t <sub>sk(pp)</sub>             | Part-to-Part Skew       | PECL_CLK<br>CMOS_CLK                                     | (Notes 4 and 6)                  |            |            | 850<br>750 | pS   |

| DC                              | Output Duty Cycle       | f <sub>CLK</sub> < 134 MHz<br>f <sub>CLK</sub> ≤ 250 MHz | Input DC = 50%<br>Input DC = 50% | 45<br>40   | 50<br>50   | 55<br>60   | %    |

| t <sub>r</sub> , t <sub>f</sub> | Output Rise/Fall Time   | •                                                        | 0.5 – 1.8 V                      | 0.3        |            | 1.2        | nS   |

<sup>4.</sup> Tested using standard input levels, Production tested @ 150 MHz.

Table 9. DC CHARACTERISTICS (T<sub>A</sub> = 0°C to 70°C, V<sub>CCI</sub> = 2.5 V  $\pm$  5%, V<sub>CCO</sub> = 2.5 V  $\pm$  5%)

| Symbol           | Characteristic                |          | Condition                 | Min                    | Тур | Max                    | Unit |

|------------------|-------------------------------|----------|---------------------------|------------------------|-----|------------------------|------|

| V <sub>IH</sub>  | Input HIGH Voltage            | CMOS_CLK |                           | 2.0                    |     | V <sub>CCI</sub>       | V    |

| V <sub>IL</sub>  | Input LOW Voltage             | CMOS_CLK |                           |                        |     | 0.8                    | V    |

| V <sub>PP</sub>  | Peak-to-Peak Input Voltage    | PECL_CLK |                           | 500                    |     | 1000                   | mV   |

| V <sub>CMR</sub> | Common Mode Range             | PECL_CLK |                           | V <sub>CCI</sub> – 1.0 |     | V <sub>CCI</sub> - 0.6 | V    |

| V <sub>OH</sub>  | Output HIGH Voltage           |          | $I_{OH} = -12 \text{ mA}$ | 1.8                    |     |                        | V    |

| V <sub>OL</sub>  | Output LOW Voltage            |          | I <sub>OL</sub> = 12 mA   |                        |     | 0.5                    | V    |

| I <sub>IN</sub>  | Input Current                 |          |                           |                        |     | ± 200                  | μΑ   |

| C <sub>IN</sub>  | Input Capacitance             |          |                           |                        | 4.0 |                        | pF   |

| C <sub>pd</sub>  | Power Dissipation Capacitance |          | per output                |                        | 10  |                        | pF   |

| Z <sub>OUT</sub> | Output Impedance              |          |                           | 18                     | 23  | 28                     | Ω    |

| I <sub>CC</sub>  | Maximum Quiescent Supply C    | urrent   |                           |                        | 0.5 | 1.0                    | mA   |

Across temperature and voltage ranges, includes output skew.

For a specific temperature and voltage, includes output skew.

Table 10. AC Characteristics (T<sub>A</sub> = 0°C to 70°C,  $V_{CCI}$  = 2.5 V  $\pm$  5%,  $V_{CCO}$  = 2.5 V  $\pm$  5%)

| Symbol                          | Characteristic                           |                                                              | Condition                        | Min        | Тур        | Max        | Unit |

|---------------------------------|------------------------------------------|--------------------------------------------------------------|----------------------------------|------------|------------|------------|------|

| F <sub>max</sub>                | Maximum Input Frequency                  |                                                              |                                  |            |            | 200        | MHz  |

| t <sub>PLH</sub>                | Propagation Delay                        | PECL_CLK ≤ 150 MHz<br>CMOS_CLK ≤ 150 MHz                     | (Note 7)                         | 2.6<br>2.3 | 4.0<br>3.1 | 5.2<br>4.0 | nS   |

| t <sub>PLH</sub>                | Propagation Delay                        | PECL_CLK > 150 MHz<br>CMOS_CLK > 150 MHz                     |                                  | 2.8<br>2.3 | 3.8<br>3.1 | 5.0<br>4.0 | nS   |

| t <sub>sk(o)</sub>              | Output-to-output Skew<br>Within one bank | PECL_CLK<br>CMOS_CLK                                         | (Note 7)                         |            |            | 200<br>200 | pS   |

| t <sub>sk(pp)</sub>             | Part-to-Part Skew                        | PECL_CLK ≤ 150 MHz<br>CMOS_CLK ≤ 150 MHz                     | (Notes 7 and 8)                  |            |            | 2.6<br>1.7 | nS   |

| t <sub>sk(pp)</sub>             | Part-to-Part Skew                        | PECL_CLK > 150 MHz<br>CMOS_CLK > 150 MHz                     | (Notes 7 and 8)                  |            |            | 2.2<br>1.7 | nS   |

| t <sub>sk(pp)</sub>             | Part-to-Part Skew                        | PECL_CLK<br>CMOS_CLK                                         | (Notes 7 and 9)                  |            |            | 1.2<br>1.0 | nS   |

| DC                              | Output Duty Cycle                        | $f_{CLK} < 134 \text{ MHz}$<br>$f_{CLK} \le 200 \text{ MHz}$ | Input DC = 50%<br>Input DC = 50% | 45<br>40   | 50<br>50   | 55<br>60   | %    |

| t <sub>r</sub> , t <sub>f</sub> | Output Rise/Fall Time                    |                                                              | 0.5 – 1.8 V                      | 0.3        |            | 1.2        | nS   |

- 7. Tested using standard input levels, Production tested @ 150 MHz.

- Across temperature and voltage ranges, includes output skew.

For a specific temperature and voltage, includes output skew.

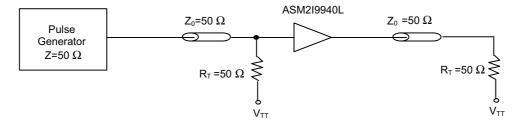

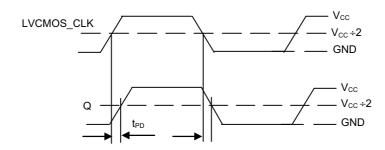

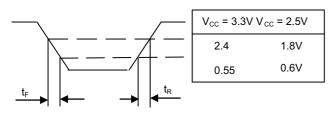

Figure 3. LVCMOS\_CLK ASM2I9940L AC Test Reference for  $V_{CC}$  = 3.3 V and  $V_{CC}$  = 2.5 V

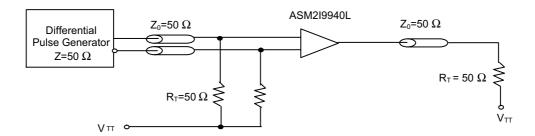

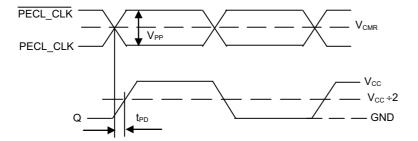

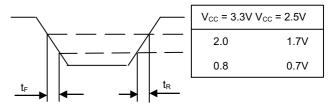

Figure 4. PECL\_CLK ASM2I9940L AC Test Reference for  $V_{CC}$  = 3.3 V and  $V_{CC}$  = 2.5 V

Figure 5. Propagation Delay (tpD) Test Reference

Figure 6. LVCMOS Propagation Delay (tpD) Test Reference

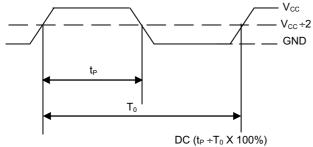

The time from the PLL controlled edge to the non-controlled edge, divided by the time between PLL controlled edges, expressed as a percentage.

Figure 7. Output Duty Cycle (DC)

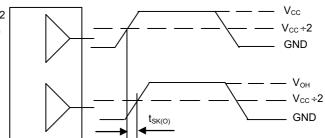

The pin-to-pin skew is defined as the worst case difference in propagation delay between any similar delay path within a single device

Figure 8. Output-to-Output Skew t<sub>SK(O)</sub>

Figure 9. Output Transition Time Test Reference

Figure 10. Input Transition Time Test Reference

# Power Consumption of the ASM2I9940L and Thermal Management

The ASM2I9940L AC specification is guaranteed for the entire operating frequency range up to 250 MHz. The ASM2I9940L power consumption and the associated long-term reliability may decrease the maximum frequency limit, depending on operating conditions such as clock frequency, supply voltage, output loading, ambient temperature, vertical convection and thermal conductivity of package and board. This section describes the impact of these parameters on the junction temperature and gives a guideline to estimate the ASM2I9940L die junction temperature and the associated device reliability.

Table 11. DIE JUNCTION TEMPERATURE AND MTBF

| Junction Temperature (°C) | MTBF (Years) |

|---------------------------|--------------|

| 100                       | 20.4         |

| 110                       | 9.1          |

| 120                       | 4.2          |

| 130                       | 2.0          |

Increased power consumption will increase the die junction temperature and impact the device reliability (MTBF). According to the system-defined tolerable MTBF, the die junction temperature of the ASM2I9940L needs to be controlled and the thermal impedance of the board/package should be optimized. The power dissipated in the ASM2I9940L is represented in Equation 1.

Where  $I_{CCQ}$  is the static current consumption of the ASM2I9940L,  $C_{PD}$  is the power dissipation capacitance per output,  $(M)\Sigma C_L$  represents the external capacitive output load, N is the number of active outputs (N is always 12 in case of the ASM2I9940L). The ASM2I9940L supports driving transmission lines to maintain high signal integrity and tight timing parameters. Any transmission line will hide the lumped capacitive load at the end of the board trace, therefore,  $\Sigma C_L$  is zero for controlled transmission line systems and can be eliminated from Equation 1. Using parallel termination output termination results in Equation 2 for power dissipation.

In Equation 2, P stands for the number of outputs with a parallel or the venin termination,  $V_{OL}, I_{OL}, V_{OH}$  and  $I_{OH}$  are a function of the output termination technique and  $DC_Q$  is the clock signal duty cycle. If transmission lines are used  $\Sigma C_L$  is zero in Equation 2 and can be eliminated. In general, the use of controlled transmission line techniques eliminates the impact of the lumped capacitive loads at the end lines and greatly reduces the power dissipation of the device. Equation 3 describes the die junction temperature  $T_J$  as a function of the power consumption.

Where  $R_{\theta ja}$  is the thermal impedance of the package (junction-to-ambient) and  $T_A$  is the ambient temperature. According to Table 11, the junction temperature can be used to estimate the long-term device reliability. Further, combining Equation 1 and Equation 2 results in a maximum operating frequency for the ASM2I9940L in a series terminated transmission line system, Equation 4.

$$P_{\text{TOT}} = \left[ I_{\text{CCQ}} + V_{\text{CC}} \cdot f_{\text{CLOCK}} \cdot \left( N \cdot C_{\text{PD}} + \sum_{M} C_{L} \right) \right] \cdot V_{\text{CC}}$$

(eq. 1)

$$\mathsf{P}_{\mathsf{TOT}} = \mathsf{V}_{\mathsf{CC}} \cdot \left[ \mathsf{I}_{\mathsf{CCQ}} + \mathsf{V}_{\mathsf{CC}} \cdot f_{\mathsf{CLOCK}} \cdot \left( \mathsf{N} \cdot \mathsf{C}_{\mathsf{PD}} + \sum_{\mathsf{M}} \mathsf{C}_{\mathsf{L}} \right) \right] + \sum_{\mathsf{P}} \left[ \mathsf{DC}_{\mathsf{Q}} \cdot \mathsf{I}_{\mathsf{OH}} \! \! \left( \mathsf{V}_{\mathsf{CC}} - \mathsf{V}_{\mathsf{OH}} \right) + \left( \mathsf{1} - \mathsf{DC}_{\mathsf{Q}} \right) \cdot \mathsf{I}_{\mathsf{OL}} \cdot \mathsf{V}_{\mathsf{OL}} \right] \right] \\ \text{(eq. 2)}$$

$$T_{J} = T_{A} + P_{TOT} \cdot R_{\theta JA}$$

(eq. 3)

$$f_{\text{CLOCKMAX}} = \frac{1}{C_{\text{PD}} \cdot \text{N} \cdot \text{V}_{\text{CC}}^{2}} \cdot \left[ \frac{\text{T}_{\text{JMAX}} - \text{T}_{\text{A}}}{\text{R}_{\theta \text{JA}}} - \left( \text{I}_{\text{CCQ}} \cdot \text{V}_{\text{CC}} \right) \right]$$

(eq. 4)

$T_{J,MAX}$  should be selected according to the MTBF system requirements and Table 11.  $R_{\theta ja}$  can be derived from Table 12. The  $R_{\theta ja}$  represent data based on 1S2P boards, using 2S2P boards will result in a lower thermal impedance than indicated below.

Table 12. THERMAL PACKAGE IMPEDANCE OF THE 32LQFP

| Convection,<br>LFPM | R <sub>thja</sub> (1P2S<br>board), °C/W | R <sub>thja</sub> (2P2S<br>board), °C/W |

|---------------------|-----------------------------------------|-----------------------------------------|

| Still air           | 86                                      | 61                                      |

| 100 lfpm            | 76                                      | 56                                      |

| 200 lfpm            | 71                                      | 54                                      |

| 300 lfpm            | 68                                      | 53                                      |

| 400 lfpm            | 66                                      | 52                                      |

| 500 lfpm            | 60                                      | 49                                      |

If the calculated maximum frequency is below 250 MHz, it becomes the upper clock speed limit for the given application conditions. The following eight derating charts describe the safe frequency operation range for the ASM2I9940L. The charts were calculated for a maximum tolerable die junction temperature of 110°C (120°C),

corresponding to an estimated MTBF of 9.1 years (4 years), a supply voltage of 3.3 V and series terminated transmission line or capacitive loading. Depending on a given set of these operating conditions and the available device convection a decision on the maximum operating frequency can be made.

# **ORDERING INFORMATION**

| Part Number      | Marking | Package                | Temperature    | Shipping <sup>†</sup> |

|------------------|---------|------------------------|----------------|-----------------------|

| ASM2I9940LG-32LT | 2l9940L | 32-pin LQFP<br>Pb-Free | -40°C to +85°C | 250 Units / Tray      |

#### PACKAGE DIMENSIONS

Pentium is a registered trademark of Intel Corporation.

ON Semiconductor and un are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice on semiconductor and are registered readerlands of semiconductor Components industries, Ite (SCILLC) . Solitude services are inject to make triangles without further holice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA

Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com

N. American Technical Support: 800-282-9855 Toll Free USA/Canada

Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910

Japan Customer Focus Center Phone: 81-3-5773-3850

ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative

ASM219940L/D