$2\times 25~\text{mW}$  class-G stereo headphone driver with l^2C-bus volume control

Rev. 01 — 26 March 2010

**Product data sheet**

## 1. General description

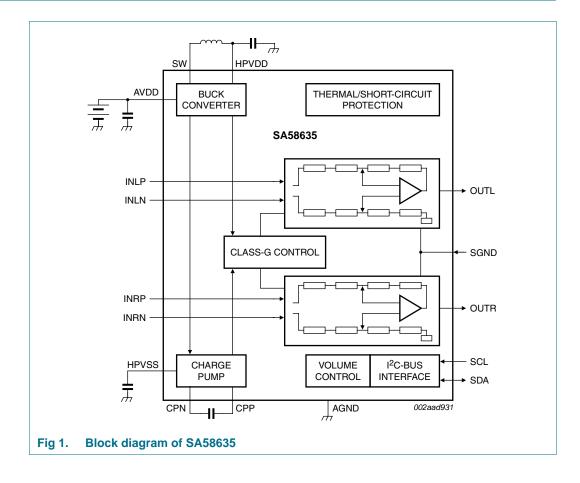

The SA58635 is a stereo, class-G headphone driver with I<sup>2</sup>C-bus volume control. The I<sup>2</sup>C-bus control allows maximum flexibility with digital volume control, independent channel enable and mute control.

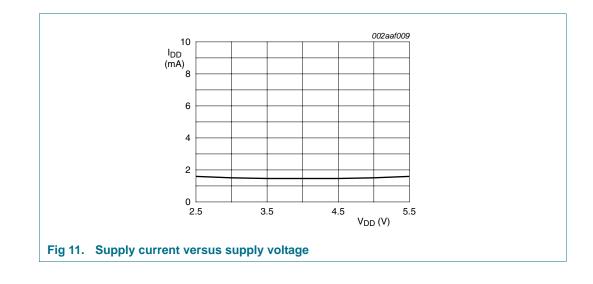

The output of the SA58635 is referenced around true ground zero. It is designed to operate at the low supply current of 1.5 mA making it battery friendly. A unique power management technique provides class-G power efficiency by using a buck converter to step down the battery supply from a typical lithium ion battery (4.8 V to 2.3 V). Efficiency is further increased by allowing the output amplifier/driver to operate at multiple voltage rails based on the output/input swing.

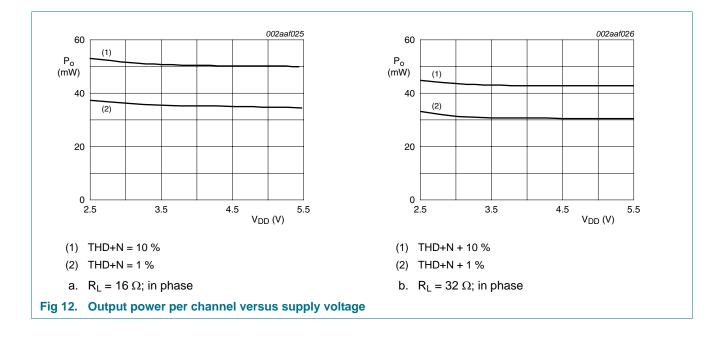

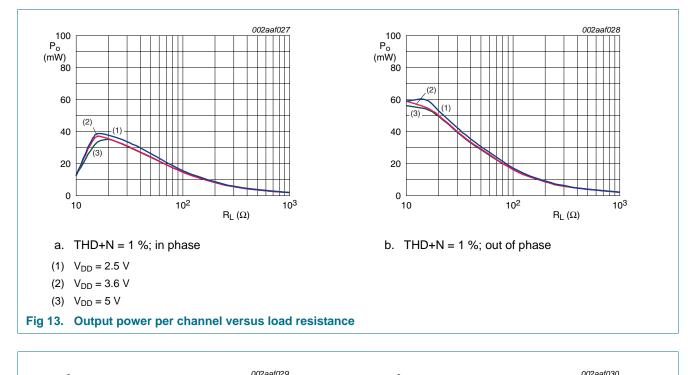

The SA58635 delivers 2  $\times$  25 mW minimum into 16  $\Omega$  and 32  $\Omega$  loads. The SA58635 provides thermal shutdown and self limiting current protection.

The SA58635 is a high fidelity HP driver amplifier with a S/N of 100 dB minimum. An excellent PSRR of more than 100 dB, differential input circuit topology allows for maximum noise immunity in the noisy mobile phone environment.

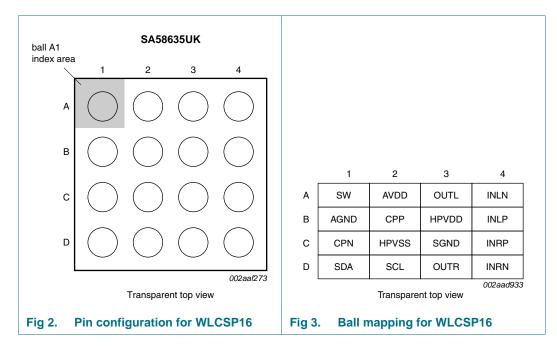

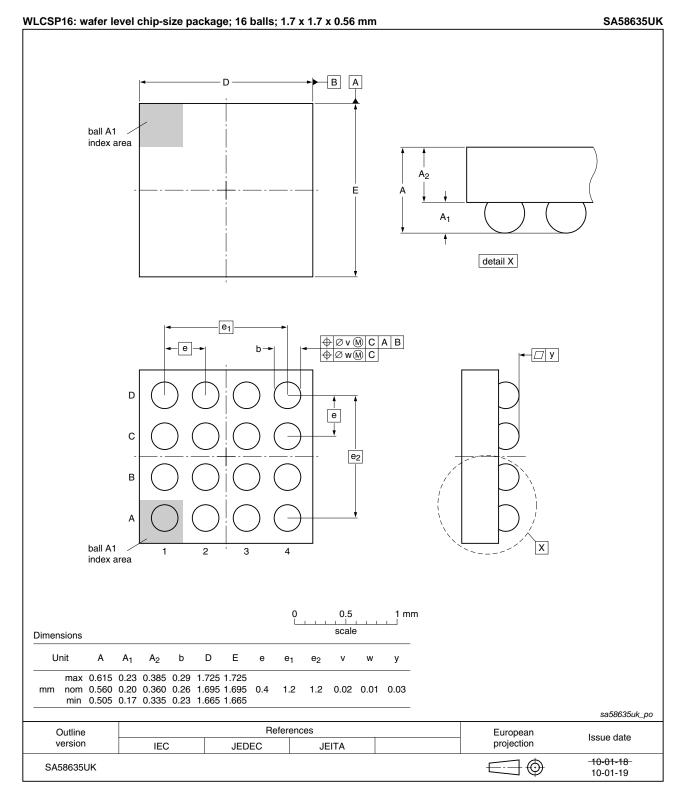

The SA58635 is available in a 16-bump WLCSP (Wafer Level Chip-Size Package) making it ideal choice for cellular handsets and portable media players.

## 2. Features

- Power supply range: 2.3 V to 5.5 V

- High efficiency employing class-G dynamic power management

- 2 × 25 mW into 16 Ω or 32 Ω at THD+N = 1 %

- Very low THD+N at 0.02 % at V<sub>O</sub> of  $0.7V_{o(RMS)}$  and R<sub>L</sub> of 47  $\Omega$

- Integrated charge pump to eliminate DC blocking capacitors, reduce cost and PCB space while improving low frequency audio fidelity

- Excellent PSRR: > 100 dB

- S/N performance of 100 dB minimum

- Low supply current: 1.5 mA typical

- Low shutdown current: 5 μA maximum

- I<sup>2</sup>C-bus interface for –59 dB to ±4 dB volume control, independent channel enable, mute and software shutdown

- Self limiting current with thermal protection and ground loop noise suppression

- Pop-and-click suppression

- Available in 1.7 mm × 1.7 mm 16-bump WLCSP

## 3. Applications

- Wireless and cellular handsets

- Portable media players

- Portable DVD player

- Notebook PC

- High fidelity applications

## 4. Ordering information

| Type number | Package | Package                                                                    |           |  |  |  |  |  |

|-------------|---------|----------------------------------------------------------------------------|-----------|--|--|--|--|--|

|             | Name    | Description                                                                | Version   |  |  |  |  |  |

| SA58635UK   | WLCSP16 | wafer level chip-size package; 16 balls; 1.7 $\times$ 1.7 $\times$ 0.56 mm | SA58635UK |  |  |  |  |  |

## 5. Block diagram

## 6. Pinning information

## 6.1 Pinning

## 6.2 Pin description

| Table 2. | Pin descrij | otion                                          |

|----------|-------------|------------------------------------------------|

| Symbol   | Pin         | Description                                    |

| SW       | A1          | buck converter switching mode                  |

| AVDD     | A2          | analog supply; same as battery                 |

| OUTL     | A3          | headphone left channel output                  |

| INLN     | A4          | left channel negative differential input       |

| AGND     | B1          | analog supply ground                           |

| CPP      | B2          | charge pump positive capacitor                 |

| HPVDD    | B3          | buck converter output voltage                  |

| INLP     | B4          | left channel positive differential input       |

| CPN      | C1          | charge pump negative capacitor                 |

| HPVSS    | C2          | charge pump negative output voltage            |

| SGND     | C3          | ground sense; connect to headphone jack ground |

| INRP     | C4          | right channel positive differential input      |

| SDA      | D1          | I <sup>2</sup> C-bus serial data               |

| SCL      | D2          | I <sup>2</sup> C-bus serial clock              |

| OUTR     | D3          | headphone right channel output                 |

| INRN     | D4          | right channel negative differential input      |

SA58635\_1

Product data sheet

## 7. Functional description

Refer to Figure 1 "Block diagram of SA58635".

### 7.1 Device address

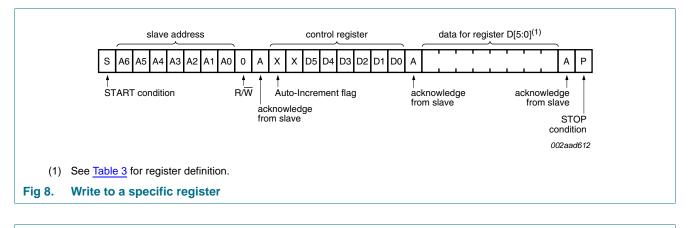

Following a START condition, the bus master must output the address of the slave it is accessing.

The SA58635 responds to two slave addresses: 1100 000xb for standard accesses and the General Call writes (0000 0000b) for software reset. The last bit of the address byte defines the operation to be performed. When set to logic 1 a read is selected, while a logic 0 selects a write operation.

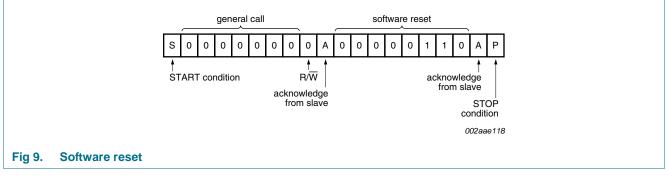

When a reset of the I<sup>2</sup>C-bus needs to be performed by the master, the master will write to the General Call address followed by a write of the reset command (0000 0110b). When a General Call reset command is sent by the master, the SA58635 will respond with an acknowledge and execute a reset to the digital logic. This will return the register set and the volume controls to the Power-On Reset (POR) values.

### 7.2 Control register

Following the successful acknowledgement of the slave address, the bus master will send a byte to the SA58635, which will be stored in the Control register.

The lowest 3 bits are used as a pointer to determine which register will be accessed (D[2:0]). The remaining bits are not used and are ignored.

## 7.3 Register definitions

| Table 3.                    | Register su | mmary      |                                                                                                          |

|-----------------------------|-------------|------------|----------------------------------------------------------------------------------------------------------|

| Register<br>number<br>(hex) | Name        | Туре       | Function                                                                                                 |

| 00                          | -           | -          | Reserved; this address is empty and will be NACKed.                                                      |

| 01                          | MODE1       | read/write | Contains the left and right channel amplifier enable bits, thermal status and the software shutdown bit. |

| 02                          | VOLCTL      | read/write | Volume setting and mute left and right bits.                                                             |

| 03                          | HIZ         | read/write | High-impedance controls for left and right channel.                                                      |

| 04                          | ID          | read only  | Vendor Identification and chip version number.                                                           |

| 05                          | -           | -          | Reserved; this address is empty and will be NACKed.                                                      |

| 06                          | TEST1       | read/write | This register is for manufacturing test.                                                                 |

| 07                          | -           | read/write | Reserved; this register is empty and will be NACKed.                                                     |

### 7.3.1 MODE1 register, MODE1

# Table 4. MODE1 - Mode register 1 (address 01h) bit description Legend: \* default value.

| Bit | Symbol  | Access      | Value | Description                                                     |

|-----|---------|-------------|-------|-----------------------------------------------------------------|

| 7   | HP_EN_L | IP_EN_L R/W | 0*    | Left channel inactive. A zero will turn off the left channel.   |

|     |         |             | 1     | Left channel active.                                            |

| 6   | HP_EN_R | R/W         | 0*    | Right channel inactive. A zero will turn off the right channel. |

|     |         |             | 1     | Right channel active.                                           |

| 5   | -       | read only   | 0*    | Reserved; always reads back as a 0.                             |

| 4   | -       | read only   | 0*    | Reserved; always reads back as a 0.                             |

| 3   | -       | read only   | 0*    | Reserved; always reads back as a 0.                             |

| 2   | -       | read only   | 0*    | Reserved; always reads back as a 0.                             |

| 1   | THERMAL | read only   | 0*    | Device is operating normally.                                   |

|     |         |             | 1     | Device is in thermal shutdown.                                  |

| 0   | SWS     | R/W         | 0*    | Device is enabled.                                              |

|     |         |             | 1     | Software shutdown; charge pump is disabled.                     |

|     |         |             |       |                                                                 |

#### 7.3.2 Volume control register, VOLCTL

# Table 5. VOLCTL - Volume control register (address 02h) bit description Legend: \* default value.

| Bit    | Symbol   | Access    | Value | Description                                                                                |

|--------|----------|-----------|-------|--------------------------------------------------------------------------------------------|

| 7      | MUTEL    | R/W       | 0     | A zero indicates that the left channel is not muted.                                       |

|        |          |           | 1*    | Left channel is muted.                                                                     |

| 6      | MUTER    |           | 0     | A zero indicates that the right channel is not muted.                                      |

|        |          |           | 1*    | Right channel is muted.                                                                    |

| 5 to 1 | VOL[4:0] | R/W       | 0*    | These bits indicate the volume on the outputs per the gain table shown in <u>Table 9</u> . |

| 0      | -        | read only | 0*    | This bit is reserved and will always return a zero.                                        |

#### 7.3.3 High-impedance register, HIZ

# Table 6. HIZ - High-impedance register (address 03h) bit description Legend: \* default value.

| Bit    | Symbol   | Access    | Value | Description                               |

|--------|----------|-----------|-------|-------------------------------------------|

| 7 to 2 | -        | read only | 0*    | Unused; always returns 0.                 |

| 1      | HIZL R/W |           | 0*    | Device outputs are not in high-impedance. |

|        |          |           | 1     | Device outputs are in high-impedance.     |

| 0      | HIZR     | R/W       | 0*    | Device outputs are not in high-impedance. |

|        |          |           | 1     | Device outputs are in high-impedance.     |

Product data sheet

#### 7.3.4 Chip identification register, ID

# Table 7. ID - Chip identification register (address 04h) bit description Legend: \* default value.

| Bit    | Symbol   | Access    | Value | Description                                                                                                                   |

|--------|----------|-----------|-------|-------------------------------------------------------------------------------------------------------------------------------|

| 7 to 6 | SUPPLIER | read only | 11b*  | This is the supplier identification for this device,<br>indicating that this device is manufactured by<br>NXP Semiconductors. |

| 5 to 4 | -        | read only | 00b*  | Unused; always returns 0.                                                                                                     |

| 3 to 0 | VER[3:0] | read only | 0000b | These bits indicate the version number for this device. Initial silicon will be set to 0h.                                    |

### 7.3.5 Test register 1, TEST1

## Table 8. TEST1 - Test register 1 (address 06h) bit description Legend: \* default value \*

| Leyenu. | Legend. delaut value. |        |       |                                                                                                                                                                                      |  |  |  |  |

|---------|-----------------------|--------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Bit     | Symbol                | Access | Value | Description                                                                                                                                                                          |  |  |  |  |

| 7 to 0  | -                     | R/W    | 00h*  | Software should refrain from writing to this register.<br>Software should write only 0's to this register.<br>Values other than 0 may cause the part to not<br>function as expected. |  |  |  |  |

SA58635\_1

### 7.4 Volume control

Volume levels are set in the VOLCTL register (register 02h) as described in <u>Section 7.3.2</u>. As the volume is changed including muting and un-muting, the SA58635, will step to the new value at an incremental (or decremental) rate of approximately one millisecond per step. A full sweep from 00h to 1Fh will take roughly 32 milliseconds. The VOLCTL register values represent a gain on the output channels as indicated in <u>Table 9</u>.

| Table 9.   Volume and gain co | ontrol              |

|-------------------------------|---------------------|

| Volume control word           | Gain $\pm$ 0.5 (dB) |

| 0000 000x                     | -59                 |

| 0000 001x                     | -55                 |

| 0000 010x                     | -51                 |

| 0000 011x                     | -47                 |

| 0000 100x                     | -43                 |

| 0000 101x                     | -39                 |

| 0000 110x                     | -35                 |

| 0000 111x                     | -31                 |

| 0001 000x                     | -27                 |

| 0001 001x                     | -25                 |

| 0001 010x                     | -23                 |

| 0001 011x                     | -21                 |

| 0001 100x                     | –19                 |

| 0001 101x                     | –17                 |

| 0001 110x                     | –15                 |

| 0001 111x                     | –13                 |

| 0010 000x                     | –11                 |

| 0010 001x                     | –10                 |

| 0010 010x                     | -9                  |

| 0010 011x                     | -8                  |

| 0010 100x                     | -7                  |

| 0010 101x                     | -6                  |

| 0010 110x                     | -5                  |

| 0010 111x                     | -4                  |

| 0011 000x                     | -3                  |

| 0011 001x                     | -2                  |

| 0011 010x                     | -1                  |

| 0011 011x                     | 0                   |

| 0011 100x                     | +1                  |

| 0011 101x                     | +2                  |

| 0011 110x                     | +3                  |

| 0011 111x                     | +4                  |

| 1xxx xxxx                     | Mute Left active    |

| x1xx xxxx                     | Mute Right active   |

SA58635\_1

**Product data sheet**

#### 7.5 Power-on reset

When power is applied to AVDD, an internal power-on reset holds the SA58635 in a reset condition until AVDD has reached  $V_{POR}$ . At this point, the reset condition is released and the SA58635 registers and I<sup>2</sup>C-bus state machine are initialized to their default states (all zeroes) causing all the channels to be deselected. Thereafter, AVDD must be lowered below 0.2 V to reset the device.

## 8. Characteristics of the I<sup>2</sup>C-bus

The I<sup>2</sup>C-bus is for 2-way, 2-line communication between different ICs or modules. The two lines are a serial data line (SDA) and a serial clock line (SCL). Both lines must be connected to a positive supply via a pull-up resistor when connected to the output stages of a device. Data transfer may be initiated only when the bus is not busy.

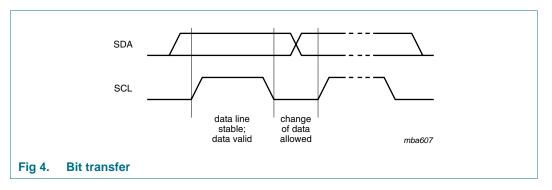

### 8.1 Bit transfer

One data bit is transferred during each clock pulse. The data on the SDA line must remain stable during the HIGH period of the clock pulse as changes in the data line at this time will be interpreted as control signals (see Figure 4).

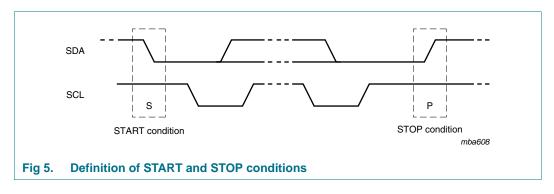

#### 8.1.1 START and STOP conditions

Both data and clock lines remain HIGH when the bus is not busy. A HIGH-to-LOW transition of the data line while the clock is HIGH is defined as the START condition (S). A LOW-to-HIGH transition of the data line while the clock is HIGH is defined as the STOP condition (P) (see Figure 5).

### 8.2 System configuration

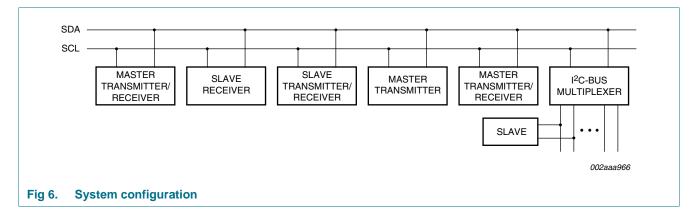

A device generating a message is a 'transmitter'; a device receiving is the 'receiver'. The device that controls the message is the 'master' and the devices which are controlled by the master are the 'slaves' (see Figure 6).

### 8.3 Acknowledge

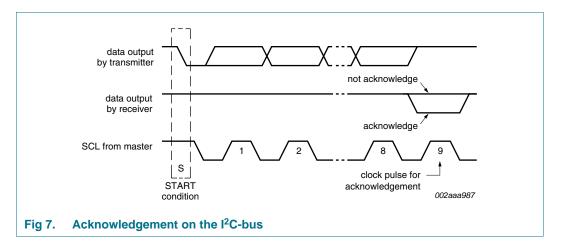

The number of data bytes transferred between the START and the STOP conditions from transmitter to receiver is not limited. Each byte of eight bits is followed by one acknowledge bit. The acknowledge bit is a HIGH level put on the bus by the transmitter, whereas the master generates an extra acknowledge related clock pulse.

A slave receiver which is addressed must generate an acknowledge after the reception of each byte. Also a master must generate an acknowledge after the reception of each byte that has been clocked out of the slave transmitter. The device that acknowledges has to pull down the SDA line during the acknowledge clock pulse, so that the SDA line is stable LOW during the HIGH period of the acknowledge related clock pulse; set-up time and hold time must be taken into account.

A master receiver must signal an end of data to the transmitter by not generating an acknowledge on the last byte that has been clocked out of the slave. In this event, the transmitter must leave the data line HIGH to enable the master to generate a STOP condition.

**Product data sheet**

$2 \times 25$  mW class-G stereo headphone driver

## 9. Bus transactions

## **10. Limiting values**

#### Table 10. Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134).[1]

| Symbol           | Parameter                          | Conditions                          | Min              | Max             | Unit |

|------------------|------------------------------------|-------------------------------------|------------------|-----------------|------|

| V <sub>DD</sub>  | supply voltage                     | Active mode                         | -0.3             | +6.0            | V    |

|                  |                                    | Shutdown mode                       | -0.3             | +6.0            | V    |

| VI               | input voltage                      | INRN, INRP, INLN, INLP              | -0.3             | 2.1             | V    |

| V <sub>IO</sub>  | input/output voltage               | SCL, SDA                            | $V_{AGND} - 0.5$ | V <sub>DD</sub> | V    |

| I <sub>BR</sub>  | breakdown current                  | continuous                          | [2] _            | 200             | mA   |

| Р                | power dissipation                  | WLCSP16; derating factor 10 mW/K    |                  |                 |      |

|                  |                                    | T <sub>amb</sub> = 25 °C            | -                | 1000            | mW   |

|                  |                                    | T <sub>amb</sub> = 70 °C            | -                | 550             | mW   |

|                  |                                    | T <sub>amb</sub> = 85 °C            | -                | 400             | mW   |

| T <sub>amb</sub> | ambient temperature                | operating in free air               | -40              | +85             | °C   |

| Tj               | junction temperature               | operating                           | -40              | +85             | °C   |

| T <sub>stg</sub> | storage temperature                |                                     | -65              | +150            | °C   |

| V <sub>ESD</sub> | electrostatic discharge<br>voltage | human body model                    | ±4000            | -               | V    |

|                  |                                    | machine model                       | ±300             | -               | V    |

|                  |                                    | charged-device model                | ±750             | -               | V    |

|                  |                                    | device use level:                   |                  |                 |      |

|                  |                                    | IEC61000-4-2 level 4, contact       | <u>[3]</u> ±30   | -               | kV   |

|                  |                                    | IEC61000-4-2 level 4, air discharge | <u>[3]</u> ±30   | -               | kV   |

[1] V<sub>DD</sub> is the supply voltage on pin AVDD.

[2] Breakdown current of output protection diodes.

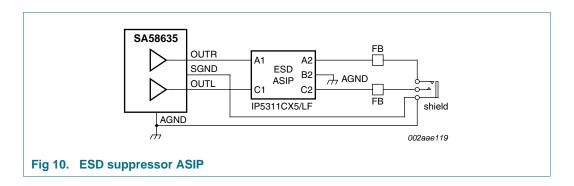

[3] ESD shock needs to be conducted to the connector pins (see Figure 10).

All functions of a device/system perform as designed during and after exposure to a disturbance.

Remark: External ESD suppressor ASIP protects the amplifier outputs. Suppressor is between amplifier and connector;

15  $\Omega$  serial resistance + 5 nF capacitor and Zener diodes (14 V breakdown voltage) connected to the ground. In addition, there is a ferrite bead in series between suppressor and connector (see Figure 10).

**Remark:** Air discharge test can be ignored if contact discharge test range is increased to corresponding same voltages as air discharge (reason: contact discharge is more stable and repeatable test than air discharge).

SA58635\_1

$2\times25$  mW class-G stereo headphone driver

## 11. Static characteristics

#### Table 11. Static characteristics

$V_{DD} = 3.6 \text{ V}; R_L = 15 \Omega + 32 \Omega;$  two channels in phase;  $T_{amb} = 25 \text{ °C}$ , unless otherwise specified.<sup>[1]</sup>

| 66                     | ,                            | i , and ,                                       | 1    |     |      |      |

|------------------------|------------------------------|-------------------------------------------------|------|-----|------|------|

| Symbol                 | Parameter                    | Conditions                                      | Min  | Тур | Max  | Unit |

| V <sub>DD</sub>        | supply voltage               | continuous                                      | 2.3  | -   | 5.5  | V    |

| I <sub>DD</sub>        | supply current               | both channels enabled;<br>no audio signal       | -    | 1.5 | -    | mA   |

| I <sub>DD(sd)</sub>    | shutdown mode supply current | I <sup>2</sup> C-bus in operation               | -    | 1   | 5    | μA   |

| V <sub>i(cm)</sub>     | common-mode input voltage    | differential                                    | -1.3 | -   | +1.3 | V    |

| V <sub>POR</sub>       | power-on reset voltage       |                                                 | -    | 2.1 | -    | V    |

| V <sub>O(offset)</sub> | output offset voltage        | absolute value;<br>both channels enabled        | -    | 0.5 | 3    | mV   |

| PSRR                   | power supply rejection ratio | $G_v = 0 dB$                                    | 100  | -   | -    | dB   |

| Zi                     | input impedance              | differential                                    | 20   | -   | -    | kΩ   |

| Zo                     | output impedance             | high-impedance mode                             |      |     |      |      |

|                        |                              | <40 kHz                                         | 10   | -   | -    | kΩ   |

|                        |                              | 6 MHz                                           | 500  | -   | -    | Ω    |

|                        |                              | 36 MHz                                          | 75   | -   | -    | Ω    |

| I <sup>2</sup> C-bus p | ins (SCL, SDA)               |                                                 |      |     |      |      |

| I <sub>OL</sub>        | LOW-level output current     | SDA output; $V_{OL} = 0.4 V$ ; $V_{DD} = 3.6 V$ | 3    | -   | -    | mA   |

| I <sub>LI</sub>        | input leakage current        | SCL, SDA                                        | -1   | -   | +1   | μA   |

| Ci                     | input capacitance            | SCL, SDA                                        | -    | -   | 10   | pF   |

| V <sub>IH</sub>        | HIGH-level input voltage     | SCL, SDA                                        | 1.2  | -   | -    | V    |

| V <sub>IL</sub>        | LOW-level input voltage      | SCL, SDA                                        | -    | -   | 0.6  | V    |

| -                      |                              |                                                 |      |     |      |      |

[1]  $V_{DD}$  is the supply voltage on pin AVDD.

**Product data sheet**

$2 \times 25$  mW class-G stereo headphone driver

## **12. Dynamic characteristics**

#### Table 12. Dynamic characteristics

$V_{DD} = 3.6 \text{ V}; R_L = 15 \Omega + 32 \Omega;$  two channels in phase;  $T_{amb} = 25 \text{ °C};$  unless otherwise specified.<sup>[1]</sup>

| Symbol                     | Parameter                               | Conditions                                         | Min        | Тур | Max  | Unit |

|----------------------------|-----------------------------------------|----------------------------------------------------|------------|-----|------|------|

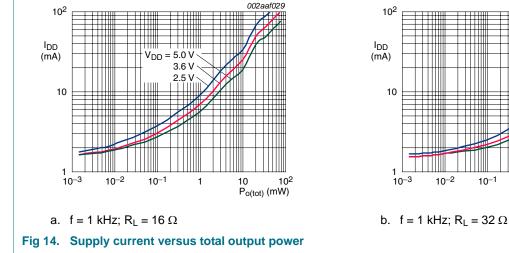

| Po                         | output power                            | stereo; f = 1 kHz; THD+N = 1 %                     | 2 	imes 25 | -   | -    | mW   |

| I <sub>DD</sub>            | supply current                          | output 2 $\times$ 100 $\mu W$ at 3 dB crest factor | -          | 2.5 | 3.5  | mA   |

|                            |                                         | output 2 $\times$ 500 $\mu W$ at 3 dB crest factor | -          | 4.5 | 5.5  | mA   |

|                            |                                         | output $2 \times 1$ mW at 3 dB crest factor        | -          | 6.5 | 7.5  | mA   |

| V <sub>o(RMS)</sub>        | RMS output voltage                      | amplifier                                          |            |     |      |      |

|                            |                                         | $R_L$ = 16 $\Omega$ ; THD+N = 1 %; L + R in phase  | 0.63       | -   | -    | V    |

|                            |                                         | $R_L$ = 32 $\Omega$ ; THD+N = 1 %; L + R in phase  | 0.89       | -   | -    | V    |

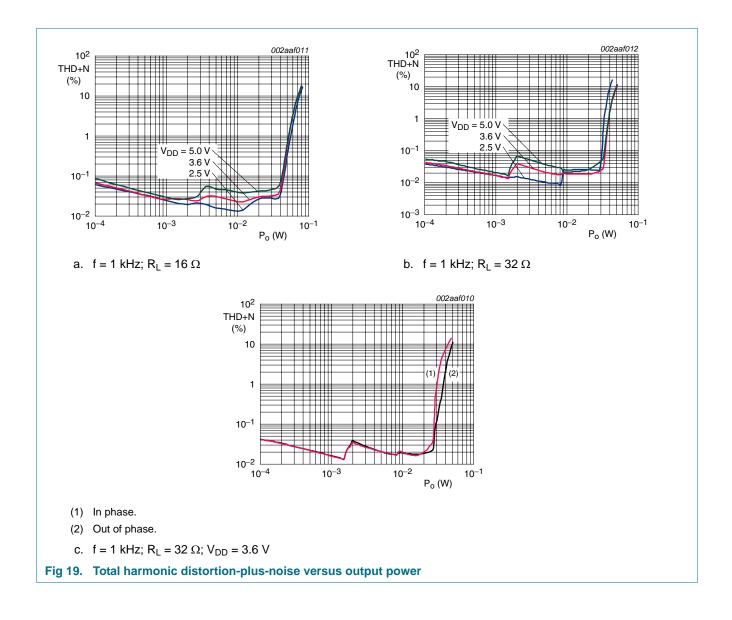

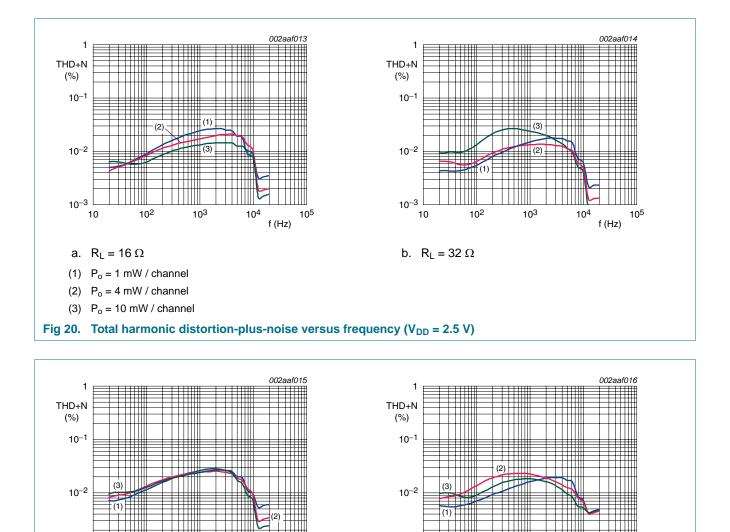

| THD+N                      | total harmonic<br>distortion-plus-noise | f = 1 kHz; V <sub>O</sub> = 700 mV (RMS)           | -          | -   | 0.02 | %    |

| SVRR                       | supply voltage ripple rejection         | G <sub>v</sub> = 4 dB; f = 217 Hz                  | 75         | -   | -    | dB   |

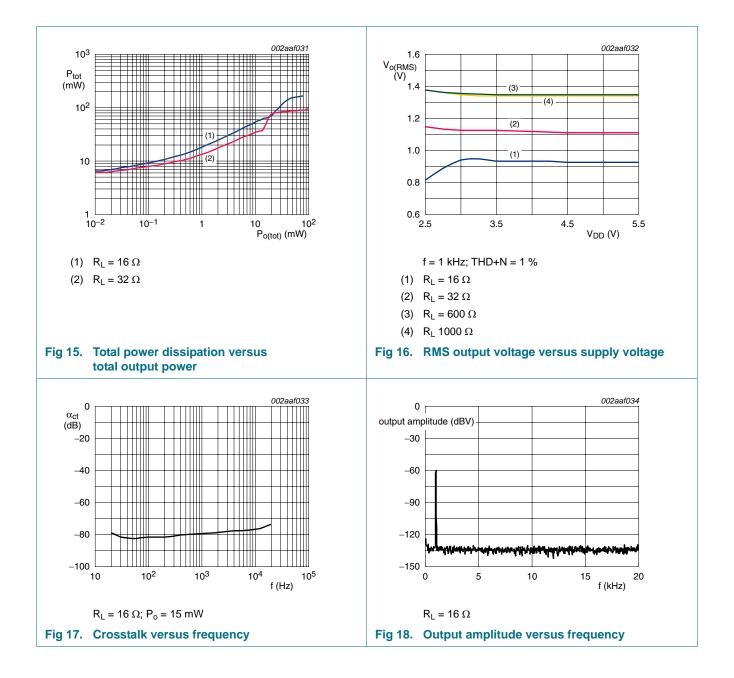

| $\alpha_{ct(ch)}$          | channel crosstalk                       | $P_{o} = 15 \text{ mW}; f = 1 \text{ kHz}$         | 90         | -   | -    | dB   |

|                            |                                         | line out > 10 k $\Omega$                           | 80         | -   | -    | dB   |

| V <sub>n(o)(RMS)</sub>     | RMS output noise voltage                | $G_v = 4 \text{ dB}; \text{ A-weight}$             | -          | 7   | -    | μV   |

| t <sub>d(sd-startup)</sub> | delay time from shutdown to start-up    |                                                    | -          | -   | 15   | ms   |

| S/N                        | signal-to-noise ratio                   | V <sub>O</sub> = 1 V (RMS); f = 1 kHz              | 100        | -   | -    | dB   |

| T <sub>off</sub>           | switch-off temperature                  | threshold                                          | -          | 180 | -    | °C   |

|                            |                                         | hysteresis                                         | -          | 35  | -    | °C   |

[1]  $V_{DD}$  is the supply voltage on pin AVDD.

# **SA58635**

#### $2 \times 25$ mW class-G stereo headphone driver

= 50 VV<sub>DD</sub>

3.6 \

5

10 10<sup>2</sup> P<sub>o(tot)</sub> (mW)

10-2

10-1

1

# SA58635

#### $2\times25$ mW class-G stereo headphone driver

# SA58635

#### $2\times25$ mW class-G stereo headphone driver

# SA58635

#### $2\times25$ mW class-G stereo headphone driver

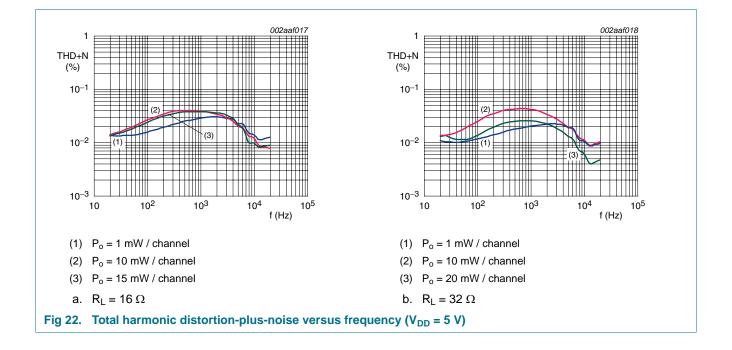

10<sup>-3</sup>

10

b.  $R_L = 32 \Omega$

10<sup>2</sup>

10<sup>3</sup>

10<sup>4</sup>

10<sup>5</sup>

f (Hz)

SA58635 1

10<sup>-3</sup>

10

a.  $R_L = 16 \Omega$

(1)  $P_o = 1 \text{ mW} / \text{channel}$ (2)  $P_o = 10 \text{ mW} / \text{channel}$ (3)  $P_o = 15 \text{ mW} / \text{channel}$

10<sup>2</sup>

10<sup>3</sup>

104

Fig 21. Total harmonic distortion-plus-noise versus frequency (V<sub>DD</sub> = 3.6 V)

10<sup>5</sup>

f (Hz)

# SA58635

#### $2\times 25\ \text{mW}$ class-G stereo headphone driver

#### $2\times25$ mW class-G stereo headphone driver

#### $2 \times 25$ mW class-G stereo headphone driver

| Symbol              | Parameter                                                         | Conditions |     | Standard-mode<br>I <sup>2</sup> C-bus |      | Fast-mode<br>I <sup>2</sup> C-bus     |     | Unit |

|---------------------|-------------------------------------------------------------------|------------|-----|---------------------------------------|------|---------------------------------------|-----|------|

|                     |                                                                   |            |     | Min                                   | Max  | Min                                   | Max |      |

| f <sub>SCL</sub>    | SCL clock frequency                                               |            |     | 0                                     | 100  | 0                                     | 400 | kHz  |

| t <sub>BUF</sub>    | bus free time between a STOP and START condition                  |            |     | 4.7                                   | -    | 1.3                                   | -   | μS   |

| t <sub>HD;STA</sub> | hold time (repeated) START condition                              |            |     | 4.0                                   | -    | 0.6                                   | -   | μS   |

| t <sub>SU;STA</sub> | set-up time for a repeated START condition                        |            |     | 4.7                                   | -    | 0.6                                   | -   | μS   |

| t <sub>SU;STO</sub> | set-up time for STOP condition                                    |            |     | 4.0                                   | -    | 0.6                                   | -   | μS   |

| t <sub>HD;DAT</sub> | data hold time                                                    |            |     | 0                                     | -    | 0                                     | -   | ns   |

| t <sub>VD;ACK</sub> | data valid acknowledge time                                       | ļ          | [1] | 0.3                                   | 3.45 | 0.1                                   | 0.9 | μS   |

| t <sub>VD;DAT</sub> | data valid time                                                   | ļ          | 2]  | 0.3                                   | 3.45 | 0.1                                   | 0.9 | μS   |

| t <sub>SU;DAT</sub> | data set-up time                                                  |            |     | 250                                   | -    | 100                                   | -   | ns   |

| t <sub>LOW</sub>    | LOW period of the SCL clock                                       |            |     | 4.7                                   | -    | 1.3                                   | -   | μS   |

| t <sub>HIGH</sub>   | HIGH period of the SCL clock                                      |            |     | 4.0                                   | -    | 0.6                                   | -   | μS   |

| t <sub>f</sub>      | fall time of both SDA and SCL signals                             | [3]        | [4] | -                                     | 300  | 20 + 0.1C <sub>b</sub> 5              | 300 | ns   |

| t <sub>r</sub>      | rise time of both SDA and SCL signals                             |            |     | -                                     | 1000 | 20 + 0.1C <sub>b</sub> <sup>[5]</sup> | 300 | ns   |

| t <sub>SP</sub>     | pulse width of spikes that must be suppressed by the input filter | l          | [6] | -                                     | 50   | -                                     | 50  | ns   |

#### Table 13. Dynamic characteristics for I<sup>2</sup>C-bus

[1]  $t_{VD;ACK}$  = time for Acknowledgement signal from SCL LOW to SDA (out) LOW.

[2] t<sub>VD;DAT</sub> = minimum time for SDA data out to be valid following SCL LOW.

[3] A master device must internally provide a hold time of at least 300 ns for the SDA signal (refer to the V<sub>IL</sub> of the SCL signal) in order to bridge the undefined region of SCL's falling edge.

[4] The maximum t<sub>f</sub> for the SDA and SCL bus lines is specified at 300 ns. The maximum fall time (t<sub>f</sub>) for the SDA output stage is specified at 250 ns. This allows series protection resistors to be connected between the SDA and the SCL pins and the SDA/SCL bus lines without exceeding the maximum specified t<sub>f</sub>.

[5]  $C_b = total capacitance of one bus line in pF.$

[6] Input filters on the SDA and SCL inputs suppress noise spikes less than 50 ns.

## **13. Application information**

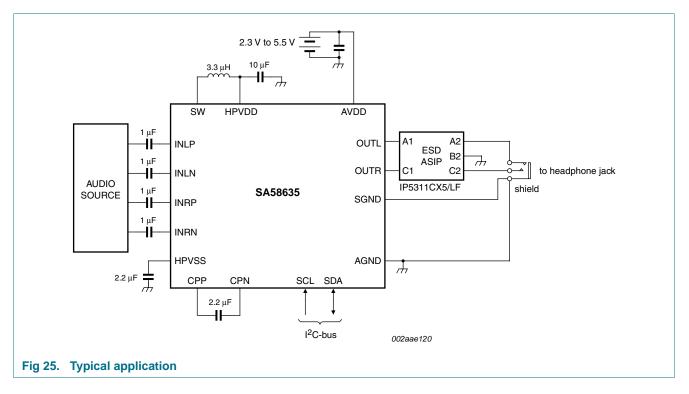

### 13.1 Power supply decoupling considerations

The SA58635 is a stereo class-G headphone driver amplifier that requires proper power supply decoupling to ensure the rated performance for THD+N and power efficiency. To decouple high frequency transients, power supply spikes and digital noise on the power bus line, a low Equivalent Series Resistance (ESR) capacitor, of typically 1  $\mu$ F is placed as close as possible to the AVDD terminals of the device. It is important to place the decoupling capacitor at the power pins of the device because any resistance or inductance in the PCB trace between the device and the capacitor can cause a loss in efficiency. 10  $\mu$ F or greater capacitors are usually not required due to high PSRR of the SA58635.

### 13.2 Input capacitor selection

The SA58635 does not require input coupling capacitors when used with a differential audio source that is biased from -1.3 V to +1.3 V. In other words, the input signal must be biased within the common-mode input voltage range. If high-pass filtering is required or if it is driven using a single-ended source, input coupling capacitors are required.

The 3 dB cut-off frequency is created by the input coupling capacitors and the input resistance of the SA58635. C<sub>i</sub> is the value of the input coupling capacitors. The input resistance (R<sub>i</sub>) of the SA58635 is a function of amplifier gain; it will vary from approximately 11.06 k $\Omega$  (minimum) to 28.47 k $\Omega$  (maximum) (see Table 14).

| Table 14. | Input resistance as a function of amplifier gain |           |  |  |  |

|-----------|--------------------------------------------------|-----------|--|--|--|

| Steps     | <b>R<sub>i</sub> (k</b> Ω <b>)</b>               | Gain (dB) |  |  |  |

| 0         | 28.468                                           | -58.986   |  |  |  |

| 1         | 28.450                                           | -55.185   |  |  |  |

| 2         | 28.421                                           | -51.083   |  |  |  |

| 3         | 28.375                                           | -47.117   |  |  |  |

| 4         | 28.298                                           | -42.942   |  |  |  |

| 5         | 28.177                                           | -38.819   |  |  |  |

| 6         | 27.995                                           | -34.884   |  |  |  |

| 7         | 27.697                                           | -30.758   |  |  |  |

| 8         | 27.302                                           | -27.155   |  |  |  |

| 9         | 26.982                                           | -24.997   |  |  |  |

| 10        | 26.587                                           | -22.858   |  |  |  |

| 11        | 26.163                                           | -20.981   |  |  |  |

| 12        | 25.550                                           | -18.751   |  |  |  |

| 13        | 24.910                                           | -16.826   |  |  |  |

| 14        | 24.183                                           | -14.967   |  |  |  |

| 15        | 23.264                                           | -12.953   |  |  |  |

| 16        | 22.173                                           | -10.893   |  |  |  |

| 17        | 21.560                                           | -9.846    |  |  |  |

| 18        | 20.947                                           | -8.861    |  |  |  |

| 19        | 20.334                                           | -7.925    |  |  |  |

| 20        | 19.607                                           | -6.868    |  |  |  |

| 21        | 18.880                                           | -5.857    |  |  |  |

| 22        | 18.267                                           | -5.034    |  |  |  |

| 23        | 17.420                                           | -3.930    |  |  |  |

| 24        | 16.572                                           | -2.857    |  |  |  |

| 25        | 15.725                                           | -1.804    |  |  |  |

| 26        | 14.998                                           | -0.913    |  |  |  |

| 27        | 14.207                                           | 0.052     |  |  |  |

| 28        | 13.480                                           | 0.939     |  |  |  |

| 29        | 12.754                                           | 1.831     |  |  |  |

| 30        | 11.906                                           | 2.884     |  |  |  |

| 31        | 11.058                                           | 3.958     |  |  |  |

|           |                                                  |           |  |  |  |

Table 14. Input resistance as a function of amplifier gain

The 3 dB cut-off frequency is calculated by Equation 1:

$$f_{-3dB} = \frac{1}{2\pi \times R_i \times C_i} \tag{1}$$

Since the values of the input coupling capacitor and the input resistor affects the low frequency performance of the audio amplifier, it is important to consider in the system design.

For a required 3 dB cut-off frequency, Equation 2 is used to determine  $C_i$ :

$$C_i = \frac{1}{2\pi \times R_i \times f_{-3dB}}$$

(2)

For  $C_i = 1 \ \mu$ F, the 3 dB cut-off frequency will vary with gain settings. For gain setting of 4 dB, the SA58635 input resistance,  $R_i$  is 11.06 k $\Omega$  (refer to <u>Table 14</u>). Substituting  $R_i$  and  $C_i$  in <u>Equation 1</u> yields  $f_{-3dB} = 14.4$  Hz.

### **13.3 PCB layout considerations**

Component location is very important for performance of the SA58635. Place all external components very close to the device. Placing decoupling capacitors directly at the power supply pins increases efficiency because the resistance and inductance in the trace between the device power supply pins and the decoupling capacitor causes a loss in power efficiency.

The trace width and routing are also very important for power output and noise considerations.

For the input pins (INLP, INLN, INRP, INRN), the traces must be symmetrical and run side-by-side to maximize common-mode cancellation.

#### **13.4 Thermal information**

The SA58635 16-bump WLCSP package ground bumps are soldered directly to the PCB heat spreader. The heat spreader is the PCB ground plane or special heat sinking layer designed into the PCB. The thickness and area of the heat spreader may be maximized to optimize heat transfer and achieve lower package thermal resistance.

SA58635\_1

$2\times25$  mW class-G stereo headphone driver

## 14. Package outline

#### Fig 26. Package outline SA58635UK (WLCSP16)

SA58635\_1

Product data sheet

## **15. Soldering of WLCSP packages**

### 15.1 Introduction to soldering WLCSP packages

This text provides a very brief insight into a complex technology. A more in-depth account of soldering WLCSP (Wafer Level Chip-Size Packages) can be found in application note *AN10439 "Wafer Level Chip Scale Package"* and in application note *AN10365 "Surface mount reflow soldering description"*.

Wave soldering is not suitable for this package.

All NXP WLCSP packages are lead-free.

### 15.2 Board mounting

Board mounting of a WLCSP requires several steps:

- 1. Solder paste printing on the PCB

- 2. Component placement with a pick and place machine

- 3. The reflow soldering itself

### 15.3 Reflow soldering

Key characteristics in reflow soldering are:

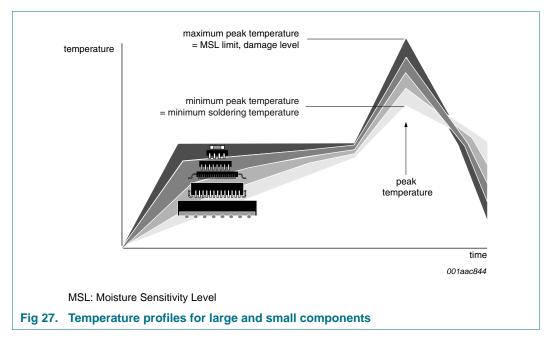

- Lead-free versus SnPb soldering; note that a lead-free reflow process usually leads to higher minimum peak temperatures (see <u>Figure 27</u>) than a PbSn process, thus reducing the process window

- Solder paste printing issues, such as smearing, release, and adjusting the process window for a mix of large and small components on one board

- Reflow temperature profile; this profile includes preheat, reflow (in which the board is heated to the peak temperature), and cooling down. It is imperative that the peak temperature is high enough for the solder to make reliable solder joints (a solder paste characteristic) while being low enough that the packages and/or boards are not damaged. The peak temperature of the package depends on package thickness and volume and is classified in accordance with <u>Table 15</u>.

| Package thickness (mm) | Package reflow temperature (°C) |             |        |  |  |

|------------------------|---------------------------------|-------------|--------|--|--|

|                        | Volume (mm <sup>3</sup> )       |             |        |  |  |

|                        | < 350                           | 350 to 2000 | > 2000 |  |  |

| < 1.6                  | 260                             | 260         | 260    |  |  |

| 1.6 to 2.5             | 260                             | 250         | 245    |  |  |

| > 2.5                  | 250                             | 245         | 245    |  |  |

#### Table 15. Lead-free process (from J-STD-020C)

Moisture sensitivity precautions, as indicated on the packing, must be respected at all times.

Studies have shown that small packages reach higher temperatures during reflow soldering, see Figure 27.

SA58635\_1 Product data sheet

$2 \times 25$  mW class-G stereo headphone driver

For further information on temperature profiles, refer to application note *AN10365 "Surface mount reflow soldering description".*

#### 15.3.1 Stand off

The stand off between the substrate and the chip is determined by:

- The amount of printed solder on the substrate

- The size of the solder land on the substrate

- The bump height on the chip

The higher the stand off, the better the stresses are released due to TEC (Thermal Expansion Coefficient) differences between substrate and chip.

#### 15.3.2 Quality of solder joint

A flip-chip joint is considered to be a good joint when the entire solder land has been wetted by the solder from the bump. The surface of the joint should be smooth and the shape symmetrical. The soldered joints on a chip should be uniform. Voids in the bumps after reflow can occur during the reflow process in bumps with high ratio of bump diameter to bump height, i.e. low bumps with large diameter. No failures have been found to be related to these voids. Solder joint inspection after reflow can be done with X-ray to monitor defects such as bridging, open circuits and voids.

#### 15.3.3 Rework

In general, rework is not recommended. By rework we mean the process of removing the chip from the substrate and replacing it with a new chip. If a chip is removed from the substrate, most solder balls of the chip will be damaged. In that case it is recommended not to re-use the chip again.

Device removal can be done when the substrate is heated until it is certain that all solder joints are molten. The chip can then be carefully removed from the substrate without damaging the tracks and solder lands on the substrate. Removing the device must be done using plastic tweezers, because metal tweezers can damage the silicon. The surface of the substrate should be carefully cleaned and all solder and flux residues and/or underfill removed. When a new chip is placed on the substrate, use the flux process instead of solder on the solder lands. Apply flux on the bumps at the chip side as well as on the solder pads on the substrate. Place and align the new chip while viewing with a microscope. To reflow the solder, use the solder profile shown in application note *AN10365 "Surface mount reflow soldering description"*.

#### 15.3.4 Cleaning

Cleaning can be done after reflow soldering.

## 16. Abbreviations

| Table 16.            | Abbreviations                                  |

|----------------------|------------------------------------------------|

| Acronym              | Description                                    |

| ASIP                 | Application Specific Instruction-set Processor |

| DVD                  | Digital Versatile Disk                         |

| ESD                  | ElectroStatic Discharge                        |

| ESR                  | Equivalent Series Resistance                   |

| FB                   | FeedBack                                       |

| HP                   | HeadPhone                                      |

| I <sup>2</sup> C-bus | Inter-integrated Circuit bus                   |

| PC                   | Personal Computer                              |

| PCB                  | Printed-Circuit Board                          |

## 17. Revision history

| Table 17. Revision hist | ory          |                    |               |            |

|-------------------------|--------------|--------------------|---------------|------------|

| Document ID             | Release date | Data sheet status  | Change notice | Supersedes |

| SA58635_1               | 20100326     | Product data sheet | -             | -          |

## **18. Legal information**

### 18.1 Data sheet status

| Document status[1][2]          | Product status <sup>[3]</sup> | Definition                                                                            |

|--------------------------------|-------------------------------|---------------------------------------------------------------------------------------|

| Objective [short] data sheet   | Development                   | This document contains data from the objective specification for product development. |

| Preliminary [short] data sheet | Qualification                 | This document contains data from the preliminary specification.                       |

| Product [short] data sheet     | Production                    | This document contains the product specification.                                     |

[1] Please consult the most recently issued document before initiating or completing a design.

[2] The term 'short data sheet' is explained in section "Definitions".

[3] The product status of device(s) described in this document may have changed since this document was published and may differ in case of multiple devices. The latest product status information is available on the Internet at URL <a href="http://www.nxp.com">http://www.nxp.com</a>.

### **18.2 Definitions**

**Draft** — The document is a draft version only. The content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included herein and shall have no liability for the consequences of use of such information.

Short data sheet — A short data sheet is an extract from a full data sheet with the same product type number(s) and title. A short data sheet is intended for quick reference only and should not be relied upon to contain detailed and full information. For detailed and full information see the relevant full data sheet, which is available on request via the local NXP Semiconductors sales office. In case of any inconsistency or conflict with the short data sheet, the full data sheet shall prevail.

**Product specification** — The information and data provided in a Product data sheet shall define the specification of the product as agreed between NXP Semiconductors and its customer, unless NXP Semiconductors and customer have explicitly agreed otherwise in writing. In no event however, shall an agreement be valid in which the NXP Semiconductors product is deemed to offer functions and qualities beyond those described in the Product data sheet.

### 18.3 Disclaimers

Limited warranty and liability — Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information.

In no event shall NXP Semiconductors be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation - lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory.

Notwithstanding any damages that customer might incur for any reason whatsoever, NXP Semiconductors' aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the *Terms and conditions of commercial sale* of NXP Semiconductors.

Right to make changes — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

Suitability for use — NXP Semiconductors products are not designed, authorized or warranted to be suitable for use in medical, military, aircraft, space or life support equipment, nor in applications where failure or

malfunction of an NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental damage. NXP Semiconductors accepts no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

**Applications** — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

NXP Semiconductors does not accept any liability related to any default, damage, costs or problem which is based on a weakness or default in the customer application/use or the application/use of customer's third party customer(s) (hereinafter both referred to as "Application"). It is customer's sole responsibility to check whether the NXP Semiconductors product is suitable and fit for the Application planned. Customer has to do all necessary testing for the Application in order to avoid a default of the Application and the product. NXP Semiconductors does not accept any liability in this respect.

Limiting values — Stress above one or more limiting values (as defined in the Absolute Maximum Ratings System of IEC 60134) will cause permanent damage to the device. Limiting values are stress ratings only and (proper) operation of the device at these or any other conditions above those given in the Recommended operating conditions section (if present) or the Characteristics sections of this document is not warranted. Constant or repeated exposure to limiting values will permanently and irreversibly affect the quality and reliability of the device.

Terms and conditions of commercial sale — NXP Semiconductors products are sold subject to the general terms and conditions of commercial sale, as published at <a href="http://www.nxp.com/profile/terms">http://www.nxp.com/profile/terms</a>, unless otherwise agreed in a valid written individual agreement. In case an individual agreement is concluded only the terms and conditions of the respective agreement shall apply. NXP Semiconductors hereby expressly objects to applying the customer's general terms and conditions with regard to the purchase of NXP Semiconductors products by customer.

**No offer to sell or license** — Nothing in this document may be interpreted or construed as an offer to sell products that is open for acceptance or the grant, conveyance or implication of any license under any copyrights, patents or other industrial or intellectual property rights.

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from national authorities.

Non-automotive qualified products — Unless this data sheet expressly states that this specific NXP Semiconductors product is automotive qualified, the product is not suitable for automotive use. It is neither qualified nor tested in accordance with automotive testing or application requirements. NXP Semiconductors accepts no liability for inclusion and/or use of non-automotive qualified products in automotive equipment or applications.

In the event that customer uses the product for design-in and use in automotive applications to automotive specifications and standards, customer (a) shall use the product without NXP Semiconductors' warranty of the

SA58635\_1

Product data sheet

product for such automotive applications, use and specifications, and (b) whenever customer uses the product for automotive applications beyond NXP Semiconductors' specifications such use shall be solely at customer's own risk, and (c) customer fully indemnifies NXP Semiconductors for any liability, damages or failed product claims resulting from customer design and use of the product for automotive applications beyond NXP Semiconductors' standard warranty and NXP Semiconductors' product specifications.

## **19. Contact information**

For more information, please visit: http://www.nxp.com

For sales office addresses, please send an email to: salesaddresses@nxp.com

#### SA58635 1

18.4 Trademarks

Notice: All referenced brands, product names, service names and trademarks are the property of their respective owners.

I<sup>2</sup>C-bus — logo is a trademark of NXP B.V.

# SA58635

$2\times25$  mW class-G stereo headphone driver

## 20. Contents

| 1                          | General description 1                       |

|----------------------------|---------------------------------------------|

| 2                          | Features 1                                  |

| 3                          | Applications 2                              |

| 4                          | Ordering information 2                      |

| 5                          | Block diagram 2                             |

| 6                          | Pinning information 3                       |

| 6.1                        | Pinning                                     |

| 6.2                        | Pin description 3                           |

| 7                          | Functional description 4                    |

| 7.1                        | Device address 4                            |

| 7.2                        | Control register 4                          |

| 7.3                        | Register definitions                        |

| 7.3.1                      | MODE1 register, MODE1 5                     |

| 7.3.2                      | Volume control register, VOLCTL             |

| 7.3.3                      | High-impedance register, HIZ                |

| 7.3.4                      | Chip identification register, ID            |

| 7.3.5                      | Test register 1, TEST1                      |

| 7.4                        | Volume control                              |

| 7.5                        | Power-on reset                              |

| 8                          | Characteristics of the I <sup>2</sup> C-bus |

| 8.1                        | Bit transfer                                |

| 8.1.1                      | START and STOP conditions                   |

| 8.2<br>8.3                 | System configuration                        |

|                            | 5 5 5                                       |

| 9                          | Bus transactions 10                         |

| 10                         | Limiting values 11                          |

| 11                         | Static characteristics                      |

| 12                         | Dynamic characteristics 13                  |

| 13                         | Application information 21                  |

| 13.1                       | Power supply decoupling considerations 21   |

| 13.2                       | Input capacitor selection                   |

| 13.3                       | PCB layout considerations 23                |

| 13.4                       | Thermal information 23                      |

| 14                         | Package outline 24                          |

| 15                         | Soldering of WLCSP packages                 |

| 15.1                       | Introduction to soldering WLCSP packages 25 |

| 15.2                       | Board mounting 25                           |

| 15.3                       | Reflow soldering                            |

| 15.3.1                     | Stand off                                   |

|                            | Quality of colder joint                     |

| 15.3.2                     | Quality of solder joint                     |

| 15.3.2<br>15.3.3           | Rework                                      |

| 15.3.2<br>15.3.3<br>15.3.4 | Rework                                      |

| 15.3.2<br>15.3.3           | Rework                                      |

| 18   | Legal information   | 28 |

|------|---------------------|----|

| 18.1 | Data sheet status   | 28 |

| 18.2 | Definitions         | 28 |

| 18.3 | Disclaimers         | 28 |

| 18.4 | Trademarks          | 29 |

| 19   | Contact information | 29 |

| 20   | Contents            | 30 |

Please be aware that important notices concerning this document and the product(s) described herein, have been included in section 'Legal information'.

#### © NXP B.V. 2010.

All rights reserved.

For more information, please visit: http://www.nxp.com For sales office addresses, please send an email to: salesaddresses@nxp.com

Date of release: 26 March 2010 Document identifier: SA58635\_1