### INTEGRATED CIRCUITS

Product data Supersedes data of 2003 Nov 10 2004 May 11

Philips Semiconductors

### PCA9504A

#### FEATURES

- Dual, Strapping, Selectable Feature Sets

- Audio-disable Circuit

- Mute Audio Circuit

- 5 V reference generation

- 5 V standby reference generation

- HD single color LED driver

- IDE reset signal generation/PCIRST# buffers

- PWROK (PWRGD\_3V) signal generation

- Power Sequencing / BACKFEED\_CUT

- Power Supply turn on circuitry

- RMSRST# generation

- Voltage translation for DDC to VGA monitor

- HSYNCH / VSYNCH voltage translation to VGA monitor

- 3-state buffers for test

- Extra GP Logic gates

- Power LED Drivers

- Flash FLUSH# / INIT# circuit

- 5 V I<sup>2</sup>C to 3.3 V SMBus conversion to 400 kHz

- Requires both 3.3 V and 5.0 V operating voltages

- 0 to +70 °C operating temperature range

- ESD protection exceeds 1000 V HBM per JESD22-A114 and 750 V CDM per JESD22-C101

- Latch-up testing is done to JEDEC Standard JESD78 which exceeds 100 mA

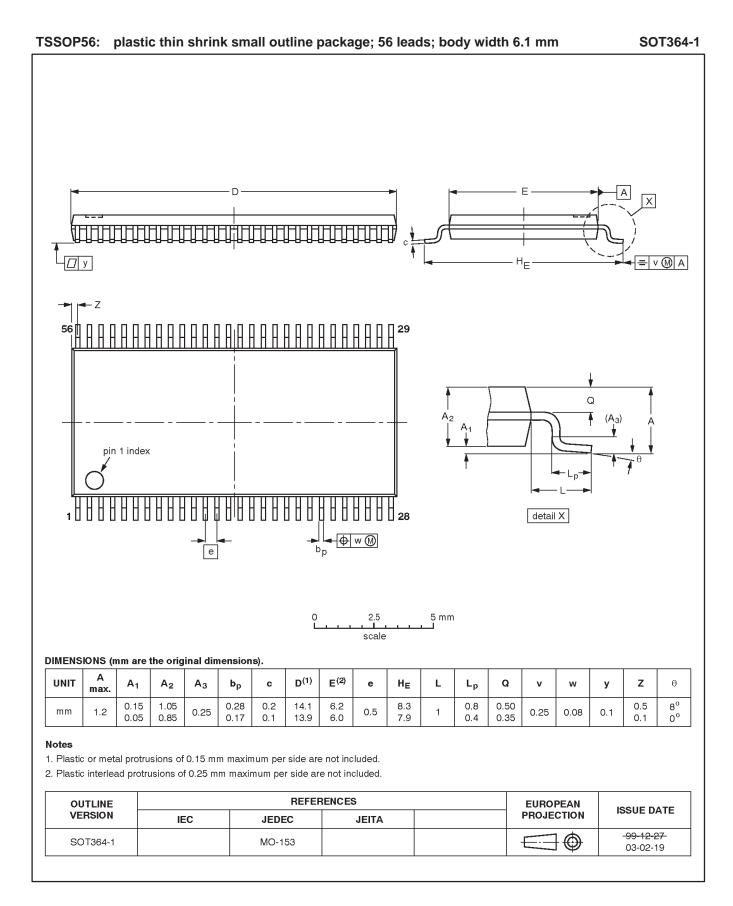

- Package offered: TSSOP56

#### DESCRIPTION

The PCA9504A Glue Chip 4 is a highly integrated and cost-efficient custom ASIC that reduces logic part count, overall component cost, and board space requirements for PC designers and manufacturers. The Glue Chip 4 supports the latest generation of high-volume

platforms based on Intel® processors and chipsets that require additional external circuitry in order to function properly. It is used on entry servers/workstations (840 and 860 chipsets), high-end desktops (820 and 850 chipsets), as well as mid range (815, 830 and 845 chipsets) and low-end (810 chipset) motherboards. Some of these functionalities include meeting timing specifications, buffering signals, and switching between power wells.

The PCA9504A Glue Chip 4 integrates miscellaneous motherboard logic and analog functions into a single, small footprint 56-pin TSSOP device. The Glue Chip 4 typically resides on the motherboard close to the I/O controller Hub (ICH) and is optimized for the Intel 82801BA I/O controller hub (ICH2).

### **PIN CONFIGURATION**

| VREF3IN                |    | 56 GP3_OUT             |

|------------------------|----|------------------------|

| V_5P0_STBY             | 2  | 55 GP3_IN              |

| V_3P3_STBY             | 3  | 54 STRAP               |

| GPO_FLUSH_CACHE/GP1_IN | 4  | 53 VCCP_VREF           |

| A20M/GP1_INB           | 5  | 52 VSYNC_5V            |

| INIT/GP1_INA           | 6  | 51 HSYNC_5V            |

| FLUSH_OUT_CPU/GP1_OUT  | 7  | 50 VSYNC_3V            |

| INIT_OUT/GP2_OUT       | 8  | 49 HSYNC_3V            |

| CLK_IN                 | 9  | 48 REF5V_STBY          |

| SEL_33_66              | 10 | 47 AUD_SHDN            |

| GND                    | 11 | 46 MUTE_AUD            |

| PCIRST                 | 12 | 45 VREF5IN             |

| PCRIST_OUT             | 13 | 44 REF5V               |

| AUD_EN                 | 14 | 43 GND                 |

| AUD_RST                | 15 | 42 RSMRST              |

| IDE_RSTDRV             | 16 | 41 TEST_EN             |

| 3V_DDCSCL              | 17 | 40 GRN_LED             |

| 5V_DDCSCL              | 18 | 39 YLW_LED             |

| 3V_DDCSDA              | 19 | 38 YLW_BLNK            |

| 5V_DDCSDA              | 20 | 37 GRN_BLNK            |

| CPU_PRESENT            | 21 | 36 SLP_S5              |

| SLP_S3                 | 22 | 35 SCK_BJT_GATE        |

| PS_ON                  | 23 | 34 PWRGD_3V            |

| HD_LED                 | 24 | 33 FPRST               |

| PRIMARY_HD             | 25 | 32 PWRGD_PS            |

| SCSI 🗄                 | 26 | 31 FLUSH_OUT_FWH       |

| SECONDARY_HD           | 27 | 30 LATCHED_BACKFED_CUT |

| BACKFEED_CUT           | 28 | 29 GND                 |

|                        | L  | SW00578                |

|                        |    |                        |

#### **ORDERING INFORMATION**

| PACKAGE              | TEMPERATURE RANGE | ORDER CODE  | TOPSIDE MARK | DRAWING NUMBER |

|----------------------|-------------------|-------------|--------------|----------------|

| 56-Pin Plastic TSSOP | 0 °C to +70 °C    | PCA9504ADGG | PCA9504ADGG  | SOT364-1       |

Standard packing quantities and other packaging data are available at www.philipslogic.com/packaging.

# PCA9504A

### **PIN DESCRIPTION**

| PIN(S)     |       | SYMBOL                   | FUNCTION                                                     |  |  |

|------------|-------|--------------------------|--------------------------------------------------------------|--|--|

| 1          | 31    | VREF3IN                  | 3.3 V input                                                  |  |  |

| 2          | Р     | V_5P0_STBY               | 5 V system standby power supply                              |  |  |

| 3          | Р     | V_3P3_STBY               | 3 V system standby power supply                              |  |  |

| 4          | 3IU   | GPO_FLUSH_CACHE / GP2_IN | GPO from SIO / ICH2 / Buffer 2 input                         |  |  |

| 5          | REF   | A20M / GP1_INB           | A20M signal from ICH2 / NAND 1 input B                       |  |  |

| 6          | REF   | INIT / GP1_INA           | INIT signal from the ICH2 / Buffer 1 input A                 |  |  |

| 7          | 5V OD | FLUSH_OUT_CPU / GP1_OUT  | Open drain signal, goes to the CPU / NAND 1 output           |  |  |

| 8          | 5V OD | <br>INIT_OUT / GP2_OUT   | Delayed INIT signal into the CPU / Buffer 2 output           |  |  |

| 9          | 31    | <br>CLK_IN               | Either 33MHz or 66MHz clock, based on SEL_33_66 pin          |  |  |

| 10         | 3IU   | <br>SEL_33_66            | Strapping option for 33MHz or 66MHz CLK_IN                   |  |  |

| 11, 29, 43 | G     | GND                      | Ground                                                       |  |  |

| 12         | 31    | PCRIST                   | PCI reset signal                                             |  |  |

| 13         | 30    | PCRIST_OUT               | Copy of PCRIST, increased drive-strength                     |  |  |

| 14         | 3IU   | AUD_EN                   | Audio enable input (GPO from ICH2 / SIO)                     |  |  |

| 15         | 30    | AUD_RST                  | Audio reset output                                           |  |  |

| 16         | 50    | IDE_RSTDRV               | IDE reset output, 5 V push/pull                              |  |  |

| 17         | 3IOD  | 3V_DDCSCL                | DDCSCL input/output 3.3 V side                               |  |  |

| 18         | 5IOD  | 5V_DDCSCL                | DDCSCL input/output 5 V side                                 |  |  |

| 19         | 3IOD  | 3V_DDCSDA                | DDCSDA input/output 3.3 V side                               |  |  |

| 20         | 5IOD  | 5V_DDCSDA                | DDCSDA input/output 5 V side                                 |  |  |

| 21         | 3IU   | CPU_PRESENT              | CPU present signal from the processor                        |  |  |

| 22         | 31    | SLP_S3                   | Signal from ICH2 for transitioning to the S3 power state     |  |  |

| 23         | 5V OD | PS_ON                    | Power supply turn-on signal                                  |  |  |

| 24         | 5V OD | HD_LED                   | Hard drive front panel LED output                            |  |  |

| 25         | 5IU   | PRIMARY_HD               | IDE primary drive active input                               |  |  |

| 26         | 5IU   | SCSI                     | SCSI drive active input                                      |  |  |

| 27         | 5IU   | SECONDARY_HD             | IDE secondary drive active input                             |  |  |

| 28         | 5V OD | BACKFEED_CUT             | Signal used for STR circuitry                                |  |  |

| 30         | 50    | LATCHED_BACKFEED_CUT     | Signal used for STR circuitry                                |  |  |

| 31         | 5V OD | FLUSH_OUT_FWH            | Open drain signal, goes to the FWH                           |  |  |

| 32         | 5IU   | PWRGD_PS                 | Power good signal from power supply                          |  |  |

| 33         | 5IU   | FPRST                    | Reset signal from the front panel                            |  |  |

| 34         | 30    | PWRGD_3V                 | 3.3 V power good output                                      |  |  |

| 35         | 5V OD | SCK_BJT_GATE             | Gate signal from the SCK BJT in suspend to RAM               |  |  |

| 36         | 31    | SLP_S5                   | Signal from the ICH2 for transitioning to the S5 power state |  |  |

| 37         | 3IU   | GRN_BLNK                 | Power LED input, from SIO GPIO                               |  |  |

| 38         | 3IU   | YLW_BLNK                 | Power LED input, from SIO GPIO                               |  |  |

| 39         | 5V OD | YLW_LED                  | Power LED output                                             |  |  |

| 40         | 5V OD | GRN_LED                  | Power LED output                                             |  |  |

| 41         | 5ID   | TEST_EN                  | Test enable, 100K internal pull-down to GND                  |  |  |

| 42         | 30    | RSMRST                   | Reset for the ICH2 resume well                               |  |  |

| 44         | AO    | REF5V                    | Highest system supply reference voltage                      |  |  |

| 45         | 51    | VREF5IN                  | 5V system primary supply input                               |  |  |

| 46         | 3IU   | MUTE_AUD                 | Signal from SIO to mute audio on power up/down               |  |  |

| 47         | 5O    | AUD_SHDN                 | Signal to audio amp to signal shutdown                       |  |  |

| 48         | AO    | REF5V_STBY               | Highest system standby voltage                               |  |  |

| 49         | 31    | HSYNC_3V                 | HSYNCH input from chipset video                              |  |  |

3

### PCA9504A

### **PIN DESCRIPTION CONTINUED**

|    | PIN(S) | SYMBOL                 | FUNCTION                                                                    |

|----|--------|------------------------|-----------------------------------------------------------------------------|

| 50 | 31     | VSYNC_3V               | VSYNCH input from chipset video                                             |

| 51 | 5O     | HSYNC_5V               | HSYNCH output to monitor                                                    |

| 52 | 5O     | VSYNC_5V               | VSYNCH output to monitor                                                    |

| 53 | AI     | V <sub>CCP</sub> _VREF | Analog voltage reference for determining INIT/A20M input thresholds         |

| 54 | 3IV/3O | STRAP                  | Strapping option for GP or FLUSH mode (internal pull-up resistor)<br>Note 1 |

| 55 | 51     | GP3_IN                 | Generic logic gate 3 input                                                  |

| 56 | 5V OD  | GP3_OUT                | Generic logic gate 3 output                                                 |

NOTE:

1. The pin is internally pulled up to default to FLUSH mode.

| TYPE  | DESCRIPTION                                               |

|-------|-----------------------------------------------------------|

| 31    | 3.3 V input signal                                        |

| 3IU   | 3.3 V input signal with internal pull-up                  |

| 51    | 5 V input signal                                          |

| 5IU   | 5 V input signal with internal pull-up                    |

| 5ID   | 5 V input signal with internal pull-down                  |

| Р     | Power (input)                                             |

| G     | Ground (input)                                            |

| 30    | 3.3 V output signal                                       |

| 5O    | 5 V output signal                                         |

| 3V OD | 3.3 V open-drain output signal                            |

| 5V OD | 5 v open-drain output signal                              |

| AO    | Analog output                                             |

| AI    | Analog input                                              |

| 3IOD  | 3.3 V input/output open-drain                             |

| 5IOD  | 5 V input/output open-drain                               |

| REFL  | Input voltage levels referenced to V <sub>CCP</sub> _VREF |

### **FUNCTION TABLES**

#### Strapping Selection Pin

| STRAP (pin 54) <sup>1</sup> | MODE <sup>1</sup> | PIN NAME & (PIN NUMBER) |

|-----------------------------|-------------------|-------------------------|

| 1 No connect                | FLUSH             | GPO_FLUSH_CACHE (4)     |

| 1 No connect                | FLUSH             | A20M (5)                |

| 1 No connect                | FLUSH             | INIT (6)                |

| 1 No connect                | FLUSH             | FLUSH_OUT_CPU (7)       |

| 1 No connect                | FLUSH             | INIT_OUT (8)            |

| 0 GND                       | GP                | GP2_IN (4)              |

| 0 GND                       | GP                | GP1_INB (5)             |

| 0 GND                       | GP                | GP1_INA (6)             |

| 0 GND                       | GP                | GP1_OUT (7)             |

| 0 GND                       | GP                | GP2_OUT (8)             |

**NOTE:** 1. The pin is internally pulled up to default to FLUSH mode.

Product data

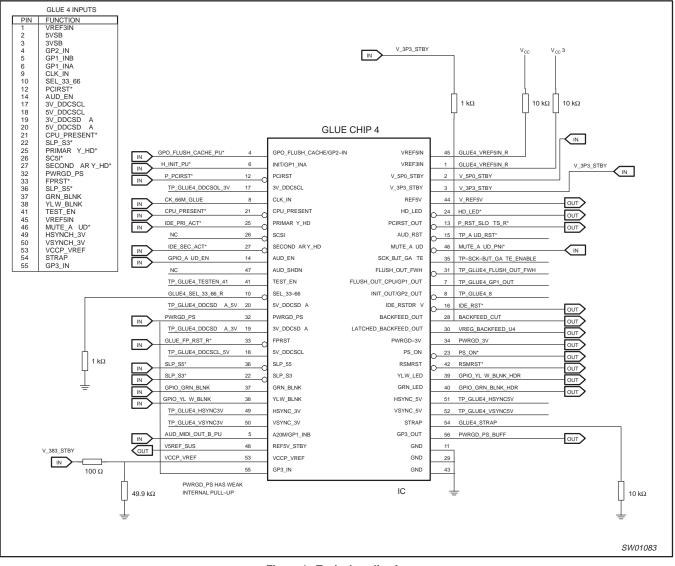

#### **TYPICAL APPLICATION**

Figure 1. Typical application

#### Product data

### PCA9504A

#### **ABSOLUTE MAXIMUM RATINGS<sup>1</sup>**

| SYMBOL                | PARAMETER                         | CONDITION |      | LIMITS         |      |  |

|-----------------------|-----------------------------------|-----------|------|----------------|------|--|

| STMBOL                |                                   | CONDITION | MIN  | MAX            | UNIT |  |

| V_5P0_STBY            | DC 5.0V supply                    |           | -0.5 | +6.0           | V    |  |

| V_3P3_STBY            | DC 3.3V supply                    |           | -0.5 | +6.0           | V    |  |

| V <sub>I (5V)</sub>   | DC input voltage (5 V pins)       | Note 2    | -0.5 | V_5P0_STBY+0.5 | V    |  |

| V <sub>O (5V)</sub>   | Output voltage range (5 V pins)   | Note 2    | -0.5 | V_5P0_STBY+0.5 | V    |  |

| V <sub>I (3.3V)</sub> | DC input voltage (3.3 V pins)     | Note 2    | -0.5 | V_3P3_STBY+0.5 | V    |  |

| V <sub>O (3.3V)</sub> | Output voltage range (3.3 V pins) | Note 2    | -0.5 | V_3P3_STBY+0.5 | V    |  |

| SPD                   | Supply power dissipation          |           |      | 100            | MW   |  |

| ESD                   | Static Discharge voltage          |           | 2000 |                | V    |  |

| T <sub>STG</sub>      | Storage temperature range         |           | -55  | +150           | °C   |  |

| T <sub>OTR</sub>      | Operating Temperature Range       |           | 0    | 70             | °C   |  |

NOTES:

Stresses beyond those listed may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other condition beyond those indicated under "recommended operating condition" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

2. The input and output voltage rating may be exceeded if the input and output current ratings are observed.

### **RECOMMENDED OPERATING CONDITIONS**

| SYMBOL           | PARAMETER                                       | CONDITIONS | LIMITS |                                      | UNIT |

|------------------|-------------------------------------------------|------------|--------|--------------------------------------|------|

|                  |                                                 | CONDITIONS | MIN    | MAX                                  |      |

| V <sub>DD3</sub> | DC 3.3 V supply voltage                         |            | 3.0    | 3.6                                  | V    |

| V <sub>DDL</sub> | DC 2.5 V supply voltage                         |            | 4.75   | 5.25                                 | V    |

| VI               | DC input voltage                                |            | 0      | V <sub>DD3</sub>                     | V    |

| Vo               | DC output voltage                               |            | 0      | V <sub>DDL</sub><br>V <sub>DD3</sub> | V    |

| T <sub>A</sub>   | Operating ambient temperature range in free air |            | 0      | +70                                  | °C   |

### PCA9504A

### **DC CHARACTERISTICS**

V\_5P0\_STBY = 5 V  $\pm$  5%; V\_3P3\_STBY = 3.3 V  $\pm$  10%

|                            |                           |                         |                    | LIMITS    |                   |      |

|----------------------------|---------------------------|-------------------------|--------------------|-----------|-------------------|------|

| SYMBOL                     | PARAMETER                 | TEST CONDITION          | T <sub>amb</sub> = | • 0 °C to | +70 °C            | UNIT |

|                            |                           |                         | MIN                | TYP       | MAX               |      |

| STRAP                      |                           |                         |                    |           |                   |      |

| V <sub>IH</sub>            | HIGH-level input voltage  |                         | 2.0                |           |                   | V    |

| V <sub>IL</sub>            | LOW-level input voltage   |                         |                    |           | 0.8               | V    |

| I <sub>IH</sub>            | Input leakage HIGH        |                         | -1                 |           | 1                 | μA   |

| V <sub>OL</sub>            | LOW-level output voltage  | I <sub>OL</sub> = 6 mA  |                    |           | 0.4               | V    |

| V <sub>OH</sub>            | HIGH-level output voltage | I <sub>OH</sub> = -3 mA | 2.4                |           |                   | V    |

| IIL                        | Input leakage LOW         |                         | -88                |           | -26               | μA   |

| AUD_EN                     |                           |                         |                    |           |                   |      |

| V <sub>IH</sub>            | HIGH-level input voltage  |                         | 2.0                |           |                   | V    |

| V <sub>IL</sub>            | LOW-level input voltage   |                         |                    |           | 0.8               | V    |

| IIL                        | Input leakage LOW         | V <sub>IL</sub> = 0 V   | -88                |           | -26               | μΑ   |

| IIH                        | Input leakage HIGH        |                         | -1                 |           | 1                 | μA   |

| PCIRST                     | •                         | •                       | •                  |           |                   |      |

| V <sub>IH</sub>            | HIGH-level input voltage  |                         | 2.2                |           |                   | V    |

| V <sub>IL</sub>            | LOW-level input voltage   |                         |                    |           | 0.8               | V    |

| IL                         | Input leakage             |                         | -1                 |           | 1                 | μA   |

| Hys                        | Input hysteresis          |                         | 400                |           |                   | mV   |

| MUTE_AUC                   | )                         | I                       | •                  |           |                   |      |

| V <sub>IH</sub>            | HIGH-level input voltage  |                         | 2.2                |           |                   | V    |

| V <sub>IL</sub>            | LOW-level input voltage   |                         |                    |           | 0.8               | V    |

| IIH                        | Input leakage HIGH        |                         | -1                 |           | 1                 | μA   |

| IIL                        | Input leakage LOW         | V <sub>IL</sub> = 0 V   | -88                |           | -26               | μA   |

| VREF5IN                    |                           | I                       | •                  |           | 1                 |      |

| V <sub>IH</sub>            | HIGH-level input voltage  |                         | 0.85*V5P<br>0_STBY |           |                   | V    |

| V <sub>IL</sub>            | LOW-level input voltage   |                         |                    |           | 0.2*V5P<br>0_STBY | V    |

| IL                         | Input leakage             |                         | -1                 |           | 1                 | μA   |

| VREF3IN                    | •                         | •                       | •                  | •         | •                 |      |

| V <sub>IH</sub>            | HIGH-level input voltage  |                         | 2.2                |           |                   | V    |

| V <sub>IL</sub>            | LOW-level input voltage   |                         |                    |           | 0.8               | V    |

| IL                         | Input leakage             |                         | -1                 |           | 1                 | μA   |

| PRIMARY_                   | HD                        | •                       | •                  |           |                   |      |

| V <sub>IH</sub>            | HIGH-level input voltage  |                         | 0.7*5VSB           |           |                   | V    |

| V <sub>IL</sub>            | LOW-level input voltage   |                         |                    |           | 0.2*5VSB          | V    |

| Hys                        | Input hysteresis          |                         | 400                |           |                   | mV   |

| IIL                        | Input leakage LOW         | V <sub>IL</sub> = 0 V   | -88                |           | -26               | μA   |

| <u></u><br>I <sub>IH</sub> | Input leakage HIGH        | V <sub>IH</sub> = 5VSB  | -1                 |           | 1                 | μΑ   |

| SECONDA                    |                           |                         |                    |           |                   |      |

| V <sub>IH</sub>            | HIGH-level input voltage  |                         | 0.7*5VSB           |           |                   | V    |

| V <sub>IL</sub>            | LOW-level input voltage   | 1                       | 1                  |           | 0.2*5VSB          | V    |

|                            |                           |                         |                    |           |                   |      |

| Hys                        | Input hysteresis          |                         | 400                |           |                   | mV   |

|                       |                          |                              |          | LIMITS                  |          |      |

|-----------------------|--------------------------|------------------------------|----------|-------------------------|----------|------|

| SYMBOL                | PARAMETER                | TEST CONDITION               | Tai      | <sub>mb</sub> = 0 °C to | +70 °C   | UNIT |

|                       |                          |                              | MIN      | TYP                     | MAX      |      |

| I <sub>IH</sub>       | Input leakage HIGH       | V <sub>IH</sub> = 5VSB       | -1       |                         | 1        | μA   |

| SCSI                  | •                        | •                            | •        |                         | •        |      |

| V <sub>IH</sub>       | HIGH-level input voltage |                              | 0.7*5VSB |                         |          | V    |

| V <sub>IL</sub>       | LOW-level input voltage  |                              |          |                         | 0.2*5VSB | V    |

| Hys                   | Input hysteresis         |                              | 400      |                         |          | mV   |

| IIL                   | Input leakage LOW        | V <sub>IL</sub> = 0 V        | -88      |                         | -26      | μA   |

| IIH                   | Input leakage HIGH       | V <sub>IH</sub> = 5VSB       | -1       |                         | 1        | μA   |

| FPRST                 | •                        | •                            | •        |                         | •        |      |

| V <sub>IH</sub>       | HIGH-level input voltage |                              | 0.7*5VSB |                         |          | V    |

| V <sub>IL</sub>       | LOW-level input voltage  |                              |          |                         | 0.2*5VSB | V    |

| Hys                   | Input hysteresis         |                              | 400      |                         |          | mV   |

| IIL                   | Input leakage LOW        | V <sub>IL</sub> = 0 V        | -88      |                         | -26      | μA   |

| IIH                   | Input leakage HIGH       | V <sub>IH</sub> = 5VSB       | -1       |                         | 1        | μA   |

| PWRGD_P               | S                        | •                            | •        |                         | •        |      |

| V <sub>IH</sub>       | HIGH-level input voltage |                              | 0.7*5VSB |                         |          | V    |

| V <sub>IL</sub>       | LOW-level input voltage  |                              |          |                         | 0.2*5VSB | V    |

| Hys                   | Input hysteresis         |                              | 400      |                         |          | mV   |

| IIL                   | Input leakage LOW        | V <sub>IL</sub> = 0 V        | -88      |                         | -26      | μA   |

| IIH                   | Input leakage HIGH       | V <sub>IH</sub> = 5VSB       | -1       |                         | 1        | μA   |

| GPO_FLUS              | H_CACHE/GP2_IN           |                              | •        |                         | •        | I    |

| V <sub>IH</sub>       | HIGH-level input voltage |                              | 2.2      |                         |          | V    |

| V <sub>IL</sub>       | LOW-level input voltage  |                              |          |                         | 0.8      | V    |

| ۱ <sub>L</sub>        | Input leakage            | V <sub>IL</sub> = 0 V        | -88      |                         | -26      | μΑ   |

| IIH                   | Input leakage            | V <sub>IH</sub> = 5 V        | -1       |                         | 1        | μA   |

| INIT / GP1_           | INA (GP Mode)            | •                            | •        |                         | •        | I    |

| V <sub>IH</sub>       | HIGH-level input voltage | Part is strapped for GP mode | 2.4      |                         |          | V    |

| V <sub>IL</sub>       | LOW-level input voltage  | Part is strapped for GP mode |          |                         | 0.8      | V    |

| ΙL                    | Input leakage            | Part is strapped for GP mode | -1       |                         | 1        | μΑ   |

| VCCP_V <sub>ref</sub> | Bias voltage             | GP mode                      | 1.95     |                         | 2.1      | V    |

| INIT / GP1_           | INA (Flush Mode)         |                              | •        |                         |          |      |

| V <sub>IH</sub>       | HIGH-level input voltage | FLUSH mode                   | 1.5      |                         |          | V    |

| V <sub>IL</sub>       | LOW-level input voltage  | FLUSH mode                   |          |                         | 0.4      | V    |

| IIL                   | Input leakage            | FLUSH mode                   | -1       |                         | 1        | μA   |

| VCCP_V <sub>ref</sub> | Bias voltage             | FLUSH mode                   | 0.95     |                         | 1.1      | V    |

# PCA9504A

|                       |                          |                        |                                   | LIMITS         |          |    |

|-----------------------|--------------------------|------------------------|-----------------------------------|----------------|----------|----|

| SYMBOL                | PARAMETER                | TEST CONDITION         | T <sub>amb</sub> = 0 °C to +70 °C |                |          |    |

|                       |                          |                        | MIN                               | TYP            | MAX      |    |

| A20M / GP1            |                          |                        |                                   |                |          |    |

| V <sub>IH</sub>       | HIGH-level input voltage | FLUSH mode             | 1.5                               |                |          | V  |

| V <sub>IL</sub>       | LOW-level input voltage  | FLUSH mode             |                                   |                | 0.4      | V  |

| IIL                   | Input leakage            | FLUSH mode             | -1                                |                | 1        | μΑ |

| VCCP_V <sub>ref</sub> | Bias voltage             | FLUSH mode             | 0.95                              |                | 1.1      | V  |

| V <sub>IH</sub>       | HIGH-level input voltage | GP mode                | 2.4                               |                |          | V  |

| V <sub>IL</sub>       | LOW-level input voltage  | GP mode                |                                   |                | 0.8      | V  |

| L                     | Input leakage            | GP mode                | -1                                |                | 1        | μΑ |

| VCCP_V <sub>ref</sub> | Bias voltage             | GP mode                | 1.95                              |                | 2.1      | V  |

| CLK_IN                |                          |                        |                                   |                |          |    |

| V <sub>IH</sub>       | HIGH-level input voltage |                        | 2.2                               |                |          | V  |

| V <sub>IL</sub>       | LOW-level input voltage  |                        |                                   |                | 0.8      | V  |

| Hys                   | Input hysteresis         |                        | 250                               |                |          | mV |

| IL                    | Input leakage            |                        | -1                                |                | 1        | μA |

| SEL_33_66             | -                        |                        | -                                 |                |          |    |

| V <sub>IH</sub>       | HIGH-level input voltage |                        | 2.0                               |                |          | V  |

| VIL                   | LOW-level input voltage  |                        |                                   |                | 0.8      | V  |

| Hys                   | Input hysteresis         |                        | 400                               |                |          | mV |

| н                     | Input leakage            |                        | -1                                |                | 1        | μA |

| IL                    | Input leakage            | V <sub>IL</sub> = 0 V  | -88                               |                | -26      | μA |

| SLP_S3                | •                        | •                      |                                   | I              | •        |    |

| V <sub>IH</sub>       | HIGH-level input voltage |                        | 2.2                               |                |          | V  |

| V <sub>IL</sub>       | LOW-level input voltage  |                        |                                   |                | 0.8      | V  |

| Hys                   | Input hysteresis         |                        | 400                               |                |          | mV |

|                       | Input leakage            |                        | -1                                |                | 1        | μA |

| SLP_S5                |                          |                        |                                   |                |          |    |

| V <sub>IH</sub>       | HIGH-level input voltage |                        | 2.2                               |                |          | V  |

| V <sub>IL</sub>       | LOW-level input voltage  |                        |                                   |                | 0.8      | V  |

| Hys                   | Input hysteresis         |                        | 400                               |                |          | mV |

| <br>                  | Input leakage            |                        | -1                                |                | 1        | μA |

| _<br>CPU_PRES         | •                        |                        |                                   |                |          |    |

| V <sub>IH</sub>       | HIGH-level input voltage |                        | 2.0                               |                |          | V  |

| V <sub>IL</sub>       | LOW-level input voltage  |                        |                                   |                | 0.8      | V  |

| Hys                   | Input hysteresis         |                        | 400                               |                |          | mV |

| Ін                    | Input leakage            | V <sub>IH</sub> = 3VSB | -1                                |                | 1        | μA |

|                       | Input leakage            | $V_{IL} = 0 V$         | -88                               |                | -26      | μA |

| TEST_EN               |                          | 1 <sup>16</sup>        | 1                                 |                | 1        | C  |

| V <sub>IH</sub>       | HIGH-level input voltage |                        | 0.7*5VSB                          |                | 1        | V  |

| V <sub>IL</sub>       | LOW-level input voltage  |                        |                                   |                | 0.2*5VSB | V  |

| Hys                   | Input hysteresis         |                        | 400                               |                |          | mV |

| н                     | Input leakage            | V <sub>IL</sub> = 0 V  | -1                                | <del>-  </del> | 1        | μΑ |

|                       | Input leakage            | V <sub>IH</sub> = 5VSB | 20                                |                | 88       | μΑ |

Philips Semiconductors

# PCA9504A

|                   |                           |                             | LIMITS                            |     |                            |    |

|-------------------|---------------------------|-----------------------------|-----------------------------------|-----|----------------------------|----|

| SYMBOL            | PARAMETER                 | TEST CONDITION              | T <sub>amb</sub> = 0 °C to +70 °C |     |                            |    |

|                   |                           |                             | MIN                               | TYP | MAX                        |    |

| HSYNC_3V          |                           |                             |                                   |     |                            |    |

| V <sub>IH</sub>   | HIGH-level input voltage  |                             | 2.2                               |     |                            | V  |

| V <sub>IL</sub>   | LOW-level input voltage   |                             |                                   |     | 0.8                        | V  |

| IL                | Input leakage             |                             | -1                                |     | 1                          | μΑ |

| VSYNC_3V          | -                         |                             |                                   |     | -                          |    |

| V <sub>IH</sub>   | HIGH-level input voltage  |                             | 2.2                               |     |                            | V  |

| V <sub>IL</sub>   | LOW-level input voltage   |                             |                                   |     | 0.8                        | V  |

| IL                | Input leakage             |                             | -1                                |     | 1                          | μΑ |

| GRN_BLNK          | <u>[</u>                  |                             |                                   |     |                            |    |

| V <sub>IH</sub>   | HIGH-level input voltage  |                             | 2.2                               |     |                            | V  |

| V <sub>IL</sub>   | LOW-level input voltage   |                             |                                   |     | 0.8                        | V  |

| Ін                | Input leakage             |                             | -1                                |     | 1                          | μA |

| IIL               | Input leakage             | $V_{IL} = 0 V$              | -88                               |     | -26                        | μΑ |

| YLW_BLNK          |                           |                             |                                   |     |                            |    |

| V <sub>IH</sub>   | HIGH-level input voltage  |                             | 2.0                               |     |                            | V  |

| V <sub>IL</sub>   | LOW-level input voltage   |                             |                                   |     | 0.8                        | V  |

| Ін                | Input leakage             |                             | -1                                |     | 1                          | μΑ |

| IIL               | Input leakage             | $V_{IL} = 0 V$              | -88                               |     | -26                        | μΑ |

| GP3_IN            |                           | •                           | •                                 |     | •                          | -  |

| V <sub>IH</sub>   | HIGH-level input voltage  |                             | 2.2                               |     |                            | V  |

| V <sub>IL</sub>   | LOW-level input voltage   |                             |                                   |     | 0.8                        | V  |

| IL                | Input leakage             |                             | -1                                |     | 1                          | μA |

| AUD_RST           | •                         | •                           | •                                 |     | •                          |    |

| V <sub>OL</sub>   | LOW-level output voltage  | I <sub>OL</sub> = 6 mA      |                                   |     | 0.4                        | V  |

| V <sub>OH</sub>   | HIGH-level output voltage | I <sub>OH</sub> = -3 mA     | 2.4                               |     |                            | V  |

| I <sub>OZ</sub>   | Off state output current  |                             | -1                                |     | 1                          | μA |

| AUD_SHDN          | I                         | •                           | •                                 |     |                            |    |

| V <sub>OL</sub>   | LOW-level output voltage  | I <sub>OL</sub> = 6 mA      |                                   |     | 0.4                        | V  |

| V <sub>OH</sub>   | HIGH-level output voltage | I <sub>OH</sub> =6 mA       | 2.4                               |     |                            | V  |

| I <sub>OZ</sub>   | Off state output current  |                             | -1                                |     | 1                          | μA |

| REF5V             | •                         |                             |                                   |     | •                          |    |

| V <sub>OUT5</sub> | LOW-level output voltage  | V <sub>REF5in</sub> > 1.5 V | V <sub>REF5in</sub> – 0.05        |     | V <sub>REF5in</sub> + 0.05 | V  |

| V <sub>OUT3</sub> | HIGH-level output voltage | V <sub>REF3in</sub> > 1.5 V | V <sub>REF3in</sub> – 0.05        |     | V <sub>REF3in</sub> + 0.05 | V  |

| IOUTL             | Off state output current  |                             | -20                               |     | 20                         | μA |

| REF5V_STI         | BY                        | •                           |                                   |     |                            |    |

| V <sub>OUT5</sub> | LOW-level output voltage  | V_5P0_STBY > 1.5 V          | V_5P0_STBY - 0.05                 |     | V_5P0_STBY + 0.05          | V  |

| V <sub>OUT3</sub> | HIGH-level output voltage | V_5P0_STBY > 1.5 V          | V_5P0_STBY - 0.05                 |     | V_5P0_STBY + 0.05          | V  |

| IOUTL             | Off state output current  |                             | -20                               |     | 20                         | μA |

| HD_LED            |                           |                             |                                   |     | •                          |    |

| V <sub>OL</sub>   | LOW-level output voltage  | I <sub>OL</sub> = 12 mA     |                                   |     | 0.4                        | V  |

| I <sub>OZ</sub>   | Off state output current  |                             | -1                                |     | 1                          | μA |

| <u></u>           |                           | I                           | 1                                 |     |                            |    |

Downloaded from Arrow.com.

2004 May 11

# Glue chip 4

Philips Semiconductors

| P | C | A | 95 | 0 | 44 | ł |

|---|---|---|----|---|----|---|

|   |   |   |    |   | ., | • |

|                 |                           |                         |                                   | LIMITS |     |    |

|-----------------|---------------------------|-------------------------|-----------------------------------|--------|-----|----|

| SYMBOL          | PARAMETER                 | TEST CONDITION          | T <sub>amb</sub> = 0 °C to +70 °C |        |     |    |

|                 |                           |                         | MIN                               | TYP    | MAX |    |

| IDE_RSTDF       | RV                        |                         | -                                 |        | -   |    |

| V <sub>OL</sub> | LOW-level output voltage  | I <sub>OL</sub> = 6 mA  |                                   |        | 0.4 | V  |

| V <sub>OH</sub> | HIGH-level output voltage | I <sub>OH</sub> =6 mA   | 2.4                               |        |     | V  |

| I <sub>OZ</sub> | Off state output current  |                         | -1                                |        | 1   | μA |

| PCIRST_O        | JT                        |                         | •                                 |        | •   |    |

| V <sub>OL</sub> | LOW-level output voltage  | I <sub>OL</sub> = 6 mA  |                                   |        | 0.4 | V  |

| V <sub>OH</sub> | HIGH-level output voltage | I <sub>OH</sub> = -3 mA | 2.4                               |        |     | V  |

| I <sub>OZ</sub> | Off state output current  |                         | -1                                |        | 1   | μA |

| PRWGD_3         | l I                       |                         |                                   |        | -   |    |

| V <sub>OL</sub> | LOW-level output voltage  | I <sub>OL</sub> = 6 mA  |                                   |        | 0.4 | V  |

| V <sub>OH</sub> | HIGH-level output voltage | I <sub>OH</sub> = –3 mA | 2.4                               |        |     | V  |

| I <sub>OZ</sub> | Off state output current  |                         | -1                                |        | 1   | μA |

| INIT_OUT /      | GP2_OUT                   |                         | •                                 |        | •   |    |

| V <sub>OL</sub> | LOW-level output voltage  | I <sub>OL</sub> = 12 mA |                                   |        | 0.4 | V  |

| I <sub>OZ</sub> | Off state output current  |                         | -1                                |        | 1   | μA |

| FLUSH_OU        | T_CPU / GP1_OUT           | •                       | •                                 |        | •   | •  |

| V <sub>OL</sub> | LOW-level output voltage  | I <sub>OL</sub> = 12 mA |                                   |        | 0.4 | V  |

| I <sub>OZ</sub> | Off state output current  |                         | -1                                |        | 1   | μA |

| BACKFEED        | D_CUT                     |                         | •                                 |        |     |    |

| V <sub>OL</sub> | LOW-level output voltage  | I <sub>OL</sub> = 6 mA  |                                   |        | 0.4 | V  |

| I <sub>OZ</sub> | Off state output current  |                         | -1                                |        | 1   | μA |

| FLUSH_OU        | T_FWH                     | •                       | •                                 |        | •   |    |

| V <sub>OL</sub> | LOW-level output voltage  | I <sub>OL</sub> = 6 mA  |                                   |        | 0.4 | V  |

| I <sub>OZ</sub> | Off state output current  |                         | -1                                |        | 1   | μA |

| LATCHED_        | BACKFEED_CUT              |                         |                                   |        |     |    |

| V <sub>OL</sub> | LOW-level output voltage  | I <sub>OL</sub> = 6 mA  |                                   |        | 0.4 | V  |

| V <sub>OH</sub> | HIGH-level output voltage | I <sub>OH</sub> =6 mA   | 2.4                               |        |     | V  |

| I <sub>OZ</sub> | Off state output current  |                         | -1                                |        | 1   | μA |

| PS_ON           | •                         | •                       | •                                 |        | •   |    |

| V <sub>OL</sub> | LOW-level output voltage  | I <sub>OL</sub> = 6 mA  |                                   |        | 0.4 | V  |

| I <sub>OZ</sub> | Off state output current  |                         | -1                                |        | 1   | μA |

| RSMRST          | •                         |                         | •                                 |        |     |    |

| V <sub>OL</sub> | LOW-level output voltage  | I <sub>OL</sub> = 6 mA  |                                   |        | 0.4 | V  |

| V <sub>OH</sub> | HIGH-level output voltage | I <sub>OH</sub> = -3 mA | 2.4                               |        |     | V  |

| I <sub>OZ</sub> | Off state output current  |                         | -1                                |        | 1   | μA |

| VTRIP           | 5VSB LOW trip voltage     |                         | 1.8                               |        | 3.5 | V  |

| SCK_BJT_        | GATE                      | •                       |                                   | -      |     | •  |

| V <sub>OL</sub> | LOW-level output voltage  | I <sub>OL</sub> = 6 mA  |                                   |        | 0.4 | V  |

| I <sub>OZ</sub> | Off state output current  |                         | -1                                |        | 1   | μA |

# PCA9504A

|                 |                           | TEST CONDITION              |                                   | UNIT |     |    |

|-----------------|---------------------------|-----------------------------|-----------------------------------|------|-----|----|

| SYMBOL          | PARAMETER                 |                             | T <sub>amb</sub> = 0 °C to +70 °C |      |     |    |

|                 |                           |                             | MIN                               | TYP  | MAX |    |

| 3V_DDCSD        | A                         |                             | -                                 |      | -   |    |

| V <sub>OL</sub> | LOW-level output voltage  | I <sub>OL</sub> = 6 mA      |                                   |      | 0.4 | V  |

| I <sub>H</sub>  | Input leakage             | $5V_DDCSDA = V_{DD}$        | -1                                |      | 2.5 | μA |

| I <sub>OZ</sub> | Off state output current  |                             | -1                                |      | 1   | μA |

| 5V_DDCSD        | A                         |                             | -                                 |      | -   |    |

| V <sub>OL</sub> | LOW-level output voltage  | I <sub>OL</sub> = 6 mA      |                                   |      | 0.4 | V  |

| Ι <sub>Η</sub>  | Input leakage             | 3V_DDCSDA = V <sub>DD</sub> | -1                                |      | 2.5 | μA |

| I <sub>OZ</sub> | Off state output current  |                             | -1                                |      | 1   | μA |

| 3V_DDCSC        | L                         |                             | -                                 |      | -   |    |

| V <sub>OL</sub> | LOW-level output voltage  | I <sub>OL</sub> = 6 mA      |                                   |      | 0.4 | V  |

| I <sub>H</sub>  | Input leakage             | 5V_DDCSCL = V <sub>DD</sub> | -1                                |      | 2.5 | μA |

| I <sub>OZ</sub> | Off state output current  |                             | -1                                |      | 1   | μA |

| 5V_DDCSC        | L                         |                             | •                                 |      | •   |    |

| V <sub>OL</sub> | LOW-level output voltage  | I <sub>OL</sub> = 6 mA      |                                   |      | 0.4 | V  |

| Ι <sub>Η</sub>  | Input leakage             | 3V_DDCSCL = V <sub>DD</sub> | -1                                |      | 2.5 | μA |

| I <sub>OZ</sub> | Off state output current  |                             | -1                                |      | 1   | μA |

| HSYNC_5V        |                           |                             | -                                 |      | -   |    |

| V <sub>OL</sub> | LOW-level output voltage  | I <sub>OL</sub> = 6 mA      |                                   |      | 0.4 | V  |

| V <sub>OH</sub> | HIGH-level output voltage | I <sub>OH</sub> =6 mA       | 3.8                               |      |     | V  |

| I <sub>OZ</sub> | Off state output current  |                             | -1                                |      | 1   | μA |

| VSYNC_5V        |                           |                             | -                                 |      | -   |    |

| V <sub>OL</sub> | LOW-level output voltage  | I <sub>OL</sub> = 6 mA      |                                   |      | 0.4 | V  |

| V <sub>OH</sub> | HIGH-level output voltage | I <sub>OH</sub> =6 mA       | 3.8                               |      |     | V  |

| I <sub>OZ</sub> | Off state output current  |                             | -1                                |      | 1   | μA |

| GRN_LED         | YLW_LED                   |                             | •                                 |      | •   |    |

| V <sub>OL</sub> | LOW-level output voltage  | I <sub>OL</sub> = 24 mA     |                                   |      | 0.4 | V  |

| I <sub>OZ</sub> | Off state output current  |                             | -1                                |      | 1   | μA |

| GP3_OUT         |                           |                             |                                   |      |     |    |

| V <sub>OL</sub> | LOW-level output voltage  | I <sub>OL</sub> = 6 mA      |                                   |      |     |    |

| I <sub>OZ</sub> | Off state output current  |                             | -1                                |      | 1   | μA |

# PCA9504A

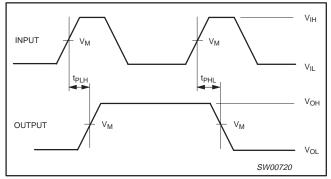

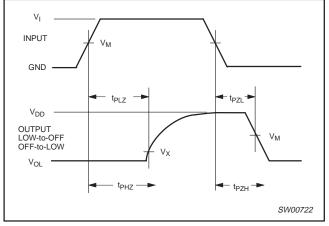

### AC CHARACTERISTICS

$V_{CC1} = 3.3 \text{ V}; V_{CC} = 5.0 \text{ V}$

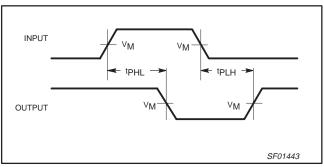

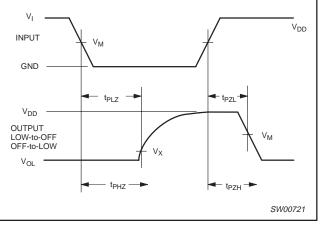

| SYMBOL                             | PARAMETER                                                                                                     | T <sub>amb</sub> | UNITS | NOTES |    |  |

|------------------------------------|---------------------------------------------------------------------------------------------------------------|------------------|-------|-------|----|--|

|                                    |                                                                                                               | MIN              | TYP   | MAX   |    |  |

| t <sub>RESET</sub>                 | RSMRST                                                                                                        | 4.0              |       | 100   | ms |  |

| tRESET_FALL                        | RSMRST                                                                                                        |                  |       | 100   | ns |  |

| t <sub>PHL</sub> ∕t <sub>PLH</sub> | Propagation Delay<br>AUD_EN to AUD_RST<br>PCIRST to AUD_RST<br>PCIRST to IDE_RSTDRV<br>PCIRST to PCIRST_OUT   | 1.0              |       | 11.0  | ns |  |

| t <sub>PLH</sub> /t <sub>PHL</sub> | Propagation Delay<br>MUTE_AUD to MUTE_SHDN                                                                    | 2.5              |       | 6.0   | ns |  |

| t <sub>PLH</sub> /t <sub>PHL</sub> | Propagation Delay<br>PWRGD_PS to PWRGD_3V<br>FPRST to PWRGD_3V                                                | 4.5              |       | 11.0  | ns |  |

| t <sub>PLH</sub> /t <sub>PHL</sub> | Propagation Delay<br>HSYNC_3V to HSYNC_5V<br>VSYNC_3V to VSYNC_5V                                             | 2.0              |       | 5.0   | ns |  |

| t <sub>PLH</sub> /t <sub>PHL</sub> | Propagation Delay<br>PWRGD_PS to SCK_BJT_GATE<br>FPRST to SCK_BJT_GATE                                        | 1.0              |       | 6.0   | ns |  |

| t <sub>PLZ</sub> /t <sub>PZL</sub> | Open Drain Prop Delay<br>PRIMARY_HD to HD_LED<br>PRIMARY_HD to HD_LED<br>PRIMARY_HD to HD_LED                 | 1.0              |       | 5.0   | ns |  |

| t <sub>PLZ</sub> /t <sub>PZL</sub> | Open Drain Prop Delay<br>GP1_INA to GP1_OUT 3<br>GP2_INA to GP1_OUT                                           |                  |       | 25.0  | ns |  |

| t <sub>PLZ</sub> /t <sub>PZL</sub> | Open Drain Prop Delay<br>GP2_IN to GP2_OUT                                                                    | 3.0              |       | 7.0   | ns |  |

| t <sub>PLZ</sub> /t <sub>PZL</sub> | Open Drain Prop Delay<br>GP3_IN to GP3_OUT                                                                    | 1.0              |       | 4.0   | ns |  |

| t <sub>PLZ</sub> /t <sub>PZL</sub> | Open Drain Prop Delay<br>SLP_S3 to BACKFEED_OUT<br>PRWGD_PS to BACKFEED_OUT                                   | 1.0              |       | 6.0   | ns |  |

| t <sub>PLZ</sub> /t <sub>PZL</sub> | Open Drain Prop Delay<br>CPU_PRESENT to PS_ON                                                                 | 2.0              |       | 10.0  | ns |  |

| t <sub>PLZ</sub> /t <sub>PZL</sub> | Open Drain Prop Delay<br>SLP_S3 to PS_ON                                                                      | 2.0              |       | 10.0  | ns |  |

| t <sub>PLZ</sub> /t <sub>PZL</sub> | Open Drain Prop Delay<br>BACKFEED_OUT to<br>LATCHED_BACKFEED_OUT                                              | 2.0              |       | 11.0  | ns |  |

| tpLZ/tpZL                          | Open Drain Prop Delay<br>SLP_S5 to YLW_LED<br>SLP_S5 to GRN_LED<br>YLW_BLNK to YLW_LED<br>GRN_BLNK to GRN_LED |                  |       | 5.0   | ns |  |

| t <sub>PLZ</sub> /t <sub>PZL</sub> | Open Drain Prop Delay<br>3V_DDOSDA to 5V_DDOSDA<br>3V_DDOSDA to 5V_DDOSDA                                     | 1.0              |       | 5.0   | ns |  |

| t <sub>r</sub> , t <sub>f</sub>    | Rise and Fall Times<br>HSYNC_5V<br>VSYNC_5V                                                                   | 3.5              |       |       | ns |  |

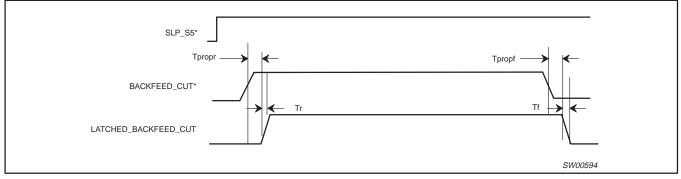

| t <sub>r</sub> , t <sub>f</sub>    | Rise and Fall Times<br>LATCHED_BACKFEED_OUT                                                                   |                  |       | 1.0   | μs |  |

### PCA9504A

WAVEFORMS

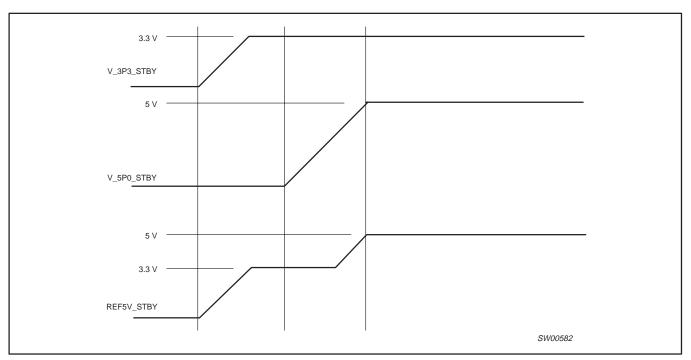

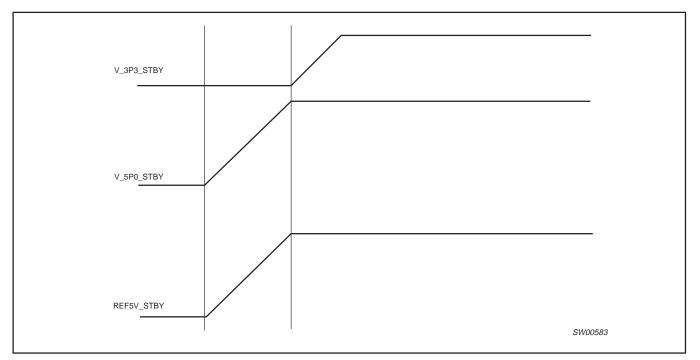

Waveform 2.

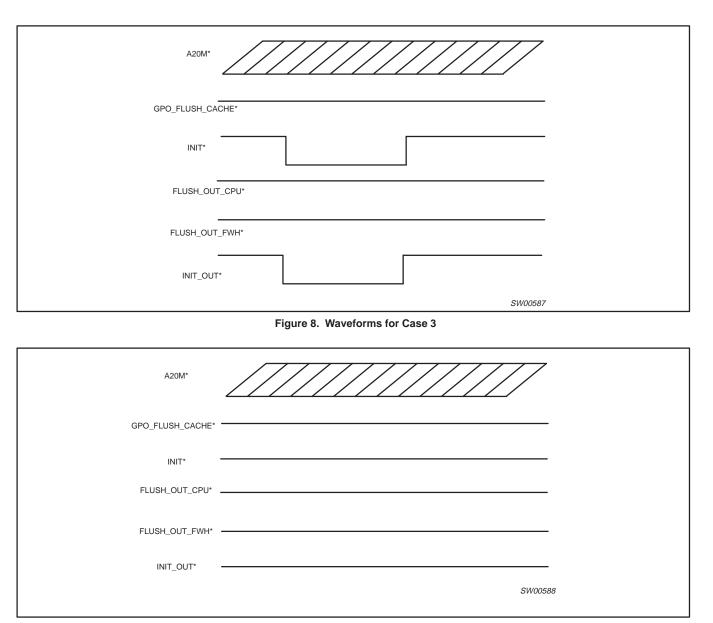

Waveform 3.

Waveform 4.

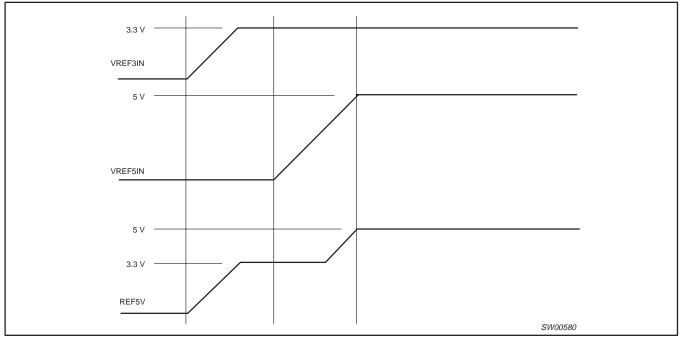

### **5V REFERENCE GENERATION**

| Supply            | REF5V   |

|-------------------|---------|

| VREF5IN < VREF3IN | VREF3IN |

| VREF5IN > VREF3IN | VREF5IN |

Figure 1. REF5V when VREF3IN ramps before VREF5IN

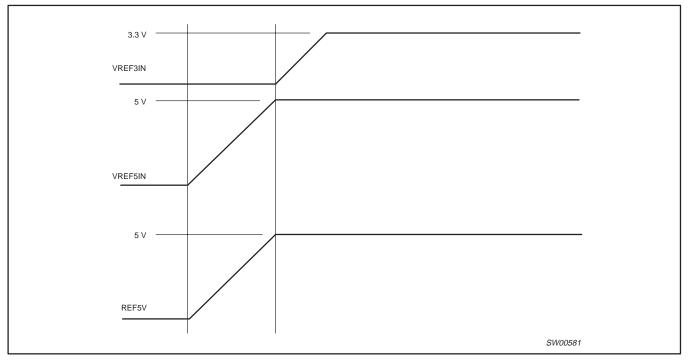

Figure 2. REF5V when VREF5IN ramps before VREF3IN

### **5V STANDBY REFERENCE GENERATION**

| Standby Supply          | REF5V_STBY |

|-------------------------|------------|

| V_5PO_STBY < V_3P3_STBY | V_3P3_STBY |

| V_5PO_STBY > V_3P3_STBY | V_5PO_STBY |

Figure 3. REF5V\_STBY when V\_3P3\_STBY ramps before V\_5PO\_STBY

Figure 4. REF5V\_STBY when V\_5PO\_STBY ramps before V\_3P3\_STBY

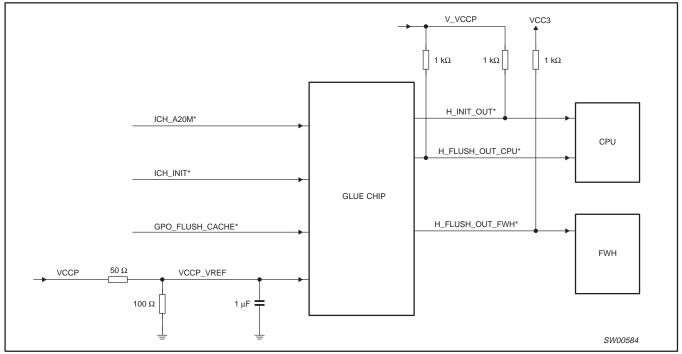

### FLUSH OUT\* / INIT OUT\* CIRCUIT

Figure 5. Block diagram for FLUSH\_OUT\*/INIT\_OUT\* circuit

| Case | A20M* | GPO FLUSH<br>CACHE* | INIT* | FLUSH OUT<br>CPU* | FLUSH OUT<br>FWH* | INIT OUT*                                              |

|------|-------|---------------------|-------|-------------------|-------------------|--------------------------------------------------------|

| 1    | 1     | falling edge        | 0     | 0 (for t1)        | 0 (for t1)        | 0, Hi-Z, then 0 (delayed by t1-t, then active for 2*t) |

| 2    | 1     | falling edge        | 1     | 0 (for t1)        | 0 (for t1)        | Hi-Z, 0 (delayed by t1-t, then active for 2*t)         |

| 3    | Х     | 1                   | 0     | Hi-Z              | Hi-Z              | 0                                                      |

| 4    | Х     | 1                   | 1     | Hi-Z              | Hi-Z              | Hi-Z                                                   |

| 5    | 0     | falling edge        | 1     | Hi-Z              | Hi-Z              | Hi-Z                                                   |

| 6    | 0     | falling edge        | 0     | Hi-Z              | Hi-Z              | 0                                                      |

#### NOTE:

1. Nominal value timings with tolerances are listed in the DC Characteristics table for t and t1. All Hi-Z outputs are shown as 1's or HIGH in the following diagrams.

# PCA9504A

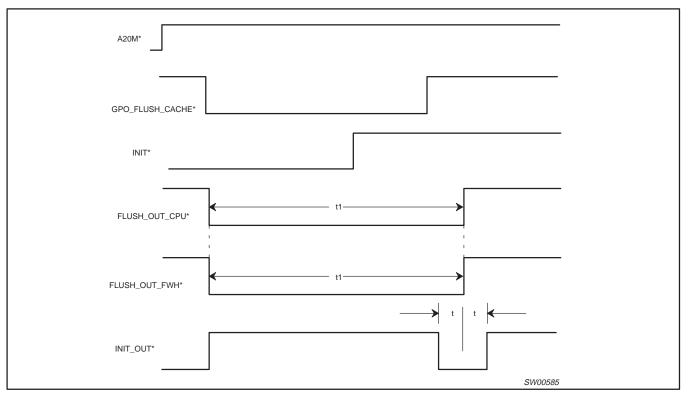

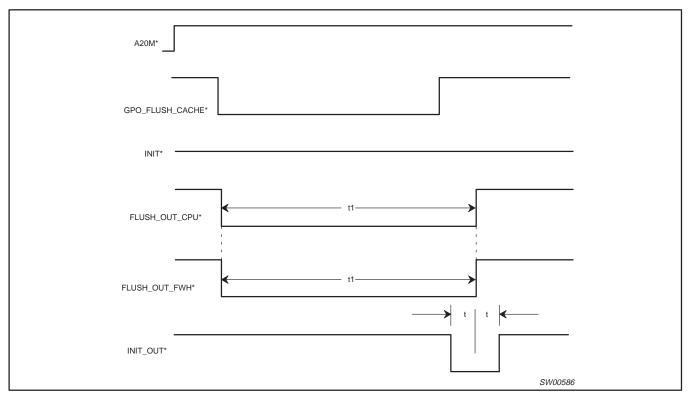

#### Figure 6. Waveforms for Case 1

Figure 7. Waveforms for Case 2

### PCA9504A

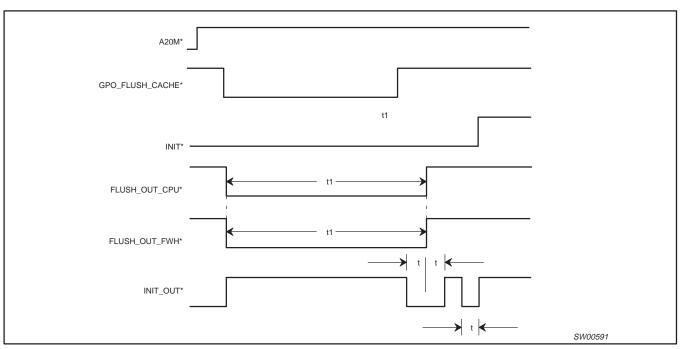

Figure 9. Waveforms for Case 4

# PCA9504A

| A20M*            |         |  |

|------------------|---------|--|

| GPO_FLUSH_CACHE* |         |  |

| INIT*            |         |  |

| FLUSH_OUT_CPU*   |         |  |

| FLUSH_OUT_FWH*   |         |  |

| INIT_OUT*        |         |  |

|                  | SW00589 |  |

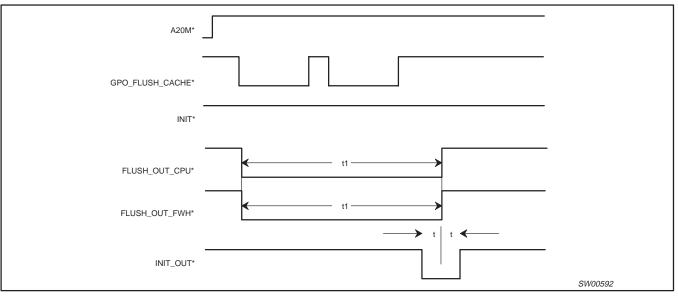

#### Figure 10. Waveforms for Case 5

| A20M*            |         |

|------------------|---------|

| GPO_FLUSH_CACHE* |         |

| INIT*            |         |

| FLUSH_OUT_CPU*   | <br>    |

| FLUSH_OUT_FWH*   | <br>    |

| INIT_OUT*        | <br>    |

|                  | SW00590 |

#### Figure 11. Waveforms for Case 6

### PCA9504A

Figure 12. Waveforms for Case 7

Figure 13. Waveforms for boundary GPO\_FLUSH\_CACHE\* Case

- Timings should remain the same for both a 66 MHz or 33 MHz CLK\_IN input.

- The boundary condition for INIT listed above, is a special case where immediately following the FLUSH\_OUT\*, INIT\_OUT\* cycle, the ICH2 asserts INIT\* into the Glue Chip.

- The boundary condition for GPO\_FLUSH\_CACHE\* listed above, is a special case where immediately following the first assertion of GPO\_FLUSH\_CACHE\*, the GPO is de-asserted, then re-asserted again before the timings have had a chance to complete.

#### NOTE:

1. Nominal timing values with tolerances are listed in the DC Characteristics table.

GPO\_FLUSH\_CACHE\* – input to logic, GPO from the ICH2, programmed active LOW.

INIT\* – input to logic, INIT\* signal from the ICH2.

A20M\* - input to logic, A20M\* signal from the ICH2.

FLUSH\_OUT\_CPU\* - output of logic, route to CPU FLUSH\* pin.

FLUSH\_OUT\_CPU\* - output of logic, routed to FWH INIT\* pin.

INIT\_OUT\* – output of logic, routed to CPU INIT\* pin.

### PCA9504A

Figure 14. Power up signal sequencing

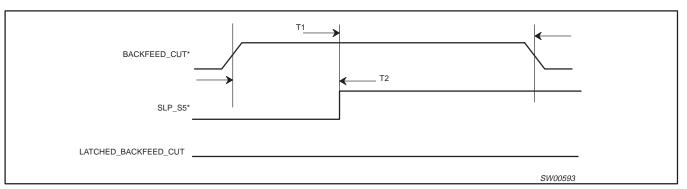

Power up signal sequencing is shown in Figure 14. BACKFEED\_CUT\* is following the power rail up to its final value. LATCHED\_BACKFEED\_CUT should stay LOW, never turning on. SLP\_S5\* goes to its HIGH value when the power rails have stabilized, ~25 msec after power on. BACKFEED\_CUT\* is pulled LOW a period T1 after SLP\_S5\* goes HIGH. T1 can be as short as 1msec. Typical measured values are ~200 msec. T1 and T2 are guaranteed by the inherent design of the system and are not controlled by Glue Chip.

Figure 15. 1st sequence timing

The first possible sequence is with SLP\_S5\*staying HIGH and BACKFEED\_CUT\* transitioning from LOW to HIGH, remaining HIGH for an undetermined period and then going back to LOW and the system is back at the end of the power-up sequence. The power-up sequence is shown in Figure 15. During these BACKFEED\_CUT\* transitions, the propagation delays, rise and fall times, and going into regulation times LATCHED\_BACKFEED\_CUT are as described in Figure 16. The first sequence starts can start at the end of the power-up sequence at any time.

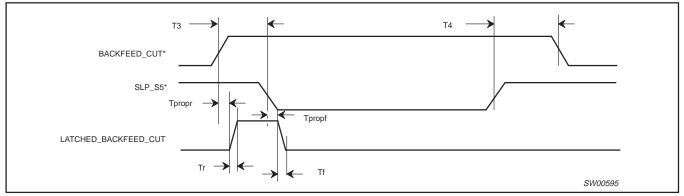

Signal sequencing for the second possible sequence is shown in Figure 16. BACKFEED\_CUT\* goes from LOW to HIGH and SLP\_S5\* goes from HIGH to LOW, 30 µsec to 65 µsec (T3) later. LATCHED\_BACKFEED\_CUT goes HIGH when BACKFEED\_CUT\* goes HIGH and then LATCHED\_BACKFEED\_CUT returns to LOW when SLP\_S5\* goes LOW. BACKFEED\_CUT\* stays HIGH and SLP\_S5\* stays LOW for an indeterminate time and then SLP\_S5\* will go HIGH. A minimum of 1msec (T4) later, BACKFEED\_CUT\* will go LOW and the system is back at the end of the power-up sequence. Typical measured values of T4 are ~250 msec. During all transitions, the propagation delays, rise and fall times, and going into regulation times for LATCHED\_BACKFEED\_CUT are as described in Figure 16. The first sequence starts can start at the end of the power-up sequence at any time.

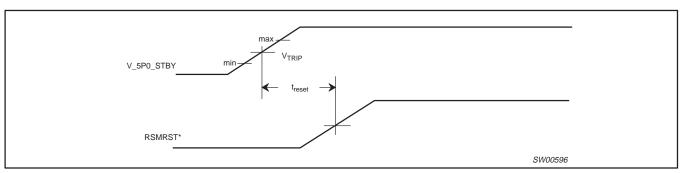

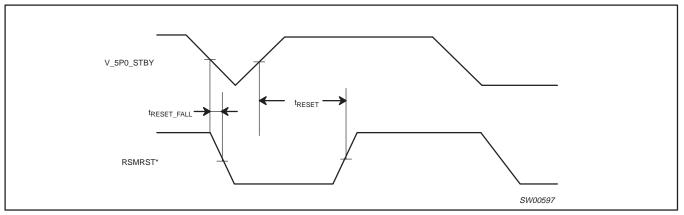

#### **RSMRST\* GENERATION**

RSMRST\* is a delayed 3.3 V hysteresis copy of V\_5PO\_STBY. RSMRST\* is delayed going inactive from the rising edge of V\_5PO\_STBY by 32 ms, nominal. This delay starts when V\_5PO\_STBY hits the trip point. There is minimal delay on the falling edge.

Figure 17. Resume reset functionality

Figure 18. Resume reset functionality during brown out

### AUDIO-DISABLE

| AUD_EN | PCIRST | AUD_RST |

|--------|--------|---------|

| 0      | 0      | 0       |

| 0      | 1      | 0       |

| 1      | 0      | 0       |

| 1      | 1      | 1       |

### MUTE AUDIO CIRCUIT

| MUTE_AUD | AUD_SHDN |

|----------|----------|

| 0        | 1        |

| 1        | 0        |

### HD SINGLE COLOR LED DRIVER

| PRIMARY_HD | SECONDARY_HD | SCSI | HD_LED |

|------------|--------------|------|--------|

| 0          | 0            | 0    | 0      |

| 0          | Х            | Х    | 0      |

| Х          | 0            | Х    | 0      |

| Х          | Х            | 0    | 0      |

| 1          | 1            | 1    | HI–Z   |

### IDE RESET SIGNAL GENERATION AND PCRIST DRIVE STRENGTH

| PCIRST | IDE_RSTDRV <sup>1</sup> | PCIRST_OUT |

|--------|-------------------------|------------|

| 0      | 0                       | 0          |

| 1      | 1                       | 1          |

NOTE:

1. IDE\_RSTDRV is a 5 V copy of PCIRST. PCIRST\_OUT is a 3.3 V copy of PCIRST.

### **PWRGD SIGNAL GENERATION**

| FPRST | PWRGD_PS | PWRGD_3V |

|-------|----------|----------|

| 0     | 0        | 0        |

| 0     | 1        | 0        |

| 1     | 0        | 0        |

| 1     | 1        | 1        |

### FLUSH\_OUT / INIT\_OUT CIRCUIT

| CASE | A20M | GPO_FLUSH_CACHE | INIT | FLUSH_OUT_CPU | FLUSH_OUT_FWH | INIT_OUT                                               |

|------|------|-----------------|------|---------------|---------------|--------------------------------------------------------|

| 1    | 1    | Falling edge    | 0    | 0(for t1)     | 0(for t1)     | 0, Hi-Z, then 0 (delayed by t1-t, then active for 2*t) |

| 2    | 1    | Falling edge    | 1    | 0(for t1)     | 0(for t1)     | Hi-Z, 0 (delayed by t1-t,<br>then active for 2*t)      |

| 3    | Х    | 1               | 0    | Hi-Z          | Hi-Z          | 0                                                      |

| 4    | Х    | 1               | 1    | Hi-Z          | Hi-Z          | Hi-Z                                                   |

| 5    | 0    | Falling edge    | 1    | Hi-Z          | Hi-Z          | Hi-Z                                                   |

| 6    | 0    | Falling edge    | 0    | Hi-Z          | Hi-Z          | 0                                                      |

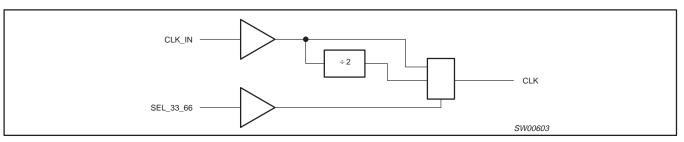

### CLK\_IN AND SEL\_33\_66

| SEL_33_66 | CLK_IN RATE |  |

|-----------|-------------|--|

| 0         | 66 MHz      |  |

| 1         | 33 MHz      |  |

### PCA9504A

#### Figure 19.

### **GP\_IN/GP\_OUT GENERAL PURPOSE GATES**

| GP1_INA | GP1_INB | GP1_OUT |

|---------|---------|---------|

| 0       | 0       | 1       |

| 0       | 1       | 1       |

| 1       | 0       | 1       |

| 1       | 1       | 0       |

### GP\_IN/GP\_OUT GENERAL PURPOSE GATES (continued)

| GP2_IN | GP2_OUT |

|--------|---------|

| 0      | 1       |

| 1      | 0       |

### GP\_IN/GP\_OUT GENERAL PURPOSE GATES (continued)

| GP3_IN | GP3_OUT |  |

|--------|---------|--|

| 0      | 0       |  |

| 1      | 1       |  |

### **POWER SEQUENCING / BACKFEED\_CUT**

| PWRGD_PS | SLP_S3 | BACKFEED_CUT |

|----------|--------|--------------|

| 0        | 0      | HI-Z         |

| 0        | 1      | HI-Z         |

| 1        | 0      | HI-Z         |

| 1        | 1      | 0            |

#### **POWER SUPPLY TURN-ON CIRCUIT**

| SLOTOCC | SLP_S3 | SLP_S3A |

|---------|--------|---------|

| 0       | 0      | Hi-Z    |

| 0       | 1      | 0       |

| 1       | 0      | Hi-Z    |

| 1       | 1      | Hi-Z    |

#### RAMBUS\_SCK\_BJT

| PWRGD_3V | SCK_BJT_GATE |

|----------|--------------|

| 0        | Hi-Z         |

| 1        | 0            |

# PCA9504A

### **VGA DCC VOLTAGE TRANSLATION**

| 3V_DDCSDA | 3V_DDCSCL | 5V_DDCSDA | 5V_DDCSCL |

|-----------|-----------|-----------|-----------|

| 0         | 0         | 0         | 0         |

| 0         | 1         | 0         | 1         |

| 1         | 0         | 1         | 0         |

| 1         | 1         | 1         | 1         |

### **HSYNC / VSYNC VOLTAGE TRANSLATION**

| HSYNC_3V | HSYNC_5V | VSYNC_3V | VSYNC_5V |  |

|----------|----------|----------|----------|--|

| 0        | 0        | 0        | 0        |  |

| 1        | 1        | 1        | 1        |  |

### POWER LED DRIVER

| YLW_BLNK | SLP_S5 | YLW_LED | GRN_BLNK | SLP_S5 | GRN_LED |

|----------|--------|---------|----------|--------|---------|

| 0        | 0      | 0       | 0        | 0      | 0       |

| 0        | 1      | 0       | 0        | 1      | 0       |

| 1        | 0      | 0       | 1        | 0      | 0       |

| 1        | 1      | HI-Z    | 1        | 1      | Hi-Z    |

Product data

Product data

# PCA9504A

### **REVISION HISTORY**

| Rev | Date     | Description                                                                                                                                                                                                                          |

|-----|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| _5  | 20040511 | <ul> <li>Product data (9397 750 13279). Supersedes data of 2003 Nov 10 (9397 750 12288).</li> <li>Modifications:</li> <li>Page 24, Audio-disable table: AUD_EN column (reading veritcally) changed from '0000' to '0011'.</li> </ul> |

| _4  | 20031110 | Product data (9397 750 12288); ECN 853-2206 30409 dated 10 October 2003.<br>Supersedes data of 28 March 2003 (9397 750 09602).                                                                                                       |

| _3  | 20030328 | Product data (9397 750 09602); ECN: 853–2206 27930 (2003 Mar 28)                                                                                                                                                                     |

PCA9504A

Purchase of Philips I<sup>2</sup>C components conveys a license under the Philips' I<sup>2</sup>C patent to use the components in the I<sup>2</sup>C system provided the system conforms to the I<sup>2</sup>C specifications defined by Philips. This specification can be ordered using the code 9398 393 40011.

#### Data sheet status

| Level | Data sheet status <sup>[1]</sup> | Product<br>status <sup>[2] [3]</sup> | Definitions                                                                                                                                                                                                                                                                                    |

|-------|----------------------------------|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I     | Objective data                   | Development                          | This data sheet contains data from the objective specification for product development.<br>Philips Semiconductors reserves the right to change the specification in any manner without notice.                                                                                                 |

| II    | Preliminary data                 | Qualification                        | This data sheet contains data from the preliminary specification. Supplementary data will be published at a later date. Philips Semiconductors reserves the right to change the specification without notice, in order to improve the design and supply the best possible product.             |

| III   | Product data                     | Production                           | This data sheet contains data from the product specification. Philips Semiconductors reserves the right to make changes at any time in order to improve the design, manufacturing and supply. Relevant changes will be communicated via a Customer Product/Process Change Notification (CPCN). |

[1] Please consult the most recently issued data sheet before initiating or completing a design.

[2] The product status of the device(s) described in this data sheet may have changed since this data sheet was published. The latest information is available on the Internet at URL http://www.semiconductors.philips.com.

[3] For data sheets describing multiple type numbers, the highest-level product status determines the data sheet status.

#### Definitions

Short-form specification — The data in a short-form specification is extracted from a full data sheet with the same type number and title. For detailed information see the relevant data sheet or data handbook.

Limiting values definition — Limiting values given are in accordance with the Absolute Maximum Rating System (IEC 60134). Stress above one or more of the limiting values may cause permanent damage to the device. These are stress ratings only and operation of the device at these or at any other conditions above those given in the Characteristics sections of the specification is not implied. Exposure to limiting values for extended periods may affect device reliability.

Application information — Applications that are described herein for any of these products are for illustrative purposes only. Philips Semiconductors make no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

#### Disclaimers

Life support — These products are not designed for use in life support appliances, devices, or systems where malfunction of these products can reasonably be expected to result in personal injury. Philips Semiconductors customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Philips Semiconductors for any damages resulting from such application.

Right to make changes — Philips Semiconductors reserves the right to make changes in the products—including circuits, standard cells, and/or software—described or contained herein in order to improve design and/or performance. When the product is in full production (status 'Production'), relevant changes will be communicated via a Customer Product/Process Change Notification (CPCN). Philips Semiconductors assumes no responsibility or liability for the use of any of these products, conveys no license or title under any patent, copyright, or mask work right to these products, and makes no representations or warranties that these products are free from patent, copyright, or mask work right infringement, unless otherwise specified.

#### **Contact information**

For additional information please visit http://www.semiconductors.philips.com. Fa

Fax: +31 40 27 24825

All rights reserved. Printed in U.S.A.

© Koninklijke Philips Electronics N.V. 2004

Date of release: 05-04

For sales offices addresses send e-mail to: sales.addresses@www.semiconductors.philips.com Document order number:

9397 750 13279

Let's make things better.

Philips

Semiconductors