## INTEGRATED CIRCUITS

# DATA SHEET

## **SCC2681T**

Dual asynchronous receiver/transmitter (DUART)

Product data 2004 Apr 06

## **Dual asynchronous receiver/transmitter (DUART)**

## **SCC2681T**

#### **DESCRIPTION**

The Philips Semiconductors SCC2681 Dual Universal Asynchronous Receiver/Transmitter (DUART) is a single-chip MOS-LSI communications device that provides two independent full-duplex asynchronous receiver/transmitter channels in a single package. The SCC2681T features a faster bus cycle time than the standard SCC2681. The quick bus cycle eliminates or reduces the need for wait states with fast CPUs and permits high throughput in I/O intensive systems. Higher external clock rates may be used with the transmitter, receiver and counter timer which in turn provide greater versatility in baud rate generation. The SCC2681T interfaces directly with microprocessors and may be used in a polled or interrupt driven system. It is manufactured in CMOS technology.

The operating mode and data format of each channel can be programmed independently. Additionally, each receiver and transmitter can select its operating speed as one of eighteen fixed baud rates, a 16× clock derived from a programmable counter/timer, or an external 1× or 16× clock. The baud rate generator and counter/timer can operate directly from a crystal or from external clock inputs. The ability to independently program the operating speed of the receiver and transmitter make the DUART particularly attractive for dual-speed channel applications such as clustered terminal systems.

Each receiver is quadruple buffered to minimize the potential of receiver over-run or to reduce interrupt overhead in interrupt driven systems. In addition, a flow control capability is provided to disable a remote DUART transmitter when the receiver buffer is full.

Also provided on the SCC2681T are a multipurpose 7-bit input port and a multipurpose 8-bit output port. These can be used as general purpose I/O ports or can be assigned specific functions (such as clock inputs or status/interrupt outputs) under program control.

For a complete functional description and programming information for the SCC2681T, refer to the SCC2681 product specification.

#### **FEATURES**

- Fast bus cycle times reduce or eliminate CPU wait states

- Dual full-duplex asynchronous receiver/transmitters

- Quadruple buffered receiver data registers

- Programmable data format

- 5 to 8 data bits plus parity

- Odd, even, no parity or force parity

- 1, 1.5 or 2 stop bits programmable in 1/16-bit increments

- 16-bit programmable Counter/Timer

- Programmable baud rate for each receiver and transmitter selectable from:

- 22 fixed rates: 50 to 115.2 k baud

- Non-standard rates to 115.2

- Non-standard user-defined rate derived from programmable counter/timer

- External 1x or 16x clock

- Parity, framing, and overrun error detection

- False start bit detection

- Line break detection and generation

- Programmable channel mode

- Normal (full-duplex)

- Automatic echo

- Local loopback

- Remote loopback

- Multi-function programmable 16-bit counter/timer

- Multi-function 7-bit input port

- Can serve as clock or control inputs

- Change of state detection on four inputs

- 100 kΩ typical pull-up resistors

- Multi-function 8-bit output port

- Individual bit set/reset capability

- Outputs can be programmed to be status/interrupt/DMA signals

- Auto 485 turn-around

- Versatile interrupt system

- Single interrupt output with eight maskable interrupting conditions

- Output port can be configured to provide a total of up to six separate wire-ORable interrupt outputs

- Maximum data transfer rates:

- 1×-1 MB/sec transmitter and receiver

- 16× 500 kB/sec receiver and 250 kB/sec transmitter

- Automatic wake-up mode for multidrop applications

- Start-end break interrupt/status

- Detects break which originates in the middle of a character

- On-chip crystal oscillator

- Single +5 V power supply

- Commercial temperature range

#### **ORDERING INFORMATION**

| DESCRIPTION                             | $V_{CC}$ = +5 V $\pm$ 10%, $T_{amb}$ = 0 °C to +70 °C | DWG#     |  |

|-----------------------------------------|-------------------------------------------------------|----------|--|

| 44-Pin Plastic Lead Chip Carrier (PLCC) | SCC2681TC1A44                                         | SOT187-2 |  |

NOTE: For a full register description and programming information see the SCC2681.

## Dual asynchronous receiver/transmitter (DUART)

SCC2681T

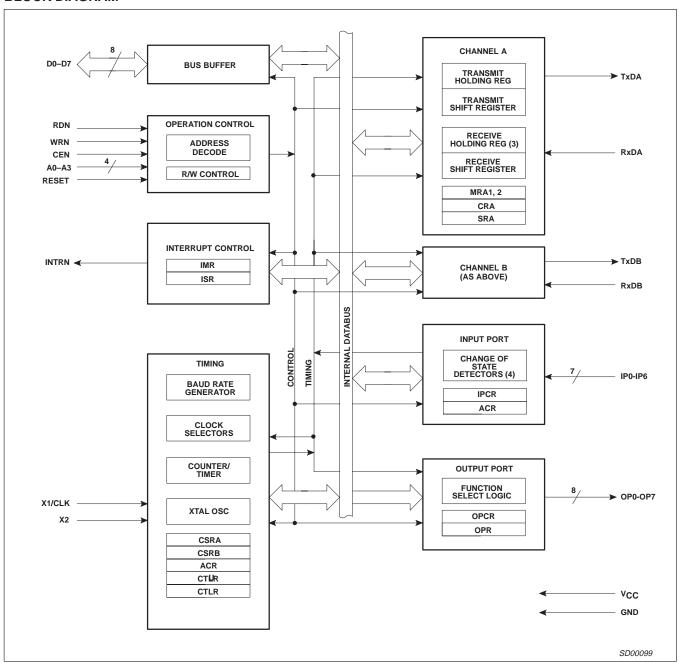

#### **BLOCK DIAGRAM**

Figure 1. Block Diagram

NOTE

Refer to SCC2681 for functional description.

## Dual asynchronous receiver/transmitter (DUART)

SCC2681T

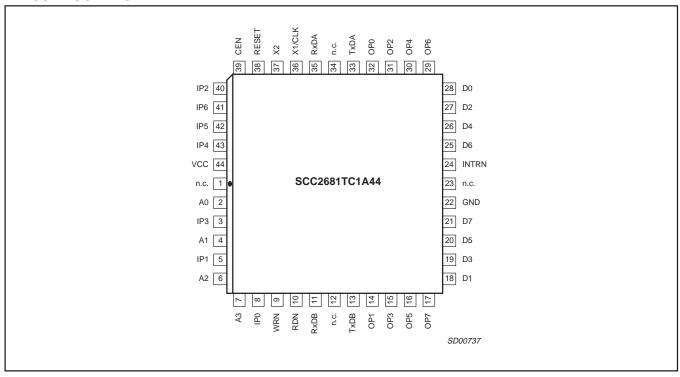

#### **PIN CONFIGURATION**

Figure 2. Pin configuration

#### **PIN DESCRIPTION**

| MNEMONIC | PIN                                  | TYPE | NAME AND FUNCTION                                                                                                                                                                                                                                                                            |

|----------|--------------------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D0-D7    | 21, 25, 20,<br>26, 19, 27,<br>18, 28 | I/O  | <b>Data Bus:</b> Bidirectional three-state data bus used to transfer commands, data and status between the DUART and the CPU. D0 is the least significant bit.                                                                                                                               |

| CEN      | 39                                   | I    | <b>Chip Enable:</b> Active LOW input signal. When LOW, data transfers between the CPU and the DUART are enabled on D0–D7 as controlled by the WRN, RDN, and A0–A3 inputs. When CEN is HIGH, the DUART places the D0–D7 lines in the three-state condition.                                   |

| WRN      | 9                                    | I    | Write Strobe: When LOW and CEN is also LOW, the contents of the data bus is loaded into the addressed register. The transfer occurs on the rising edge of the signal.                                                                                                                        |

| RDN      | 10                                   | I    | Read Strobe: When low and CEN is also LOW, causes the contents of the addressed register to be presented on the data bus. The read cycle begins on the falling edge of RDN.                                                                                                                  |

| A0-A3    | 2, 4, 6, 7                           | ı    | Address Inputs: Select the DUART internal registers and ports for read/write operations.                                                                                                                                                                                                     |

| RESET    | 38                                   | ı    | Reset: A HIGH level clears internal registers (SRA, SRB, IMR, ISR, OPR, OPCR), puts OP0–OP7 in the HIGH state, stops the counter/timer, and puts channels A and B in the inactive state, with the TxDA and TxDB outputs in the mark (HIGH) state. Clears Test modes, sets MR pointer to MR1. |

| INTRN    | 24                                   | 0    | <b>Interrupt Request:</b> Active-LOW, open-drain output which signals the CPU that one or more of the eight maskable interrupting conditions are true.                                                                                                                                       |

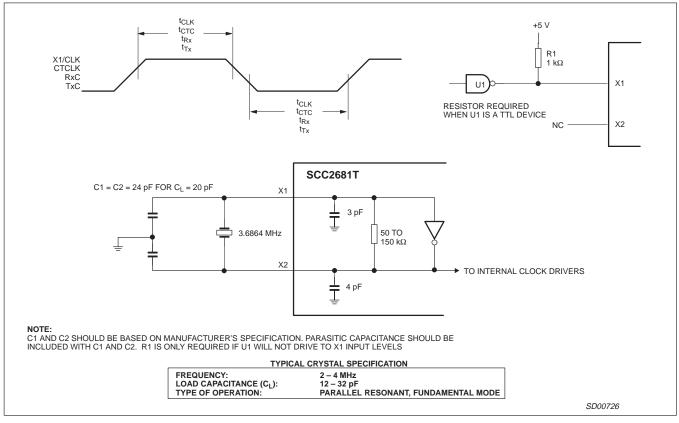

| X1/CLK   | 36                                   | ı    | Crystal 1: Crystal connection or an external clock input. A crystal of a clock the appropriate frequency (nominally 3.6864 MHz) must be supplied at all times. For crystal connections see Figure 7, Clock Timing.                                                                           |

| X2       | 37                                   | I    | Crystal 2: Crystal connection. See Figure 7. If a crystal is not used it is best to keep this pin not connected.  It must not be grounded.                                                                                                                                                   |

| RxDA     | 35                                   | I    | Channel A Receiver Serial Data Input: The least significant bit is received first. 'Mark' is HIGH, 'space' is LOW.                                                                                                                                                                           |

| RxDB     | 11                                   | I    | Channel B Receiver Serial Data Input: The least significant bit is received first. 'Mark' is HIGH, 'space' is LOW.                                                                                                                                                                           |

## Dual asynchronous receiver/transmitter (DUART)

## SCC2681T

| MNEMONIC        | PIN              | TYPE | NAME AND FUNCTION                                                                                                                                                                                                                                                                                   |

|-----------------|------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TxDA            | 33               | 0    | <b>Channel A Transmitter Serial Data Output:</b> The least significant bit is transmitted first. This output is held in the 'mark' condition when the transmitter is disabled, idle, or when operating in local loopback mode. 'Mark' is HIGH, 'space' is LOW.                                      |

| TxDB            | 13               | 0    | Channel B Transmitter Serial Data Output: The least significant bit is transmitted first. This output is held in the 'mark' condition when the transmitter is disabled, idle, or when operating in local loopback mode. 'Mark' is HIGH, 'space' is LOW.                                             |

| OP0             | 32               | 0    | Output 0: General purpose output, or channel A request to send (RTSAN, active-LOW). Can be deactivated automatically on receive or transmit.                                                                                                                                                        |

| OP1             | 14               | 0    | Output 1: General purpose output, or channel B request to send (RTSBN, active-LOW). Can be deactivated automatically on receive or transmit.                                                                                                                                                        |

| OP2             | 31               | 0    | Output 2: General purpose output, or channel A transmitter 1× or 16× clock output, or channel A receiver 1× clock output.                                                                                                                                                                           |

| OP3             | 15               | 0    | Output 3: General purpose output, or open-drain, active-LOW counter/timer interrupt output, or channel B transmitter 1× clock output, or channel B receiver 1× clock output.                                                                                                                        |

| OP4             | 30               | 0    | Output 4: General purpose output, or channel A open-drain, active-LOW, RxRDYA/FFULLA interrupt output.                                                                                                                                                                                              |

| OP5             | 16               | 0    | Output 5: General purpose output, or channel B open-drain, active-LOW, RxRDYB/FFULLB interrupt output.                                                                                                                                                                                              |

| OP6             | 29               | 0    | Output 6: General purpose output, or channel A open-drain, active-LOW, TxRDYA interrupt output.                                                                                                                                                                                                     |

| OP7             | 17               | 0    | Output 7: General purpose output, or channel B open-drain, active-LOW TxRDYB interrupt output.                                                                                                                                                                                                      |

| IP0             | 8                | I    | <b>Input 0:</b> General purpose input, or channel A clear to send active-LOW input (CTSAN). Pin has an internal $V_{CC}$ pull-up device supplying 1 to 4 $\mu$ A of current.                                                                                                                        |

| IP1             | 5                | I    | <b>Input 1:</b> General purpose input, or channel B clear to send active-LOW input (CTSBN). Pin has an internal $V_{CC}$ pull-up device supplying 1 to 4 $\mu$ A of current.                                                                                                                        |

| IP2             | 40               | I    | <b>Input 2:</b> General purpose input, or counter/timer external clock input. Pin has an internal $V_{CC}$ pull-up device supplying 1 to 4 $\mu A$ of current.                                                                                                                                      |

| IP3             | 3                | I    | <b>Input 3:</b> General purpose input, or channel A transmitter external clock input (TxCA). When the external clock is used by the transmitter, the transmitted data is clocked on the falling edge of the clock. Pin has an internal $V_{CC}$ pull-up device supplying 1 to 4 $\mu$ A of current. |

| IP4             | 43               | I    | <b>Input 4:</b> General purpose input, or channel A receiver external clock input (RxCA). When the external clock is used by the receiver, the received data is sampled on the rising edge of the clock. Pin has an internal $V_{CC}$ pull-up device supplying 1 to 4 $\mu$ A of current.           |

| IP5             | 42               | I    | <b>Input 5:</b> General purpose input, or channel B transmitter external clock input (TxCB). When the external clock is used by the transmitter, the transmitted data is clocked on the falling edge of the clock. Pin has an internal $V_{CC}$ pull-up device supplying 1 to 4 $\mu$ A of current. |

| IP6             | 41               | I    | <b>Input 6:</b> General purpose input, or channel B receiver external clock input (RxCB). When the external clock is used by the receiver, the received data is sampled on the rising edge of the clock. Pin has an internal $V_{CC}$ pull-up device supplying 1 to 4 $\mu$ A of current.           |

| V <sub>CC</sub> | 44               | I    | Power Supply: +5 V supply input.                                                                                                                                                                                                                                                                    |

| GND             | 22               | Ι    | Ground                                                                                                                                                                                                                                                                                              |

| n.c.            | 1, 12, 23,<br>34 |      | not connected                                                                                                                                                                                                                                                                                       |

5

Downloaded from Arrow.com.

## Dual asynchronous receiver/transmitter (DUART)

SCC2681T

#### ABSOLUTE MAXIMUM RATINGS<sup>1</sup>

| SYMBOL           | PARAMETER                                        | RATING                           | UNIT |

|------------------|--------------------------------------------------|----------------------------------|------|

| T <sub>amb</sub> | Operating ambient temperature range <sup>2</sup> | 0 to +70                         | °C   |

| T <sub>stg</sub> | Storage temperature range                        | -65 to +150                      | °C   |

|                  | All voltages with respect to GND <sup>3</sup>    | -0.5 to +6.0                     | V    |

|                  | Pin voltage range                                | $V_{SS} - 0.5$ to $V_{CC} + 0.5$ | V    |

<sup>1.</sup> Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operation section of this specification is not

For operating at elevated temperatures, the device must be derated based on +150 °C maximum junction temperature.

This product includes circuitry specifically designed for the protection of its internal devices from damaging effects of excessive static charge. Nonetheless, it is suggested that conventional precautions be taken to avoid applying any voltages larger than the rated maxima.

## Dual asynchronous receiver/transmitter (DUART)

SCC2681T

## DC ELECTRICAL CHARACTERISTICS<sup>1, 2, 3</sup>

$T_{amb}$  = 0 °C to +70 °C;  $V_{CC}$  = +5.0 V  $\pm$  10%

| CVMDOL             | DADAMETER                                                          | TEST COMPLETIONS                   | L                     |     |     |      |

|--------------------|--------------------------------------------------------------------|------------------------------------|-----------------------|-----|-----|------|

| SYMBOL             | PARAMETER                                                          | TEST CONDITIONS                    | Min                   | Тур | Max | UNIT |

| $V_{IL}$           | LOW-level input voltage                                            |                                    | -                     | _   | 0.8 | V    |

| $V_{IH}$           | HIGH-level input voltage (except X1/CLK)                           | T <sub>amb</sub> ≥ 0 °C            | 2.0                   | -   | -   | V    |

| $V_{IH}$           | HIGH-level input voltage (except X1/CLK)                           | T <sub>amb</sub> < 0 °C            | 2.5                   | -   | -   | V    |

| V <sub>IH</sub>    | HIGH-level input voltage (X1/CLK)                                  |                                    | 0.8 V <sub>CC</sub>   |     |     | V    |

| $V_{OL}$           | LOW-level output voltage                                           | $I_{OL} = 2.4 \text{ mA}$          | _                     | _   | 0.4 | V    |

| V <sub>OH</sub>    | HIGH-level output voltage (except open-drain outputs) <sup>4</sup> | $I_{OH} = -400  \mu A$             | V <sub>CC</sub> – 0.5 | -   | -   | V    |

| I <sub>IX1</sub>   | X1/CLK input current                                               | $V_{IN} = 0 \text{ V to } V_{CC}$  | -10                   | -   | +10 | μΑ   |

| I <sub>ILX1</sub>  | X1/CLK input LOW current – operating                               | $V_{IN} = 0 V$                     | -75                   | -   | 0   | μΑ   |

| I <sub>IHX1</sub>  | X1/CLK input HIGH current – operating                              | $V_{IN} = V_{CC}$                  | 0                     | _   | 75  | μΑ   |

| I <sub>OHX2</sub>  | X2 output HIGH current – operating                                 | $V_{OUT} = V_{CC}; X1 = 0$         | 0                     | _   | +75 | μΑ   |

| I <sub>OHX2S</sub> | X2 output HIGH short circuit current – operating                   | $V_{OUT} = 0 V; X1 = 0$            | -10                   | -   | -1  | mΑ   |

| $I_{OLX2}$         | X2 output LOW current – operating                                  | $V_{OUT} = 0 V; X1 = V_{CC}$       | -75                   | -   | 0   | μΑ   |

| I <sub>OLX2S</sub> | X2 output LOW short circuit current – operating                    | $V_{OUT} = V_{CC}$ ; $X1 = V_{CC}$ | 1                     | _   | 10  | mA   |

|                    | Input leakage current:                                             |                                    |                       |     |     |      |

| II                 | All except input port pins                                         | $V_{IN} = 0 V to V_{CC}$           | -10                   | -   | +10 | μΑ   |

|                    | Input port pins                                                    | $V_{IN} = 0 V \text{ to } V_{CC}$  | -20                   | _   | +10 | μΑ   |

| l <sub>ozh</sub>   | Output off current HIGH, 3-state data bus                          | $V_{IN} = V_{CC}$                  | _                     | _   | 10  | μΑ   |

| $I_{OZL}$          | Output off current LOW, 3-state data bus                           | $V_{IN} = 0 V$                     | -10                   | _   | _   | μΑ   |

| I <sub>ODL</sub>   | Open-drain output LOW current in off-state                         | V <sub>IN</sub> = 0 V              | -10                   | _   | _   | μА   |

| I <sub>ODH</sub>   | Open-drain output HIGH current in off-state                        | $V_{IN} = V_{CC}$                  | _                     | _   | 10  | μΑ   |

| loo                | Power supply current <sup>5</sup>                                  |                                    |                       |     |     |      |

| Icc                | Operating mode                                                     | CMOS input levels                  | -                     | _   | 10  | mA   |

1. Parameters are valid over specified temperature range.

<sup>2.</sup> All voltage measurements are referenced to ground (GND). For testing, all inputs swing between 0.4 V and 2.4 V with a transition time of 5 ns maximum. For X1/CLK this swing is between 0.4 V and 4.4 V. All time measurements are referenced at input voltages of 0.8 V and 2.0 V and output voltages of 0.8 V and 2.0 V, as appropriate.

3. Typical values are at +25 °C, typical supply voltages, and typical processing parameters.

<sup>4.</sup> Test conditions for outputs:  $C_L$  = 150 pF, except interrupt outputs. Test conditions for interrupt outputs:  $C_L$  = 50 pF,  $R_L$  = 2.7 k $\Omega$  to  $V_{CC}$ . 5. All outputs are disconnected. Inputs are switching between CMOS levels of  $V_{CC}$  – 0.2 V and  $V_{SS}$  + 0.2 V.

## Dual asynchronous receiver/transmitter (DUART)

SCC2681T

#### AC ELECTRICAL CHARACTERISTICS<sup>1, 2, 3, 4</sup>

| SYMBOL            | DADAMETED                                                                                                                                   |     | LIMIT    |     |       |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------|-----|----------|-----|-------|

| STMBUL            | PARAMETER                                                                                                                                   | Min | Тур      | Max | UNIT  |

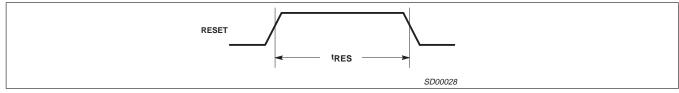

| Reset timin       | g (see Figure 3)                                                                                                                            |     |          |     |       |

| t <sub>RES</sub>  | Reset pulse width                                                                                                                           | 1.0 | -        | _   | μs    |

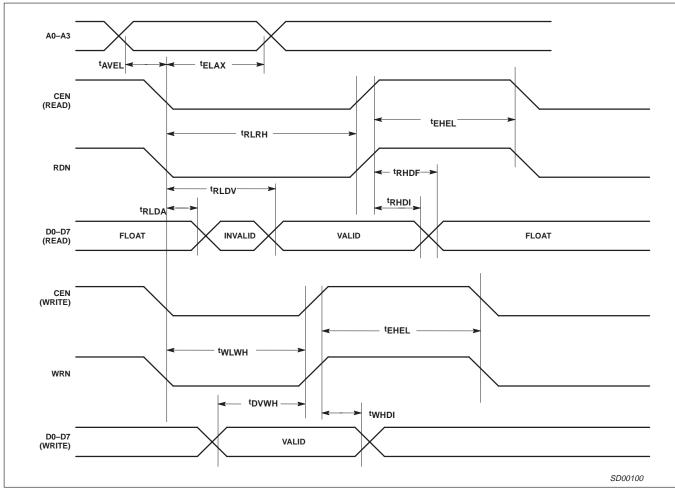

| Bus timing        | (see Figure 4) (Note 5)                                                                                                                     |     |          |     |       |

| t <sub>AVEL</sub> | A0-A3 set-up to RDN and CEN, or WRN and CEN LOW                                                                                             | 0   | -        | -   | ns    |

| $t_{ELAX}$        | RDN and CEN, or WRN and CEN LOW to A0-A3 invalid                                                                                            | 100 | _        | -   | ns    |

| t <sub>RLRH</sub> | RDN and CEN LOW to RDN or CEN HIGH                                                                                                          | 120 | _        | -   | ns    |

| t <sub>EHEL</sub> | CEN HIGH to CEN LOW <sup>6, 7</sup>                                                                                                         | 110 | -        | _   | ns    |

| t <sub>RLDA</sub> | CEN and RDN LOW to data outputs active                                                                                                      | 15  | _        | _   | ns    |

| t <sub>RLDV</sub> | CEN and RDN LOW to data valid                                                                                                               | _   | _        | 100 | ns    |

| t <sub>RHDI</sub> | CEN or RDN HIGH to data invalid                                                                                                             | 10  | -        | -   | ns    |

| t <sub>RHDF</sub> | CEN or RDN HIGH to data outputs floating                                                                                                    | _   | _        | 65  | ns    |

| t <sub>WLWH</sub> | WRN and CEN LOW to WRN or CEN HIGH                                                                                                          | 75  | _        | _   | ns    |

| t <sub>DVWH</sub> | Data input valid to WRN or CEN HIGH                                                                                                         | 35  | _        | _   | ns    |

| twhDi             | WRN or CEN HIGH to data invalid                                                                                                             | 15  | _        | _   | ns    |

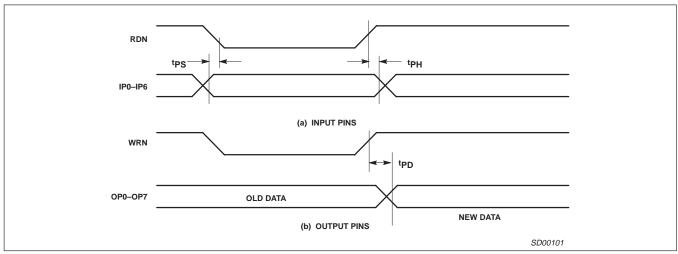

| Port timing       | (see Figure 5)                                                                                                                              |     |          |     |       |

| t <sub>PS</sub>   | Port input set-up time before RDN LOW                                                                                                       | 0   | _        | -   | ns    |

| t <sub>PH</sub>   | Port input hold time after RDN HIGH                                                                                                         | 0   | _        | -   | ns    |

| t <sub>PD</sub>   | Port output valid after WRN HIGH                                                                                                            | _   | _        | 200 | ns    |

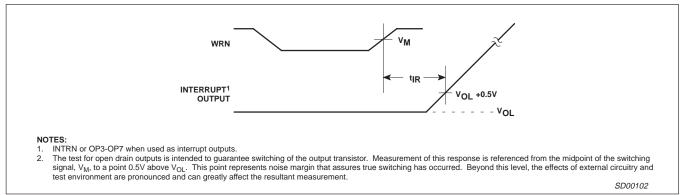

| nterrupt tin      | ning (see Figure 6)                                                                                                                         |     |          |     |       |

|                   | INTRN (or OP3–OP7 when used as interrupts) negated from:                                                                                    |     |          |     |       |

|                   | Read RHR (RxRDY/FFULL interrupt)                                                                                                            | _   | _        | 200 | ns    |

| t <sub>IR</sub>   | Write THR (TxRDY interrupt)                                                                                                                 | _   | _        | 200 | ns    |

|                   | Reset command (delta break interrupt)                                                                                                       | _   | -        | 200 | ns    |

|                   | Stop C/T command (counter interrupt)                                                                                                        | _   | _        | 200 | ns    |

|                   | Read IPCR (input port change interrupt)                                                                                                     | _   | _        | 200 | ns    |

|                   | Write IMR (clear of interrupt mask bit)                                                                                                     | _   | _        | 200 | ns    |

| Clock timin       | g (see Figure 7)                                                                                                                            |     |          |     |       |

| t <sub>CLK</sub>  | X1/CLK HIGH or LOW time                                                                                                                     | 90  |          |     | ns    |

| f <sub>CLK</sub>  | X1/CLK frequency                                                                                                                            | 2   |          | 4   | MHz   |

| t <sub>CTC</sub>  | CTCLK (IP2) HIGH or LOW time                                                                                                                | 55  |          |     | ns    |

| fстс              | CTCLK (IP2) frequency <sup>8</sup>                                                                                                          | 0   |          | 8   | MHz   |

| $t_{RX}$          | RxC HIGH or LOW time                                                                                                                        | 55  |          |     | ns    |

| 4                 | RxC frequency (16×) <sup>8</sup>                                                                                                            | 0   | 3.6864   | 8   | MHz   |

| f <sub>RX</sub>   | (1×) <sup>8</sup>                                                                                                                           | 0   |          | 1   | MHz   |

| t <sub>TX</sub>   | TxC HIGH or LOW time                                                                                                                        | 110 |          |     | ns    |

| f <sub>TX</sub>   | TxC frequency (16x) <sup>8</sup>                                                                                                            | 0   |          | 4   | MHz   |

|                   | (1×) <sup>8</sup>                                                                                                                           | 0   |          | 1   | MHz   |

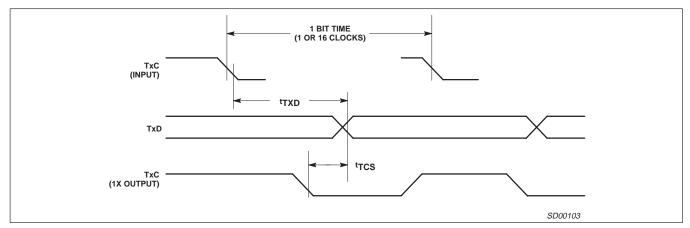

| Transmit tin      | ning (see Figure 8)                                                                                                                         |     |          |     |       |

| t <sub>TXD</sub>  | TxD output delay from TxC external clock input on IP pin                                                                                    | -   | _        | 300 | ns    |

| t <sub>TCS</sub>  | Output delay from TxC LOW at OP pin to TxD data output                                                                                      | 0   | <u> </u> | 100 | ns    |

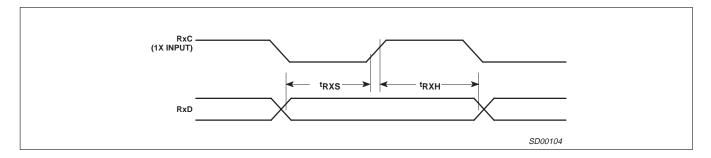

|                   | ing (see Figure )                                                                                                                           |     | 1        |     | 1     |

|                   | RxD data set-up time before RxC HIGH at external clock input on IP pin                                                                      | 200 | _        | _   | ns    |

|                   | · · · · · ·                                                                                                                                 |     | _        |     | ns    |

| t <sub>RXS</sub>  | RXD data set-up time before RXC HIGH at external clock input on IP pin  RXD data hold time after RXC HIGH at external clock input on IP pin | 25  | -        | -   | $\pm$ |

#### NOTES:

- 1. Parameters are valid over specified temperature range. See Ordering information table for applicable operating temperature range and V<sub>CC</sub>

- All voltage measurements are referenced to ground (GND). For testing, all inputs except X1/CLK swing between 0.4 V and 2.4 V with a transition time of 20 ns maximum. For X1/CLK this swing is between 0.4 V and 4.0 V. All time measurements are referenced at input voltages of 0.8 V and 2.0 V and output voltages of 0.8 V and 2.0 V as appropriate.

Typical values are at +25 °C, typical supply voltages, and typical processing parameters.

## Dual asynchronous receiver/transmitter (DUART)

SCC2681T

- 4. Test conditions for outputs:  $C_L = 150$  pF, except interrupt outputs. Test conditions for interrupt outputs:  $C_L = 50$  pF,  $R_L = 2.7$  k $\Omega$  to  $V_{CC}$ .

- 5. For bus operations, CEN and RDN (also CEN and WRN) are ANDed internally. As a consequence, the signal asserted last initiates the cycle and the signal negated first terminates the cycle.

- 6. If CEN is used as the 'strobing' input, the parameter defines the minimum HIGH times between one CEN and the next. The RDN signal must be negated for t<sub>EHEL</sub> to guarantee that any status register changes are valid. As a consequence, this minimum time must be met for the RDN input even if the CEN is used as the strobing signal for bus operations.

- 7. Consecutive write operations to the same command register require at least three edges of the X1 clock between writes.

- 8. Minimum frequencies are not tested but are guaranteed by design.

Figure 3. Reset Timing

Figure 4. Bus Timing

## Dual asynchronous receiver/transmitter (DUART)

SCC2681T

Figure 5. Port Timing

Figure 6. Interrupt Timing

10

## Dual asynchronous receiver/transmitter (DUART)

SCC2681T

Figure 7. Clock Timing

Figure 8. Transmit

## Dual asynchronous receiver/transmitter (DUART)

SCC2681T

Figure 9. Receive

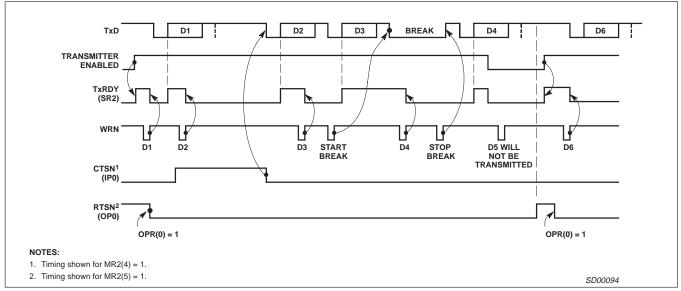

Figure 10. Transmitter Timing

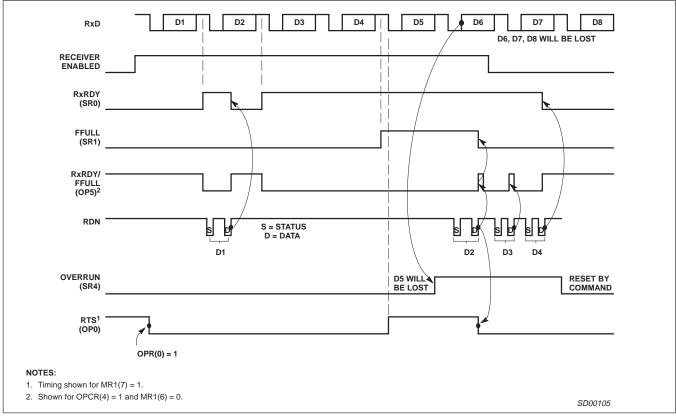

Figure 11. Receiver Timing

12

## Dual asynchronous receiver/transmitter (DUART)

## SCC2681T

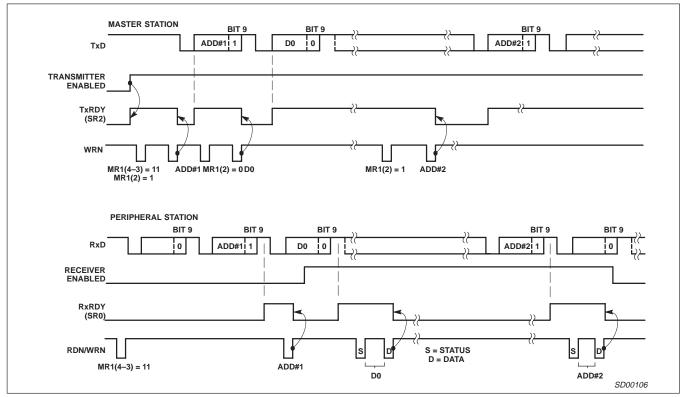

Figure 12. Wake-Up Mode

13

## Dual asynchronous receiver/transmitter (DUART)

SCC2681T

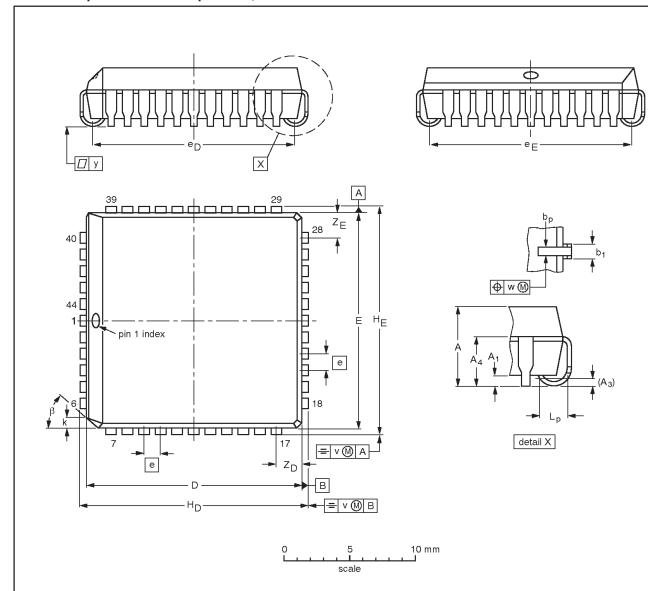

PLCC44: plastic leaded chip carrier; 44 leads

SOT187-2

## DIMENSIONS (mm dimensions are derived from the original inch dimensions)

| UNIT   | А              | A <sub>1</sub><br>min. | A <sub>3</sub> | A <sub>4</sub><br>max. | bр           | b <sub>1</sub> | D <sup>(1)</sup> | E <sup>(1)</sup> | е    | еD             | еE | Н <sub>D</sub> | HE | k | Lp           | v     | w     | у     |       | Z <sub>E</sub> <sup>(1)</sup><br>max. | β   |

|--------|----------------|------------------------|----------------|------------------------|--------------|----------------|------------------|------------------|------|----------------|----|----------------|----|---|--------------|-------|-------|-------|-------|---------------------------------------|-----|

| mm     | 4.57<br>4.19   | 0.51                   | 0.25           | 3.05                   | 0.53<br>0.33 | 0.81<br>0.66   |                  | 16.66<br>16.51   | 1.27 | 16.00<br>14.99 |    |                |    |   | 1.44<br>1.02 | 0.18  | 0.18  | 0.1   | 2.16  | 2.16                                  | 45° |

| inches | 0.180<br>0.165 | 0.02                   | 0.01           |                        |              |                |                  | 0.656<br>0.650   |      | 0.63<br>0.59   |    | 0.695<br>0.685 |    |   |              | 0.007 | 0.007 | 0.004 | 0.085 |                                       |     |

#### Note

1. Plastic or metal protrusions of 0.25 mm (0.01 inch) maximum per side are not included.

| OUTLINE  |        | REFER  | EUROPEAN | ISSUE DATE |            |                                   |

|----------|--------|--------|----------|------------|------------|-----------------------------------|

| VERSION  | IEC    | JEDEC  | JEITA    |            | PROJECTION | ISSUE DATE                        |

| SOT187-2 | 112E10 | MS-018 | EDR-7319 |            |            | <del>-99-12-27-</del><br>01-11-14 |

14

## Dual asynchronous receiver/transmitter (DUART)

SCC2681T

#### REVISION HISTORY

| Rev | Date     | Description                                                                |

|-----|----------|----------------------------------------------------------------------------|

| _1  | 20040406 | Product data (9397 750 12073). ECN 853-2446 01-A15014 of 15 December 2003. |

#### Data sheet status

| Level | Data sheet status [1] | Product<br>status <sup>[2] [3]</sup> | Definitions                                                                                                                                                                                                                                                                                    |

|-------|-----------------------|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I     | Objective data        | Development                          | This data sheet contains data from the objective specification for product development.  Phillips Semiconductors reserves the right to change the specification in any manner without notice.                                                                                                  |

| II    | Preliminary data      | Qualification                        | This data sheet contains data from the preliminary specification. Supplementary data will be published at a later date. Philips Semiconductors reserves the right to change the specification without notice, in order to improve the design and supply the best possible product.             |

| III   | Product data          | Production                           | This data sheet contains data from the product specification. Philips Semiconductors reserves the right to make changes at any time in order to improve the design, manufacturing and supply. Relevant changes will be communicated via a Customer Product/Process Change Notification (CPCN). |

<sup>[1]</sup> Please consult the most recently issued data sheet before initiating or completing a design.

#### **Definitions**

**Short-form specification** — The data in a short-form specification is extracted from a full data sheet with the same type number and title. For detailed information see the relevant data sheet or data handbook.

Limiting values definition — Limiting values given are in accordance with the Absolute Maximum Rating System (IEC 60134). Stress above one or more of the limiting values may cause permanent damage to the device. These are stress ratings only and operation of the device at these or at any other conditions above those given in the Characteristics sections of the specification is not implied. Exposure to limiting values for extended periods may affect device reliability.

**Application information** — Applications that are described herein for any of these products are for illustrative purposes only. Philips Semiconductors make no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

#### **Disclaimers**

Life support — These products are not designed for use in life support appliances, devices, or systems where malfunction of these products can reasonably be expected to result in personal injury. Philips Semiconductors customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Philips Semiconductors for any damages resulting from such application.

Right to make changes — Philips Semiconductors reserves the right to make changes in the products—including circuits, standard cells, and/or software—described or contained herein in order to improve design and/or performance. When the product is in full production (status 'Production'), relevant changes will be communicated via a Customer Product/Process Change Notification (CPCN). Philips Semiconductors assumes no responsibility or liability for the use of any of these products, conveys no license or title under any patent, copyright, or mask work right to these products, and makes no representations or warranties that these products are free from patent, copyright, or mask work right infringement, unless otherwise specified.

#### **Contact information**

For additional information please visit

http://www.semiconductors.philips.com. Fax: +31 40 27 24825

For sales offices addresses send e-mail to:

sales.addresses@www.semiconductors.philips.com

© Koninklijke Philips Electronics N.V. 2004 All rights reserved. Printed in U.S.A.

Date of release: 04-04

Document order number: 9397 750 12073

Let's make things better.

Philips Semiconductors

<sup>[2]</sup> The product status of the device(s) described in this data sheet may have changed since this data sheet was published. The latest information is available on the Internet at URL http://www.semiconductors.philips.com.

<sup>[3]</sup> For data sheets describing multiple type numbers, the highest-level product status determines the data sheet status.