√RoHS

# Power Amplifier Module for LTE and 5G

The AFSC5G40E38 is a fully integrated Doherty power amplifier module designed for wireless infrastructure applications that demand high performance in the smallest footprint. Ideal for applications in massive MIMO systems, outdoor small cells and low power remote radio heads. The field-proven LDMOS power amplifiers are designed for TDD and FDD LTE systems.

## 3700-4000 MHz

• Typical LTE Performance:  $P_{out} = 6.3 \text{ W Avg.}$ ,  $V_{DD} = 28 \text{ Vdc}$ ,  $1 \times 20 \text{ MHz LTE}$ , Input Signal PAR = 8 dB @ 0.01% Probability on CCDF. <sup>(1)</sup>

| Carrier Center<br>Frequency | Gain<br>(dB) | ACPR<br>(dBc) | PAE<br>(%) |

|-----------------------------|--------------|---------------|------------|

| 3710 MHz                    | 26.1         | -27.2         | 38.3       |

| 3800 MHz                    | 26.6         | -26.7         | 39.5       |

| 3900 MHz                    | 27.5         | -25.7         | 39.3       |

| 3990 MHz                    | 28.5         | -23.9         | 37.6       |

1. All data measured with device soldered in NXP reference circuit.

## Features

- Frequency: 3700–4000 MHz

- Advanced high performance in-package Doherty

- · Fully matched (50 ohm input/output, DC blocked)

- · Designed for low complexity analog or digital linearization systems

3700–4000 MHz, 27 dB, 6.3 W Avg. AIRFAST POWER AMPLIFIER MODULE

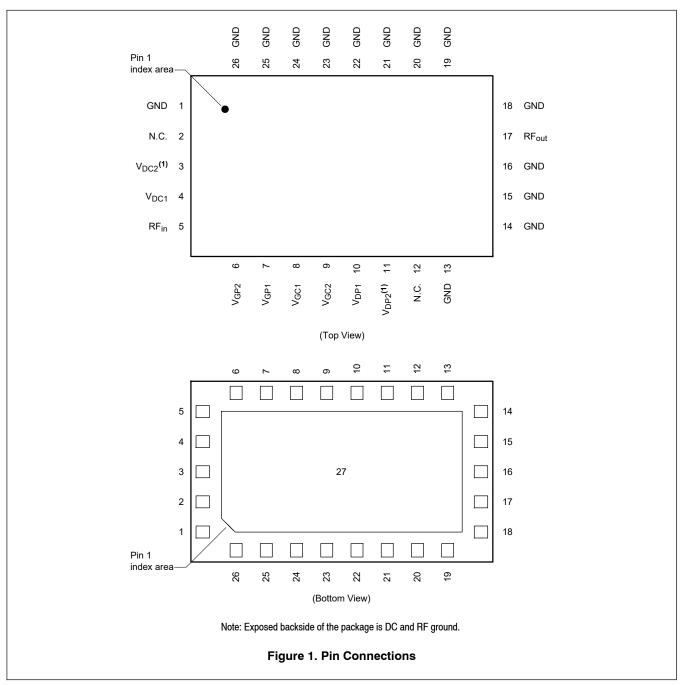

1.  $V_{DC2}$  and  $V_{DP2}$  are DC coupled internal to the package and must be powered by a single DC power supply.

# Table 1. Functional Pin Description

| Pin Number                                                | Pin Function      | Pin Description               |

|-----------------------------------------------------------|-------------------|-------------------------------|

| 1, 13, 14, 15, 16, 18, 19, 20, 21, 22, 23, 24, 25, 26, 27 | GND               | Ground                        |

| 2, 12                                                     | N.C.              | No Connection                 |

| 3                                                         | V <sub>DC2</sub>  | Carrier Drain Supply, Stage 2 |

| 4                                                         | V <sub>DC1</sub>  | Carrier Drain Supply, Stage 1 |

| 5                                                         | RF <sub>in</sub>  | RF Input                      |

| 6                                                         | V <sub>GP2</sub>  | Peaking Gate Supply, Stage 2  |

| 7                                                         | V <sub>GP1</sub>  | Peaking Gate Supply, Stage 1  |

| 8                                                         | V <sub>GC1</sub>  | Carrier Gate Supply, Stage 1  |

| 9                                                         | V <sub>GC2</sub>  | Carrier Gate Supply, Stage 2  |

| 10                                                        | V <sub>DP1</sub>  | Peaking Drain Supply, Stage 1 |

| 11                                                        | V <sub>DP2</sub>  | Peaking Drain Supply, Stage 2 |

| 17                                                        | RF <sub>out</sub> | RF Output                     |

# Table 2. Maximum Ratings

| Rating                                                                 | Symbol           | Value       | Unit |

|------------------------------------------------------------------------|------------------|-------------|------|

| Gate-Bias Voltage Range                                                | V <sub>G</sub>   | -0.5 to +10 | Vdc  |

| Operating Voltage Range                                                | V <sub>DD</sub>  | 24 to 30    | Vdc  |

| Storage Temperature Range                                              | T <sub>stg</sub> | 65 to +150  | °C   |

| Case Operating Temperature                                             | T <sub>C</sub>   | 125         | °C   |

| Peak Input Power<br>(3950 MHz, Pulsed CW, 10 μsec(on), 10% Duty Cycle) | P <sub>in</sub>  | 25          | dBm  |

Table 3. Lifetime

| Characteristic                             | Symbol | Value | Unit  |

|--------------------------------------------|--------|-------|-------|

| Mean Time to Failure                       | MTTF   | > 10  | Years |

| Case Temperature 125°C, 6.3 W Avg., 30 Vdc |        |       |       |

## **Table 4. ESD Protection Characteristics**

| Test Methodology                      | Class |

|---------------------------------------|-------|

| Human Body Model (per JS-001-2017)    | 1A    |

| Charge Device Model (per JS-002-2014) | C2b   |

# Table 5. Moisture Sensitivity Level

| Test Methodology                     | Rating | Package Peak Temperature | Unit |

|--------------------------------------|--------|--------------------------|------|

| Per JESD22-A113, IPC/JEDEC J-STD-020 | 3      | 260                      | °C   |

| Characteristic                                                                                                             | Symbol              | Тур | Range | Unit |

|----------------------------------------------------------------------------------------------------------------------------|---------------------|-----|-------|------|

| Carrier Stage 1 — On Characteristics                                                                                       | 1                   |     |       |      |

| Gate Threshold Voltage <sup>(1)</sup><br>(V <sub>DS</sub> = 10 Vdc, I <sub>D</sub> = 1.6 μAdc)                             | V <sub>GS(th)</sub> | 1.2 | ±0.4  | Vdc  |

| Gate Quiescent Voltage<br>(V <sub>DS</sub> = 28 Vdc, I <sub>DQ1A</sub> = 15 mAdc)                                          | V <sub>GS(Q)</sub>  | 1.9 | ±0.4  | Vdc  |

| Fixture Gate Quiescent Voltage<br>(V <sub>DD</sub> = 28 Vdc, I <sub>DQ1A</sub> = 15 mAdc, Measured in Functional Test)     | V <sub>GG(Q)</sub>  | 4.8 | ±1.4  | Vdc  |

| Carrier Stage 2 — On Characteristics                                                                                       |                     |     |       |      |

| Gate Threshold Voltage (1)<br>( $V_{DS} = 10 \text{ Vdc}, I_D = 14.4 \mu \text{Adc}$ )                                     | V <sub>GS(th)</sub> | 1.2 | ±0.4  | Vdc  |

| Gate Quiescent Voltage<br>(V <sub>DS</sub> = 28 Vdc, I <sub>DQ2A</sub> = 50 mAdc)                                          | V <sub>GS(Q)</sub>  | 1.8 | ±0.4  | Vdc  |

| Fixture Gate Quiescent Voltage $(V_{DD} = 28 \text{ Vdc}, I_{DQ2A} = 50 \text{ mAdc}, \text{Measured in Functional Test})$ | V <sub>GG(Q)</sub>  | 2.7 | ±1.2  | Vdc  |

| Peaking Stage 1 — On Characteristics <sup>(1)</sup>                                                                        |                     | ·   |       | ł    |

| Gate Threshold Voltage $(V_{DS} = 10 \text{ Vdc}, I_D = 2.0 \ \mu\text{Adc})$                                              | V <sub>GS(th)</sub> | 1.2 | ±0.4  | Vdc  |

| Gate Quiescent Voltage ( $V_{DS} = 28 \text{ Vdc}, I_{DQ1A} = 5.1 \mu \text{Adc}$ )                                        | V <sub>GS(Q)</sub>  | 1.2 | ±0.4  | Vdc  |

| Fixture Gate Quiescent Voltage ( $V_{DD}$ = 28 Vdc, $I_{DQ1A}$ = 5.1 µAdc, Measured in Functional Test)                    | V <sub>GG(Q)</sub>  | 1.2 | ±0.4  | Vdc  |

| Peaking Stage 2 — On Characteristics <sup>(1)</sup>                                                                        |                     |     |       |      |

| Gate Threshold Voltage $(V_{DS} = 10 \text{ Vdc}, I_D = 27.2 \ \mu\text{Adc})$                                             | V <sub>GS(th)</sub> | 1.2 | ±0.4  | Vdc  |

| Gate Quiescent Voltage<br>(V <sub>DS</sub> = 28 Vdc, I <sub>DQ2A</sub> = 16.7 μAdc)                                        | V <sub>GS(Q)</sub>  | 1.2 | ±0.4  | Vdc  |

| Fixture Gate Quiescent Voltage<br>(V <sub>DD</sub> = 28 Vdc, I <sub>DQ2A</sub> = 16.7 μAdc, Measured in Functional Test)   | V <sub>GG(Q)</sub>  | 1.2 | ±0.4  | Vdc  |

## Table 6. Electrical Characteristics (T<sub>A</sub> = 25°C unless otherwise noted)

1. Each side of device measured separately.

(continued)

| Characteristic                                                                                                                                                                                                     | Symbol                                | Min                          | Тур                                    | Max                         | Unit        |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|------------------------------|----------------------------------------|-----------------------------|-------------|

| Functional Tests — 3800 MHz <sup>(1)</sup> (In NXP Doherty Production ATE <sup>(2)</sup> Te<br>$DQ2A = 50 \text{ mA}, V_{GS1B} = (V_t - 0.21) \text{ Vdc}, V_{GS2B} = (V_t - 0.20) \text{ Vdc}, P_{out} = 0$       | st Fixture, 50 oh<br>6.3 W Avg., 1-to | m system) V<br>one CW, f = 3 | <sub>DD</sub> = 28 Vdc, I<br>800 MHz.  | <sub>DQ1A</sub> = 15 mA     | ι,          |

| Gain                                                                                                                                                                                                               | G                                     | 24.8                         | 26.7                                   | _                           | dB          |

| Drain Efficiency                                                                                                                                                                                                   | η <sub>D</sub>                        | 34.5                         | 43.5                                   | _                           | %           |

| Pout @ 3 dB Compression Point                                                                                                                                                                                      | P3dB                                  | 43.6                         | 44.4                                   | _                           | dBm         |

| Functional Tests — 4000 MHz <sup>(1)</sup> (In NXP Doherty Production ATE <sup>(2)</sup> Te<br>$DQ2A = 50 \text{ mA}, V_{GS1B} = (V_t - 0.21) \text{ Vdc}, V_{GS2B} = (V_t - 0.20) \text{ Vdc}, P_{out} = 0$       | st Fixture, 50 oh<br>6.3 W Avg., 1-to | m system) V<br>one CW, f = 4 | <sub>DD</sub> = 28 Vdc, I<br>₀000 MHz. | <sub>DQ1A</sub> = 15 mA     | ι,          |

| Gain                                                                                                                                                                                                               | G                                     | 27.1                         | 28.8                                   | _                           | dB          |

| Drain Efficiency                                                                                                                                                                                                   | η <sub>D</sub>                        | 33.0                         | 38.0                                   | _                           | %           |

| Pout @ 3 dB Compression Point                                                                                                                                                                                      | P3dB                                  | 42.9                         | 43.7                                   | _                           | dBm         |

| <ul> <li>V<sub>GSP1</sub> = 1.3 Vdc, V<sub>GSP2</sub> = 1.3 Vdc, f = 3900 MHz, Additive White Gauss</li> <li>ISBW of 400 MHz at 30 Vdc, 3 dB Input Overdrive from 6.3 W Avg.<br/>Modulated Output Power</li> </ul> |                                       | No [                         | Device Degrac                          |                             | - 0         |

| <b>Typical Performance <sup>(3)</sup></b> (In NXP Doherty Power Amplifier Module Refere<br>DQ2A = 50 mA, V <sub>GSP1</sub> = 1.3 Vdc, V <sub>GSP2</sub> = 1.3 Vdc, P <sub>out</sub> = 6.3 W Avg., 39               | 00 MHz                                | onn system)                  | +                                      | ;, I <sub>DQ1A</sub> = 15 I | <del></del> |

| VBW Resonance Point, 2-tone, 1 MHz Tone Spacing<br>(IMD Third Order Intermodulation Inflection Point)                                                                                                              | VBW <sub>res</sub>                    | _                            | 241                                    | _                           | MHz         |

| Quiescent Current Accuracy over Temperature (4)with 2.2 k $\Omega$ Gate Feed Resistors (-40 to 105°C)Stage 1with 2.2 k $\Omega$ Gate Feed Resistors (-40 to 105°C)Stage 2                                          | Δl <sub>QT</sub>                      | _                            | 1.0<br>6.0                             | _                           | %           |

| 1-carrier 20 MHz LTE, 8 dB Input Signal PAR                                                                                                                                                                        |                                       |                              |                                        | •                           |             |

| Gain                                                                                                                                                                                                               | G                                     | —                            | 27.5                                   | _                           | dB          |

| Power Added Efficiency                                                                                                                                                                                             | PAE                                   | —                            | 39.3                                   | _                           | %           |

| Adjacent Channel Power Ratio                                                                                                                                                                                       | ACPR                                  | _                            | -25.7                                  | _                           | dBc         |

| Adjacent Channel Power Ratio                                                                                                                                                                                       | ALT1                                  | _                            | -38.8                                  | _                           | dBc         |

| Adjacent Channel Power Ratio                                                                                                                                                                                       | ALT2                                  | _                            | -44.8                                  | _                           | dBc         |

| Gain Flatness <sup>(5)</sup>                                                                                                                                                                                       | G <sub>F</sub>                        | —                            | 2.4                                    | _                           | dB          |

| Fast CW, 27 ms Sweep                                                                                                                                                                                               |                                       |                              | •                                      |                             | •           |

| Pout @ 3 dB Compression Point                                                                                                                                                                                      | P3dB                                  | _                            | 45.5                                   | _                           | dBm         |

| AM/PM @ P3dB                                                                                                                                                                                                       | Φ                                     | _                            | -46                                    | _                           | 0           |

| Gain Variation @ Avg. Power over Temperature<br>(-40°C to +105°C)                                                                                                                                                  | ΔG                                    | _                            | 0.025                                  | _                           | dB/°C       |

| P3dB Variation over Temperature                                                                                                                                                                                    | ∆P3dB                                 | _                            | 0.014                                  | _                           | dB/°C       |

## Table 7. Ordering Information

| Device        | Tape and Reel Information                               | Package             |

|---------------|---------------------------------------------------------|---------------------|

| AFSC5G40E38T2 | T2 Suffix = 2,000 Units, 24 mm Tape Width, 13-inch Reel | 10 mm × 6 mm Module |

1. Part input and output matched to 50 ohms.

2. ATE is a socketed test environment.

3. All data measured in fixture with device soldered in NXP reference circuit.

4. Refer to AN1977, Quiescent Current Thermal Tracking Circuit in the RF Integrated Circuit Family, and to AN1987, Quiescent Current Control for the RF Integrated Circuit Device Family. Go to <u>http://www.nxp.com/RF</u> and search for AN1977 or AN1987. 5. Gain flatness =  $Max(G(f_{Low} \text{ to } f_{High})) - Min(G(f_{Low} \text{ to } f_{High}))$

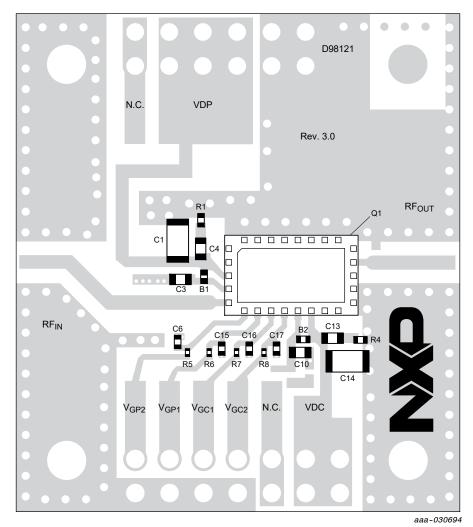

Figure 2. AFSC5G40E38 Reference Circuit Component Layout

| Part              | Description                                 | Part Number       | Manufacturer |

|-------------------|---------------------------------------------|-------------------|--------------|

| B1, B2            | 30 $\Omega$ Ferrite Bead                    | BLM15PD300SN1     | Murata       |

| C1, C14           | 10 μF Chip Capacitor                        | CL31A106KBHNNNE   | Samsung      |

| C3, C4, C10, C13  | 1 μF Chip Capacitor                         | 06035D105KAT2A    | AVX          |

| C6, C15, C16, C17 | 0.1 μF Chip Capacitor                       | GRM155R61H104KE14 | Murata       |

| Q1                | Power Amplifier Module                      | AFSC5G40E38       | NXP          |

| R1, R4            | 5.1 Ω, 1/10 W Chip Resistor                 | ERJ-2GEJ5R1X      | Panasonic    |

| R5, R6, R7, R8    | 2.2 kΩ, 1/20 W Chip Resistor                | ERJ-1GNJ222C      | Panasonic    |

| PCB               | Rogers RO4350B, 0.020", $\epsilon_r = 3.67$ | D98121            | MTL          |

Note: Component numbers C2, C5, C7, C8, C9, C11, C12, R2 and R3 are intentionally omitted.

Figure 3. Product Marking

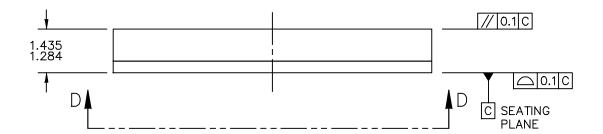

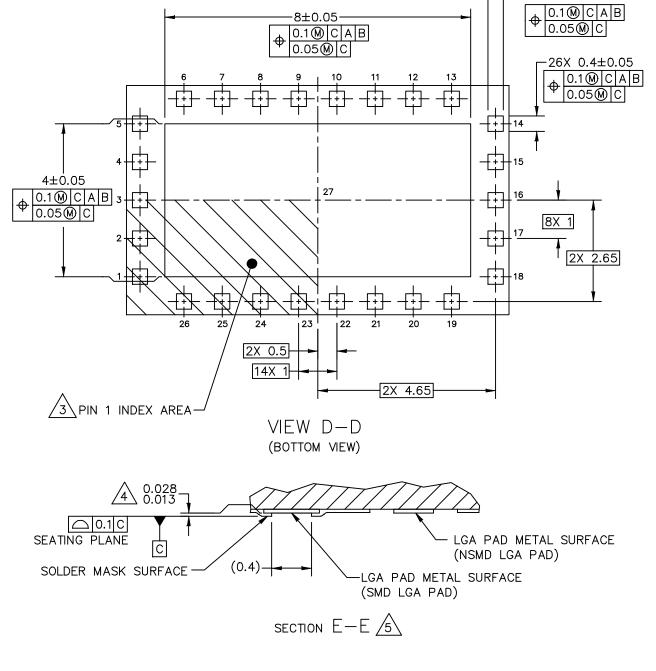

H-PLGA-27 I/O 10 X 6 X 1.365 PKG, 1 PITCH

> PIN 1 INDEX AREA 3 PIN 1 INDEX AREA 3 E E E I TOP VIEW

| © NXP B.V.                 | ALL RIGHTS RESERVED |                 | DATE: 2   | 6 SEP 2019 |

|----------------------------|---------------------|-----------------|-----------|------------|

| MECHANICAL OUTLINE         | STANDARD:           | drawing number: | REVISION: | page:      |

| PRINT VERSION NOT TO SCALE | NON—JEDEC           | 98ASA01540D     | O         | 1 OF 6     |

# AFSC5G40E38

SOT1831-2

SOT1831-2

|          | C NXP B.V.     | ALL RIGHTS RESERVED |                 | DATE: 2   | 6 SEP 2019 |

|----------|----------------|---------------------|-----------------|-----------|------------|

| MECHANIC | CAL OUTLINE    | STANDARD:           | DRAWING NUMBER: | REVISION: | PAGE:      |

|          | N NOT TO SCALE | NON-JEDEC           | 98ASA01540D     | 0         | 2          |

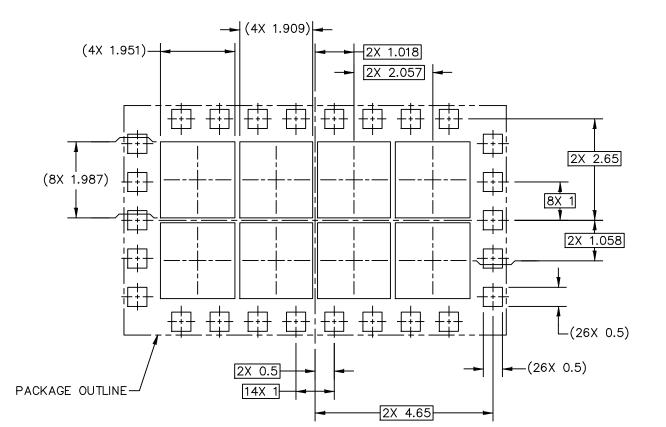

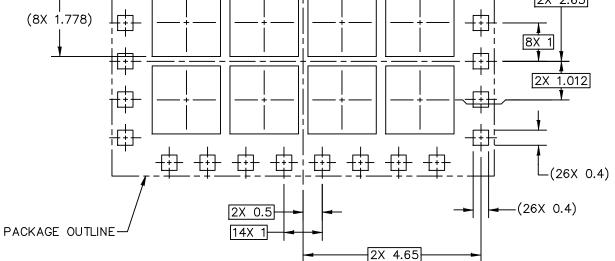

# PCB DESIGN GUIDELINES - SOLDER MASK OPENING PATTERN

THIS SHEET SERVES ONLY AS A GUIDELINE TO HELP DEVELOP A USER SPECIFIC SOLUTION. DEVELOPMENT EFFORT WILL STILL BE REQUIRED BY END USERS TO OPTIMIZE PCB MOUNTING PROCESSES AND BOARD DESIGN IN ORDER TO MEET INDIVIDUAL/SPECIFIC REQUIREMENTS.

| NXP B.V.                   | ALL RIGHTS RESERVED |                 | DATE: 2   | 6 SEP 2019 |

|----------------------------|---------------------|-----------------|-----------|------------|

| MECHANICAL OUTLINE         | STANDARD:           | DRAWING NUMBER: | REVISIÓN: | PAGE:      |

| PRINT VERSION NOT TO SCALE | NON-JEDEC           | 98ASA01540D     | 0         | 3          |

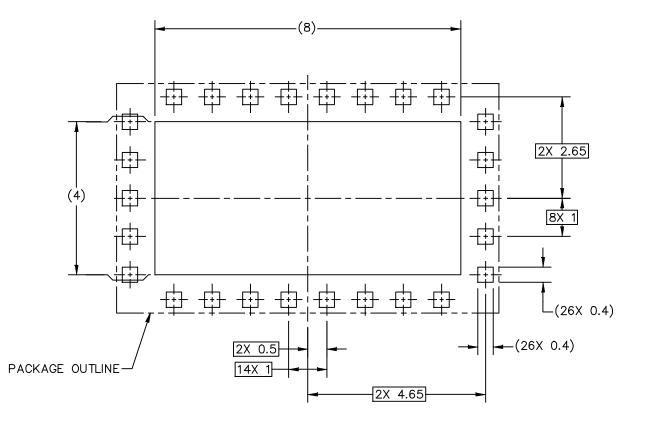

# PCB DESIGN GUIDELINES - I/O PADS AND SOLDERABLE AREAS

THIS SHEET SERVES ONLY AS A GUIDELINE TO HELP DEVELOP A USER SPECIFIC SOLUTION. DEVELOPMENT EFFORT WILL STILL BE REQUIRED BY END USERS TO OPTIMIZE PCB MOUNTING PROCESSES AND BOARD DESIGN IN ORDER TO MEET INDIVIDUAL/SPECIFIC REQUIREMENTS.

| ONXP B.V.                  | ALL RIGHTS RESERVED |                 | DATE: 2   | 6 SEP 2019 |

|----------------------------|---------------------|-----------------|-----------|------------|

| MECHANICAL OUTLINE         | STANDARD:           | DRAWING NUMBER: | REVISIÓN: | PAGE:      |

| PRINT VERSION NOT TO SCALE | NON-JEDEC           | 98ASA01540D     | 0         | 4          |

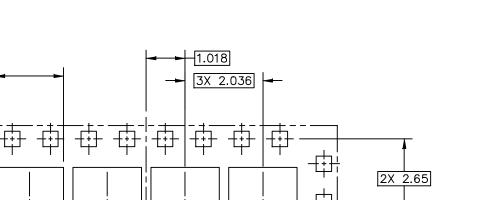

(8X 1.788)-

## RECOMMENDED STENCIL THICKNESS 0.125

PCB DESIGN GUIDELINES - SOLDER PASTE STENCIL

THIS SHEET SERVES ONLY AS A GUIDELINE TO HELP DEVELOP A USER SPECIFIC SOLUTION. DEVELOPMENT EFFORT WILL STILL BE REQUIRED BY END USERS TO OPTIMIZE PCB MOUNTING PROCESSES AND BOARD DESIGN IN ORDER TO MEET INDIVIDUAL/SPECIFIC REQUIREMENTS.

| C NXP B.V.                 | ALL RIGHTS RESERVED |                 | DATE: 2   | 6 SEP 2019 |

|----------------------------|---------------------|-----------------|-----------|------------|

| MECHANICAL OUTLINE         | STANDARD:           | DRAWING NUMBER: | REVISIÓN: | PAGE:      |

| PRINT VERSION NOT TO SCALE | NON-JEDEC           | 98ASA01540D     | 0         | 5          |

## H-PLGA-27 I/O 10 X 6 X 1.365 PKG, 1 PITCH

#### NOTES:

′4.`

5

- 1. ALL DIMENSIONS IN MILLIMETERS.

- 2. DIMENSIONING AND TOLERANCING PER ASME Y14.5M-1994.

- 3. PIN 1 FEATURE SHAPE, SIZE AND LOCATION MAY VARY.

$\Delta$  DIMENSION APPLIES TO ALL LEADS AND FLAG.

THE BOTTOM VIEW SHOWS THE SOLDERABLE AREA OF THE PADS. THE CENTER PAD (PIN 27) IS SOLDER MASK DEFINED. SOME PERIPHERAL PADS ARE SOLDER MASK DEFINED (SMD) AND OTHERS ARE NON-SOLDERMASK DEFINED (NSMD).

| • NXP B.V.                 | ALL RIGHTS RESERVED |                 | DATE: 2   | 6 SEP 2019 |

|----------------------------|---------------------|-----------------|-----------|------------|

| MECHANICAL OUTLINE         | STANDARD:           | DRAWING NUMBER: | REVISION: | PAGE:      |

| PRINT VERSION NOT TO SCALE | NON-JEDEC           | 98ASA01540D     | 0         | 6          |

## **PRODUCT DOCUMENTATION AND TOOLS**

Refer to the following resources to aid your design process.

## **Application Notes**

- AN1977: Quiescent Current Thermal Tracking Circuit in the RF Integrated Circuit Family

- · AN1987: Quiescent Current Control for the RF Integrated Circuit Device Family

#### **Development Tools**

• Printed Circuit Boards

## FAILURE ANALYSIS

At this time, because of the physical characteristics of the part, failure analysis is limited to electrical signature analysis. In cases where NXP is contractually obligated to perform failure analysis (FA) services, full FA may be performed by third party vendors with moderate success. For updates contact your local NXP Sales Office.

## **REVISION HISTORY**

The following table summarizes revisions to this document.

| Revision | Date       | Description                   |  |

|----------|------------|-------------------------------|--|

| 0        | Sept. 2020 | Initial release of data sheet |  |

#### How to Reach Us:

Home Page: nxp.com

Web Support: nxp.com/support Information in this document is provided solely to enable system and software implementers to use NXP products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits based on the information in this document. NXP reserves the right to make changes without further notice to any products herein.

NXP makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does NXP assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in NXP data sheets and/or specifications can and do vary in different applications, and actual performance may vary over time. All operating parameters, including "typicals," must be validated for each customer application by customer's technical experts. NXP does not convey any license under its patent rights nor the rights of others. NXP sells products pursuant to standard terms and conditions.

NXP, the NXP logo, Freescale, the Freescale logo and Airfast are trademarks of NXP B.V. All other product or service names are the property of their respective owners. © 2020 NXP B.V.