# **∍scale Semiconductor** Technical Data

# Analog Dual Axis Micromachined **Accelerometer**

The MMA62XXAKEG series of dual axis (X and Y) silicon capacitive, micromachined accelerometers features a full digital signal processing for filtering, trim and data formatting. It has been optimized for analog output and offers an over-damped transducer.

#### **Features**

- Available in ±20/20g, ±50/50g, or ±100/100g versions. Additional g-ranges between 20 and 100g may be available upon request

- Full-scale range is independently specified for each axis

- 400 Hz, 4 Pole, 16 µs sample time, additional filter options are available

- Ratiometric analog voltage output

- Capture/hold input for system-wide synchronization support

- 3.3 or 5 V single supply operation

- On-chip temperature sensor and voltage regulator

- Internal self-test

- Minimal external component requirements

- Pb-free 20-pin SOIC package

- Qualified AEC-Q100, Rev. F Grade 2 (-40°C/+105°C)

#### **Typical Applications**

- Crash Detection (Airbag)

- Impact and vibration monitoring

- Shock detection

# Rev 0, 12/2009

# **VRoHS**

# MMA6222AKEG MMA6255AKEG **MMA621010AKEG**

# 2-AXIS **ACCELEROMETER**

**KEG SUFFIX (Pb-free)** 20-LEAD SOIC **CASE 475A-02**

| ORDERING INFORMATION |                |                |                   |         |             |  |  |  |

|----------------------|----------------|----------------|-------------------|---------|-------------|--|--|--|

| Device Name          | X-Axis g-Level | Y-Axis g-Level | Temperature Range | Package | Packaging   |  |  |  |

| MMA6222AEG           | 20             | 20             | -40 to +105°C     | 475A-02 | Tubes       |  |  |  |

| MMA6222AEGR2         | 20             | 20             | -40 to +105°C     | 475A-02 | Tape & Reel |  |  |  |

| MMA6222AKEG*         | 20             | 20             | -40 to +105°C     | 475A-02 | Tubes       |  |  |  |

| MMA6222AKEGR2*       | 20             | 20             | -40 to +105°C     | 475A-02 | Tape & Reel |  |  |  |

| MMA6255AEG           | 50             | 50             | -40 to +105°C     | 475A-02 | Tubes       |  |  |  |

| MMA6255AEGR2         | 50             | 50             | -40 to +105°C     | 475A-02 | Tape & Reel |  |  |  |

| MMA6255AKEG*         | 50             | 50             | -40 to +105°C     | 475A-02 | Tubes       |  |  |  |

| MMA6255AKEGR2*       | 50             | 50             | -40 to +105°C     | 475A-02 | Tape & Reel |  |  |  |

| MMA621010AEG         | 100            | 100            | -40 to +105°C     | 475A-02 | Tubes       |  |  |  |

| MMA621010AEGR2       | 100            | 100            | -40 to +105°C     | 475A-02 | Tape & Reel |  |  |  |

| MMA621010AKEG*       | 100            | 100            | -40 to +105°C     | 475A-02 | Tubes       |  |  |  |

| MMA621010AKEGR2*     | 100            | 100            | -40 to +105°C     | 475A-02 | Tape & Reel |  |  |  |

<sup>\*</sup>Part number sourced from a different facility.

Note: If one axis of the MMA62XXAKEG sensor is expected to be used as a confirmation of the other axis, Freescale recommends that MMA62XXAKEG used in conjunction with an additional sensing/safing device for each axis.

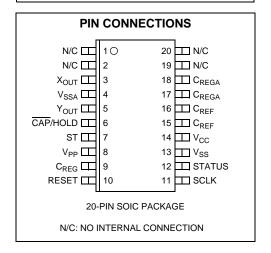

Figure 1-1 Simplified Airbag Application Diagram

# 1.1 INTRODUCTION

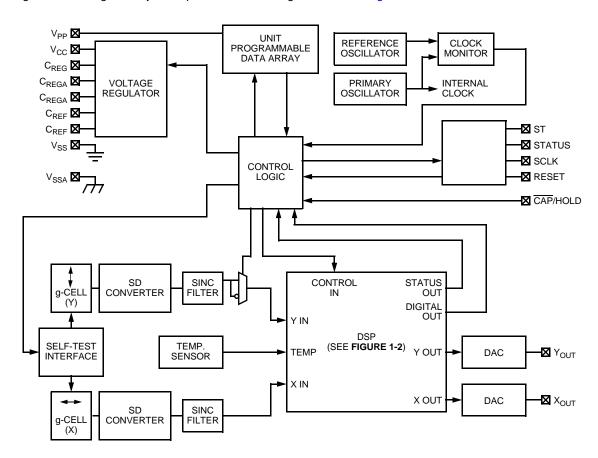

The MMA62XXKEG is trimmed to provide the most accurate voltage representation of acceleration at  $X_{OUT}$  and  $Y_{OUT}$ . This is done by adjusting the signal within the DSP to compensate for errors within the digital-to-analog converters. The SPI is disabled when the device is in normal operating mode, and dedicated ST (self-test activation) and STATUS pin functions are assigned.

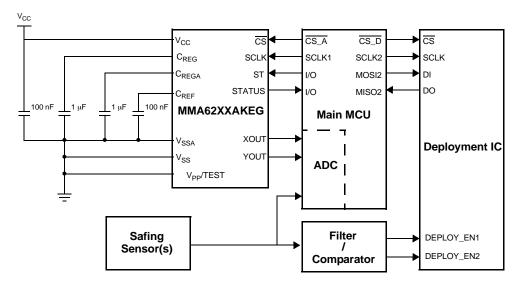

#### 1.2 BLOCK DIAGRAM

A block diagram illustrating the major components of the design is shown in Figure 1-2.

Figure 1-2 MMA62XXAKEG Block Diagram

Figure 1-3 MMA62XXAKEG DSP Block Diagram NOTE: Models of signal chain are available upon request

MMA6222AKEG

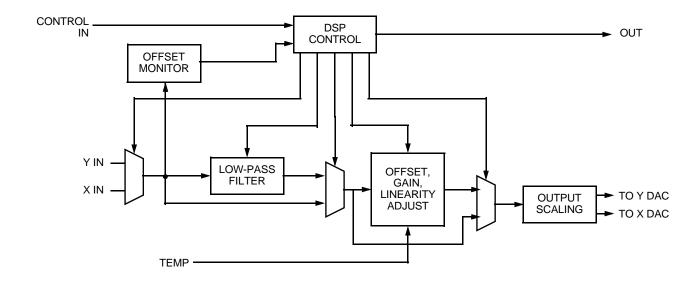

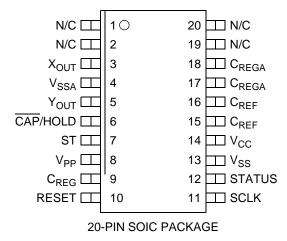

# 1.3 PIN FUNCTIONS

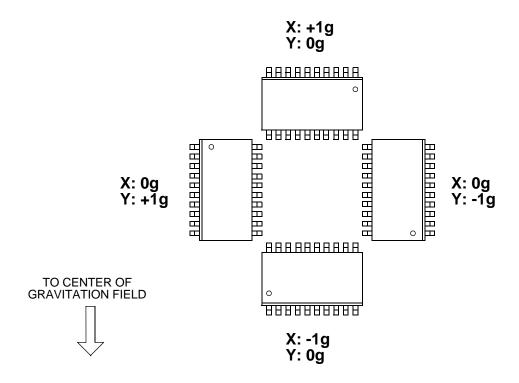

The pinout for the MMA62XXAKEG device is illustrated in Figure 1-4. Pin functions are described below. When self-test is active, the output becomes more positive in both axes if ST1 is cleared, or more negative in both axes if ST1 is set.

N/C: NO INTERNAL CONNECTION

Response to static orientation within 1g field.

Figure 1-4 MMA62XXAKEG Pinout

#### 1.4 PIN FUNCTION DESCRIPTIONS

# 1.4.1 V<sub>CC</sub>

This pin supplies power to the device. Careful printed wiring board layout and capacitor placement is critical to ensure best performance. An external bypass capacitor between this pin and  $V_{SS}$  is required, as described in Section 1.5.

#### 1.4.2 V<sub>SS</sub>

This pin is the power supply return node for the digital circuitry on the MMA62XXKEG device.

# 1.4.3 V<sub>SSA</sub>

This pin is the power supply return node for analog circuitry on the MMA62XXAKEG device. An external bypass capacitor between this pin and  $V_{CC}$  is required, as described in Section 1.5.

# 1.4.4 C<sub>REG</sub>

This pin is connected to the internal digital circuitry power supply rail. An external filter capacitor must be connected between this pin and  $V_{SS}$ , as described in Section 1.5.

# 1.4.5 C<sub>REGA</sub>

These pins are connected in parallel to the internal analog circuitry power supply rail. One or two external filter capacitors must be connected between these pins and  $V_{SSA}$ , as described in Section 1.5. Two pins are provided to support redundant connection to the printed wiring board assembly. Redundant external capacitors may be connected to these pins for maximum reliability, as described in Section 1.5.

# 1.4.6 C<sub>REF</sub>

These pins are connected in parallel to an internal reference voltage node utilized by the analog circuitry. One or two external filter capacitors must be connected between these pins and  $V_{SSA}$ , as described shown in Section 1.5. Two pins are provided to support redundant connection to the printed wiring board assembly. Redundant external capacitors may be connected to these pins for maximum reliability, as described in Section 1.5.

#### 1.4.7 VPP

This pin should be tied directly to V<sub>SS</sub>.

#### 1.4.8 SCLK

This input may be left unconnected unless it is desired to initiate device reset as described in Section 1.4.9.

#### 1.4.9 **RESET**

This pin may be used to initiate a hardware reset. If RESET is held low and SCLK is held high for 512 μs, the internal reset signal is asserted.

An internal pull-up device is connected to this pin.

# 1.4.10 STATUS

This pin provides an indicator of internal status. The STATUS output will be driven to a logic high level should any of the following fault conditions be detected:

- · Internal parity fault

- Over-temperature condition

- Internal clock frequency fault

- · Device reset

- Device initialization

Immediately following device reset, STATUS is placed in a high impedance state for approximately  $800 \, \mu s$ . At the end of this time, STATUS is driven high and a 3ms stabilization delay required by the internal circuitry begins. The STATUS condition may not be cleared during the stabilization delay. Reset is reported by the device so the system can be aware of potential difficulties if unexpected resets occur.

Once asserted, the STATUS output will remain high until the ST pin is driven from a logic low to a logic high state. If a fault condition persists, the STATUS output will be driven high again as soon as it is cleared.

MMA6222AKEG

Freescale Semiconductor

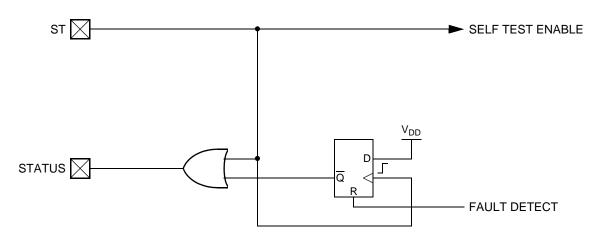

#### 1.4.11 ST

This pin performs a dual function. When driven to a logic high level, the internal self-test voltage generator is activated. A low-to-high transition on this pin will clear the internal STATUS latch. Note that under certain fault conditions, the STATUS latch will be immediately reset, indicating a terminal fault condition.

A diagram illustrating operation of the STATUS latch following device initialization is illustrated in Figure 1-5.

Figure 1-5 ST and STATUS Interaction

# 1.4.12 CAP/HOLD

When this input pin is low, acceleration data is updated by the DSP whenever a data sample becomes available. Upon a low-to-high transition of CAP/HOLD acceleration data is frozen. Acceleration data is not updated as long as the pin remains at a logic '1' level. This pin may be tied directly to V<sub>SS</sub> if the hold function is not desired.

# 1.4.13 X<sub>OUT</sub>, Y<sub>OUT</sub>

Two digital-to-analog converters (DACs) are provided. These converters translate output of the DSP block into voltage levels proportional to the magnitude of the numerical result and ratiometric to  $V_{CC}$ .

#### 1.5 EXTERNAL COMPONENTS

The connections illustrated in Figure 1-1 are recommended. Careful printed wiring board layout and component placement is essential for best performance. Low ESR capacitors must be connected to C<sub>REG</sub> and C<sub>REGA</sub> pins for the best performance. A grounded land area with solder mask should be placed under the package for improved shielding of the device from external effects. If a land area is not provided, no signals should be routed beneath the package. See Figure 1-1.

# **SECTION 2 PERFORMANCE SPECIFICATION**

#### 2.1 MAXIMUM RATINGS

Maximum ratings are the extreme limits to which the device can be exposed without permanently damaging it. The device contains circuitry to protect the inputs against damage from high static voltages; however, do not apply voltages higher than those shown in the table below. Keep input and output voltages within the range  $V_{SS} \le V \le V_{CC}$ .

| Ref            | Rating                                                                                      | Symbol                                                     | Value                         | Unit        |

|----------------|---------------------------------------------------------------------------------------------|------------------------------------------------------------|-------------------------------|-------------|

| 1              | Supply Voltage                                                                              | V <sub>CC</sub>                                            | -0.3 to +7                    | V           |

| 2              | $C_{REG}$ , $C_{REGA}$ , $C_{REF}$                                                          | V <sub>REG</sub>                                           | -0.3 to +3                    | V           |

| 3              | $V_{PP}$                                                                                    | V <sub>REG</sub>                                           | -0.3 to +11                   | V           |

| 4              | SCLK, ST, CAP/HOLD                                                                          | V <sub>IN</sub>                                            | -0.3 to V <sub>CC</sub> + 0.3 | V           |

| 5              | STATUS (high impedance state)                                                               | V <sub>IN</sub>                                            | -0.3 to V <sub>CC</sub> + 0.3 | V           |

| 6              | X <sub>OUT</sub> , Y <sub>OUT</sub> (DACEN = 0)                                             | V <sub>DAC</sub>                                           | -0.3 to V <sub>CC</sub> + 0.3 | V           |

| 7              | Current Drain per Pin Excluding V <sub>CC</sub> and V <sub>SS</sub>                         | per Pin Excluding V <sub>CC</sub> and V <sub>SS</sub> I 10 |                               | mA          |

| 8              | Acceleration (without hitting internal g-cell stops)                                        | g <sub>max</sub> ±800                                      |                               | g           |

| 9              | Powered Shock (six sides, 0.5 ms duration)                                                  | g <sub>pms</sub>                                           | ±1500                         | g           |

| 10             | Unpowered Shock (six sides, 0.5 ms duration)                                                | g <sub>shock</sub>                                         | ±2000                         | g           |

| 11             | Drop Shock (to concrete surface)                                                            | h <sub>DROP</sub>                                          | 1.2                           | m           |

| 12<br>13<br>14 | Electrostatic Discharge Human Body Model (HBM) Charge Device Model (CDM) Machine Model (MM) | V <sub>ESD</sub><br>V <sub>ESD</sub><br>V <sub>ESD</sub>   | ±2000<br>±500<br>±200         | V<br>V<br>V |

| 15             | Storage Temperature Range                                                                   | T <sub>stg</sub>                                           | -40 to +125                   | °C          |

Notes:

# 2.2 OPERATING RANGE

The operating ratings are the limits normally expected in the application and define the range of operation.

| Ref      | Characteristic                                                                                                 | Symbol          | Min                              | Тур          | Max                              | Units |            |

|----------|----------------------------------------------------------------------------------------------------------------|-----------------|----------------------------------|--------------|----------------------------------|-------|------------|

| 16<br>17 | Supply Voltage Standard Operating Voltage, 3.3V operating range Standard Operating Voltage, 5V operating range | V <sub>CC</sub> | V <sub>L</sub><br>+3.15<br>+4.75 | +3.3<br>+5.0 | V <sub>H</sub><br>+3.45<br>+5.25 | V     | (1)<br>(1) |

| 18       | Operating Temperature Range                                                                                    | T <sub>A</sub>  | T <sub>L</sub><br>-40            |              | T <sub>H</sub><br>+105           | С     | (2)        |

Notes:

- 1. Characterized at all values of  $V_L$  and  $V_H$ . Production test is conducted at typical voltage unless otherwise noted.

- 2. Parameters tested 100% at final test.

<sup>1.</sup> Verified by characterization, not tested in production.

#### **ELECTRICAL CHARACTERISTICS** 2.3

$V_L \le (V_{CC} - V_{SS}) \le V_H$ ,  $T_L \le T_A \le T_H$ ,  $|\Delta T_A| < 4$  K/min unless otherwise specified

| Ref                  | Characteristic                                                                                                  | Symbol                                                                                   | Min                          | Тур                            | Max                          | Units                                |                                      |

|----------------------|-----------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|------------------------------|--------------------------------|------------------------------|--------------------------------------|--------------------------------------|

| 19                   | Supply Current Drain<br>Analog-only output configuration                                                        | I <sub>DD</sub>                                                                          |                              | _                              | 9.0                          | mA                                   | (1)                                  |

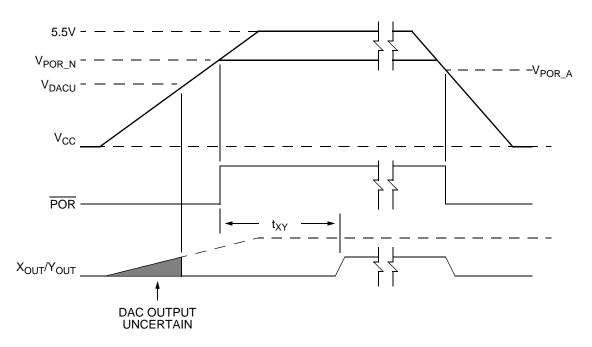

| 20<br>21<br>22<br>23 | Power-On Recovery Threshold (See Figure 2-1)  VCC  CREG  CREGA  CREF                                            | V <sub>POR_N</sub><br>V <sub>POR_N</sub><br>V <sub>POR_N</sub><br>V <sub>POR_N</sub>     | 2.77<br>1.80<br>2.18<br>1.11 | _<br>_<br>_<br>_               | 3.15<br>2.32<br>2.50<br>1.29 | V<br>V<br>V                          | (2)<br>(2)<br>(2)<br>(2)             |

| 24<br>25<br>26<br>27 | Power-On Reset Threshold (See Figure 2-1)  V <sub>CC</sub> C <sub>REG</sub> C <sub>REGA</sub> C <sub>REF</sub>  | V <sub>POR_</sub> A<br>V <sub>POR_</sub> A<br>V <sub>POR_</sub> A<br>V <sub>POR_</sub> A | 2.77<br>1.80<br>2.18<br>1.11 | _<br>_<br>_<br>_               | 2.95<br>2.10<br>2.31<br>1.19 | V<br>V<br>V                          | (2)<br>(2)<br>(2)<br>(2)             |

| 28<br>29<br>30<br>31 | Hysteresis (VPOR_N - VPOR_A, See Figure 2-1) $$\rm V_{CC}$$ $\rm C_{REG}$ $\rm C_{REGA}$ $\rm C_{REF}$          | V <sub>HYST</sub><br>V <sub>HYST</sub><br>V <sub>HYST</sub><br>V <sub>HYST</sub>         | 0<br>0<br>0<br>0             | _<br>_<br>_<br>_               | 388<br>300<br>261<br>150     | mV<br>mV<br>mV                       |                                      |

| 32                   | Minimum Functional Voltage (See Figure 2-1)                                                                     | V <sub>DACU</sub>                                                                        | _                            | _                              | 2.0                          | V                                    | (2)                                  |

| 33<br>34<br>35       | Internally Regulated Voltages  C <sub>REG</sub> C <sub>REGA</sub> (3) C <sub>REF</sub> *                        | V <sub>DD</sub><br>V <sub>2.5</sub><br>V <sub>REF</sub>                                  | 2.42<br>2.42<br>1.20         | 2.50<br>2.50<br>1.25           | 2.58<br>2.58<br>1.29         | V<br>V<br>V                          | (1)<br>(1)<br>(1)                    |

| 36<br>37             | External Filter Capacitor (C <sub>REG</sub> , C <sub>REGA</sub> ) Value ESR (including interconnect resistance) | C <sub>REG</sub><br>ESR                                                                  | 800<br>—                     | 1000                           | <br>200                      | nF<br>mΩ                             | (2)<br>(2)                           |

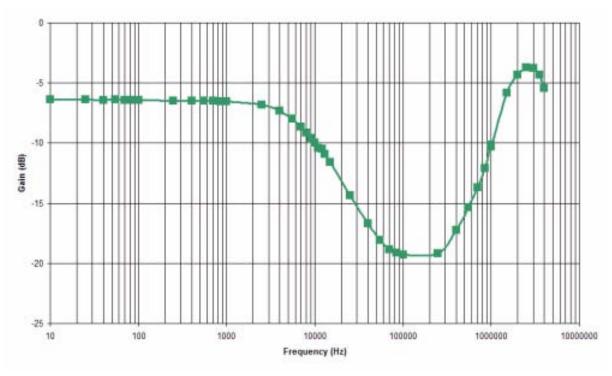

| 38                   | Power Supply Coupling (4) Analog output                                                                         |                                                                                          |                              | See Figu                       | ure 2-2                      |                                      | (2)                                  |

| 39<br>40<br>41<br>42 | Analog Sensitivity (X <sub>OUT</sub> , Y <sub>OUT</sub> ) 20g Range 35g Range 50g Range 100g Range              | ASENS<br>ASENS<br>ASENS<br>ASENS                                                         | _<br>_<br>_<br>_             | 23.40<br>13.40<br>9.37<br>4.68 | _<br>_<br>_<br>_             | mV/V/g<br>mV/V/g<br>mV/V/g<br>mV/V/g | (1)(5)<br>(1)(5)<br>(1)(5)<br>(1)(5) |

| 43<br>44             | Sensitivity Error $T_A = 25^{\circ}C \\ 40^{\circ}C \le T_A \le 105^{\circ}C$                                   | ASLINS                                                                                   | -8<br>-8                     | _<br>_                         | +8<br>+8                     | %<br>%                               | (1)(5)<br>(1)(5)                     |

| 45<br>Note           | Offset at 0g Analog output (X <sub>OUT</sub> , Y <sub>OUT</sub> ) *                                             | A <sub>OUT</sub>                                                                         | 0.46 × V <sub>CC</sub>       | 0.5 × V <sub>CC</sub>          | 0.54 × V <sub>CC</sub>       | V                                    | (1)(5)                               |

- 1. Parameters tested 100% at final test.

- 2. Verified by characterization, not tested in production.

- 3. Tested at V<sub>CC</sub> = V<sub>L</sub> and V<sub>CC</sub> = V<sub>H</sub>.

4. Power supply ripple at frequencies greater than 900 kHz should be minimized to the greatest extent possible.

- 5. Devices are trimmed at 100 Hz with 1000 Hz low-pass filter option selected.

- (#) Indicates a FSL significant parameter (CPK > 1.33).

- (\*) Indicates a FSL critical parameter (CPK > 1.67).

# 2.3 ELECTRICAL CHARACTERISTICS (CONTINUED)

$V_L \leq (V_{CC} - V_{SS}) \leq V_H, \, T_L \leq T_A \leq T_H, \, |\Delta T_A| < 4 \, \, \text{K/min unless otherwise specified}$

| Ref                        | Characteristic                                                                                                                                                                                                     | Symbol                                                                   | Min                               | Тур                               | Max                               | Units                           |                                 |

|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|-----------------------------------|-----------------------------------|-----------------------------------|---------------------------------|---------------------------------|

|                            | Output value on overrange                                                                                                                                                                                          |                                                                          |                                   |                                   |                                   |                                 |                                 |

| 46<br>47<br>48<br>49       | 20g Range<br>35g Range<br>50g Range<br>100g Range                                                                                                                                                                  | 9over<br>9over<br>9over<br>9over                                         | +20.0<br>+35.0<br>+50.0<br>+100.1 | +20.9<br>+36.6<br>+52.1<br>+104.3 | +22.1<br>+38.7<br>+55.3<br>+110.5 | g<br>g<br>g                     | (3)<br>(3)<br>(3)<br>(3)        |

|                            | Output value on Underrange                                                                                                                                                                                         |                                                                          |                                   |                                   |                                   |                                 |                                 |

| 50<br>51<br>52<br>53       | 20g Range<br>35g Range<br>50g Range<br>100g Range                                                                                                                                                                  | 9under<br>9under<br>9under<br>9under                                     | -20.1<br>-35.1<br>-50.1<br>-100.3 | -20.9<br>-36.6<br>-52.2<br>-104.5 | -22.2<br>-38.8<br>-55.4<br>-110.7 | g<br>g<br>g                     | (3)<br>(3)<br>(3)<br>(3)        |

| 54                         | Maximum acceleration without saturation of internal circuitry All ranges                                                                                                                                           | g <sub>SAT</sub>                                                         | -200                              | _                                 | +200                              | g                               | (3)                             |

| 55                         | Nonlinearity                                                                                                                                                                                                       | NL <sub>OUT</sub>                                                        | -1                                | _                                 | 1                                 | % FSR                           | (3)                             |

| 56                         | Noise (1Hz-1kHz)                                                                                                                                                                                                   | n <sub>SD</sub>                                                          | _                                 | _                                 | 1.1                               | mg/√Hz                          | (3)                             |

| 57<br>58                   | Positive Self Test Output Change $(X_{OUT}, Y_{OUT}, analog)$<br>$T_A = 25^{\circ}C$<br>$-40^{\circ}C \le T_A \le 105^{\circ}C$                                                                                    | ΔST<br>ΔST                                                               | 10<br>10                          | _                                 | 18<br>18                          | % FS<br>% FS                    | (1)                             |

| 59<br>60<br>61<br>62       | Cross-Axis Sensitivity V <sub>ZX</sub> V <sub>YX</sub> V <sub>ZY</sub> V <sub>XY</sub>                                                                                                                             | V <sub>ZX</sub><br>V <sub>YX</sub><br>V <sub>ZY</sub><br>V <sub>XY</sub> | -4<br>-4<br>-4<br>-4              |                                   | +4<br>+4<br>+4<br>+4              | %<br>%<br>%                     | (3)<br>(3)<br>(3)<br>(3)        |

| 63<br>64<br>65<br>66<br>67 | DAC Characteristics (X <sub>OUT</sub> , Y <sub>OUT</sub> )  Minimum Output Level, I <sub>OUT</sub> = -200 μA  Maximum Output Level, I <sub>OUT</sub> = 200 μA  Offset Error  Gain Error  Differential Nonlinearity | AV <sub>LOW</sub><br>AV <sub>HIGH</sub><br>OFST<br>GERR<br>DNL           |                                   | _<br>_<br>_<br>_                  | 0.25<br><br>+0.2<br>+0.3<br>+2    | V<br>V<br>%FSR<br>%FSR<br>digit | (2)<br>(2)<br>(2)<br>(2)<br>(2) |

| 68<br>69                   | Integral Nonlinearity  T <sub>A</sub> = 25°C -40°C ≤ T <sub>A</sub> ≤ 105°C                                                                                                                                        | INL<br>INL                                                               | -3<br>-3.5                        | <u> </u>                          | +3<br>+3.5                        | digit<br>digit                  | (2)<br>(3)                      |

| 70<br>71                   | Output High Voltage STATUS ( $I_{Load}$ = -100 $\mu$ A) 3.15 V $\leq$ ( $V_{CC}$ - $V_{SS}$ ) $\leq$ 3.45 V 4.75 V $\leq$ ( $V_{CC}$ - $V_{SS}$ ) $\leq$ 5.25 V                                                    | V <sub>OH</sub><br>V <sub>OH</sub>                                       | 3.25<br>3.75                      | =                                 | _                                 | V                               | (2)                             |

|                            | Output Low Voltage STATUS ( $I_{Load} = 100 \mu A$ ) 3.15 V $\leq$ ( $V_{CC} - V_{SS}$ ) $\leq$ 3.45 V 4.75 V $\leq$ ( $V_{CC} - V_{SS}$ ) $\leq$ 5.25 V                                                           | V <sub>OL</sub><br>V <sub>OL</sub>                                       |                                   |                                   | 0.4<br>0.4                        | V                               | (2)                             |

| 74<br>75                   | Output Loading (STATUS)<br>Load Resistance<br>Load Capacitance                                                                                                                                                     | Z <sub>OUT</sub><br>C <sub>OUT</sub>                                     | 47<br>—                           | _<br>_                            | <br>35                            | kΩ<br>pF                        | (3)<br>(3)                      |

Notes:

- 1. Parameters tested 100% at final test.

- 2. Parameters tested 100% at unit probe.

- 3. Verified by characterization, not tested in production.

MMA6222AKEG

# 2.3 ELECTRICAL CHARACTERISTICS (CONTINUED)

$V_L \leq (V_{CC} - V_{SS}) \leq V_H, \, T_L \leq T_A \leq T_H, \, |\Delta T_A| < 4 \, \, \text{K/min unless otherwise specified}$

| Ref                  | Characteristic                                                                                                                                                                                            | Symbol                               | Min              | Тур              | Max                | Units          |                   |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|------------------|------------------|--------------------|----------------|-------------------|

| 76<br>77             | Output Loading (X <sub>OUT</sub> , Y <sub>OUT</sub> )<br>Load Resistance<br>Load Capacitance                                                                                                              | Z <sub>OUT</sub><br>C <sub>OUT</sub> | 25<br>—          | _<br>_           | —<br>60            | kΩ<br>pF       | (3)               |

|                      | Input High Voltage RESET, SCLK, ST, $\overline{\text{CAP}}/\text{HOLD}$ 3.15 V $\leq$ (V <sub>CC</sub> - V <sub>SS</sub> ) $\leq$ 3.45 V 4.75 V $\leq$ (V <sub>CC</sub> - V <sub>SS</sub> ) $\leq$ 5.25 V | V <sub>IH</sub><br>V <sub>IH</sub>   | 1.5<br>2.5       | _                | _                  | V              | (2)<br>(2)        |

|                      | Input Low Voltage RESET, SCLK, ST, $\overline{\text{CAP}}/\text{HOLD}$ 3.15 V $\leq$ (V <sub>CC</sub> - V <sub>SS</sub> ) $\leq$ 3.45 V 4.75 V $\leq$ (V <sub>CC</sub> - V <sub>SS</sub> ) $\leq$ 5.25 V  | V <sub>IL</sub><br>V <sub>IL</sub>   |                  | _                | 0.85<br>1.0        | V              | (2)               |

| 82<br>83<br>84<br>85 | Input Current High (at V <sub>IH</sub> ) SCLK, ST, CAP/HOLD V <sub>PP</sub> /TEST (internal pulldown resistor) Low (at V <sub>IL</sub> ) RESET                                                            | I <sub>IH</sub><br>R <sub>IN</sub>   | -30<br>190<br>30 | -50<br>270<br>50 | -260<br>350<br>260 | μΑ<br>kΩ<br>μΑ | (2)<br>(2)<br>(2) |

Notes:

- 2. Parameters tested 100% at unit probe.

- 3. Verified by characterization, not tested in production.

# 2.4 CONTROL TIMING

$V_L \leq (V_{CC} - V_{SS}) \leq V_H, \, T_L \leq T_A \leq T_H, \, |\Delta T_A| < 4 \, \, \text{K/min unless otherwise specified}$

| Ref      | Characteristic                                                                       | Symbol                   | Min      | Тур     | Max    | Units       |   |

|----------|--------------------------------------------------------------------------------------|--------------------------|----------|---------|--------|-------------|---|

|          | DSP Low-Pass Filter (Note 9)<br>Cutoff frequency (Note 10)                           |                          |          |         |        |             |   |

| 86       | Filter Option \$0C, \$1F                                                             | f <sub>C(LPF)</sub>      | 380      | 400     | 420    | Hz          | ( |

| 87       | DSP Low-Pass Filter Cutoff frequency (-3dB, referenced to 0 Hz) Filter \$0C, \$1F    | f <sub>C(LPF)</sub>      | 335      | 353     | 371    | Hz          | ( |

| 88       | Filter Order<br>Filter \$00 - \$12                                                   | O <sub>LPF</sub>         | _        | 4       | _      | 1           | ( |

| 89       | Power-On Recovery Time<br>Power applied to X <sub>OUT</sub> , Y <sub>OUT</sub> valid | t <sub>XY</sub>          |          | _       | 10     | ms          | ( |

| 90       | Internal Oscillator Frequency                                                        | fosc                     | 3.8      | 4.0     | 4.2    | MHz         | ( |

| 91       | Clock Monitor Threshold                                                              | f <sub>MON</sub>         | 3.6      | _       | 4.4    | MHz         |   |

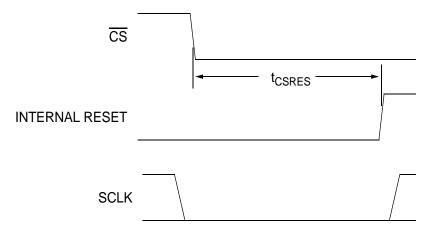

| 92       | Chip Select to Internal Reset (See Figure 2-3)                                       | t <sub>CSRES</sub>       | 486      | 512     | 538    | μs          | ( |

| 93<br>94 | DAC Low-Pass Filter Number of Poles Cutoff Frequency                                 | nPOLES<br>f <sub>C</sub> | <u> </u> | 1<br>10 | <br>20 | unit<br>kHz | ( |

| 95       | Sensing Element Rolloff Frequency (-3 dB)                                            | BW <sub>GCELL</sub>      | _        | 3       | _      | kHz         |   |

#### Notes:

- 1. Parameters tested 100% at final test.

- 2. Parameters tested 100% at unit probe.

- 3. Verified by characterization, not tested in production.

- 4. (\*) Indicates a FSL critical parameter (CPK > 1.67). (#) Indicates a FSL significant parameter (CPK > 1.33).

- 7. Functionality verified 100% via scan. Timing characteristic is directly determined by internal oscillator frequency.

- 9. Devices are trimmed at 100 Hz with 1000 Hz low-pass filter option selected.

- Low-pass filter characteristics match those of other Freescale accelerometer devices. Cutoff frequencies shown are -4dB referenced to 0 Hz response, to correspond with previous specifications.

Figure 2-1 Power-Up Timing

Figure 2-2 Power Supply Coupling - DAC Outputs

Figure 2-3 CS Reset Timing

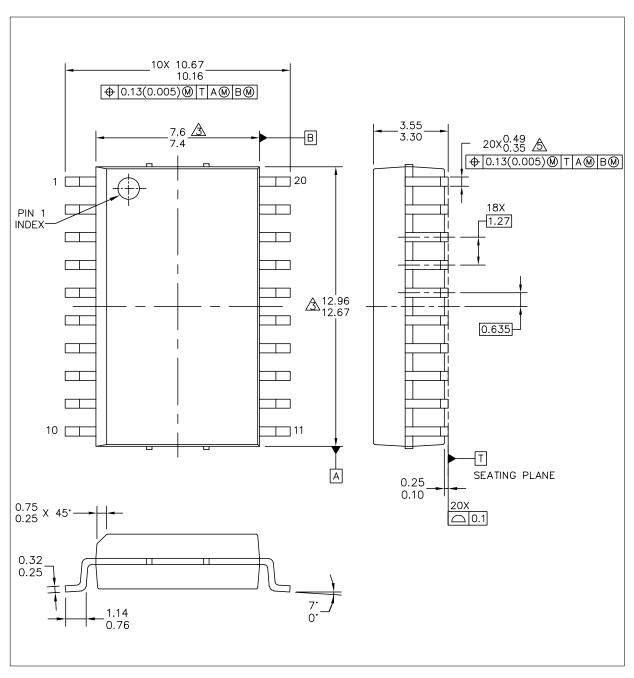

# **PACKAGE DIMENSIONS**

| © FREESCALE SEMICONDUCTOR, INC.<br>ALL RIGHTS RESERVED. | MECHANICA    | L OUTLINE   | PRINT VERSION NO | T TO SCALE  |

|---------------------------------------------------------|--------------|-------------|------------------|-------------|

| TITLE:                                                  | 7 DITOU      | DOCUMENT NO | ): 98ASB17933C   | REV: C      |

| 20LD SOIC W/B, 1.27 PITCH<br>7.5 X 12.8, ACCLEROMETER   |              | CASE NUMBER | R: 475A-02       | 06 JUL 2006 |

| CASE-OUTLINE                                            | STANDARD: NO | N-JEDEC     |                  |             |

# **PACKAGE DIMENSIONS**

#### NOTES:

- 1. DIMENSIONING AND TOLERANCING PER ASME Y14.5M-1994.

- 2. DIMENSIONS ARE IN MILLIMETERS.

3 THIS DIMENSION DO NOT INCLUDE MOLD PROTRUSION.

4. MAXIMUM MOLD PROTRUSION 0.15(0.006) PER SIDE.

5 THIS DIMENSION DOES NOT INCLUDE DAM BAR PROTRUSION ALLOWABLE DAM BAR PROTRUSION SHALL BE 0.13(0.005) TOTAL IN EXCESS OF THIS DIMENSION AT MAXIMUM MATERIAL CONDITION.

| © FREESCALE SEMICONDUCTOR, INC. ALL RIGHTS RESERVED. | MECHANICA | L OUTLINE    | PRINT VERSION NO | OT TO SCALE |

|------------------------------------------------------|-----------|--------------|------------------|-------------|

| TITLE: 20LD SOIC W/B, 1.                             | 27 PITCH  | DOCUMENT NO  | ): 98ASB17933C   | REV: C      |

| 7. 5 X 12. 8, ACCLEROMETER CASE-OUTLINE              |           | CASE NUMBER  | R: 475A-02       | 06 JUL 2006 |

|                                                      |           | STANDARD: NO | N-JEDEC          |             |

MMA6222AKEG

#### How to Reach Us:

Home Page:

www.freescale.com

Web Support:

http://www.freescale.com/support

#### **USA/Europe or Locations Not Listed:**

Freescale Semiconductor, Inc. Technical Information Center, EL516 2100 East Elliot Road Tempe, Arizona 85284 1-800-521-6274 or +1-480-768-2130 www.freescale.com/support

#### Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) www.freescale.com/support

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku, Tokyo 153-0064 Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor China Ltd. Exchange Building 23F No. 118 Jianguo Road Chaoyang District Beijing 100022 China +86 10 5879 8000 support.asia@freescale.com

#### For Literature Requests Only:

Freescale Semiconductor Literature Distribution Center 1-800-441-2447 or +1-303-675-2140 Fax: +1-303-675-2150 LDCForFreescaleSemiconductor@hibbertgroup.com

Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals", must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

Freescale<sup>™</sup> and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners.

© Freescale Semiconductor, Inc. 2009. All rights reserved.

RoHS-compliant and/or Pb-free versions of Freescale products have the functionality and electrical characteristics of their non-RoHS-compliant and/or non-Pb-free counterparts. For further information, see http://www.freescale.com or contact your Freescale sales representative.

$For information on Freescale's \ Environmental \ Products \ program, go to \ http://www.freescale.com/epp.$

MMA6222AKEG Rev. 0 12/2009