# IP4778CZ38

# **HDMI ESD protection, DDC buffering and hot plug control**

Rev. 3 — 31 March 2011

**Product data sheet**

## 1. General description

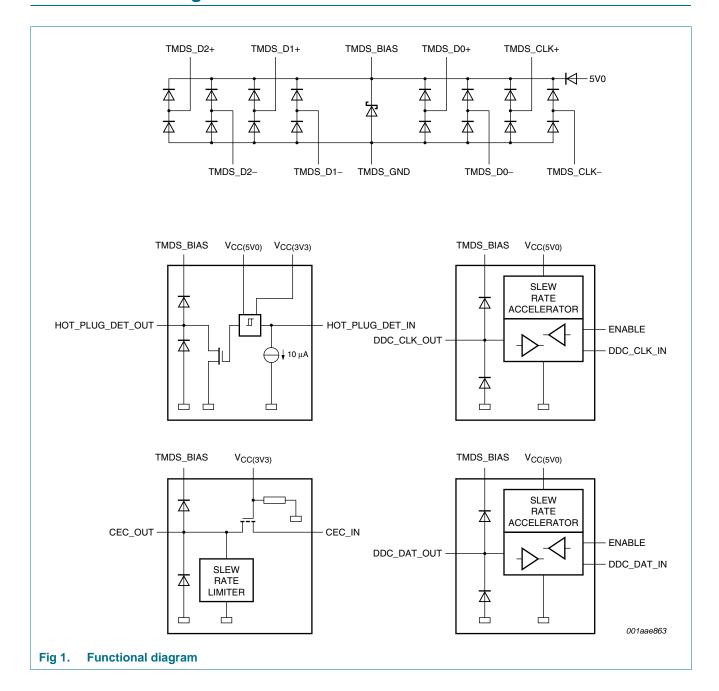

The IP4778CZ38 is designed for HDMI receiver host interface protection.

The IP4778CZ38 includes DDC buffering, slew rate acceleration and decoupling, hot plug control, backdrive protection, CEC slew rate control, optional multiplexing of DDC signals, and high-level ESD protection diodes for all HDMI signals.

The DDC lines are buffered using a new buffering concept which decouples the internal capacitive load from the external capacitive load. This allows higher PCB design flexibility for the DDC lines with respect to a maximum load of 50 pF. This buffering also boosts the DDC signals, allowing the use of longer HDMI cables having a higher capacitive load than 700 pF. The CEC slew rate limiter prevents ringing on the CEC line and greatly reduces the number of discrete components needed by the CEC application. HDMI receiver and system GPIO applications are simplified by an internal hot plug driver module and hot plug control.

The DDC, hot plug and CEC lines are backdrive protected to guarantee HDMI interface signals are not pulled down if the system is powered down or enters Standby mode.

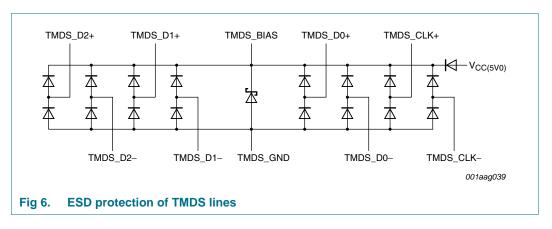

All TMDS intra-pairs are protected by a special diode configuration offering a low line capacitance of 0.7 pF only (to ground) and 0.05 pF between the TMDS pairs. These diodes provide protection to components downstream from ESD voltages of up to  $\pm 8$  kV contact in accordance with the IEC 61000-4-2, level 4 standard.

#### 2. Features and benefits

- Pb-free and RoHS compliant

- Robust ESD protection without degradation after several ESD strikes

- Low leakage even after several hundred ESD discharges

- Very high diode switching speed (ns) and low line capacitance of 0.7 pF to ground and 0.05 pF between channels ensures signal integrity

- DDC capacitive decoupling between system side and HDMI connector side and drive cable buffering with capacitive load (> 700 pF)

- Hot plug control for direct connection to system GPIO

- CEC ringing prevention by slew rate limiter

- DDC and hot plug enable signal for multiplexing and backdrive protection

- All TMDS lines with integrated rail-to-rail clamping diodes with downstream ESD protection of ±8 kV in accordance with IEC 61000-4-2, level 4

- Matched 0.5 mm trace spacing

- Component count reduction of HDMI receiver application

# HDMI ESD protection, DDC buffering and hot plug control

- Highest integration in a small footprint, PCB level, optimized RF routing, 38-pin TSSOP lead-free package

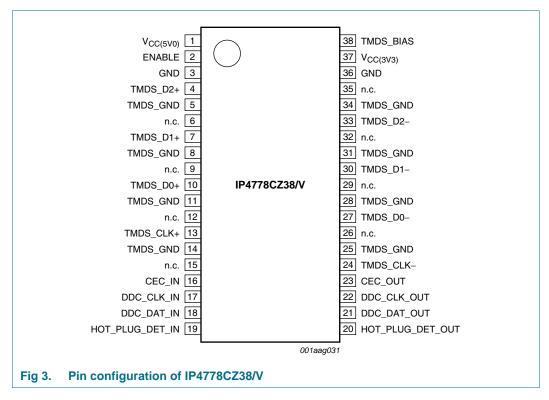

- Choice of system compatible or RF routing optimized pinning variants

# 3. Applications

- The IP4778CZ38 can be used for a wide range of HDMI sink devices e.g.:

- ◆ TV

- Projectors

- PC monitors

- ◆ HDMI buffer modules (extensions of HDMI cable length)

- ◆ HDMI picture performance quality enhancer modules

# 4. Ordering information

Table 1. Ordering information

| Type number  | Package |                                                      |          |  |  |  |  |

|--------------|---------|------------------------------------------------------|----------|--|--|--|--|

|              | Name    | Description                                          | Version  |  |  |  |  |

| IP4778CZ38   | TSSOP38 | plastic thin shrink small outline package; 38 leads; | SOT510-1 |  |  |  |  |

| IP4778CZ38/V |         | body width 4.4 mm; lead pitch 0.5 mm                 |          |  |  |  |  |

## HDMI ESD protection, DDC buffering and hot plug control

# 5. Functional diagram

## **HDMI ESD protection, DDC buffering and hot plug control**

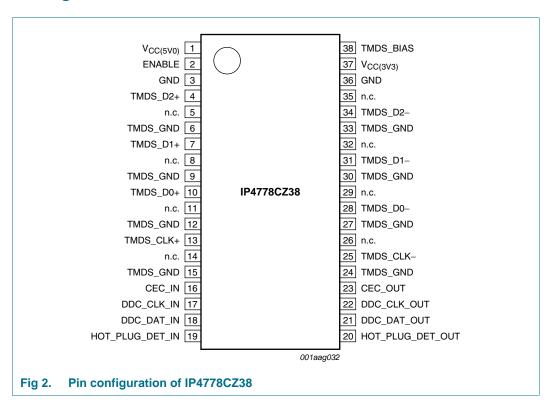

# 6. Pinning information

#### 6.1 Pinning

IP4778CZ38

All information provided in this document is subject to legal disclaimers.

© NXP B.V. 2011. All rights reserved.

# HDMI ESD protection, DDC buffering and hot plug control

# 6.2 Pin description

Table 2. Pin description

| Symbol               | Pin        |              | Description                                             |

|----------------------|------------|--------------|---------------------------------------------------------|

|                      | IP4778CZ38 | IP4778CZ38/V |                                                         |

| V <sub>CC(5V0)</sub> | 1          | 1            | supply voltage for DDC and hot plug circuits            |

| ENABLE               | 2          | 2            | enable for DDC and hot plug circuits                    |

| GND                  | 3          | 3            | ground for DDC, hot plug and CEC circuits[1]            |

| TMDS_D2+             | 4          | 4            | ESD protection TMDS channel D2+[2]                      |

| TMDS_GND             | 6          | 5            | ground for TMDS channel[1]                              |

| n.c.                 | 5          | 6            | not connected[2]                                        |

| TMDS_D1+             | 7          | 7            | ESD protection TMDS channel D1+[2]                      |

| TMDS_GND             | 9          | 8            | ground for TMDS channel[1]                              |

| n.c.                 | 8          | 9            | not connected[2]                                        |

| TMDS_D0+             | 10         | 10           | ESD protection TMDS channel D0+[2]                      |

| TMDS_GND             | 12         | 11           | ground for TMDS channel[1]                              |

| n.c.                 | 11         | 12           | not connected[2]                                        |

| TMDS_CLK+            | 13         | 13           | ESD protection TMDS channel CLK+[2]                     |

| TMDS_GND             | 15         | 14           | ground for TMDS channel[1]                              |

| n.c.                 | 14         | 15           | not connected[2]                                        |

| CEC_IN               | 16         | 16           | CEC signal input to system controller[3]                |

| DDC_CLK_IN           | 17         | 17           | DDC clock input to system controller[3]                 |

| DDC_DAT_IN           | 18         | 18           | DDC data input to system controller[3]                  |

| HOT_PLUG_DET_IN      | 19         | 19           | hot plug Detect input from system GPIO[3]               |

| HOT_PLUG_DET_OUT     | 20         | 20           | hot plug Detect output to HDMI connector <sup>[4]</sup> |

| DDC_DAT_OUT          | 21         | 21           | DDC data output to HDMI connector[4]                    |

| DDC_CLK_OUT          | 22         | 22           | DDC clock output to HDMI connector <sup>[4]</sup>       |

| CEC_OUT              | 23         | 23           | CEC signal output to HDMI connector[3]                  |

| TMDS_CLK-            | 25         | 24           | ESD protection TMDS channel CLK-[2]                     |

| TMDS_GND             | 24         | 25           | ground for TMDS channel[1]                              |

| n.c.                 | 26         | 26           | not connected[2]                                        |

| TMDS_D0-             | 28         | 27           | ESD protection TMDS channel D0-2                        |

| TMDS_GND             | 27         | 28           | ground for TMDS channel[1]                              |

| n.c.                 | 29         | 29           | not connected[2]                                        |

| TMDS_D1-             | 31         | 30           | ESD protection TMDS channel D1-2                        |

| TMDS_GND             | 30         | 31           | ground for TMDS channel[1]                              |

IP4778CZ38

All information provided in this document is subject to legal disclaimers.

© NXP B.V. 2011. All rights reserved.

#### **HDMI ESD protection, DDC buffering and hot plug control**

Table 2.

Pin description ...continued

| Symbol               | Pin        |              | Description                                                                                |

|----------------------|------------|--------------|--------------------------------------------------------------------------------------------|

|                      | IP4778CZ38 | IP4778CZ38/V |                                                                                            |

| n.c.                 | 32         | 32           | not connected <sup>[2]</sup>                                                               |

| TMDS_D2-             | 34         | 33           | ESD protection TMDS channel D2-[2]                                                         |

| TMDS_GND             | 33         | 34           | ground for TMDS channel[1]                                                                 |

| n.c.                 | 35         | 35           | not connected[2]                                                                           |

| GND                  | 36         | 36           | ground for DDC, hot plug and CEC circuits[1]                                               |

| V <sub>CC(3V3)</sub> | 37         | 37           | supply voltage for CEC circuit                                                             |

| TMDS_BIAS            | 38         | 38           | bias input for TMDS ESD protection. This pin must be connected to a 0.1 $\mu F$ capacitor. |

<sup>[1]</sup> Pins GND and TMDS\_GND are internally connected.

# 7. Limiting values

Table 3. Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134).

| Parameter                       | Conditions                                                                            | Min                                                                        | Max                                                                                                                                                                                                                                                           | Unit                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|---------------------------------|---------------------------------------------------------------------------------------|----------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| supply voltage                  |                                                                                       | GND -                                                                      | - 0.5 5.5                                                                                                                                                                                                                                                     | V                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| input voltage                   | at input pins                                                                         | GND -                                                                      | - 0.5 5.5                                                                                                                                                                                                                                                     | V                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| electrostatic discharge voltage | connector side pins (to ground);<br>IEC 61000-4-2, level 4                            | <u>[1]</u>                                                                 |                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                 | contact                                                                               | -8                                                                         | +8                                                                                                                                                                                                                                                            | kV                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                 | board side pins; IEC 61000-4-2, level 1                                               | [2]                                                                        |                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                 | contact                                                                               | -2                                                                         | +2                                                                                                                                                                                                                                                            | kV                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| total power dissipation         | DDC operating at 100 kHz                                                              | -                                                                          | 8                                                                                                                                                                                                                                                             | mW                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| storage temperature             |                                                                                       | -55                                                                        | +125                                                                                                                                                                                                                                                          | °C                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                 | supply voltage input voltage electrostatic discharge voltage  total power dissipation | supply voltage input voltage at input pins electrostatic discharge voltage | supply voltage input voltage at input pins GND - electrostatic discharge voltage  connector side pins (to ground); IEC 61000-4-2, level 4  contact -8  board side pins; IEC 61000-4-2, level 1  contact -2  total power dissipation  DDC operating at 100 kHz | supply voltage         GND - 0.5         5.5           input voltage         at input pins         GND - 0.5         5.5           electrostatic discharge voltage         connector side pins (to ground); IEC 61000-4-2, level 4         11         -8         +8           board side pins; IEC 61000-4-2, level 1         12         -2         +2           total power dissipation         DDC operating at 100 kHz         -         8 |

#### [1] Connector side pins:

${\sf TMDS\_D2+, TMDS\_D2-, TMDS\_D1+, TMDS\_D1-, TMDS\_D0+, TMDS\_D0-,}$

TMDS\_CLK+, TMDS\_CLK-,

CEC\_OUT,

DDC\_DAT\_OUT and DDC\_CLK\_OUT,

HOT\_PLUG\_DET\_OUT.

[2] Board side pins:

CEC\_IN,

$\ensuremath{\mathsf{DDC\_DAT\_IN}}$  and  $\ensuremath{\mathsf{DDC\_CLK\_IN}},$

${\sf HOT\_PLUG\_DET\_IN},$

ENABLE.

<sup>[2]</sup> This pin must always be connected to the IC pin located opposite via a PCB track to guarantee correct functionality; see Figure 15.

<sup>[3]</sup> V<sub>CC(3V3)</sub> referenced logic level in.

<sup>[4]</sup> V<sub>CC(5V0)</sub> referenced logic level out.

### **HDMI ESD protection, DDC buffering and hot plug control**

## 8. Static characteristics

Table 4. TMDS protection circuit

$T_{amb} = 25$  °C; unless otherwise specified.

| Symbol                       | Parameter                                   | Conditions                                                                                                             | Min          | Тур  | Max | Unit |

|------------------------------|---------------------------------------------|------------------------------------------------------------------------------------------------------------------------|--------------|------|-----|------|

| Zener diode                  |                                             |                                                                                                                        |              |      |     |      |

| $V_{BRzd}$                   | Zener diode breakdown voltage               | I = 1 mA                                                                                                               | 6            | -    | 9   | V    |

| R <sub>dyn</sub>             | dynamic resistance                          | I = 1 A; IEC 61000-4-5/9                                                                                               |              |      |     |      |

|                              |                                             | positive transient                                                                                                     | -            | 2.4  | -   | Ω    |

|                              |                                             | negative transient                                                                                                     | -            | 1.3  | -   | Ω    |

| Protection did               | ode                                         |                                                                                                                        |              |      |     |      |

| I <sub>bck</sub>             | back current                                | from pins TMDS_x to pin TMDS_BIAS;<br>$V_{CC(5V0)} = 0 \text{ V}; V_{CC(3V3)} = 0 \text{ V}$                           | -            | 0.1  | 5   | μΑ   |

| I <sub>L(r)</sub>            | reverse leakage current                     | $V_{I} = 3.0 \text{ V}$                                                                                                | -            | 1    | -   | μΑ   |

| $V_{F}$                      | forward voltage                             |                                                                                                                        | -            | 0.7  | -   | V    |

| $V_{CL(ch)trt(pos)}$         | positive transient channel clamping voltage | V <sub>ESD</sub> = 8 kV per IEC 61000-4-2; voltage 30 ns after trigger                                                 | <u>[1]</u> _ | 8    | -   | V    |

| TMDS channe                  | el: pins TMDS_x                             |                                                                                                                        |              |      |     |      |

| C <sub>ch(TMDS)</sub>        | TMDS channel capacitance                    | $V_{CC(5V0)} = 5 \text{ V}; f = 1 \text{ MHz}; V_{bias} = 2.5 \text{ V}$                                               | [2] _        | 0.7  | -   | pF   |

| $\Delta C_{\text{ch(TMDS)}}$ | TMDS channel capacitance difference         | $V_{CC(5V0)} = 5 \text{ V}; f = 1 \text{ MHz}; V_{bias} = 2.5 \text{ V}$                                               | [2] -        | 0.05 | -   | pF   |

| $C_{\text{ch(mutual)}}$      | mutual channel capacitance                  | between signal pin TMDS_x and pin n.c.; $V_{CC(5V0)} = 0 \text{ V}$ ; $f = 1 \text{ MHz}$ ; $V_{bias} = 2.5 \text{ V}$ | [2] _        | 0.07 | -   | pF   |

<sup>[1]</sup> This measurement is performed with a 0.1  $\mu F$  external capacitor on pin TMDS\_BIAS.

Table 5. DDC circuit

$V_{CC(3V3)} = 2.7 \text{ V to } 5.5 \text{ V}; V_{CC(5V0)} = 4.5 \text{ V to } 5.5 \text{ V}; \text{ GND} = 0 \text{ V}; T_{amb} = 25 ^{\circ}\text{C}; \text{ unless otherwise specified.}$

| Symbol               | Parameter                                          | Conditions                                                                                                                                         | Min | Тур | Max | Unit |

|----------------------|----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| Supplies             | pins V <sub>CC(5V0)</sub> and V <sub>CC(3V3)</sub> |                                                                                                                                                    |     |     |     |      |

| V <sub>CC(5V0)</sub> | supply voltage (5.0 V)                             |                                                                                                                                                    | 4.5 | 5.0 | 5.5 | V    |

| V <sub>CC(3V3)</sub> | supply voltage (3.3 V)                             |                                                                                                                                                    | 2.7 | 3.3 | 5.5 | V    |

| I <sub>CC(5V0)</sub> | supply current (5.0 V)                             | $V_{\text{CC(5V0)}} = 5.5 \text{ V};$<br>both channels HIGH:<br>DDC_DAT_OUT = $V_{\text{CC(5V0)}};$<br>DDC_CLK_OUT = $V_{\text{CC(5V0)}}$          | -   | 0.5 | 1.0 | mA   |

|                      |                                                    | $V_{\text{CC(5V0)}} = 5.5 \text{ V};$<br>both channels LOW:<br>DDC_DAT_IN = GND;<br>DDC_CLK_IN = GND;<br>DDC_DAT_OUT = open;<br>DDC_CLK_OUT = open | -   | 0.5 | 1.0 | mA   |

| I <sub>CC(3V3)</sub> | supply current (3.3 V)                             | no pull-up resistor connected to $V_{\text{CC(3V3)}}$                                                                                              | -   | -   | 0.1 | μΑ   |

IP4778CZ38

© NXP B.V. 2011. All rights reserved.

<sup>[2]</sup> This parameter is guaranteed by design.

### **HDMI ESD protection, DDC buffering and hot plug control**

Table 5.

DDC circuit ...continued

$V_{\text{CC}(3V3)} = 2.7 \text{ V to } 5.5 \text{ V}; V_{\text{CC}(5V0)} = 4.5 \text{ V to } 5.5 \text{ V}; \text{GND} = 0 \text{ V}; T_{amb} = 25 ^{\circ}\text{C}; \text{ unless otherwise specified.}$

| Symbol          | Parameter                    | Conditions                                         | Min                      | Тур | Max                      | Unit |

|-----------------|------------------------------|----------------------------------------------------|--------------------------|-----|--------------------------|------|

| Board si        | de: pins DDC_CLK_OUT and D   | DC_DAT_OUT                                         |                          |     |                          |      |

| Used as i       | input                        |                                                    |                          |     |                          |      |

| $V_{IH}$        | HIGH-level input voltage     |                                                    | $0.7 \times V_{CC(3V3)}$ | -   | 5.5                      | V    |

| V <sub>IL</sub> | LOW-level input voltage      |                                                    | -0.5                     | -   | $0.3 \times V_{CC(3V3)}$ | V    |

| I <sub>IL</sub> | LOW-level input current      | V <sub>I</sub> = 0.2 V                             | -                        | -   | 1                        | μΑ   |

| $V_{IK}$        | input clamping voltage       | $I_i = -18 \text{ mA}$                             | -                        | -   | -1.2                     | V    |

| ILI             | input leakage current        | V <sub>I</sub> = 3.6 V                             | -                        | -   | ±1                       | μΑ   |

| C <sub>i</sub>  | input capacitance            | $V_I = 3 V \text{ or } 0 V$                        |                          |     |                          |      |

|                 |                              | $V_{CC(3V3)} = 3.3 \text{ V}$                      | -                        | 8   | 10                       | pF   |

|                 |                              | $V_{CC(3V3)} = 3.0 \text{ V}$                      | -                        | 8   | 10                       | pF   |

| Used as         | output                       |                                                    |                          |     |                          |      |

| V <sub>OL</sub> | LOW-level output voltage     | $I_{OL}$ = 100 $\mu A$ or 6 mA                     | -                        | 200 | -                        | mV   |

| I <sub>OH</sub> | HIGH-level output current    | V <sub>O</sub> = 3.6 V                             | -                        | -   | 1                        | μΑ   |

| Co              | output capacitance           | $V_I = 3 V \text{ or } 0 V$                        |                          |     |                          |      |

|                 |                              | $V_{CC(3V3)} = 3.3 \text{ V}$                      | -                        | 8   | 10                       | pF   |

|                 |                              | $V_{CC(3V3)} = 3.0 \text{ V}$                      | -                        | 8   | 10                       | pF   |

| Connect         | or side: pins DDC_CLK_IN and | DDC_DAT_IN                                         |                          |     |                          |      |

| Used as i       | input                        |                                                    |                          |     |                          |      |

| V <sub>IH</sub> | HIGH-level input voltage     |                                                    | -                        | 410 | -                        | mV   |

| V <sub>IL</sub> | LOW-level input voltage      |                                                    | -                        | 400 | -                        | mV   |

| I <sub>IL</sub> | LOW-level input current      | DDC_DAT_OUT,<br>DDC_CLK_OUT, $V_I = 0.2 \text{ V}$ | -                        | -   | 10                       | μΑ   |

| V <sub>IK</sub> | input clamping voltage       | $I_{I} = -18 \text{ mA}$                           | -                        | -   | -1.2                     | V    |

| ILI             | input leakage current        | V <sub>I</sub> = 3.6 V                             | -                        | -   | ±1                       | μΑ   |

| Ci              | input capacitance            | $V_I = 3 V \text{ or } 0 V$                        |                          |     |                          |      |

|                 |                              | $V_{CC(3V3)} = 3.3 \text{ V}$                      | -                        | 7   | 9                        | pF   |

|                 |                              | $V_{CC(3V3)} = 3.0 \text{ V}$                      | -                        | 7   | 9                        | pF   |

| Used as         | output                       |                                                    |                          |     |                          |      |

| V <sub>OL</sub> | LOW-level output voltage     | $I_{OL}$ = 100 $\mu A$ or 3 mA                     | -                        | 700 | -                        | mV   |

| I <sub>OH</sub> | HIGH-level output current    | $V_0 = 3.6 \text{ V}$                              | -                        | -   | 1                        | μΑ   |

| Co              | output capacitance           | $V_I = 3 V \text{ or } 0 V$                        |                          |     |                          |      |

|                 |                              | $V_{CC(3V3)} = 3.3 \text{ V}$                      | -                        | 8   | 10                       | pF   |

|                 |                              | $V_{CC(3V3)} = 3.0 \text{ V}$                      | -                        | 8   | 10                       | pF   |

### **HDMI ESD protection, DDC buffering and hot plug control**

Table 6. CEC circuit

$V_{CC(3V3)} = 2.7 \text{ V to } 5.5 \text{ V; } \text{GND} = 0 \text{ V; } T_{amb} = 25 \text{ °C; } \text{unless otherwise specified.}$

| Symbol                        | Parameter                                               | Conditions                                                                                       | Min          | Тур  | Max | Unit  |

|-------------------------------|---------------------------------------------------------|--------------------------------------------------------------------------------------------------|--------------|------|-----|-------|

| Board side: in                | put pin CEC_IN                                          |                                                                                                  |              |      |     |       |

| C <sub>I(ch-GND)(levsh)</sub> | level shifting input capacitance from channel to ground | $V_{CC(3V3)} = 0 \text{ V; } f = 1 \text{ MHz;}$<br>$V_{bias} = 2.5 \text{ V}$                   | <u>[1]</u> _ | 12   | 16  | pF    |

| SR <sub>r</sub>               | rising slew rate                                        | V <sub>I</sub> > 1.8 V                                                                           | -            | 10   | -   | mV/μs |

| N-FET                         |                                                         |                                                                                                  |              |      |     |       |

| $\Delta V_{on}$               | on-state voltage drop                                   | N-FET state = on;<br>$V_{CC(3V3)} = 2.5 \text{ V}; V_S = \text{GND};$<br>$I_{DS} = 3 \text{ mA}$ | [2] -        | 125  | 140 | mV    |

| Connector sid                 | e: output pin CEC_OUT                                   |                                                                                                  |              |      |     |       |

| ILI                           | input leakage current                                   |                                                                                                  | -1           | +0.1 | +1  | μΑ    |

| R <sub>dyn</sub>              | dynamic resistance                                      | I = 1 A; IEC 61000-4-5/9                                                                         |              |      |     |       |

|                               |                                                         | positive transient                                                                               | -            | 2.4  | -   | Ω     |

|                               |                                                         | negative transient                                                                               | -            | 1.3  | -   | Ω     |

| V <sub>CL(ch)trt(pos)</sub>   | positive transient channel clamping voltage             | $V_{ESD}$ = 8 kV per IEC 61000-4-2;<br>voltage 30 ns after trigger;<br>$T_{amb}$ = 25 °C         | [3] _        | 8    | -   | V     |

<sup>[1]</sup> This parameter is guaranteed by design.

Table 7. Enable circuit

$V_{\text{CC}(3V3)}$  = 2.7 V to 5.5 V; GND = 0 V;  $T_{amb}$  = 25 °C; unless otherwise specified.

| Symbol          | Parameter                | Conditions                                              | Min                      | Тур  | Max                      | Unit |

|-----------------|--------------------------|---------------------------------------------------------|--------------------------|------|--------------------------|------|

| Board side      | e: input pin ENABLE[1]   |                                                         |                          |      |                          |      |

| $V_{IH}$        | HIGH-level input voltage | HIGH = enable                                           | $0.7 \times V_{CC(3V3)}$ | -    | $V_{CC(5V0)} + 0.5$      | V    |

| V <sub>IL</sub> | LOW-level input voltage  | LOW = disable                                           | -0.5                     | -    | $0.3 \times V_{CC(3V3)}$ | V    |

| I <sub>IL</sub> | LOW-level input current  | $V_I = 0.2 \text{ V};$<br>$V_{CC(3V3)} = 5.5 \text{ V}$ | -                        | 10   | -                        | μΑ   |

| ILI             | input leakage current    |                                                         | -1                       | +0.1 | +1                       | μΑ   |

| C <sub>i</sub>  | input capacitance        | $V_I = 3 V \text{ or } 0 V$                             | -                        | 3    | 7                        | pF   |

<sup>[1]</sup> The ENABLE pin has to be connected permanently to  $V_{CC(3V3)}$  if no enable control is needed.

<sup>[2]</sup> For level shifting N-FET.

<sup>[3]</sup> This measurement is performed with a 0.1  $\mu\text{F}$  external capacitor on pin TMDS\_BIAS.

#### **HDMI ESD** protection, DDC buffering and hot plug control

Table 8. hot plug control circuit

$V_{\text{CC}(5V0)} = 4.5 \text{ V}$  to 5.5 V;  $V_{\text{CC}(3V3)} = 2.7 \text{ V}$  to 5.5 V; GND = 0 V;  $T_{amb} = 25 \,^{\circ}\text{C}$ ; unless otherwise specified.

| ( /             | ( /                       |                                                    |                          |      |                          |      |

|-----------------|---------------------------|----------------------------------------------------|--------------------------|------|--------------------------|------|

| Symbol          | Parameter                 | Conditions                                         | Min                      | Тур  | Max                      | Unit |

| Board si        | de: input pin HOT_PLUG_   | DET_IN                                             |                          |      |                          |      |

| $V_{IH}$        | HIGH-level input voltage  | HIGH = hot plug off                                | $0.7 \times V_{CC(3V3)}$ | -    | $V_{CC(5V0)} + 0.5$      | V    |

| $V_{IL}$        | LOW-level input voltage   | LOW = hot plug on                                  | -0.5                     | -    | $0.3 \times V_{CC(3V3)}$ | V    |

| I <sub>IL</sub> | LOW-level input current   | $V_1 = 2.0 \text{ V}; V_{CC(3V3)} = 5.5 \text{ V}$ | -                        | 10   | -                        | μΑ   |

| I <sub>LI</sub> | input leakage current     |                                                    | -1                       | +0.1 | +1                       | μΑ   |

| C <sub>i</sub>  | input capacitance         | $V_I = 3 V \text{ or } 0 V$                        | -                        | 4    | 7                        | pF   |

| Connect         | or side: output pin HOT_F | PLUG_DET_OUT                                       |                          |      |                          |      |

| I <sub>LI</sub> | input leakage current     |                                                    | -1                       | +0.1 | +1                       | μΑ   |

| Ci              | input capacitance         | $V_I = 3 \text{ V or } 0 \text{ V}$                | -                        | 6    | 7                        | pF   |

| Von             | on-state voltage          | I <sub>I</sub> = 5 mA                              | -                        | 400  | -                        | mV   |

# 9. Dynamic characteristics

#### Table 9. DDC circuits

$V_{CC(3V3)} = 2.7 \text{ V to } 5.5 \text{ V}; V_{CC(5V0)} = 4.5 \text{ V to } 5.5 \text{ V}; GND = 0 \text{ V}; T_{amb} = 25 ^{\circ}C; unless otherwise specified.}$

| Symbol           | Parameter                        | Conditions                                        |     | Min | Тур | Max | Unit |

|------------------|----------------------------------|---------------------------------------------------|-----|-----|-----|-----|------|

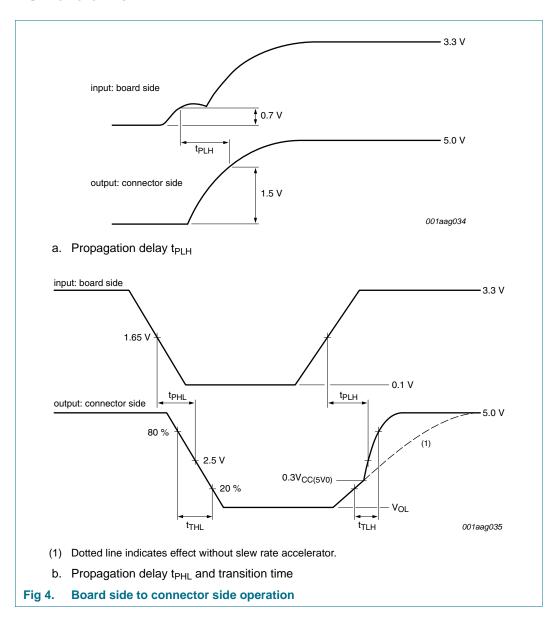

| Board side       | to connector side; see Figure 4  |                                                   |     |     |     |     |      |

| Pins DDC_        | CLK_IN to DDC_CLK_OUT and DDC    | _DAT_IN to DDC_DAT_OUT                            |     |     |     |     |      |

| t <sub>PLH</sub> | LOW to HIGH propagation delay    |                                                   | [1] | 150 | 270 | 300 | ns   |

| t <sub>PHL</sub> | HIGH to LOW propagation delay    |                                                   | [1] | 125 | 210 | 225 | ns   |

| Pins DDC_        | CLK_OUT and DDC_DAT_OUT          |                                                   |     |     |     |     |      |

| t <sub>TLH</sub> | LOW to HIGH transition time      | $R_L = 1.35 \text{ k}\Omega; C_L = 50 \text{ pF}$ |     | 90  | 110 | 130 | ns   |

| t <sub>THL</sub> | HIGH to LOW transition time      |                                                   | [1] | 2   | 3   | 5   | ns   |

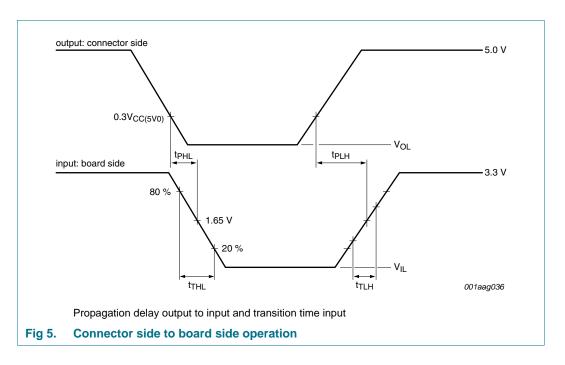

| Connector        | side to board side; see Figure 5 |                                                   |     |     |     |     |      |

| Pins DDC_        | CLK_OUT to DDC_CLK_IN and DDC    | _DAT_OUT to DDC_DAT_IN                            |     |     |     |     |      |

| t <sub>PLH</sub> | LOW to HIGH propagation delay    |                                                   |     | 90  | 110 | 130 | ns   |

| t <sub>PHL</sub> | HIGH to LOW propagation delay    |                                                   | [1] | 20  | 30  | 40  | ns   |

| Pins DDC_        | CLK_IN and DDC_DAT_IN            |                                                   |     |     |     |     |      |

| t <sub>TLH</sub> | LOW to HIGH transition time      |                                                   |     | 100 | 120 | 140 | ns   |

| t <sub>THL</sub> | HIGH to LOW transition time      |                                                   | [1] | 2   | 3   | 5   | ns   |

| Enable: pi       | n ENABLE                         |                                                   |     |     |     |     |      |

| t <sub>su</sub>  | set-up time                      | pin ENABLE = HIGH before start condition          | [2] | 100 | -   | -   | ns   |

| t <sub>h</sub>   | hold time                        | pin ENABLE = HIGH after stop condition            | [2] | 100 | -   | -   | ns   |

<sup>[1]</sup> Typical values were measured with  $V_{CC(3V3)} = 3.3 \text{ V}$ ;  $V_{CC(5V0)} = 5.0 \text{ V}$ .

<sup>[2]</sup> Pin ENABLE should only change state when the DDC bus is in an idle state.

### **HDMI ESD protection, DDC buffering and hot plug control**

#### 9.1 AC Waveforms

#### HDMI ESD protection, DDC buffering and hot plug control

## 10. Application information

#### 10.1 TMDS

To protect the TMDS lines and also to comply with the impedance requirements of the HDMI specification, the IP4778CZ38 provides ESD protection with a low capacitive load. The dominant value for the TMDS line impedance is the capacitive load to ground. The IP4778CZ38 has a capacitive load of only 0.7 pF.

#### **HDMI ESD protection, DDC buffering and hot plug control**

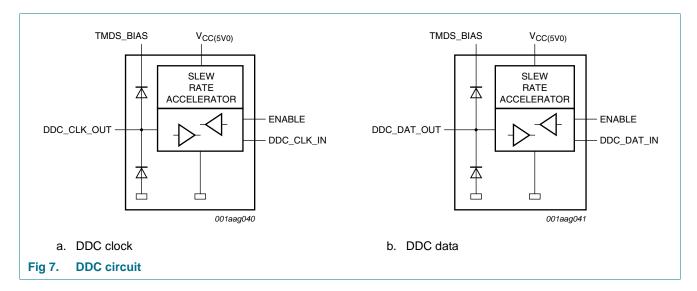

#### 10.2 DDC circuit

The DDC-bus circuit contains full capacitive decoupling between the HDMI connector and the DDC-bus lines on the PCB. The capacitive decoupling ensures that the maximum capacitive load is within the 50 pF maximum of the HDMI specification.

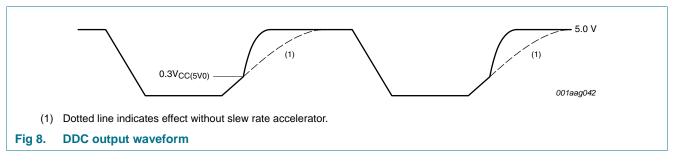

The slew rate accelerator supports high capacitive load on the HDMI cable side. Various HDMI cable suppliers produce low-cost and long (typically 25 m) HDMI cables with a capacitive load of up to 6 nF.

The slew rate accelerator boosts the DDC signal independent of which side of the bus is releasing the signal. The DDC module provides a level shifting and a multiplex option which is enabled by the ENABLE signal.

#### **HDMI ESD protection, DDC buffering and hot plug control**

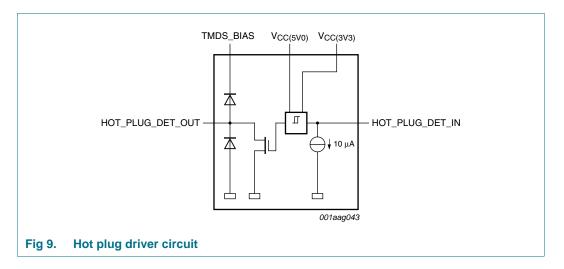

## 10.3 Hot plug driver circuit

The IP4778CZ38 includes a hot plug driver circuit that simplifies the hot plug application. The circuit can be connected directly to GPIO pins.

The hot plug control input is actively pulled LOW to ensure that at system standby or start-up, the hot plug signal is HIGH even if a GPIO pin is in a 3-state condition.

For correct CEC handling, it is essential that the hot plug signal is at HIGH-level in Standby mode. The HDMI source requires a hot plug signal so that it can read out the EDID information to initiate a proper start-up CEC sequence.

#### **HDMI ESD protection, DDC buffering and hot plug control**

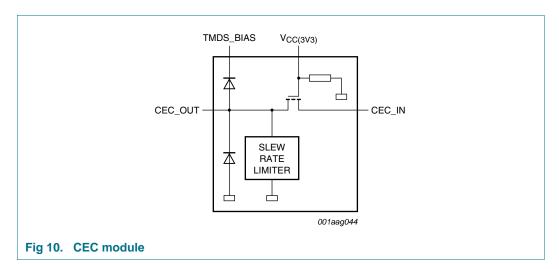

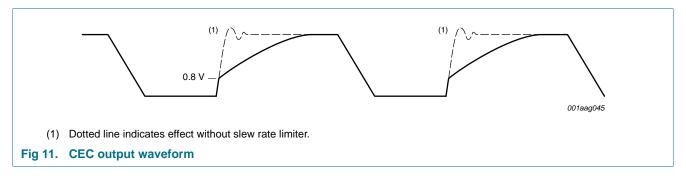

#### 10.4 CEC

The CEC signal can generate distortions caused by signal ringing in a 1 kHz domain. The CEC slew rate limiter ensures that a signal does not ring independently of the CEC slave that is releasing the signal.

A MOSFET transistor implements the backdrive protection which blocks signals during a power-down state.

The slew rate of the CEC bus is controlled by a slew rate that is defined independently of the load (ohmic and capacitive) at the CEC bus.

## **HDMI ESD protection, DDC buffering and hot plug control**

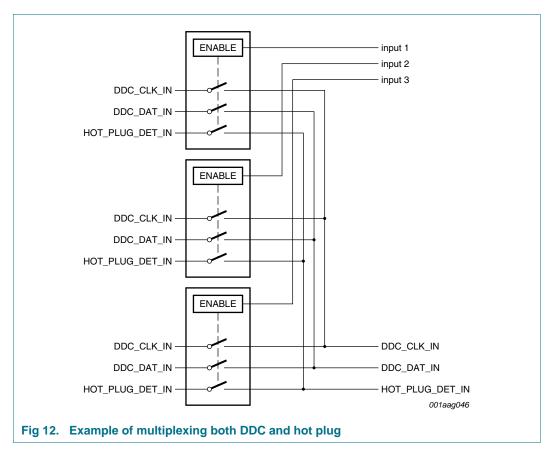

#### 10.5 Multiplexing

Up to four HDMI interface ports can exist on an HDMI receiver. The DDC and hot plug signals are both needed to support various HDMI connectors, multiplexing and switching of the TMDS lines. The CEC bus has to remain functional in order to detect activity such as a brake in support.

The combination of a TMDS switch and the IP4778CZ38 is a cost-effective way to attain various HDMI ports by using a single input HDMI receiver device. The ENABLE signal activates the HDMI DDC and hot plug lines at the port that is selected by the system controller.

#### **HDMI ESD protection, DDC buffering and hot plug control**

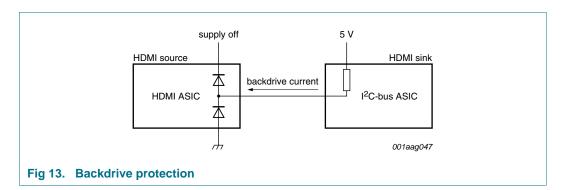

## 10.6 Backdrive protection

The HDMI contains various signals which can partly supply current into an HDMI device that is powered down.

Typically, the DDC lines and the CEC signals can force 5 V into the switched-off device. The IP4778CZ38 ensures that at power-down, the critical signals are blocked to prevent any damage to the HDMI sink and HDMI source.

#### **HDMI ESD protection, DDC buffering and hot plug control**

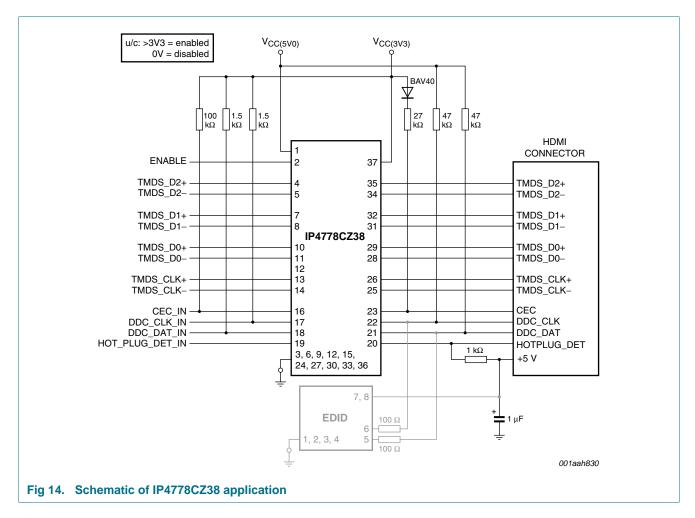

## 10.7 Application schematic

<u>Figure 14</u> shows a typical application where the IP4778CZ38 provides a simplified interface to an HDMI port. This application requires only a few external components to adapt the HDMI port to the parameters of the HDMI receiver device or HDMI multiplexer.

#### **HDMI ESD protection, DDC buffering and hot plug control**

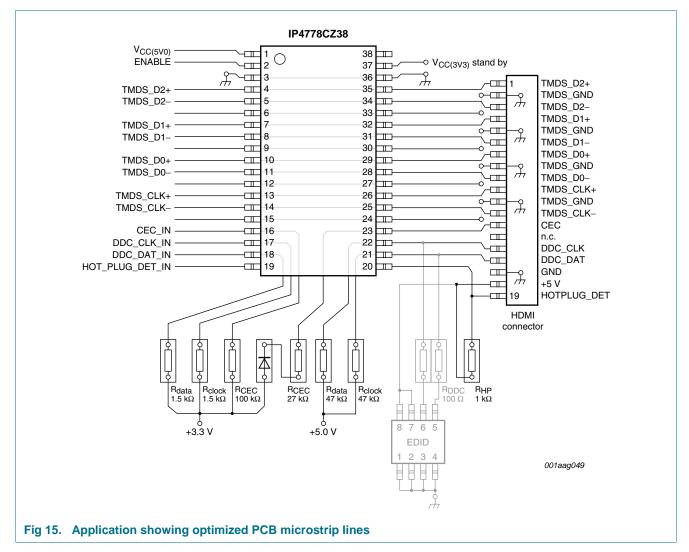

#### 10.8 Typical application

This application ensures that the EDID (stored in the EEPROM) can be read out in Standby mode, even if long cables are used, to guarantee correct CEC wake-up handling. To wake up the system from Standby to normal operation, the HDMI source has to first read the EDID in order to hand over the port ID via the CEC protocol. This ensures that the HDMI starts up and switches to the correct HDMI port to display the HDMI source which initiates the CEC wake-up sequence.

The CEC bus is enabled by activating the  $V_{CC(3V3)}$  standby supply.

The RF routing optimized pin position variant allows optimum design layout of the RF routing microstrips to ensure that the impedance of the TMDS lines remain within the specification limits. Part of the microstrips comprise a solid ground plane which is located beneath the device.

### **HDMI ESD protection, DDC buffering and hot plug control**

# 11. Test information

Fig 16. Test circuit for DDC and CEC lines

Table 10. Test data

| Test      | $R_L$           | C <sub>L</sub> | V <sub>CC</sub>      |

|-----------|-----------------|----------------|----------------------|

| DDC lines | 1.35 k $\Omega$ | 50 pF          | V <sub>CC(5V0)</sub> |

| CEC line  | 27 kΩ           | 50 pF          | V <sub>CC(3V3)</sub> |

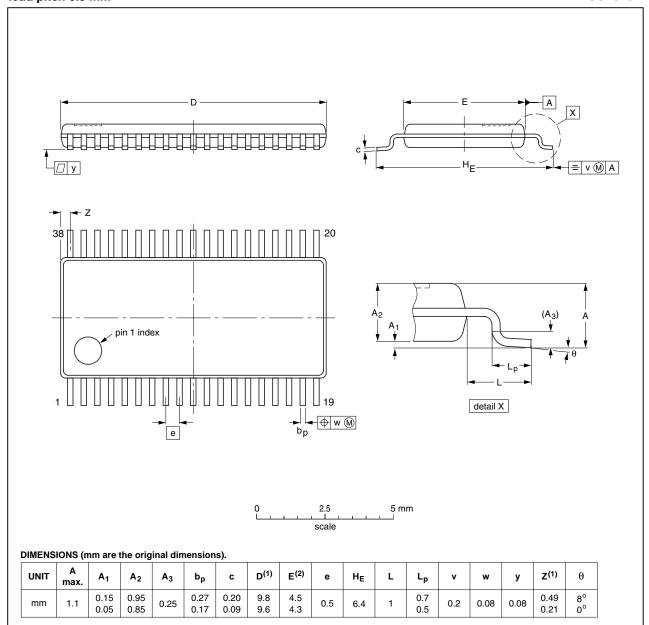

# 12. Package outline

# TSSOP38: plastic thin shrink small outline package; 38 leads; body width 4.4 mm; lead pitch 0.5 mm

SOT510-1

#### Notes

- 1. Plastic or metal protrusions of 0.15 mm maximum per side are not included.

- 2. Plastic interlead protrusions of 0.25 mm maximum per side are not included.

|          | REFERENCES |  |            | ISSUE DATE                        |

|----------|------------|--|------------|-----------------------------------|

| EC JEDEC | JEITA      |  | PROJECTION | ISSUE DATE                        |

| MO-153   |            |  |            | <del>-03-02-18-</del><br>05-11-02 |

|          |            |  |            | EC JEDEC JEHA                     |

Fig 17. Package outline SOT510-1 (TSSOP38)

IP4778CZ38 All information provided in this document is subject to legal disclaimers.

© NXP B.V. 2011. All rights reserved.

#### **HDMI ESD protection, DDC buffering and hot plug control**

## 13. Soldering of SMD packages

This text provides a very brief insight into a complex technology. A more in-depth account of soldering ICs can be found in Application Note *AN10365* "Surface mount reflow soldering description".

#### 13.1 Introduction to soldering

Soldering is one of the most common methods through which packages are attached to Printed Circuit Boards (PCBs), to form electrical circuits. The soldered joint provides both the mechanical and the electrical connection. There is no single soldering method that is ideal for all IC packages. Wave soldering is often preferred when through-hole and Surface Mount Devices (SMDs) are mixed on one printed wiring board; however, it is not suitable for fine pitch SMDs. Reflow soldering is ideal for the small pitches and high densities that come with increased miniaturization.

#### 13.2 Wave and reflow soldering

Wave soldering is a joining technology in which the joints are made by solder coming from a standing wave of liquid solder. The wave soldering process is suitable for the following:

- Through-hole components

- Leaded or leadless SMDs, which are glued to the surface of the printed circuit board

Not all SMDs can be wave soldered. Packages with solder balls, and some leadless packages which have solder lands underneath the body, cannot be wave soldered. Also, leaded SMDs with leads having a pitch smaller than ~0.6 mm cannot be wave soldered, due to an increased probability of bridging.

The reflow soldering process involves applying solder paste to a board, followed by component placement and exposure to a temperature profile. Leaded packages, packages with solder balls, and leadless packages are all reflow solderable.

Key characteristics in both wave and reflow soldering are:

- · Board specifications, including the board finish, solder masks and vias

- · Package footprints, including solder thieves and orientation

- The moisture sensitivity level of the packages

- Package placement

- Inspection and repair

- Lead-free soldering versus SnPb soldering

#### 13.3 Wave soldering

Key characteristics in wave soldering are:

- Process issues, such as application of adhesive and flux, clinching of leads, board transport, the solder wave parameters, and the time during which components are exposed to the wave

- Solder bath specifications, including temperature and impurities

## **HDMI ESD protection, DDC buffering and hot plug control**

## 13.4 Reflow soldering

Key characteristics in reflow soldering are:

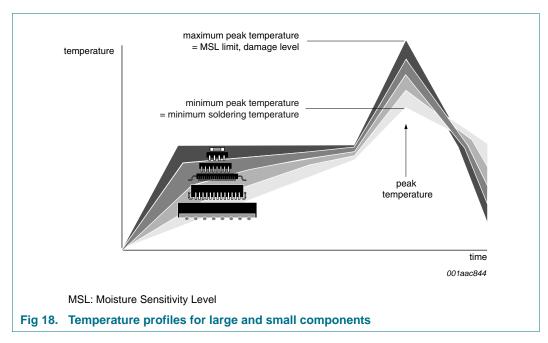

- Lead-free versus SnPb soldering; note that a lead-free reflow process usually leads to higher minimum peak temperatures (see <u>Figure 18</u>) than a SnPb process, thus reducing the process window

- Solder paste printing issues including smearing, release, and adjusting the process window for a mix of large and small components on one board

- Reflow temperature profile; this profile includes preheat, reflow (in which the board is heated to the peak temperature) and cooling down. It is imperative that the peak temperature is high enough for the solder to make reliable solder joints (a solder paste characteristic). In addition, the peak temperature must be low enough that the packages and/or boards are not damaged. The peak temperature of the package depends on package thickness and volume and is classified in accordance with Table 11 and 12

Table 11. SnPb eutectic process (from J-STD-020C)

| Package thickness (mm) | Package reflow temperature (°C) |       |  |

|------------------------|---------------------------------|-------|--|

|                        | Volume (mm³)                    |       |  |

|                        | < 350                           | ≥ 350 |  |

| < 2.5                  | 235                             | 220   |  |

| ≥ 2.5                  | 220                             | 220   |  |

Table 12. Lead-free process (from J-STD-020C)

| Package thickness (mm) | Package reflow temperature (°C) |             |        |  |

|------------------------|---------------------------------|-------------|--------|--|

|                        | Volume (mm³)                    |             |        |  |

|                        | < 350                           | 350 to 2000 | > 2000 |  |

| < 1.6                  | 260                             | 260         | 260    |  |

| 1.6 to 2.5             | 260                             | 250         | 245    |  |

| > 2.5                  | 250                             | 245         | 245    |  |

Moisture sensitivity precautions, as indicated on the packing, must be respected at all times.

Studies have shown that small packages reach higher temperatures during reflow soldering, see Figure 18.

Downloaded from Arrow.com.

#### **HDMI ESD** protection, DDC buffering and hot plug control

For further information on temperature profiles, refer to Application Note *AN10365* "Surface mount reflow soldering description".

### 14. Abbreviations

Table 13. Abbreviations

| Tubic for Abbrotiations |                                                     |

|-------------------------|-----------------------------------------------------|

| Acronym                 | Description                                         |

| CEC                     | Consumer Electronics Control                        |

| DDC                     | Data Display Channel                                |

| DVD                     | Digital Video Disk                                  |

| DVI                     | Digital Video Interface                             |

| EDID                    | Extended Display Identification Data                |

| EEPROM                  | Electrically Erasable Programmable Read-Only Memory |

| ESD                     | ElectroStatic Discharge                             |

| FET                     | Field-Effect Transistor                             |

| GPIO                    | General Purpose Input/Output                        |

| HDMI                    | High-Definition Multimedia Interface                |

| MOSFET                  | Metal Oxide Semiconductor Field Effect Transistor   |

| RoHS                    | Restriction of Hazardous Substances                 |

| TMDS                    | Transition Minimized Differential Signaling         |

|                         |                                                     |

# 15. Glossary

**HDMI sink** — Device which receives HDMI signals e.g. a TV set.

**HDMI source** — Device which transmit HDMI signal e.g. a DVD player.

# HDMI ESD protection, DDC buffering and hot plug control

# 16. Revision history

#### Table 14. Revision history

| Document ID    | Release date                                                    | Data sheet status             | Change notice | Supersedes     |

|----------------|-----------------------------------------------------------------|-------------------------------|---------------|----------------|

| IP4778CZ38 v.3 | 20110331                                                        | Product data sheet            | -             | IP4778CZ38 v.2 |

| Modifications: | Section 1 "G                                                    | eneral description": updated. |               |                |

|                | <ul> <li>Section 2 "Features and benefits": updated.</li> </ul> |                               |               |                |

|                | <ul> <li><u>Section 14 "Abbreviations"</u>: updated.</li> </ul> |                               |               |                |

|                | <ul><li>Section 17 "I</li></ul>                                 | Legal information": updated.  |               |                |

| IP4778CZ38 v.2 | 20090212                                                        | Product data sheet            | -             | IP4778CZ38 v.1 |

| IP4778CZ38 v.1 | 20080410                                                        | Objective data sheet          | -             | -              |

#### **HDMI ESD protection, DDC buffering and hot plug control**

## 17. Legal information

#### 17.1 Data sheet status

| Document status[1][2]          | Product status[3] | Definition                                                                            |

|--------------------------------|-------------------|---------------------------------------------------------------------------------------|

| Objective [short] data sheet   | Development       | This document contains data from the objective specification for product development. |

| Preliminary [short] data sheet | Qualification     | This document contains data from the preliminary specification.                       |

| Product [short] data sheet     | Production        | This document contains the product specification.                                     |

- [1] Please consult the most recently issued document before initiating or completing a design.

- [2] The term 'short data sheet' is explained in section "Definitions"

- [3] The product status of device(s) described in this document may have changed since this document was published and may differ in case of multiple devices. The latest product status information is available on the Internet at URL http://www.nxp.com.

#### 17.2 Definitions

Draft — The document is a draft version only. The content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included herein and shall have no liability for the consequences of use of such information.

Short data sheet — A short data sheet is an extract from a full data sheet with the same product type number(s) and title. A short data sheet is intended for quick reference only and should not be relied upon to contain detailed and full information. For detailed and full information see the relevant full data sheet, which is available on request via the local NXP Semiconductors sales office. In case of any inconsistency or conflict with the short data sheet, the full data sheet shall prevail.

**Product specification** — The information and data provided in a Product data sheet shall define the specification of the product as agreed between NXP Semiconductors and its customer, unless NXP Semiconductors and customer have explicitly agreed otherwise in writing. In no event however, shall an agreement be valid in which the NXP Semiconductors product is deemed to offer functions and qualities beyond those described in the Product data sheet.

#### 17.3 Disclaimers

Limited warranty and liability — Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information.

In no event shall NXP Semiconductors be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation - lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory.

Notwithstanding any damages that customer might incur for any reason whatsoever, NXP Semiconductors' aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the *Terms and conditions of commercial sale* of NXP Semiconductors.

Right to make changes — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

**Suitability for use** — NXP Semiconductors products are not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or

malfunction of an NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental damage. NXP Semiconductors accepts no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

**Applications** — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

Customers are responsible for the design and operation of their applications and products using NXP Semiconductors products, and NXP Semiconductors accepts no liability for any assistance with applications or customer product design. It is customer's sole responsibility to determine whether the NXP Semiconductors product is suitable and fit for the customer's applications and products planned, as well as for the planned application and use of customer's third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products.

NXP Semiconductors does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer's applications or products, or the application or use by customer's third party customer(s). Customer is responsible for doing all necessary testing for the customer's applications and products using NXP Semiconductors products in order to avoid a default of the applications and the products or of the application or use by customer's third party customer(s). NXP does not accept any liability in this respect.

Limiting values — Stress above one or more limiting values (as defined in the Absolute Maximum Ratings System of IEC 60134) will cause permanent damage to the device. Limiting values are stress ratings only and (proper) operation of the device at these or any other conditions above those given in the Recommended operating conditions section (if present) or the Characteristics sections of this document is not warranted. Constant or repeated exposure to limiting values will permanently and irreversibly affect the quality and reliability of the device.

Terms and conditions of commercial sale — NXP Semiconductors products are sold subject to the general terms and conditions of commercial sale, as published at <a href="http://www.nxp.com/profile/terms">http://www.nxp.com/profile/terms</a>, unless otherwise agreed in a valid written individual agreement. In case an individual agreement is concluded only the terms and conditions of the respective agreement shall apply. NXP Semiconductors hereby expressly objects to applying the customer's general terms and conditions with regard to the purchase of NXP Semiconductors products by customer.

No offer to sell or license — Nothing in this document may be interpreted or construed as an offer to sell products that is open for acceptance or the grant, conveyance or implication of any license under any copyrights, patents or other industrial or intellectual property rights.

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from national authorities.

IP4778CZ38

All information provided in this document is subject to legal disclaimers.

© NXP B.V. 2011. All rights reserved.

### **HDMI ESD** protection, DDC buffering and hot plug control

**Quick reference data** — The Quick reference data is an extract of the product data given in the Limiting values and Characteristics sections of this document, and as such is not complete, exhaustive or legally binding.

Non-automotive qualified products — Unless this data sheet expressly states that this specific NXP Semiconductors product is automotive qualified, the product is not suitable for automotive use. It is neither qualified nor tested in accordance with automotive testing or application requirements. NXP Semiconductors accepts no liability for inclusion and/or use of non-automotive qualified products in automotive equipment or applications.

In the event that customer uses the product for design-in and use in automotive applications to automotive specifications and standards, customer (a) shall use the product without NXP Semiconductors' warranty of the product for such automotive applications, use and specifications, and (b) whenever customer uses the product for automotive applications beyond NXP Semiconductors' specifications such use shall be solely at customer's own risk, and (c) customer fully indemnifies NXP Semiconductors for any

liability, damages or failed product claims resulting from customer design and use of the product for automotive applications beyond NXP Semiconductors' standard warranty and NXP Semiconductors' product specifications.

#### 17.4 Licenses

#### Purchase of NXP ICs with HDMI technology

Use of an NXP IC with HDMI technology in equipment that complies with the HDMI standard requires a license from HDMI Licensing LLC, 1060 E. Arques Avenue Suite 100, Sunnyvale CA 94085, USA, e-mail: admin@hdmi.org.

#### 17.5 Trademarks

Notice: All referenced brands, product names, service names and trademarks are the property of their respective owners.

## 18. Contact information

For more information, please visit: <a href="http://www.nxp.com">http://www.nxp.com</a>

For sales office addresses, please send an email to: salesaddresses@nxp.com

IP4778CZ38 **NXP Semiconductors HDMI ESD protection, DDC buffering and hot plug control**

### 19. Contents

| 1            | General description       | . 1 |

|--------------|---------------------------|-----|

| 2            | Features and benefits     | . 1 |

| 3            | Applications              | . 2 |

| 4            | Ordering information      | . 2 |

| 5            | Functional diagram        | . 3 |

| 6            | Pinning information       | . 4 |

| 6.1          | Pinning                   | . 4 |

| 6.2          | Pin description           | . 5 |

| 7            | Limiting values           | . 6 |

| 8            | Static characteristics    | . 7 |

| 9            | Dynamic characteristics   | 10  |

| 9.1          | AC Waveforms              | 11  |

| 10           | Application information   | 12  |

| 10.1         | TMDS                      | 12  |

| 10.2         | DDC circuit               | 13  |

| 10.3         | Hot plug driver circuit   | 14  |

| 10.4         | CEC                       | 15  |

| 10.5         | Multiplexing              | 16  |

| 10.6         | Backdrive protection      | 17  |

| 10.7         | Application schematic     | 18  |

| 10.8         | Typical application       | 19  |

| 11           | Test information          |     |

| 12           | Package outline           |     |

| 13           | Soldering of SMD packages |     |

| 13.1         | Introduction to soldering |     |

| 13.2         | Wave and reflow soldering |     |

| 13.3         | Wave soldering            |     |

| 13.4         | Reflow soldering          |     |

| 14           | Abbreviations             |     |

| 15           | Glossary                  |     |

| 16           | Revision history          |     |

| 17           | Legal information         |     |

| 17.1         | Data sheet status         |     |

| 17.2         | Definitions               |     |

| 17.3         | Disclaimers               |     |

| 17.4<br>17.5 | Licenses                  |     |

| _            | Trademarks                |     |

| 18           | Contact information       |     |

| 40           | Cantanta                  | 20  |

Please be aware that important notices concerning this document and the product(s) described herein, have been included in section 'Legal information'.

© NXP B.V. 2011.

All rights reserved.

For more information, please visit: http://www.nxp.com For sales office addresses, please send an email to: salesaddresses@nxp.com

Date of release: 31 March 2011 Document identifier: IP4778CZ38