# 88W8987 SDS

2.4/5 GHz Dual-band 1x1 Wi-Fi 5 (802.11ac) and Bluetooth 5.2 Solution

Rev. 3 — 15 September 2021

Product short data sheet

### 1 Product overview

The 88W8987 is a highly integrated Wi-Fi (2.4/5 GHz) and Bluetooth single-chip solution, specifically designed to support the speed, reliability, and quality requirements of next generation Very High Throughput (VHT) products.

The System-on-Chip (SoC) provides both simultaneous and independent operation of the following:

- IEEE 802.11ac (Wave 2), 1x1 with data rates up to MCS9 (433 Mbit/s)

- Bluetooth 5.2 (includes Bluetooth Low Energy (LE))

The SoC also provides:

- Bluetooth Classic and Bluetooth LE dual (Smart Ready) operation

- Wi-Fi indoor location positioning (802.11mc)

For security, the device supports high performance 802.11i security standards through implementation of the Advanced Encryption Standard (AES)/Counter Mode CBC-MAC Protocol (CCMP), AES/Galois/Counter Mode Protocol (GCMP), AES/Cipher-Based Message Authentication Code (CMAC), and WLAN Authentication and Privacy Infrastructure (WAPI) security mechanisms.

For video, voice, and multimedia applications, 802.11e Quality of Service (QoS) is supported. The device also supports 802.11h Dynamic Frequency Selection (DFS) for detecting radar pulses when operating in the 5 GHz range.

Host interfaces include SDIO 3.0 and high-speed UART interfaces for connecting Wi-Fi and Bluetooth technologies to the host processor.

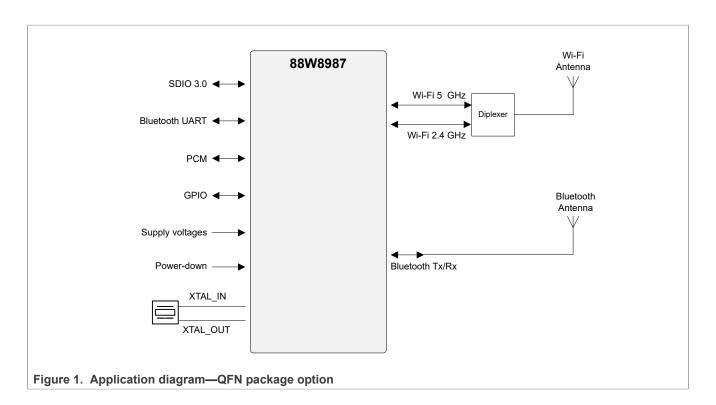

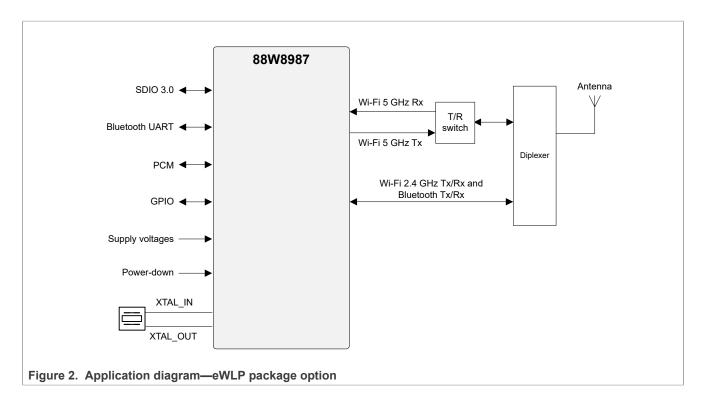

The device is designed with two front-end configurations to accommodate Wi-Fi and Bluetooth on either separate or shared paths:

- 2-antenna configuration—1x1 Wi-Fi and Bluetooth on separate paths (QFN)

- 1-antenna configuration—1x1 Wi-Fi and Bluetooth on shared paths (eWLP)

The following figures show the application diagrams for each package option.

## 1.1 Applications

- Wi-Fi and Bluetooth enabled smart phones and tablets

- · Personal computing systems including notebooks and ultrabooks

- · Wireless home audio and video entertainment systems

- · Mobile routers and Internet of Things (IoT) gateways

## 1.2 Wi-Fi key features

- Support 802.11ac/n/a/g/b

- Dual band: 2.4 GHz and 5 GHz

- Up to MCS9 data rates

- 20/40/80 MHz channel bandwidth

- · Security: AES, WAPI

## 1.3 Bluetooth key features

- Bluetooth 5.2 support

- PCM audio interface

- · Security: AES

### 1.4 Host interfaces

Wi-Fi and Bluetooth host interface options

| Wi-Fi    | Bluetooth |

|----------|-----------|

| SDIO 3.0 | UART      |

| SDIO 3.0 | SDIO 3.0  |

## 1.5 Operating characteristics

• Supply voltage: 2.2V, 1.8V, and 1.1V

Operating temperature

Extended: -30 to 85°C

Industrial: -40 to 85°C

### 1.6 General features

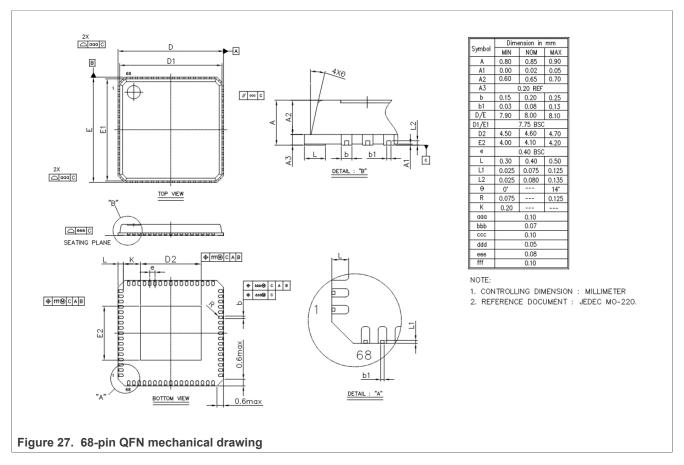

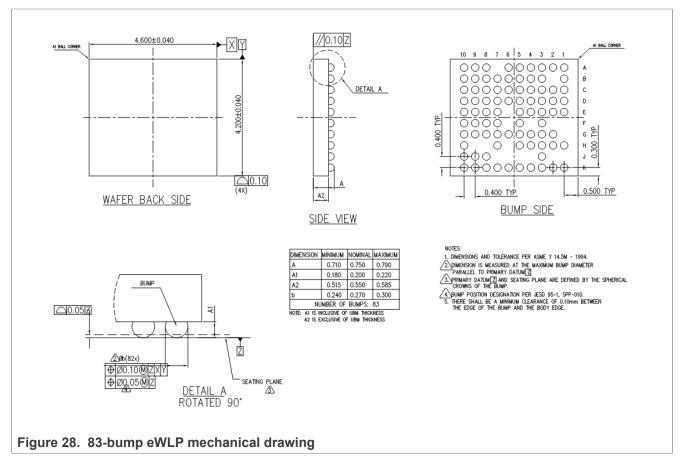

- · Package options

- 68-pin 8x8 mm QFN with wettable flanks

- 83-bump 4.6x4.2 mm eWLP

- · Power management

- Low power dissipation

- Optional lower power operation with external sleep clock

- Sleep and standby modes for low-power operation

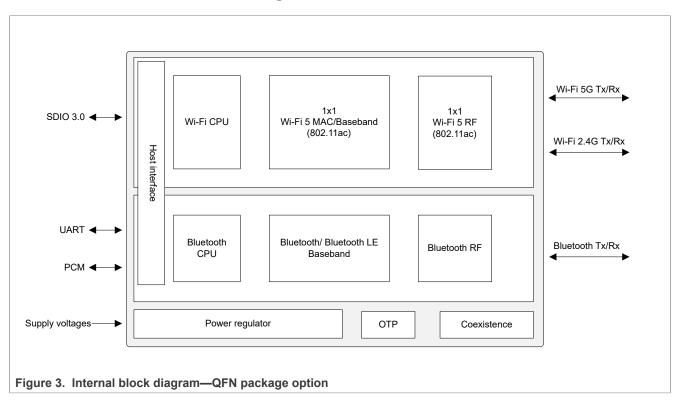

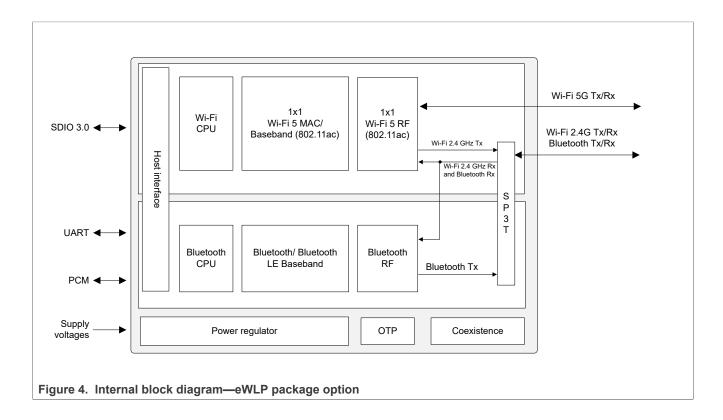

- Independent ARM-based Wi-Fi and Bluetooth CPUs

- Supports reference clock signal from external crystal or external crystal oscillator

- Memory

- Internal SRAM

- Boot ROM

- One Time Programmable (OTP) memory to store the MAC address and calibration data

- Peripheral interfaces

- GPIO interface (up to 21)

# 1.7 Internal block diagram

88W8987\_SDS

All information provided in this document is subject to legal disclaimers.

© NXP B.V. 2021. All rights reserved.

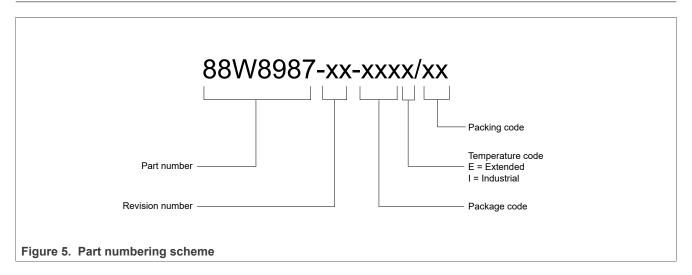

# 2 Ordering information

Table 1. Part order codes

| Part order code    | Package type                                              | Packing       |

|--------------------|-----------------------------------------------------------|---------------|

| 88W8987-A2-NYEE/AK | 68-pin HVQFN - 8 x 8 x 0.85 mm, with 0.4 mm pitch         | Tray          |

| 88W8987-A2-NYEE/AZ | 68-pin HVQFN - 8 x 8 x 0.85 mm, with 0.4 mm pitch         | Tape and reel |

| 88W8987-A2-NYEI/AK | 68-pin HVQFN - 8 x 8 x 0.85 mm, with 0.4 mm pitch         | Tray          |

| 88W8987-A2-NYEI/AZ | 68-pin HVQFN - 8 x 8 x 0.85 mm, with 0.4 mm pitch         | Tape and reel |

| 88W8987-A2-EAHE/AZ | 83-terminal eWLP - 4.6 x 4.2 x 0.75 mm, with 0.4 mm pitch | Tape and reel |

# 3 Wi-Fi subsystem

### 3.1 IEEE 802.11 standards

- 802.11 data rates of 1 and 2 Mbit/s

- 802.11b data rates of 5.5 and 11 Mbit/s

- 802.11a/g data rates 6, 9, 12, 18, 24, 36, 48, and 54 Mbit/s for multimedia content transmission

- 802.11g/b performance enhancements

- 802.11ac / 802.11n with maximum data rates up to 86.7 Mbit/s (20 MHz channel), 200 Mbit/s (40 MHz channel), 433 Mbit/s (80 MHz channel)

- 802.11d international roaming

- 802.11e quality of service

- 802.11h transmit power control

- 802.11h DFS radar pulse detection

- 802.11i enhanced security

- 802.11k radio resource measurement

- 802.11mc precise indoor location positioning

- 802.11n block acknowledgment extension

- 802.11r fast hand-off for AP roaming

- 802.11u Hotspot 2.0 (STA mode only)

- 802.11v TIM frame transmission/reception

- 802.11w protected management frames

- Fully supports clients (stations) implementing IEEE Power Save mode

Downloaded from Arrow.com.

### 3.2 Wi-Fi MAC

- Simultaneous peer-to-peer and Infrastructure Modes

- RTS/CTS for operation under DCF

- Hardware filtering of 32 multicast addresses and duplicate frame detection for up to 32 unicast addresses

- On-chip Tx and Rx FIFO for maximum throughput

- Open System and Shared Key Authentication services

- A-MPDU Rx (de-aggregation) and Tx (aggregation) (supports 802.11ac single-MPDU A-MPDU)

- 20/40/80 MHz coexistence

- Reduced Inter-Frame Spacing (RIFS) receive

- · Management information base counters

- · Radio resource measurement counters

- · Quality of service queues

- Block acknowledgment extension

- Dynamic frequency selection

- Beamforming

- 802.11ac Explicit Beamformee, supports immediate feedback generation using 802.11ac compressed steering matrix feedback

- 802.11ac Multi-User Beamformee

- 802.11n Explicit Beamformee, supports immediate feedback generation using uncompress and compress steering matrix or delayed feedback of all feedback types

- TIM frame transmission/reception

- Multiple-BSS/Station

- Transmit rate adaptation

- · Transmit power control

- · Long and short preamble generation on a frame-by-frame basis for 802.11b frames

- · Mobile hotspot

Downloaded from Arrow.com.

### 3.3 Wi-Fi baseband

- 802.11ac (on-chip RF radio)

- Backward compatibility with legacy 802.11n/a/g/b technology

- Simultaneous Wi-Fi and Bluetooth receive in single-antenna mode (eWLP only)

- PHY data rates up to 433 Mbit/s

- 20 MHz bandwidth/channel, 40 MHz bandwidth/channel, upper/lower 20 MHz packets in 40 MHz channel, 20 MHz duplicate legacy packets in 40 MHz channel mode operation

- 80 MHz bandwidth/channel, 4 positions of 20 MHz packets in 80 MHz channel, upper/ lower 40 MHz packets in 80 MHz channel, 20 MHz quadruplicate legacy packets in 80 MHz channel mode operation

- Modulation and Coding Scheme (MCS)

- 802.11ac-MCS 0~9 Nsts = 1

- 802.11n-MCS 0~7 and MCS 32 (duplicate 6 Mbit/s)

- Dynamic frequency selection (radar detection)

- Enhanced radar detection for long and short pulse radar

- Enhanced AGC scheme for DFS channel

- Japan DFS requirements for W53 and W56 frequency bands

- · Radio resource measurement

- Optional 802.11ac and 802.11n features:

- 20/40/80 MHz coexistence with middle-packet detection (GI detection) for enhanced CCA

- 1 spatial stream STBC reception

- LDPC transmission and reception for both 802.11n and 802.11ac

- 256 QAM (MCS 8, 9) modulation, optional support for 802.11ac MCS 9 in 20 MHz using LDPC

- Short guard interval

- RIFS on receive path for 802.11n packets

- 802.11n greenfield Tx/Rx

- Explicit beamformee support

- 802.11ac multi-user beamformee

- MU-PPDUs (receive)

- Wi-Fi indoor locationing (802.11mc)

- · Power save features

### 3.4 Wi-Fi radio

- Integrated direct-conversion radio

- 20, 40, and 80 MHz channel bandwidths

- Shared Wi-Fi/Bluetooth receive input scheme for 2.4 GHz band (eWLP only)

### Wi-Fi Rx path

- · Direct conversion architecture eliminates need for external SAW filter

- On-chip gain selectable LNA with optimized noise figure and power consumption

- · High dynamic range AGC function in receive mode

### Wi-Fi Tx path

- · Internal PA with power control

- Optimized Tx gain distribution for linearity and noise performance

#### Wi-Fi local oscillator

- Fractional-N for multiple reference clock support

- · Fine channel step

### 3.5 Wi-Fi encryption

- Advanced Encryption Standard (AES) / Counter-Mode/CBC-MAC Protocol (CCMP)

- Advanced Encryption Standard (AES) /Cipher-Based Message Authentication Code (CMAC)

- Advanced Encryption Standard (AES) / Galois/Counter Mode Protocol (GCMP)

- WLAN Authentication and Privacy Infrastructure (WAPI)

### 3.6 Wi-Fi host interfaces

SDIO 3.0 device interface (4-bit SDIO and 1-bit SDIO) transfer modes at full clock range up to 208 MHz

# 4 Bluetooth subsystem

### 4.1 2.4 GHz Bluetooth Tx/Rx

- Bluetooth 5.2

- · Bluetooth Class 2

- Bluetooth Class 1

- Single-ended, shared Tx/Rx path for Bluetooth (QFN package option)

- Simultaneous Wi-Fi and Bluetooth receive in single-antenna mode (eWLP package option)

- PCM interface for voice applications

- Baseband and radio BDR and EDR packet types—1 Mbit/s (GFSK), 2 Mbit/s ( $\pi$ /4-DQPSK), and 3 Mbit/s (8DPSK)

- Fully functional Bluetooth baseband—AFH, forward error correction, header error control, access code correlation, CRC, encryption bit stream generation, and whitening

- Adaptive Frequency Hopping (AFH) using Packet Error Rate (PER)

- · Interlaced scan for faster connection setup

- Simultaneous active ACL connection support

- · Automatic ACL packet type selection

- Full master and slave piconet support

- Scatternet support

- · Standard SDIO and UART HCI transport layer

- · HCI layer to integrate with profile stack

- SCO/eSCO links with hardware accelerated audio signal processing and hardware supported PPEC algorithm for speech quality improvement

- All standard SCO/eSCO voice coding

- · All standard pairing, authentication, link key, and encryption operations

- Standard Bluetooth power saving mechanisms (sniff modes, and sniff sub-rating)

- Enhanced Power Control (EPC)

- Channel Quality Driven Data Rate (CQDDR)

- Wideband Speech (WBS) support (1 WBS link)

- · Encryption (AES) support

### 4.2 Bluetooth Low Energy (LE)

- · Broadcaster, Observer, Central, and Peripheral roles

- Supports link layer topology to be master and slave (connects up to 16 links)

- Wi-Fi/Bluetooth coexistence protocol support

- · Shared RF with BDR/EDR

- Encryption (AES) support

- Intelligent Adaptive Frequency Hopping (AFH)

- Bluetooth LE Privacy 1.2

- Bluetooth LE Secure Connection

- Bluetooth LE Data Length Extension

- Bluetooth LE Advertising Extension

- 2 Mbit/s Bluetooth LE

88W8987 SDS

All information provided in this document is subject to legal disclaimers

© NXP B.V. 2021. All rights reserved

### 4.3 Bluetooth host interfaces

- SDIO 3.0

- High-speed UART

### 4.4 Coexistence

• Internal coexistence arbitration for Wi-Fi/Bluetooth

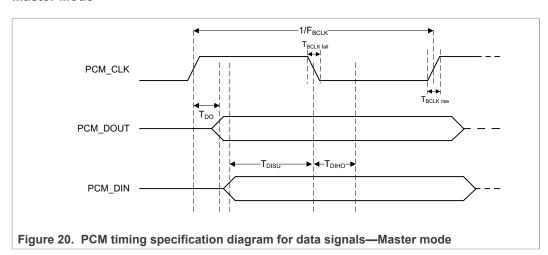

### 4.5 PCM interface

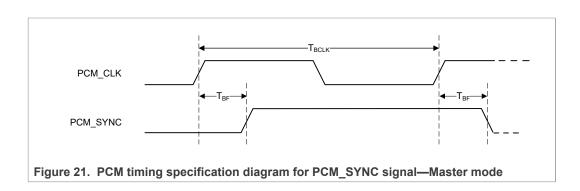

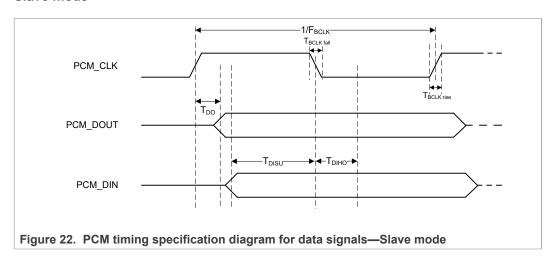

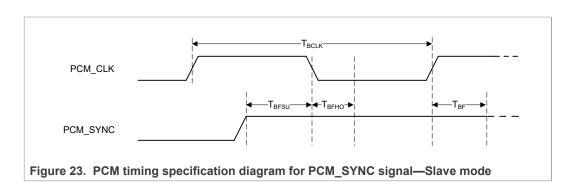

- · Master or slave mode

- PCM bit width size of 8 bits or 16 bits

- Up to 4 slots with configurable bit width and start positions

- PCM short frame and long frame synchronization

- Tri-state PCM interface capability

88W8987 SDS

All information provided in this document is subject to legal disclaimers.

© NXP B.V. 2021. All rights reserved.

<sup>1</sup> In PCM Master mode, PCM long frame synchronization is 1 clock wide. In PCM Slave mode, PCM Master's long frame synchronization pattern is supported.

# 5 Pin information

## 5.1 Signal diagrams

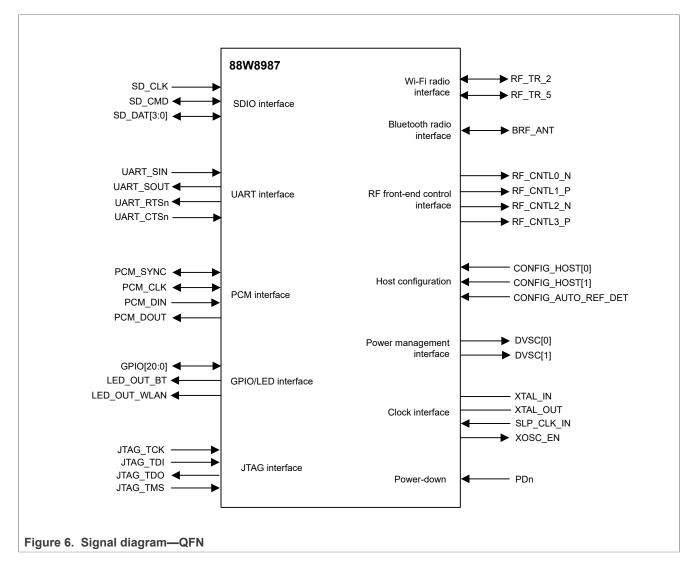

### 5.1.1 Signal diagram for QFN package option

Figure 6 shows the signals for the QFN package of the device.

Note: Signals may be muxed. See Section 5.5 "Pin description".

Downloaded from Arrow.com.

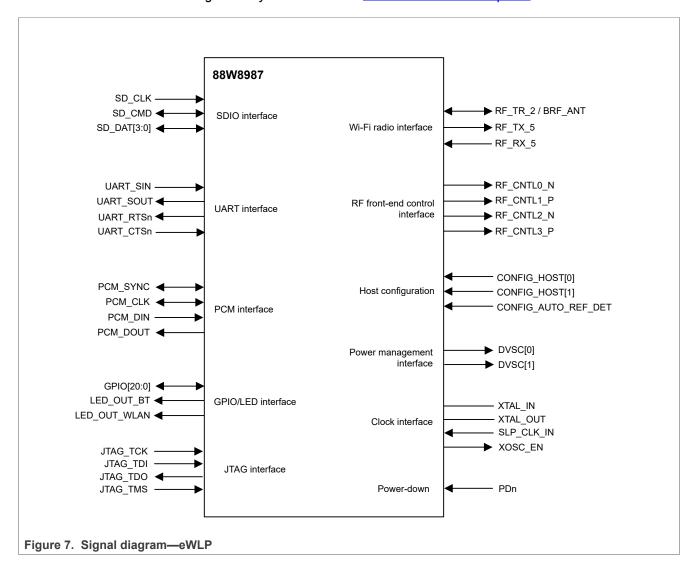

## 5.1.2 Signal diagram for eWLP package option

Figure 7 shows the signals for eWLP package option.

Note: Signals may be muxed. See Section 5.5 "Pin description".

# 5.2 Pin types

### Table 2. Pin types

| Pin type | Description          |

|----------|----------------------|

| I/O      | Digital input/output |

| I        | Digital input        |

| 0        | Digital output       |

| A, I     | Analog input         |

| A, O     | Analog output        |

| A, I/O   | Analog input/output  |

| NC       | No connect           |

| DNC      | Do not connect       |

| Power    | Power                |

| Ground   | Ground               |

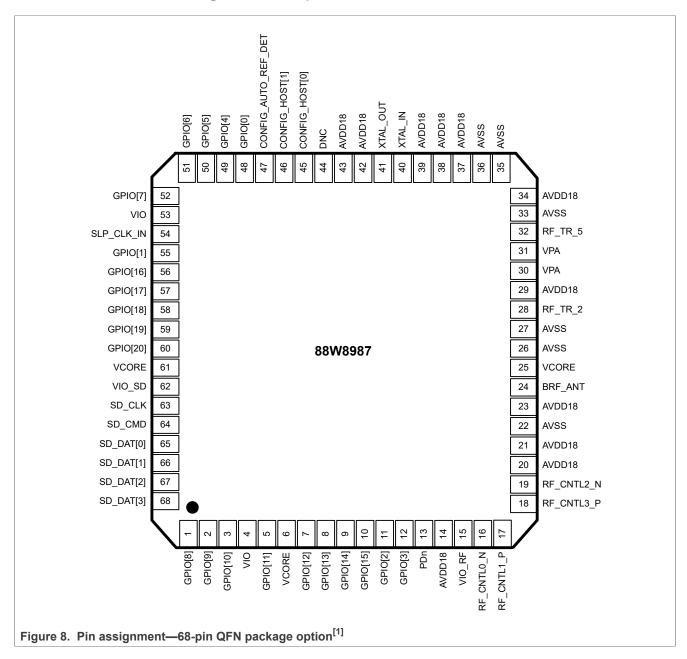

# 5.3 Pin assignment—68-pin QFN

[1] EPAD on pin 69.

## 5.3.1 Pin list by number

The following table shows the pin list sorted by pin number.

Table 3. Pin list by number

| Pin number | Pin name   | Power  | Туре   |

|------------|------------|--------|--------|

| 1          | GPIO[8]    | VIO    | I/O    |

| 2          | GPIO[9]    | VIO    | I/O    |

| 3          | GPIO[10]   | VIO    | I/O    |

| 4          | VIO        |        | Power  |

| 5          | GPIO[11]   | VIO    | I/O    |

| 6          | VCORE      |        | Power  |

| 7          | GPIO[12]   | VIO    | I/O    |

| 8          | GPIO[13]   | VIO    | I/O    |

| 9          | GPIO[14]   | VIO    | I/O    |

| 10         | GPIO[15]   | VIO    | I/O    |

| 11         | GPIO[2]    | VIO    | I/O    |

| 12         | GPIO[3]    | VIO    | I/O    |

| 13         | PDn        | AVDD18 | I      |

| 14         | AVDD18     |        | Power  |

| 15         | VIO_RF     |        | Power  |

| 16         | RF_CNTL0_N | VIO_RF | 0      |

| 17         | RF_CNTL1_P | VIO_RF | 0      |

| 18         | RF_CTLN3_P | VIO_RF | 0      |

| 19         | RF_CTLN2_N | VIO_RF | 0      |

| 20         | AVDD18     |        | Power  |

| 21         | AVDD18     |        | Power  |

| 22         | AVSS       |        | Ground |

| 23         | AVDD18     |        | Power  |

| 24         | BRF_ANT    | AVDD18 | A, I/O |

| 25         | VCORE      |        | Power  |

| 26         | AVSS       |        | Ground |

| 27         | AVSS       |        | Ground |

| 28         | RF_TR_2    | AVDD18 | A, I/O |

| 29         | AVDD18     |        | Power  |

| 30         | VPA        |        | Power  |

| 31         | VPA        |        | Power  |

| 32         | RF_TR_5    | AVDD18 | A, I/O |

| 33         | AVSS       |        | Ground |

| 34         | AVDD18     |        | Power  |

88W8987\_SDS

All information provided in this document is subject to legal disclaimers.

© NXP B.V. 2021. All rights reserved.

Table 3. Pin list by number...continued

| Pin number | Pin name            | Power  | Туре   |

|------------|---------------------|--------|--------|

| 35         | AVSS                |        | Ground |

| 36         | AVSS                |        | Ground |

| 37         | AVDD18              |        | Power  |

| 38         | AVDD18              |        | Power  |

| 39         | AVDD18              |        | Power  |

| 40         | XTAL_IN             | AVDD18 | I      |

| 41         | XTAL_OUT            | AVDD18 | 0      |

| 42         | AVDD18              |        | Power  |

| 43         | AVDD18              |        | Power  |

| 44         | DNC                 |        |        |

| 45         | CONFIG_HOST[0]      | AVDD18 | I      |

| 46         | CONFIG_HOST[1]      | AVDD18 | I      |

| 47         | CONFIG_AUTO_REF_DET | AVDD18 | I      |

| 48         | GPIO[0]             | VIO    | I/O    |

| 49         | GPIO[4]             | VIO    | I/O    |

| 50         | GPIO[5]             | VIO    | I/O    |

| 51         | GPIO[6]             | VIO    | I/O    |

| 52         | GPIO[7]             | VIO    | I/O    |

| 53         | VIO                 |        | Power  |

| 54         | SLP_CLK_IN          | VIO    | I      |

| 55         | GPIO[1]             | VIO    | I/O    |

| 56         | GPIO[16]            | VIO    | I/O    |

| 57         | GPIO[17]            | VIO    | I/O    |

| 58         | GPIO[18]            | VIO    | I/O    |

| 59         | GPIO[19]            | VIO    | I/O    |

| 60         | GPIO[20]            | VIO    | I/O    |

| 61         | VCORE               |        | Power  |

| 62         | VIO_SD              |        | Power  |

| 63         | SD_CLK              | VIO_SD | I      |

| 64         | SD_CMD              | VIO_SD | I/O    |

| 65         | SD_DAT[0]           | VIO_SD | I/O    |

| 66         | SD_DAT[1]           | VIO_SD | I/O    |

| 67         | SD_DAT[2]           | VIO_SD | I/O    |

| 68         | SD_DAT[3]           | VIO_SD | I/O    |

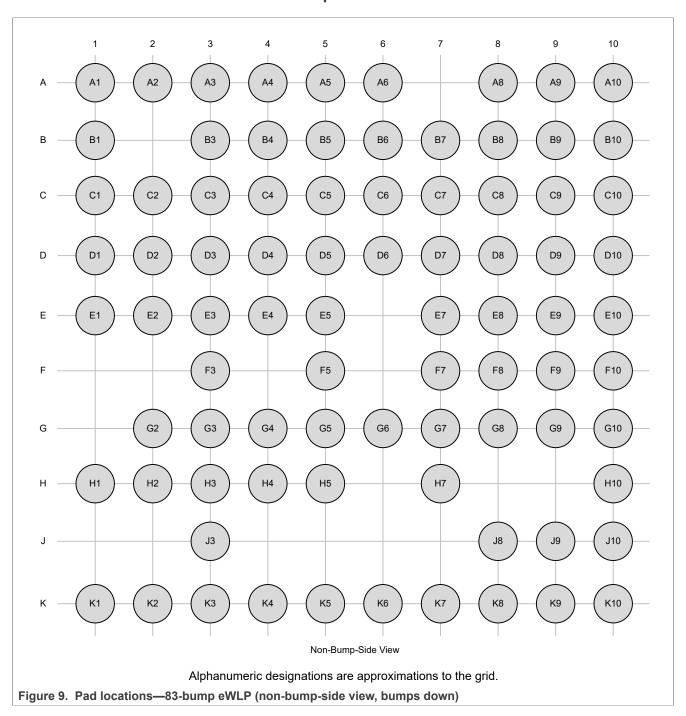

# 5.4 Pad locations—83-bump eWLP

Table 4 indicates the pad locations in 83-bump eWLP package.

Note: Alphanumeric designations are approximations to the grid shown in Figure 9

Table 4. Pad locations—83-bump eWLP

| Signal name       | Alpha-numeric designation | Pad location relative to die center (non-bump-side view) |        |  |

|-------------------|---------------------------|----------------------------------------------------------|--------|--|

|                   |                           | X                                                        | Υ      |  |

| NC                | A1                        | -1800.0                                                  | 1800.0 |  |

| GPIO[18]          | A2                        | -1400.0                                                  | 1800.0 |  |

| VSS               | A3                        | -1000.0                                                  | 1800.0 |  |

| GPIO[19]          | A4                        | -600.0                                                   | 1800.0 |  |

| VCORE             | A5                        | -200.0                                                   | 1800.0 |  |

| VIO_SD            | A6                        | 200.0                                                    | 1800.0 |  |

| VSS               | A8                        | 1000.0                                                   | 1800.0 |  |

| SD_DAT[3]         | A9                        | 1400.0                                                   | 1800.0 |  |

| VSS               | A10                       | 1800.0                                                   | 1800.0 |  |

| VIO               | B1                        | -1800.0                                                  | 1400.0 |  |

| SLP_CLK_IN        | В3                        | -1000.0                                                  | 1400.0 |  |

| GPIO[16]          | B4                        | -600.0                                                   | 1400.0 |  |

| GPI0[17]          | B5                        | -200.0                                                   | 1400.0 |  |

| GPI0[20]          | B6                        | 200.0                                                    | 1400.0 |  |

| SD_CLK            | B7                        | 600.0                                                    | 1400.0 |  |

| SD_DAT[0]         | B8                        | 1000.0                                                   | 1400.0 |  |

| SD_DAT[1]         | В9                        | 1400.0                                                   | 1400.0 |  |

| SD_DAT[2]         | B10                       | 1800.0                                                   | 1400.0 |  |

| AVDD18            | C1                        | -1800.0                                                  | 1000.0 |  |

| AVSS              | C2                        | -1400.0                                                  | 1000.0 |  |

| GPIO[0] / XOSC_EN | C3                        | -1000.0                                                  | 1000.0 |  |

| GPI0[6]           | C4                        | -600.0                                                   | 1000.0 |  |

| GPI0[7]           | C5                        | -200.0                                                   | 1000.0 |  |

| GPIO[1]           | C6                        | 200.0                                                    | 1000.0 |  |

| SD_CMD            | C7                        | 600.0                                                    | 1000.0 |  |

| GPIO[10]          | C8                        | 1000.0                                                   | 1000.0 |  |

| GPIO[8]           | C9                        | 1400.0                                                   | 1000.0 |  |

| VIO               | C10                       | 1800.0                                                   | 1000.0 |  |

| XTAL_IN           | D1                        | -1800.0                                                  | 600.0  |  |

| XTAL_OUT          | D2                        | -1400.0                                                  | 600.0  |  |

| DNC               | D3                        | -1000.0                                                  | 600.0  |  |

| CONFIG_HOST[0]    | D4                        | -600.0                                                   | 600.0  |  |

| GPIO[4]           | D5                        | -200.0                                                   | 600.0  |  |

| GPIO[5]           | D6                        | 200.0                                                    | 600.0  |  |

88W8987\_SDS

All information provided in this document is subject to legal disclaimers.

© NXP B.V. 2021. All rights reserved.

Table 4. Pad locations—83-bump eWLP...continued

| Signal name         | Alpha-numeric designation |         | relative to die<br>ump-side view) |

|---------------------|---------------------------|---------|-----------------------------------|

|                     |                           | X       | Υ                                 |

| GPIO[12]            | D7                        | 600.0   | 600.0                             |

| GPIO[9]             | D8                        | 1000.0  | 600.0                             |

| GPIO[11]            | D9                        | 1400.0  | 600.0                             |

| VCORE               | D10                       | 1800.0  | 600.0                             |

| AVDD18              | E1                        | -1800.0 | 200.0                             |

| AVSS                | E2                        | -1400.0 | 200.0                             |

| AVDD18              | E3                        | -1000.0 | 200.0                             |

| AVSS                | E4                        | -600.0  | 200.0                             |

| CONFIG_AUTO_REF_DET | E5                        | -200.0  | 200.0                             |

| GPIO[13]            | E7                        | 600.0   | 200.0                             |

| GPIO[3]             | E8                        | 1000.0  | 200.0                             |

| GPIO[15]            | E9                        | 1400.0  | 200.0                             |

| GPIO[14]            | E10                       | 1800.0  | 200.0                             |

| AVSS                | F3                        | -1000.0 | -200.0                            |

| CONFIG_HOST[1]      | F5                        | -200.0  | -200.0                            |

| GPIO[2]             | F7                        | 600.0   | -200.0                            |

| PDn                 | F8                        | 1000.0  | -200.0                            |

| AVDD18              | F9                        | 1400.0  | -200.0                            |

| VSS                 | F10                       | 1800.0  | -200.0                            |

| AVDD18              | G2                        | -1400.0 | -600.0                            |

| AVSS                | G3                        | -1000.0 | -600.0                            |

| VCORE               | G4                        | -600.0  | -600.0                            |

| AVSS                | G5                        | -200.0  | -600.0                            |

| RF_CNTL0_N          | G6                        | 200.0   | -600.0                            |

| RF_CNTL1_P          | G7                        | 600.0   | -600.0                            |

| RF_CNTL3_P          | G8                        | 1000.0  | -600.0                            |

| RF_CNTL2_N          | G9                        | 1400.0  | -600.0                            |

| VIO_RF              | G10                       | 1800.0  | -600.0                            |

| AVSS                | H1                        | -1800.0 | -1000.0                           |

| AVSS                | H2                        | -1400.0 | -1000.0                           |

| AVSS                | H3                        | -1000.0 | -1000.0                           |

| AVSS                | H4                        | -600.0  | -1000.0                           |

| AVSS                | H5                        | -200.0  | -1000.0                           |

| AVSS                | H7                        | 600.0   | -1000.0                           |

88W8987\_SDS

All information provided in this document is subject to legal disclaimers.

© NXP B.V. 2021. All rights reserved.

Table 4. Pad locations—83-bump eWLP...continued

| Signal name       | Alpha-numeric designation | Pad location relative to die center (non-bump-side view) |         |  |

|-------------------|---------------------------|----------------------------------------------------------|---------|--|

|                   |                           | X                                                        | Υ       |  |

| AVSS              | H10                       | 1800.0                                                   | -1000.0 |  |

| VPA               | J3                        | -1000.0                                                  | -1400.0 |  |

| AVSS              | J8                        | 1000.0                                                   | -1400.0 |  |

| AVSS              | J9                        | 1400.0                                                   | -1400.0 |  |

| AVSS              | J10                       | 1800.0                                                   | -1400.0 |  |

| NC                | K1                        | -1800.0                                                  | -1800.0 |  |

| RF_RX_5           | K2                        | -1400.0                                                  | -1800.0 |  |

| RF_TX_5           | K3                        | -1000.0                                                  | -1800.0 |  |

| RF_TR_2 / BRF_ANT | K4                        | -600.0                                                   | -1800.0 |  |

| AVDD18            | K5                        | -200.0                                                   | -1800.0 |  |

| AVSS              | K6                        | 200.0                                                    | -1800.0 |  |

| AVDD18            | K7                        | 600.0                                                    | -1800.0 |  |

| AVDD18            | K8                        | 1000.0                                                   | -1800.0 |  |

| AVDD18            | K9                        | 1400.0                                                   | -1800.0 |  |

| NC                | K10                       | 1800.0                                                   | -1800.0 |  |

# 5.5 Pin description

### 5.5.1 Pin states

The pin states information provided in the tables includes:

- No Pad Power State indicates the state when there is no power

- **PwrDwn State** denotes the power-down state in default configuration. Many pads have programmable power-down values, which can be set by firmware.

- **Reset State** is the state after the power-on-reset state and before the hardware state (HW State)

- HW State (hardware state) is the state after boot code finishes and before firmware

download begins (firmware may change the pin state). HW State may differ based on

the pin muxing/strap setting. For example, for UART\_RTSn and UART\_SOUT, the boot

code will enable the UART interface when the device is in SDIO-UARTor PCIe-UART

mode, making the HW states output high and output low, respectively.

- PwrDwn Prog indicates if the power-down state can be programmed

- Internal PU/PD columns indicates the following:

- Type of PU/PD (weak vs nominal)

- The polarity (PU vs. PD)

The internal pull-up or pull-down applies when the pin is in input mode

- PU denotes whether the pull-up can be programmed or not

- PD denotes whether the pull-down can be programmed or not

- Pull-up and pull-down are only effective when the pad is in input mode

- After firmware is downloaded, the pads (GPIO, RF control, and so on) are programmed in functional mode per the functionality of the pins

### 5.5.2 General purpose I/O (GPIO)

Table 5. General purpose I/O (GPIO)<sup>[1]</sup> (MFP) *Pins may be Multi-Functional Pins (MFP).*

| Pin Name                                                                                       | Supply                                                                                                              | No Pad<br>Power<br>State <sup>[2]</sup> | Reset<br>State | HW State                   | PwrDwn<br>State | PwrDwn<br>Prog | Internal PU/<br>PD | PU  | PD  |

|------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|-----------------------------------------|----------------|----------------------------|-----------------|----------------|--------------------|-----|-----|

| GPIO[20]                                                                                       | VIO                                                                                                                 | tristate                                | output         | output high <sup>[3]</sup> | tristate        | yes            | weak PU            | yes | yes |

|                                                                                                | GPIO Mode: GPIO[20] (input/output). This pin can be used for Bluetooth to host wake-up (out-of-band wake-up signal) |                                         |                |                            |                 |                |                    |     |     |

| GPIO[19]                                                                                       | VIO                                                                                                                 | tristate                                | output         | output high                | tristate        | yes            | weak PU            | yes | yes |

| <b>GPIO Mod</b>                                                                                | e: GPIO[19]                                                                                                         | (input/outp                             | ut)            |                            |                 |                |                    |     |     |

| Power Mai                                                                                      | nagement N                                                                                                          | Mode: DVS0                              | C[1] digital v | oltage scaling co          | ntrol (outpu    | t)             |                    |     |     |

| GPIO[18]                                                                                       | VIO                                                                                                                 | tristate                                | output         | output high                | tristate        | yes            | weak PU            | yes | yes |

|                                                                                                |                                                                                                                     | (input/outp                             | •              |                            |                 |                |                    |     |     |

| Power Mai                                                                                      | nagement N                                                                                                          | Node: DVS                               | C[0] digital v | oltage scaling co          | ntrol (outpu    | t)             |                    |     |     |

| GPIO[17]                                                                                       | VIO                                                                                                                 | tristate                                | input          | input                      | tristate        | yes            | weak PU            | yes | yes |

| <b>GPIO Mod</b>                                                                                | GPIO Mode: GPIO[17] (input/output)                                                                                  |                                         |                |                            |                 |                |                    |     |     |

| JTAG Mod                                                                                       | JTAG Mode: JTAG_TDO, JTAG test data (output)                                                                        |                                         |                |                            |                 |                |                    |     |     |

| This pin is used as a configuration pin: CON[9] (input). See Section 5.6 "Configuration pins". |                                                                                                                     |                                         |                |                            |                 |                |                    |     |     |

88W8987\_SDS

All information provided in this document is subject to legal disclaimers

© NXP B.V. 2021. All rights reserved

Table 5. General purpose I/O  ${\rm (GPIO)}^{[1]}$  (MFP)...continued

Pins may be Multi-Functional Pins (MFP).

| Pin Name        | Supply                   | No Pad<br>Power<br>State <sup>[2]</sup> | Reset<br>State | HW State                                      | PwrDwn<br>State        | PwrDwn<br>Prog | Internal PU/<br>PD | PU       | PD  |

|-----------------|--------------------------|-----------------------------------------|----------------|-----------------------------------------------|------------------------|----------------|--------------------|----------|-----|

| GPIO[16]        | VIO                      | tristate                                | input          | input                                         | tristate               | yes            | nominal PU         | yes      | yes |

|                 | =                        | input/outp                              | •              |                                               |                        |                |                    |          |     |

| JTAG Mod        | le: JTAG_T               | DI, JTAG te                             | st data (inpu  | it)                                           |                        |                |                    |          |     |

| GPIO[15]        | VIO                      | tristate                                | input          | input                                         | output<br>high         | yes            | nominal PU         | yes      | yes |

|                 | -                        | [] (input/outpused as Blue              | ,              | endent reset.                                 |                        |                |                    |          | ·   |

| •               |                          | MS, JTAG o                              | •              |                                               |                        |                |                    |          |     |

| GPIO[14]        | VIO                      | tristate                                | input          | input                                         | tristate               | yes            | nominal PU         | yes      | yes |

| GPIO Mod        | ⊥<br><b>le</b> : GPIO[14 | _<br>l] (input/outp                     | out)           | -                                             |                        |                |                    |          |     |

|                 | _                        | sed as Wi-F                             | ,              | nt reset.                                     |                        |                |                    |          |     |

| JTAG Mod        | le: JTAG_T               | CK, JTAG te                             | est clock (inp | •                                             |                        |                |                    |          |     |

| GPIO[13]        | VIO                      | tristate                                | input          | input <sup>[4]</sup><br>output <sup>[5]</sup> | output<br>high         | yes            | nominal PU         | yes      | yes |

| GPIO Mod        | le: GPIO[13              | ::<br>B] (input/outp                    | out)           | I.                                            |                        | 1              |                    |          |     |

|                 |                          |                                         |                | 7 Wi-Fi wake-up                               | (out-of-band           | l wake-up s    | signal).           |          |     |

| GPIO[12]        | VIO                      | tristate                                | input          | input                                         | tristate               | yes            | nominal PU         | yes      | yes |

|                 |                          | ?] (input/outp                          |                | 7 Bluetooth wak                               | e-up (out-of-l         | oand wake-     | ·up signal)        |          | ,   |

| GPIO[11]        | VIO                      | tristate                                | input          | input <sup>[4]</sup><br>output <sup>[5]</sup> | output<br>high         | yes            | weak PU            | yes      | yes |

| UART Mod        | de: UART_I               | ] (input/outp<br>RTSn (outpu            | ıt) (active lo | w)<br>] (input). See <u>Se</u>                | ection 5.6 "Co         | onfiguration   | ı pins".           | ,        |     |

| GPIO[10]        | VIO                      | tristate                                | input          | input                                         | tristate               | yes            | nominal PU         | yes      | yes |

|                 | _                        | )] (input/outp                          | •              |                                               |                        |                |                    |          |     |

| UART Mod        | de: UART_                | CTSn (input                             | ) (active low  | )                                             |                        |                |                    |          |     |

| GPIO[9]         | VIO                      | tristate                                | input          | input                                         | tristate               | yes            | nominal PU         | yes      | yes |

|                 | le: GPIO[9]<br>de: UART_ | (input/outpu<br>SIN (input)             | ıt)            |                                               |                        |                |                    |          |     |

| GPIO[8]         | VIO                      | tristate                                | input          | input <sup>[4]</sup><br>output <sup>[5]</sup> | output low             | yes            | weak PU            | yes      | yes |

| GPIO Mod        | le: GPIO[8]              | (input/outpu                            | it)            | li .                                          |                        | 1              | L                  |          |     |

| <b>UART Mod</b> | _                        | SOUT (outp                              | •              |                                               |                        |                |                    |          |     |

|                 |                          | c                                       | : OONE         | IC VOCC CEL                                   | (input) Coo            | Coation E 6    | "Configuration r   | vine"    |     |

| This pin is     | used as a d              | configuration                           | pin: CONF      | IG_XUSU_SEL                                   | (iriput). See <u>s</u> | <u> </u>       | Corniguration      | <u> </u> |     |

88W8987 SD

All information provided in this document is subject to legal disclaimers.

© NXP B.V. 2021. All rights reserved.

# Table 5. General purpose I/O (GPIO)<sup>[1]</sup> (MFP)...continued

Pins may be Multi-Functional Pins (MFP).

| Pin Name    | Supply                            | No Pad<br>Power<br>State <sup>[2]</sup> | Reset<br>State | HW State                   | PwrDwn<br>State | PwrDwn<br>Prog      | Internal PU/<br>PD | PU  | PD  |  |

|-------------|-----------------------------------|-----------------------------------------|----------------|----------------------------|-----------------|---------------------|--------------------|-----|-----|--|

| GPIO Mod    | SPIO Mode: GPIO[7] (input/output) |                                         |                |                            |                 |                     |                    |     |     |  |

|             | _                                 | NC (input/o                             | utput)         |                            |                 |                     |                    |     |     |  |

| Output if   |                                   |                                         |                |                            |                 |                     |                    |     |     |  |

| Input if sl |                                   |                                         |                |                            |                 |                     |                    |     |     |  |

| GPIO[6]     | VIO                               | tristate                                | input          | input                      | tristate        | yes                 | nominal PU         | yes | yes |  |

|             |                                   | (input/outpu                            | ,              |                            |                 |                     |                    |     |     |  |

| Output if   | _                                 | Հ (input/outբ                           | out)           |                            |                 |                     |                    |     |     |  |

| Input if sl |                                   |                                         |                |                            |                 |                     |                    |     |     |  |

| GPIO[5]     | VIO                               | tristate                                | input          | input                      | tristate        | yes                 | weak PU            | yes | yes |  |

| SPIO Mod    | e: GPIO[5]                        | input/outpu                             | t)             |                            |                 |                     |                    |     |     |  |

|             |                                   | UT (output)                             | ,              |                            |                 |                     |                    |     |     |  |

| his pin is  | used as a c                       | onfiguration                            | pin: CON[7     | ] (input). See <u>Se</u>   | ction 5.6 "Co   | <u>onfiguration</u> | pins".             |     |     |  |

| GPIO[4]     | VIO                               | tristate                                | input          | input                      | tristate        | yes                 | nominal PU         | yes | yes |  |

| GPIO Mod    | e: GPIO[4]                        | (input/outpu                            | t)             |                            |                 |                     |                    |     | ·   |  |

| PCM Mode    | : PCM_DIN                         | l (input)                               |                |                            |                 |                     |                    |     |     |  |

| GPIO[3]     | VIO                               | tristate                                | output         | output high <sup>[3]</sup> | tristate        | yes                 | weak PU            | yes | yes |  |

| GPIO Mod    | e: GPIO[3]                        | (input/outpu                            | t)             |                            |                 |                     | 1                  | '   |     |  |

| ED Mode     | : LED_OUT                         | _BT (outpu                              | t)             |                            |                 |                     |                    |     |     |  |

| GPIO[2]     | VIO                               | tristate                                | output         | output high <sup>[3]</sup> | tristate        | yes                 | weak PU            | yes | yes |  |

| GPIO Mod    | e: GPIO[2]                        | (input/outpu                            | t)             |                            |                 |                     | -                  | _   |     |  |

| _ED Mode    | : LED_OUT                         | _WLAN (ou                               | ıtput)         |                            |                 |                     |                    |     |     |  |

| GPIO[1]     | VIO                               | tristate                                | input          | input                      | tristate        | yes                 | weak PU            | yes | yes |  |

| GPIO Mod    | e: GPIO[1]                        | (input/outpu                            | t).            |                            |                 |                     |                    |     |     |  |

| This pin ca | n also be us                      | sed for 88W                             | 8987 Wi-Fi     | to host wake-up            | (out-of-band    | l wake-up s         | ignal).            |     |     |  |

| GPIO[0]     | VIO                               | tristate                                | output         | output high                | output low      | yes                 | nominal PU         | yes | no  |  |

| GPIO Mod    | e: GPIO[0]                        | input/outpu                             | t)             |                            | 1               | 1                   | 1                  | 1   |     |  |

|             |                                   |                                         | ,              | (active high). Se          | e Section 5.    | 5.9 "Clock i        | nterface".         |     |     |  |

- Not all GPIO pins can be used for Host-to-SoC wakeup signals.

Maximum input voltage is 0.4V when VIO has no power (or in uncertain situations).

- The signal may toggle while boot code is executing. When the device is in SDIO-SDIO mode. When the device is in SDIO-UART mode.

### 5.5.3 Wi-Fi/Bluetooth radio interface

## Table 6. Wi-Fi/Bluetooth radio interface - QFN package

| Pin Name | Туре   | Supply | Description                      |

|----------|--------|--------|----------------------------------|

| RF_TR_2  | A, I/O | AVDD18 | Wi-Fi Transmit/Receive (2.4 GHz) |

| RF_TR_5  | A, I/O | AVDD18 | Wi-Fi Transmit/Receive (5 GHz)   |

| BRF_ANT  | A, I/O | AVDD18 | Bluetooth Transmit/Receive       |

### Table 7. Wi-Fi/Bluetooth radio interface - eWLP package option

| Pin Name        | Туре   | Supply | Description                                                                                       |

|-----------------|--------|--------|---------------------------------------------------------------------------------------------------|

| RF_TR_2/BRF_ANT | A, I/O | AVDD18 | Wi-Fi Transmit/Receive (2.4 GHz) Bluetooth Transmit/Receive (shared path for Wi-Fi and Bluetooth) |

| RF_RX_5         | A, I   | AVDD18 | Wi-Fi Receive (5 GHz)                                                                             |

| RF_TX_5         | A, O   | AVDD18 | Wi-Fi Transmit (5 GHz)                                                                            |

### 5.5.4 Wi-Fi RF front-end control interface

### Table 8. Wi-Fi RF front-end control interface

| Pin Name                              | Supply       | No Pad<br>Power<br>State <sup>[1]</sup> | Reset<br>State | HW State           | PwrDwn<br>State | PwrDwn<br>Prog | Internal<br>PU/PD | PU | PD |

|---------------------------------------|--------------|-----------------------------------------|----------------|--------------------|-----------------|----------------|-------------------|----|----|

| RF_CNTL0_N                            | VIO_RF       | tristate                                | output         | output             | drive low       | yes            | nominal PU        | no | no |

| RF Control 0—RF                       | Control Outp | out Low (outp                           | ut)            |                    |                 |                |                   |    | ,  |

| RF_CNTL1_P                            | VIO_RF       | tristate                                | output         | output             | drive high      | yes            | weak PU           | no | no |

| RF Control 1—RF<br>This pin is used a |              | • .                                     | ,              | See <u>Sectior</u> | ı 5.6 "Configu  | ration pins".  |                   |    |    |

| RF_CNTL2_N                            | VIO_RF       | tristate                                | output         | output             | drive low       | yes            | weak PU           | no | no |

| RF Control 2—RF                       | Control Outp | out Low (outp                           | ut)            |                    | '               |                |                   |    | '  |

| RF_CNTL3_P                            | VIO_RF       | tristate                                | output         | output             | drive high      | yes            | weak PU           | no | no |

| RF Control 3—RF                       | Control Outp | out High (outp                          | out)           |                    |                 |                |                   |    |    |

<sup>[1]</sup> Maximum input voltage is 0.4V when VIO\_RF has no power (or in uncertain situations).

## 5.5.5 SDIO host interface

Table 9. SDIO host interface

| Supply | No Pad<br>Power<br>State <sup>[1]</sup>                                                                                                                                                                                         | Reset<br>State                                                                                                                                                                                                                                                                               | HW<br>State                                                                                                                                                                                                                                                                                                                                                                          | PwrDwn<br>State                                                                                                                                                                                                                                                                                                                                                                                                        | PwrDwn<br>Prog                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Internal PU/<br>PD                                                                                                                                                                                                                                                                                                                                                                                                                               | PU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | PD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VIO_SD | tristate                                                                                                                                                                                                                        | input                                                                                                                                                                                                                                                                                        | input                                                                                                                                                                                                                                                                                                                                                                                | tristate                                                                                                                                                                                                                                                                                                                                                                                                               | no                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | nominal PU                                                                                                                                                                                                                                                                                                                                                                                                                                       | yes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | yes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| •      |                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                      | '                                                                                                                                                                                                                                                                                                                                                                                                                      | ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                  | '                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| VIO_SD | tristate                                                                                                                                                                                                                        | input                                                                                                                                                                                                                                                                                        | input                                                                                                                                                                                                                                                                                                                                                                                | tristate                                                                                                                                                                                                                                                                                                                                                                                                               | no                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | nominal PU                                                                                                                                                                                                                                                                                                                                                                                                                                       | yes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | yes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|        | . ,                                                                                                                                                                                                                             | nput/output)                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

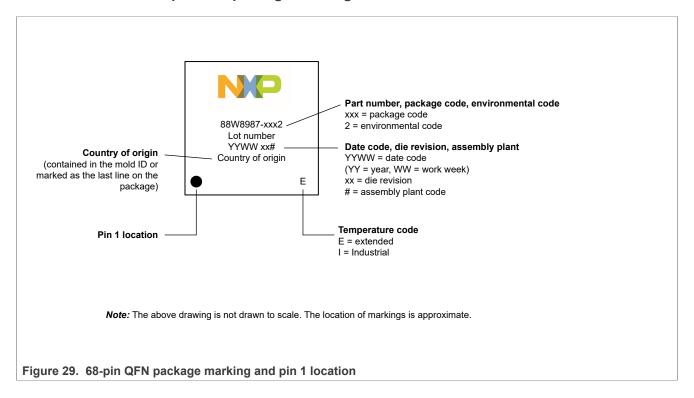

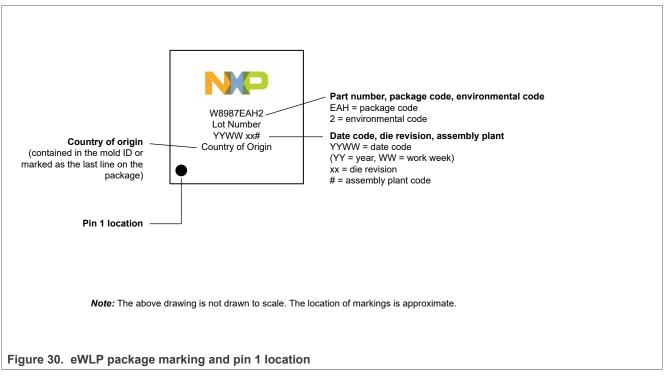

| VIO_SD | tristate                                                                                                                                                                                                                        | input                                                                                                                                                                                                                                                                                        | input                                                                                                                                                                                                                                                                                                                                                                                | tristate                                                                                                                                                                                                                                                                                                                                                                                                               | no                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | nominal PU                                                                                                                                                                                                                                                                                                                                                                                                                                       | yes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | yes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |