## Adaptive EQ 8-channel 960H Video Decoder

#### **General Features**

- → Real time AEQ 8-channel Video/Audio decoder for WD1(960H) and D1 cameras

- → Built-in Adaptive Equalizer(AEQ) for the best picture image in the several hundred meter coax cable condition

- → Proprietary Pericom AEQ technology recover weak, noisy, or unstable analog input signals

- → Resilient SYNC TIP detection to lock video signal in a noisy environment

- → Programmable sharpness, CTI, hue, saturation, contrast and brightness

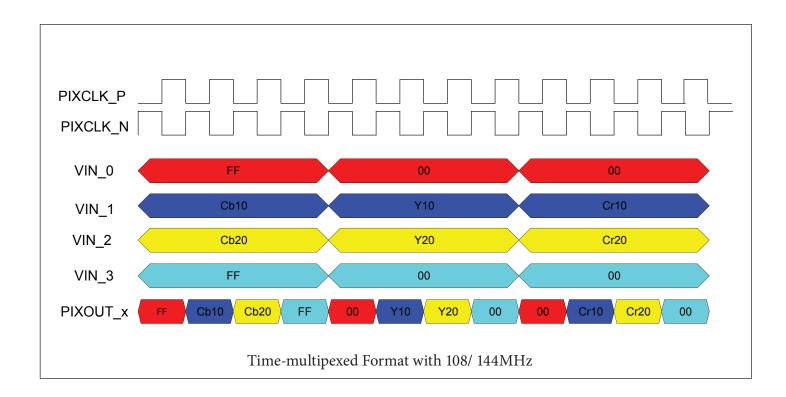

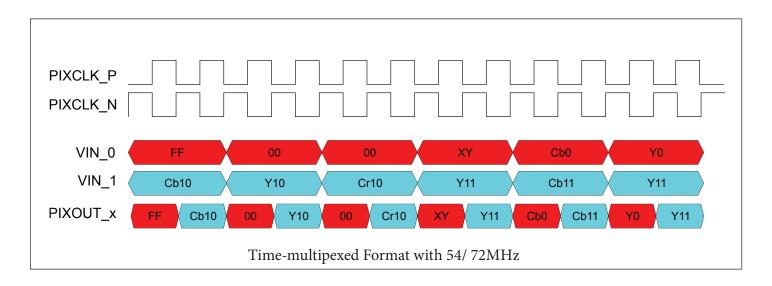

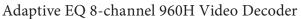

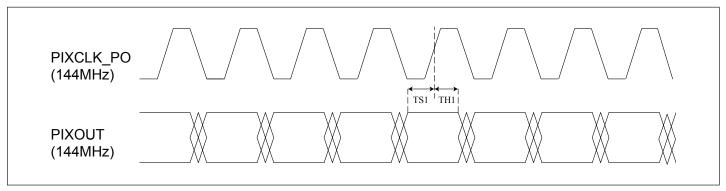

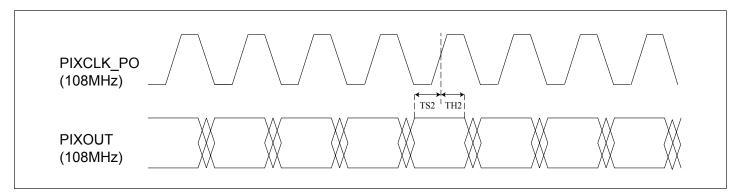

- → Support time multiplexed format of ITU-R BT.656 output with 54/108MHz or72/144MHz

- → Provides a programmable mapping from four or eight (non-real-time) analog video inputs to four BT.656 digital outputs

- → NTSC(M), NTSC 4.43, PAL (B, D, G, H, I, M, Nc, 60) standard support

- → High performance 5H comb filter for all NTSC/PAL standards

- → Built-in 10-bit audio Codec to allow 10 analog audio inputs and 1audio output

- → Mixed audio analog output for multiple audio channels with multiple audio sample rates for 8, 16, 32, 44.1, 48KHz audio frequency

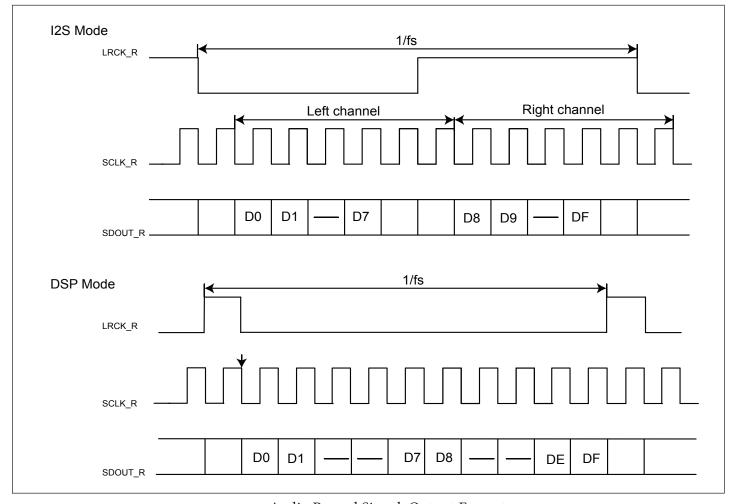

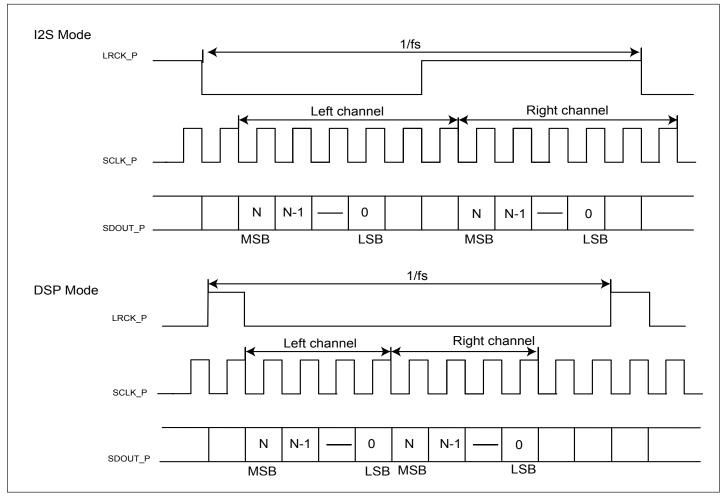

- → Two serial audio formats (I2S and DSP) are supported for recording/mixing output and playback input

- → Selectable Master and Slave serial audio interface

- → Integrated video PLL for 108MHz, 144MHz clock output

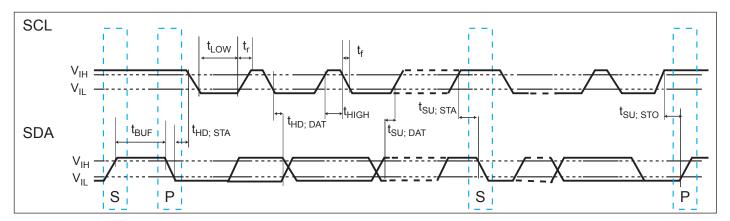

- → Two-wire serial interface(I2C) for register access

- → Industrial grade temperature support (-40°C ~ 85°C)

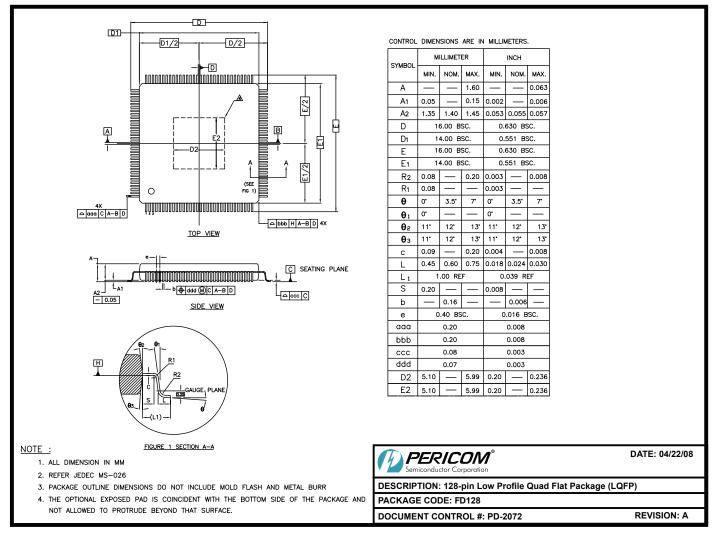

- → Packages: 128-pin LQFP

#### **Description**

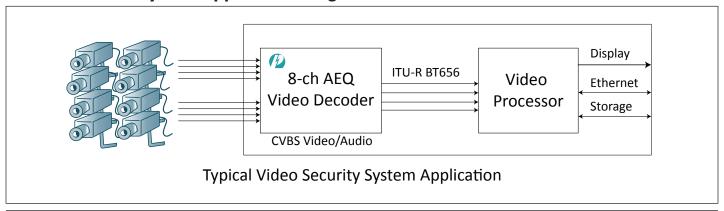

PI7VD9008ABH is AEQ 8-Channel Video Decoders and Audio Codec. Built-in Adaptive equalizer (AEQ) recover the noisy signals caused by long or small wire gauge Coax cables and display the best picture image view quality. The video decoder converts NTSC, PAL analog composite video broadcasting signal (CVBS) into digital components YCbCr for video controller or processor to perform pre-view, compression and storage etc. The converted digital video streams complying with ITU-R BT.656 are transported in time multiplexed format, which contains one, two or four video channels.

Single 27MHz reference crystal clock support NTSC, PAL and 960H standard resolution. Each video channel contains 10-bit ADC, proprietary clamp, automatic gain controller and 5H comb filter for separating luminance & chrominance to reduce artificial noise.

#### **Application**

- → Video Security DVRs

- → Automotive Camera Driver Assistant Systems

- → Video Capture Cards

## PI7VD9008ABH System Application Diagram

14-0207 www.pericom.com 12/12/14

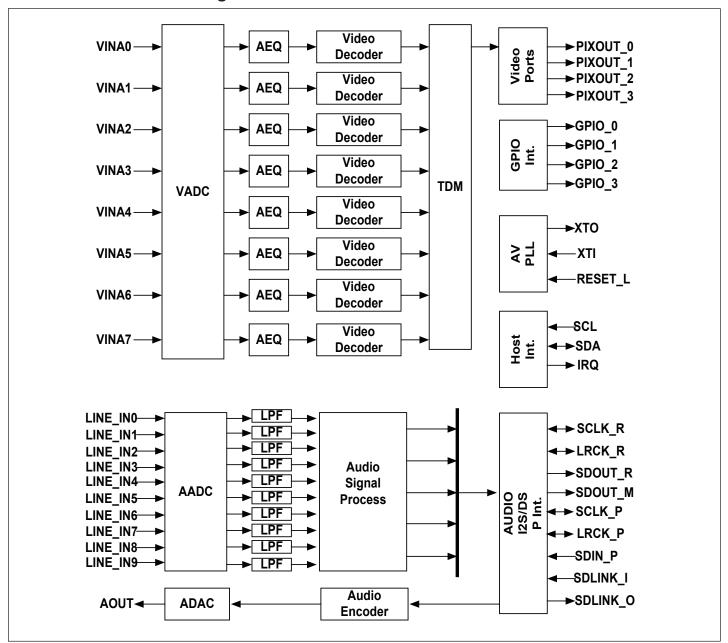

#### PI7VD9008ABH Block Diagram

| Video input sources:    | CV_INA0, CV_INA1, CV_INA2, CV_INA3, CV_INA4, CV_INA5, CV_INA6, CV_INA7                        |

|-------------------------|-----------------------------------------------------------------------------------------------|

| BT.656 TDM ports:       | PIXOUT_0, PIXOUT_1, PIXOUT_2 and PIXOUT_3                                                     |

| Audio input sources:    | LINE_IN0, LINE_IN1, LINE_IN2, LINE_IN3, LINE_IN4,LINE_IN5,LINE_IN6,LINE_IN7,LINE_IN8,LINE_IN9 |

| I2S/DSP Audio Interface | (SCLK_R, LRCK_R, SDOUT_R and SDOUT_M), (SCLK_P, LRCK_P and SDIN_P), (SD_LIN-KI, SD_LINKO)     |

12/12/14 www.pericom.com 14-0207 2

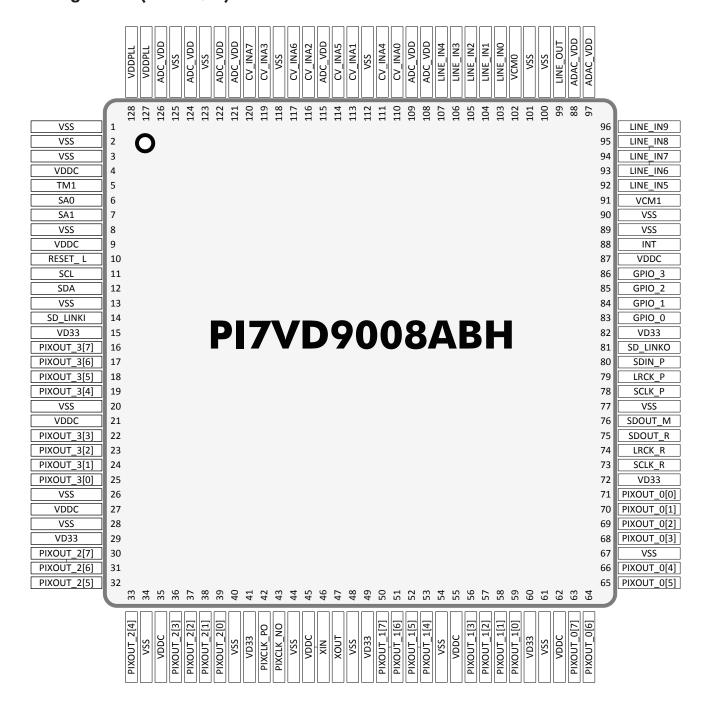

#### Pin Configuration(128-LQFP)

## **PI7VD9008ABH**Adaptive EQ 8-channel 960H Video Decoder

## Pin Configuration (128-LQFP)

| Pin | Name        | Pin | Name        | Pin | Name        | Pin | Name     |

|-----|-------------|-----|-------------|-----|-------------|-----|----------|

| 1   | VSS         | 33  | PIXOUT_2[4] | 65  | PIXOUT_0[5] | 97  | ADAC_VDD |

| 2   | VSS         | 34  | VSS         | 66  | PIXOUT 0[4] | 98  | ADAC VDD |

| 3   | VSS         | 35  | VDDC        | 67  | VSS         | 99  | LINE_OUT |

| 4   | VDDC        | 36  | PIXOUT_2[3] | 68  | PIXOUT_0[3] | 100 | VSS      |

| 5   | TM1         | 37  | PIXOUT_2[2] | 69  | PIXOUT_0[2] | 101 | VSS      |

| 6   | SA0         | 38  | PIXOUT_2[1] | 70  | PIXOUT_0[1] | 102 | VCM0     |

| 7   | SA1         | 39  | PIXOUT 2[0] | 71  | PIXOUT 0[0] | 103 | LINE INO |

| 8   | VSS         | 40  | VSS         | 72  | VD33        | 104 | LINE IN1 |

| 9   | VDDC        | 41  | VD33        | 73  | SCLK R      | 105 | LINE IN2 |

| 10  | RESET_L     | 42  | PIXCLK_PO   | 74  | LRCK_R      | 106 | LINE_IN3 |

| 11  | SCL         | 43  | PIXCLK_NO   | 75  | SDOUT_R     | 107 | LINE_IN4 |

| 12  | SDA         | 44  | VSS         | 76  | SDOUT_M     | 108 | ADC_VDD  |

| 13  | VSS         | 45  | VDDC        | 77  | VSS         | 109 | ADC_VDD  |

| 14  | SD_LINKI    | 46  | XIN         | 78  | SCLK_P      | 110 | CV_INA0  |

| 15  | VD33        | 47  | XOUT        | 79  | LRCK_P      | 111 | CV_INA4  |

| 16  | PIXOUT_3[7] | 48  | VSS         | 80  | SDIN_P      | 112 | VSS      |

| 17  | PIXOUT_3[6] | 49  | VD33        | 81  | SD_LINKO    | 113 | CV_INA1  |

| 18  | PIXOUT_3[5] | 50  | PIXOUT_1[7] | 82  | VD33        | 114 | CV_INA5  |

| 19  | PIXOUT_3[4] | 51  | PIXOUT_1[6] | 83  | GPIO_0      | 115 | ADC_VDD  |

| 20  | VSS         | 52  | PIXOUT_1[5] | 84  | GPIO_1      | 116 | CV_INA2  |

| 21  | VDDC        | 53  | PIXOUT_1[4] | 85  | GPIO_2      | 117 | CV_INA6  |

| 22  | PIXOUT_3[3] | 54  | VSS         | 86  | GPIO_3      | 118 | VSS      |

| 23  | PIXOUT_3[2] | 55  | VDDC        | 87  | VDDC        | 119 | CV_INA3  |

| 24  | PIXOUT_3[1] | 56  | PIXOUT_1[3] | 88  | INT         | 120 | CV_INA7  |

| 25  | PIXOUT_3[0] | 57  | PIXOUT_1[2] | 89  | VSS         | 121 | ADC_VDD  |

| 26  | VSS         | 58  | PIXOUT_1[1] | 90  | VSS         | 122 | ADC_VDD  |

| 27  | VDDC        | 59  | PIXOUT_1[0] | 91  | VCM1        | 123 | VSS      |

| 28  | VSS         | 60  | VD33        | 92  | LINE_IN5    | 124 | ADC_VDD  |

| 29  | VD33        | 61  | VSS         | 93  | LINE_IN6    | 125 | VSS      |

| 30  | PIXOUT_2[7] | 62  | VDDC        | 94  | LINE_IN7    | 126 | ADC_VDD  |

| 31  | PIXOUT_2[6] | 63  | PIXOUT_0[7] | 95  | LINE_IN8    | 127 | VDDPLL   |

| 32  | PIXOUT_2[5] | 64  | PIXOUT_0[6] | 96  | LINE_IN9    | 128 | VDDPLL   |

14-0207 4 www.pericom.com 12/12/14

### **Pin-out Information**

### Analog Video/Audio Interface

| Pin Name  | Pin Number | Type   | Description                      |

|-----------|------------|--------|----------------------------------|

| CV_INA0,  | 110,       |        | CVBS input of Video channel 0    |

| CV_INA4,  | 111,       |        | CVBS input of Video channel 4    |

| CV_INA1,  | 113,       |        | CVBS input of Video channel 1    |

| CV_INA5,  | 114,       | Amalaa | CVBS input of Video channel 5    |

| CV_INA2,  | 116,       | Analog | CVBS input of Video channel 2    |

| CV_INA6,  | 117,       |        | CVBS input of Video channel 6    |

| CV_INA3,  | 119,       |        | CVBS input of Video channel 3    |

| CV_INA7   | 120        |        | CVBS input of Video channel 7    |

| VCM0,     | 102,       | A 1    |                                  |

| VCM1      | 91         | Analog | Connect to an external capacitor |

| LINE_IN0, | 103,       |        | Line input of Audio channel 0    |

| LINE_IN1, | 104,       |        | Line input of Audio channel 1    |

| LINE_IN2, | 105,       |        | Line input of Audio channel 2    |

| LINE_IN3, | 106,       |        | Line input of Audio channel 3    |

| LINE_IN4  | 107        | A1     | Line input of Audio channel 4    |

| LINE_IN5, | 92         | Analog | Line input of Audio channel 5    |

| LINE_IN6, | 93         |        | Line input of Audio channel 6    |

| LINE_IN7, | 94         |        | Line input of Audio channel 7    |

| LINE_IN8, | 95         |        | Line input of Audio channel 8    |

| LINE_IN9  | 96         |        | Line input of Audio channel 9    |

| LINE_OUT  | 99         | Analog | Mixed Analog Audio Output        |

## Digital Video/Audio Interface

| Pin Name      | Pin Number                     | Type   | Description                                                                                           |

|---------------|--------------------------------|--------|-------------------------------------------------------------------------------------------------------|

| PIXOUT_0[7:0] | 63, 64, 65, 66,68,69, 70,71    | Output | Bt.656 Time Multiplex Division output of port 0                                                       |

| PIXOUT_1[7:0] | 50, 51, 52, 53, 56,57,58,59    | Output | Bt.656 Time Multiplex Division output of port 1                                                       |

| PIXOUT_2[7:0] | 30, 31, 32, 33, 36, 37, 38, 39 | Output | Bt.656 Time Multiplex Division output of port 2                                                       |

| PIXOUT_3[7:0] | 16, 17, 18, 19, 22, 23, 24, 25 | Output | Bt.656 Time Multiplex Division output of port 3                                                       |

| GPIO_0        | 83                             | Output | According to register setting, it outputs GPO, HSYC, VSYNC, FDFLAG, ACTIVE and VDLOSS of channel 0, 4 |

| GPIO_1        | 84                             | Output | According to register setting, it outputs GPO, HSYC, VSYNC, FDFLAG, ACTIVE and VDLOSS of channel 1, 5 |

| GPIO_2        | 85                             | Output | According to register setting, it outputs GPO, HSYC, VSYNC, FDFLAG, ACTIVE and VDLOSS of channel 2, 6 |

| GPIO_3        | 86                             | Output | According to register setting, it outputs GPO, HSYC, VSYNC, FDFLAG, ACTIVE and VDLOSS of channel 3, 7 |

14-0207 5 www.pericom.com 12/12/14

# **PI7VD9008ABH** Adaptive EQ 8-channel 960H Video Decoder

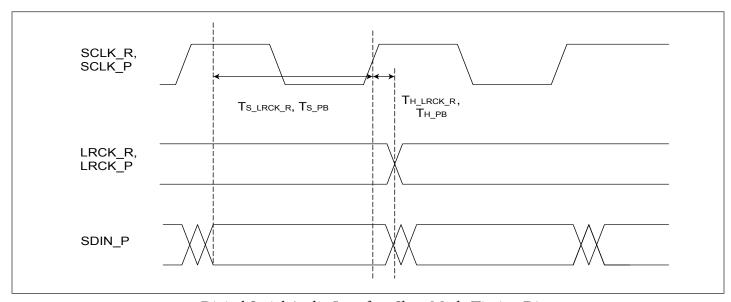

| SCLK_R   | 73 | Input/<br>Output | Record audio serial clock. It is an input pin under slave mode, while output pin under master mode.        |

|----------|----|------------------|------------------------------------------------------------------------------------------------------------|

| LRCK_R   | 74 | Input/<br>Output | Record audio serial sync pulse. It is an input pin under slave mode, while output pin under master mode.   |

| SDOUT_R  | 75 | Output           | Record audio serial data output.                                                                           |

| SDOUT_M  | 76 | Output           | Mixing audio serial data output.                                                                           |

| SCLK_P   | 78 | Input/<br>Output | Playback audio serial clock. It is an input pin under slave mode, while output pin under master mode       |

| LRCK_P   | 79 | Input/<br>Output | Playback audio serial sync pulse. It is an input pin under slave mode, while output pin under master mode. |

| SDIN_P   | 80 | Input            | Playback audio serial data input.                                                                          |

| SD_LINKI | 14 | Input            | Chip-to-Chip audio serial data input.                                                                      |

| SD_LINKO | 81 | Output           | Chip-to-Chip audio serial data output.                                                                     |

## **System Control Interface**

| Pin Name  | Pin Number | Туре          | Description                                                                                                    |

|-----------|------------|---------------|----------------------------------------------------------------------------------------------------------------|

| RESET_L   | 10         | Input         | Chip Reset. Active Low.                                                                                        |

| XIN       | 46         | Input         | 27MHz or 54MHz crystal input or 27MHz/54MHz/108MHz oscillator input                                            |

| XOUT      | 47         | Output        | 27MHz or 54MHz crystal output                                                                                  |

| PIXCLK_P0 | 42         | Output        | Positive Output clock signal running at 27/54/108MHz (720H mode) or 36/72/144MHz (960H mode) for bus PIXOUT_0. |

| PIXCLK_N0 | 43         | Output        | Negative Output clock signal running at 27/54/108MHz (720H mode) or 36/72/144MHz (960H mode) for bus PIXOUT_0  |

| TM1       | 5          | Input         | Test pin. Tied to VSS.                                                                                         |

| SA1       | 7          | Input         | Device Address 1 of I2C slave interface                                                                        |

| SA0       | 6          | Input         | Device Address 0 of I2C slave interface                                                                        |

| SCL       | 11         | Input         | Input clock signal of I2C slave interface                                                                      |

| SDA       | 12         | Input/ Output | Data signal of I2C slave interface                                                                             |

| INT       | 88         | Output        | Interrupt signal to system. Active High.                                                                       |

12/12/14 www.pericom.com 14-0207 6

#### **Power and Ground**

| Pin Name | Pin Number                                                                                                      | Туре   | Description                                                             |

|----------|-----------------------------------------------------------------------------------------------------------------|--------|-------------------------------------------------------------------------|

| VDDC     | 4, 9, 21, 27, 35,<br>45, 55, 62, 87                                                                             | Power  | 1.0V Power for core logic                                               |

| VD33     | 15, 29, 41, 49, 60,<br>72, 82                                                                                   | Power  | 3.3V Power for IO pads                                                  |

| VSS      | 1, 2, 3, 8, 13, 20,<br>26, 28, 34, 40,<br>44, 48, 54, 61,<br>67, 77, 89, 90,<br>100, 101, 112,<br>118, 123, 125 | Ground | Ground for video ADC, audio ADC, audio DAC, PLL, core logic and IO pads |

| ADC_VDD  | 108, 109, 115,<br>121, 122, 124,<br>126                                                                         | Power  | 3.3V Power for video ADC and audio ADC.                                 |

| ADAC_VDD | 97, 98                                                                                                          | Power  | 3.3V Power for audio DAC                                                |

| VDDPLL   | 127, 128                                                                                                        | Power  | 3.3V Power for AV PLL                                                   |

#### **Functional Description**

#### Video/Audio Analog Input

PI7VD9004ABH offers4 channels NTSC, PAL (720H or 960H) format composite (CVBS) inputs(CV INAx x = 0,1,2,3,4,5,6,7). When the input signal is weak and the color burst is not able to be recognized, the video is automatically switched to Black and White mode to enhance the picture image quality.

| Format      | Lines | Field | Fsc          | Country                               |

|-------------|-------|-------|--------------|---------------------------------------|

| NTSC-M      | 525   | 60    | 3.579545 MHz | U.S., many others                     |

| NTSC-Japan  | 525   | 60    | 3.579545 MHz | Japan *                               |

| NTSC (4.43) | 525   | 60    | 4.433619 MHz | Transcoding                           |

| PAL-B, G, N | 625   | 50    | 4.433619 MHz | Many                                  |

| PAL-I /H /D | 625   | 50    | 4.433619 MHz | Belgium ,China Great Britain, oth ers |

| PAL-M       | 525   | 60    | 3.575612 MHz | Brazil                                |

| PAL-CN      | 625   | 50    | 3.582056 MHz | Argentina                             |

| PAL-60      | 525   | 60    | 4.433619 MHz | China                                 |

<sup>\*</sup> PNTSC-Japan has 0 IRE setup

#### Clamping and Automatic Gain Control

Each analog input channel has built-in clamping circuits to restore signal DC level. Automatic Gain Control (AGC) circuits in the internal video processor can compensate average input video signal level for each analog input channel. The AGC and clamping circuits prevent signal level saturation and allow the video decoder to deliver the best signal-to-noise performance. On the other hand, the AGC cooperates with the digital multiplier of video decoder to boost the weak signals. The circuits perform Automatic Gain Control through internal feedback look. Manual gain control is also available through configuring the Video Decoder Control and Status Registers.

#### Video Decoder

EThe video decoder in the chip converts NTSC and PAL video signals to 8-bit ITU-R BT.656 format. The chip includes four high speed and low power 10-bit analog-to-digital converters (ADC) with 2x sampling rate to support 4-channel video decoding. When the incoming video is in the 720H format, the sampling rate is 27MHz or 54MHz by 2x factor. For 960H format, the sampling rate is 36MHz or 72MHz by 2x factor. The chip implements proprietary circuit design that is optimized for locking in weak, noisy, or unstable signals. The minimal signal voltage that can be locked in is at 160/80 mV.

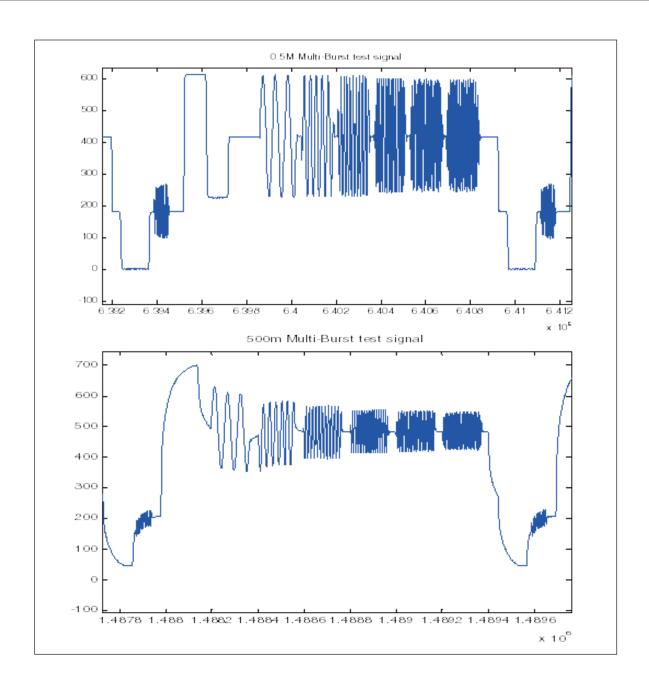

#### Adaptive Equalization

EThe CVBS is suffered from channel loss by an extended transmission distance (greater than 500m) and a small diameter (less than 0.5mm) of CCTV cable. The distortion on CVBS after the energy reduction effect of cable length is illustrated as below. For example, a Multi-Burst test signal is respectively measured at 0.5m and 500m of cable. It appears that color burst and sync tip have sever degration after 500m transmission distance. Adaptive equalization on the distorted CVBS recovers the signal back to close to the original level. Since the different cable conditions present various effects on CVBS picture image, the adaptive equalization provides to compensate the signal loss on some frequency components pertinent to the Coax cable.

### Comb filter and Y/C Separation

The video decoder is capable of separating luma (Y) and chroma (C) of NTSC or PAL video signals using 5-line adaptive comb filter or notch/band-pass filter. The comb filter searches for correlation between 5 lines of input video stored in the internal buffer. The lines are averaged based on the degree of correlation to produce the output video line. If no correlation is found between the 5 lines of video, notch/band-pass filter is used. This process is very effective at reducing cross-luma and cross-chroma noise. The noise appears as artifacts that degrade the image quality. Reduction of the noise improves the image quality significantly.

#### **Video Signal Processing**

The chip is capable of processing digital video signal to fulfill better detection in a noisy environment and achieve good image quality for viewing as well. For video signal detection, a resilient SYNC TIP detection mechanism is implemented to locate VSYNC and HSYNC correctly in order to lock the video frame or video line.

In general, the poor power adaptor or camera would introduce high frequency ripples coupling with sync tip to cause the misjudgment on the beginning of a video frame or line. The built-in video processing circuit is able to decouple the noise from sync tip to prevent from video loss.

A sharpness filter is implemented to offer programmable 16 level gains to increase the high frequency and edge information of luma for better viewing on the contour of each object. Through the I2C serial interface, hue, contrast, brightness and saturation can be programmed in the configuration registers. Hue can be controlled in 256 steps from -180 degrees to +180 degrees. Saturation can be programmed in 256 grades. Brightness can be adjusted in 256 levels.

#### **Video Output Port**

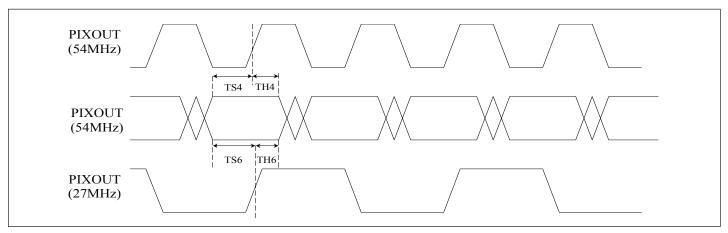

The four CVBS analog video channels are converted into four individual digital video data streams. There are four video output ports (PIXOUT\_0, PIXOUT\_1, PIXOUT\_2 and PIXOUT\_3) in the chip and each video output port can carry several converted digital video data stream following ITU-R BT.656 compatible data format. The video data of each port is synchronous with the corresponding clock signals of PIXCLK\_PO or PIXCLK\_NO. The frequency of PIXCLK\_\*O can be operated at 1x, 2x or 4x of 27MHz (720H mode) or 36MHz (960H mode). When the clock frequency is 2x or 4x rate, the video port outputs 2-channel or 4-channel video data stream in time-multiplexed format. The clock phase of PIXCLK\_POorPIXCLK\_NOcanbe programmed by delay cells through writing delay value into the registers of PIXCLK\_P\_DEL or PIXCLK\_N\_DEL. Also, the clock polarity can be controlled through inverter by setting or resetting the register of PIXCLK\_P\_POL or PIXCLK\_N\_POL. The flexibility on changing clock phase or polarity facilitates the timing design for video data stream on PCB.

#### ANALOG AUDIO INPUT

The audioADC offers 5 channels of analog inputs (LINE\_INx, x= 0, 1, 2, 3, 4, 5, 6, 7, 8, 9) with a peak-to-peak voltage range from 0.5V to 2V. Each input channel contains 4-bit programmable gain amplifier and an ADC with maximum over-sampling speed of 3.6M Sample/s. A pseudo differential input is used to minimize board level noise problems. The converted audio data stream is fed into a low pass filter to decimate audio sample at an appropriate audio sampling rate such as 8 KHz, 16 KHz, 32 KHz, 44.1 KHz and 48 KHz etc.

#### **AUDIO PROCESSING**

The audio processor accepts 5 digital audio streams from audio ADC. It also receives 2 additional digital serial audio data from pins. One digital serial audio data is SDIN\_P coming from AV compression processor, while the other one is SD\_LINKI coming from companion device.

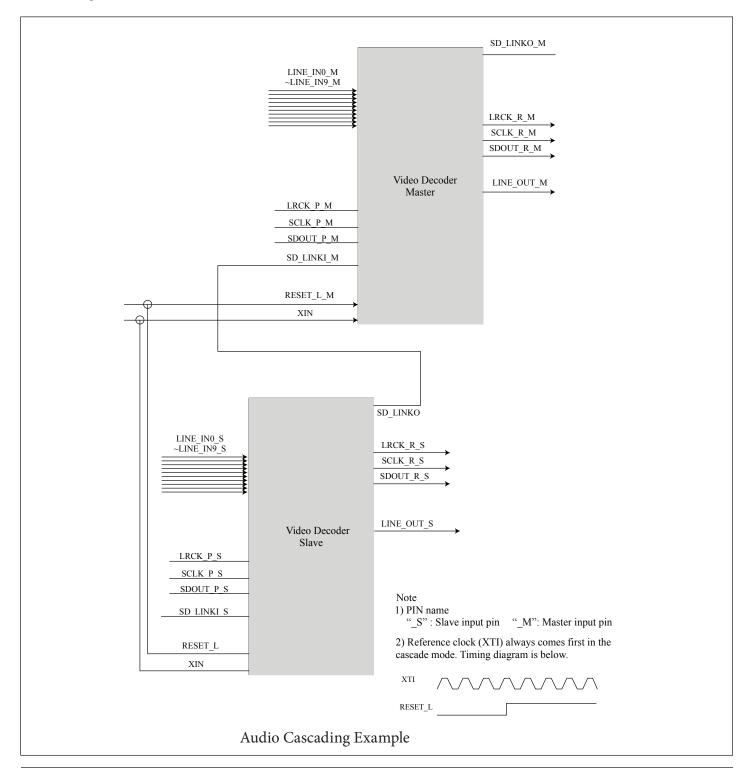

SDIN\_P represents the decompressed audio data for playback purpose. SD\_LINKI is used to cascade with digital audio outputs from one other PI7VD9008ABH chips for forming one timing multiplexed I2S digital serial audio data containing 8 or 10 digital audio channels. This device processes these 10 digital audio streams and 2 digital serial audio data, then generates one mixing analog audio signal and three digital serial audio data to fulfill the functions of mixing, recording and cascading etc.

For audio mixing, this device has both analog and digital format. The built-in mixer selects among all audio input data to generate the mixing digital audio data (SDOUT\_M), which connects to audio DAC for converting to mixing analog audio signal output (LINE\_OUT).

For audio recording, the audio processor performs multiplexing over 16 digital audio streams in timing division way to generate record digital audio output data (SDOUT\_R). For the digital serial audio data SDOUT\_R and SDOUT\_M, they are both synchronized with SCLK\_R and LRCK\_R. As to SDIN\_P, it is synchronized with SCLK\_P and LRCK\_P. These digital serial audio data support two formats of I2S and DSP that can be selected by control bits RM\_SYNC in the register at offset 0xD2 and PB\_SYNC in the register at offset 0xDB. Meanwhile, the record and playback digital serial audio interfaces of PI7VD9008ABH can be acted as Master or Slave mode based upon the setting of ACLKRMASTER and PB\_MASTER bits in the register at offset 0xDB

This device supports audio system clock with 256fs or 320fs mode, which is controlled by AIN5MD register. The record output pin contains several channel inputs that can be defined by the registers at offset of  $0xD2 \sim 0xDA$  describing the number and sequence of recorded audio streams. It supports 8bit and 16bit record data width for trading off between higher audio qualities and saving disk storage space. By controlling bit2 of register at offset 0xDB, the chip allows to select the output record data width to be either 8-bit or 16-bit mode.

Audio Record Signal Output Format

Playback Input Format

#### PI7VD9008ABH Cascade Mode

For audio cascading, the chip redirects SDOUT\_R as SD\_LINKO to connect with SD\_LINKI of another PI7VD9008AB product, which cascades its original SDOUT\_R and SD\_LINKI to create a new SDOUT\_R. PI7VD9008ABcan support 16 channel data output on first level chip recordoutput pin for saving pin layout on PCB board. The cascade chips have to use same crystal clock source and same reset signal.

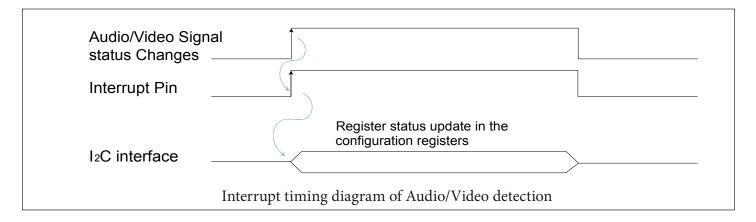

#### **I2C Host Interface**

The processor can access the internal register by executing read or write command to the indexed locations to implement the function of detecting audio and video signal and reveals the detection status through the configuration registers. If any audio or video channel is present or absent, interrupt pin (INT) can notify the status to the processor to manage CPU resource effectively by polling the status. The chip supports flexibilities to select various detection modes and enable individual audio/video channel for generating interrupt.

These control bits to interrupt pin are defined in the registers of AVDET\_MODE, AVDET1\_ENA, AVDET2\_ENA, A51DET\_ENA and A52DET\_ENA.

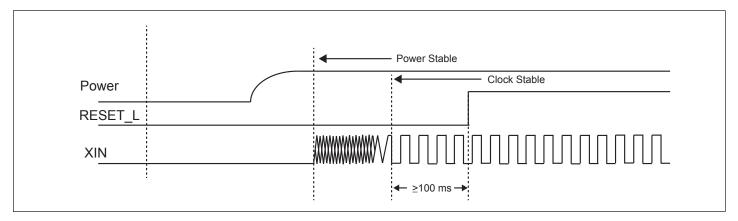

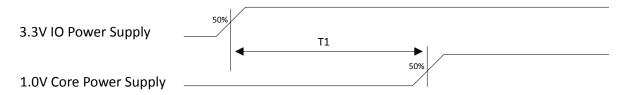

#### **Power Sequence**

The power supply should be turned on first. After the power is turned on, the clock signal should be supplied. Finally, after both power and clock signals are turned on, the RESET\_L signal is turned to HIGH to complete the power sequence.

## **CONFIGURATION, CONTROL AND STATUS REGISTER MAP**

## PAGE\_0 REGISTER MAP ( address 40h =00h)

| Address               | Function                                       |

|-----------------------|------------------------------------------------|

| 00h/10h/20h/30h (00h) | Video Status                                   |

| 01h/11h/21h/31h (00h) | Brightness Control                             |

| 02h/12h/22h/32h (64h) | Contrast Control                               |

| 03h/13h/23h/33h (00h) | Sharpness Control                              |

| 04h/14h/24h/34h (80h) | Chroma (U) Gain                                |

| 05h/15h/25h/35h (80h) | Chroma (V) Gain                                |

| 06h/16h/26h/36h (00h) | Hue Control                                    |

| 07h/17h/27h/37h       | Reserved                                       |

| 08h/18h/28h/38h       | Reserved                                       |

| 09h/19h/29h/39h       | Reserved                                       |

| 0Ah/1Ah/2Ah/3Ah       | Hdelay                                         |

| 0Bh/1Bh/2Bh/3Bh       | Reserved                                       |

| 0Ch/1Ch/2Ch/3Ch       | Reserved                                       |

| 0Dh/1Dh/2Dh/3Dh       | Reserved                                       |

| 0Eh/1Eh/2Eh/3Eh (77h) | Standard Selection                             |

| 0Fh/1Fh/2Fh/3Fh       | Reserved                                       |

| 40h-50h               | Reserved                                       |

| 51h (00h)             | F-Bit of SAV/EAV Inverted                      |

| 52h-55h               | Reserved                                       |

| 56h                   | Blanking Length of Horizontal Line             |

| 57h/58h/59h/5Ah (90h) | Blanking Length of Horizontal Line             |

| 5Bh-5Ch               | Reserved                                       |

| 5Dh(C0h)              | Vin2 Color Kill Enable                         |

| 5Eh(C0h)              | Vin2 Color Kill Enable  Vin3 Color Kill Enable |

| 5Fh(C0h)              | Vin4 Color Kill Enable                         |

| 60h                   | Reserved                                       |

| 61h (03h)             | Crystal Clock Select                           |

| 62h (00h)             | GPIO Output Enable                             |

| 63h (10h)             | ID for Video Channel 0&1                       |

| 64h (32h)             | ID for Video Channel 2&3                       |

| 65h (54h)             | ID for Video Channel 4&5                       |

| 66h (76h)             | ID for Video Channel 6&7                       |

| 67h(80h)              | HZOOM Enable                                   |

| 68h(00h)              | HI-Bits of 1234 HZOOM                          |

| 69h(00h)              | LOW-Bits of 1 HZOOM                            |

| 6Ah(00h)              | LOW-Bits of 2 HZOOM                            |

| 6Bh(00h)              | LOW-Bits of 3 HZOOM                            |

| 6Ch(00h)              | LOW-Bits of 4 HZOOM                            |

| 6Dh-6Dh               | Reserved                                       |

| 6Fh(00h)              | Video Output Enable                            |

| 70h (08h)             | Audio Clock Control                            |

| 71h (00h)             | I2S Audio Input Control                        |

| 711 (0011)<br>72h     | Reserved                                       |

| 73h(00h)              | LINE_IN4_Control                               |

| 74h(00h)              | LINE IN4 Detect Enable                         |

| 75h-7Ah               | Reserved                                       |

| 7Bh (00h)             | SDOUT_M Select (R)                             |

| 7Ch (00h)             | SDOUT_M Select (R) SDOUT_M Select (L)          |

| 7Dh (E4h)             | Extended Line Select                           |

| 7Dh (E4h)<br>7Eh      | SDOUT M I2S                                    |

| 7Fh (00h)             |                                                |

| [/ FII (UUII)         | Mix Ratio LINE_IN4                             |

14-0207 16 www.pericom.com 12/12/14

| Address                | Function                                                |

|------------------------|---------------------------------------------------------|

| 80h (00h)              | Software Reset                                          |

| 81h-88h                | Reserved                                                |

| 89h (00h)              | Audio FS Mode                                           |

| 8Ah-95h                | Reserved                                                |

| 96h(C0h)               | Vin1 Color Kill Enable                                  |

| 97h-9Eh                | Reserved                                                |

| 9Fh (00h)              | PIXCLK 0Delay                                           |

| A0h-B1h                | Reserved                                                |

| B2h (00h)              | Vin1~Vin8 Video Loss Status                             |

| B3h-C7h                | Reserved                                                |

| C8h (00h)              | GPIO 0 1 Mode                                           |

| C9h (00h)              | GPIO_2_3 Mode                                           |

| CAh (55h)              | Reserved                                                |

| CBh (00h)<br>CCh (00h) | GPIO Polarity Reserved                                  |

| CDh (00h)              | WD1,D1 Select                                           |

| CEh (0011)             | Reserved                                                |

| CFh (00h)              | Serial Mode Control                                     |

| D0h-D1h                | Reserved                                                |

| D2h (03h)              | SDOUT RM Output                                         |

| D3h (10h)              | SDOUT_R_SEQ_1_0                                         |

| D4h(32h)               | SDOUT R SEQ 3 2                                         |

| D5h (54h)              | SDOUT_R_SEQ_5_4                                         |

| D6h (76h)              | SDOUT R SEQ 7 6                                         |

| D7h (98h)              | SDOUT_R_SEQ_9_8                                         |

| D8h (BAh)              | SDOUT_R_SEQ_B_A                                         |

| D9h (DCh)              | SDOUT_R_SEQ_D_C                                         |

| DAh (FEh)              | SDOUT R SEQ F E                                         |

| DBh (C2h)              | I2S Master Control                                      |

| DCh(10h)               | MIX MUTE Control                                        |

| DDh (00h)              | Mix Ratio 0 & 1                                         |

| DEh (00h)              | Mix Ratio 2 & 3                                         |

| DFh (08h)              | PB Ratio                                                |

| E0h (14h)              | Mixing Output Control                                   |

| E1h (00h)              | Audio Detect Threshold 0123 MSB                         |

| E2h (aah)              | Audio Detect Threshold 01 LSB                           |

| E3h (aah)              | Audio Detect Threshold 23 LSB                           |

| E4h-E6h                | Reserved                                                |

| E7h(55h)               | VD0~VD4 Output Mode                                     |

| E8h (10h)              | PIXOUT_0 Output CH12 Select                             |

| E9h (32h)              | PIXOUT_0 Output CH34 Select                             |

| EAh (32h)              | PIXOUT_1 Output CH12 Select                             |

| EBh (54h)              | PIXOUT_1 Output CH34 Select                             |

| ECh (54h)              | PIXOUT_2 Output CH12 Select                             |

| EDh (76h)              | PIXOUT_2 Output CH34 Select                             |

| EEh (76h)<br>EFh (10h) | PIXOUT_3 Output CH12 Select PIXOUT_3 Output CH34 Select |

| F0h-F8 h               | Reserved                                                |

| F9h (00h)              | PIXCLK Output Mode                                      |

| FAh (00h)              | CCIR656 Control                                         |

| FBh (0Fh)              | Clock Polarity                                          |

| FCh (FFh)              | AV Detection Enable                                     |

| FDh (00h)              | AV Detection Status                                     |

| FEh (00h)              | Device ID_H                                             |

| FFh (F0h)              | Device ID_II                                            |

| 11 (1 011)             | 12 0 1 100 12 <u>-</u> 21                               |

## PAGE\_0 REGISTER MAP (address 40h =01h)

| Address               | Function                           |

|-----------------------|------------------------------------|

| 00h/10h/20h/30h (00h) | Video Status                       |

| 01h/11h/21h/31h (00h) | Brightness Control                 |

| 02h/12h/22h/32h (64h) | Contrast Control                   |

| 03h/13h/23h/33h (00h) | Sharpness Control                  |

| 04h/14h/24h/34h (80h) | Chroma (U) Gain                    |

| 05h/15h/25h/35h (80h) | Chroma (V) Gain                    |

| 06h/16h/26h/36h (00h) | Hue Control                        |

| 0Ah/1Ah/2Ah/3Ah       | Hdelay                             |

| 0Eh/1Eh/2Eh/3Eh (77h) | Standard Selection                 |

| 56h                   | Blanking Length of Horizontal Line |

| 57h/58h/59h/5Ah (90h) | Blanking Length of Horizontal Line |

| 5Dh(C0h)              | Vin6 Color Kill Enable             |

| 5Eh(C0h)              | Vin7 Color Kill Enable             |

| 5Fh(C0h)              | Vin8 Color Kill Enable             |

| 68h(00h)              | HI-Bits of 5 6 7 8HZOOM            |

| 69h(00h)              | LOW-Bits of 5 HZOOM                |

| 6Ah(00h)              | LOW-Bits of 6 HZOOM                |

| 6Bh(00h)              | LOW-Bits of 7 HZOOM                |

| 6Ch(00h)              | LOW-Bits of 8 HZOOM                |

| 73h(00h)              | LINE_IN9 Control                   |

| 74h(00h)              | LINE_IN9 Detect Enable             |

| 7Eh                   | LINE_IN9 Detect Threshold          |

| 7Fh (00h)             | Mix Ratio LINE_IN9                 |

| 96h(C0h)              | Vin5 Color Kill Enable             |

| C8h (00h)             | GPIO_4_5 Mode                      |

| C9h (00h)             | GPIO_6_7 Mode                      |

| DDh (00h)             | Mix Ratio 4 & 5                    |

| DEh (00h)             | Mix Ratio 6 & 7                    |

| E1h (00h)             | Audio Detect Threshold 5678 MSB    |

| E2h (aah)             | Audio Detect Threshold 56 LSB      |

| E3h (aah)             | Audio Detect Threshold 78 LSB      |

| FCh (FFh)             | AV Detection Enable                |

| FDh (00h)             | AV Detection Status                |

12/12/14 www.pericom.com 14-0207 18

## **Control Register**

#### **PAGE 0 REGISTERS**

| Register Type | Descriptions |

|---------------|--------------|

| R             | Read Only    |

| RW            | Read/Write   |

VIDEO STATUS REGISTER - OFFSET 00H/10H/20H/30H (Default: 00H)

| BIT | FUNCTION | ТҮРЕ | DESCRIPTION                                   |

|-----|----------|------|-----------------------------------------------|

| 0   | DET50    | R    | 0: 60Hz source detected                       |

|     |          |      | 1: 50Hz source detected                       |

| 1   | MONO     | R    | 0:Color burst signal detected                 |

|     |          |      | 1: No color burst signal detected             |

| 2   | Reserved | R    | Reset to 0b                                   |

| 3   | VLOCK    | R    | 0: Vertical logic is not locked               |

|     |          |      | 1: Vertical logic is locked to incoming video |

| 4   | Reserved | R    | Reset to 0b                                   |

| 5   | SLOCK    | R    | 0: Sub-carrier sync is not detected           |

|     |          |      | 1: Sub-carrier sync is detected               |

| 6   | HLOCK    | R    | 0:Horizontal sync is not detected             |

|     |          |      | 1: Horizontal sync is detected                |

| 7   | VDLOSS   | R    | 0: Video is detected                          |

|     |          |      | 1: Video not present                          |

### BRIGHTNESS CONTROL REGISTER - OFFSET 01H/11H/21H/31H(Default=00H)

| BIT   | FUNCTION   | ТҮРЕ | DESCRIPTION                                          |

|-------|------------|------|------------------------------------------------------|

| [7:0] | Brightness | RW   | These Signed bits control the brightness.Value range |

|       |            |      | from -128 to 127                                     |

|       |            |      | 8'h7F: brightest; 8'h80: darkest ;8'h00 : no effect  |

### CONTRASTCONTROL REGISTER - OFFSET 02H/12H/22H/32H(Default=64H)

| BIT   | FUNCTION | ТҮРЕ | DESCRIPTION                                     |

|-------|----------|------|-------------------------------------------------|

| [7:0] | Contrast | RW   | These unsigned bits control the luminance gain. |

|       |          |      | 8'h7F: maximum contrast                         |

|       |          |      | 8'h00: minimum contrast                         |

Adaptive EQ 8-channel 960H Video Decoder

#### SHARPNESSCONTROL REGISTER - OFFSET 03H/13H/23H/33H(Default=00H)

| BIT   | FUNCTION  | ТҮРЕ | DESCRIPTION                                                                   |

|-------|-----------|------|-------------------------------------------------------------------------------|

| [3:0] | Sharpness | RW   | These bits control the amount of sharpness enhancement                        |

|       |           |      | on the luminance signals                                                      |

|       |           |      | "0" has no effect on the output image                                         |

|       |           |      | "1" through "15" provides sharpness enhancement with "15" being the strongest |

| [7:4] | Reserved  | R    | Reset to 0h                                                                   |

#### CHROMA(U) GAIN REGISTER - OFFSET 04H/14H/24H/34H(Default=80H)

| BIT   | FUNCTION        | ТҮРЕ | DESCRIPTION                                           |

|-------|-----------------|------|-------------------------------------------------------|

| [7:0] | Chroma (U) Gain | RW   | Chroma gain value of controlling the color saturation |

#### CHROMA(V) GAIN REGISTER - OFFSET 05H/15H/25H/35H(Default=80H)

| I | BIT   | FUNCTION        | ТҮРЕ | DESCRIPTION                                           |

|---|-------|-----------------|------|-------------------------------------------------------|

|   | [7:0] | Chroma (V) Gain | RW   | Chroma gain value of controlling the color saturation |

#### HUECONTROL REGISTER - OFFSET 06H/16H/26H/36H(Default=00H)

| BIT   | FUNCTION | ТҮРЕ | DESCRIPTION                          |

|-------|----------|------|--------------------------------------|

| [7:0] | Hue      | RW   | These signed bits control color hue. |

|       |          |      | +90C(7Fh) to -90C(80h)               |

#### RESERVED REGISTER- OFFSET07H/17H/27H/37H

RESERVED REGISTER - OFFSET 08H/18H/28H/38H

RESERVED REGISTER - OFFSET09H/19H/29H/39H

#### H-Delay REGISTER - OFFSET 0AH/1AH/2AH/3AH(Default=00H)

| BIT   | FUNCTION               | ТҮРЕ | DESCRIPTION                                  |

|-------|------------------------|------|----------------------------------------------|

| [7:5] | Reserved               | R    | Reset to 0b                                  |

| [4:0] | HorizontalShift Pixels | R/W  | Left shift the start points of video outputs |

|       | Poinis                 |      |                                              |

#### RESERVED REGISTER - OFFSET 0BH/1BH/2BH/3BH

#### RESERVED REGISTER - OFFSET 0CH/1CH/2CH/3CH

#### RESERVED REGISTER - OFFSET 0DH/1DH/2DH/3DH

#### STANDARD SELECTION REGISTER - OFFSET 0EH/1EH/2EH/3EH(Default=77H)

| BIT   | FUNCTION           | ТҮРЕ | DESCRIPTION       |

|-------|--------------------|------|-------------------|

| [2:0] | Standard Selection | RW   | 0: NTSC(M)        |

|       |                    |      | 1: PAL(B,D,G,H,I) |

|       |                    |      | 2:Not valid       |

|       |                    |      | 3: NTSC4.43       |

|       |                    |      | 4: PAL(M)         |

|       |                    |      | 5: PAL(CN)        |

|       |                    |      | 6: PAL60          |

|       |                    |      | 7: Auto detection |

| [3]   | Reserved           | R    | Reset to 0b       |

| [6:4] | Current Standard   | R    | 0: NTSC(M)        |

|       | Detected           |      | 1: PAL(B,D,G,H,I) |

|       |                    |      | 2:Not valid       |

|       |                    |      | 3: NTSC4.43       |

|       |                    |      | 4: PAL(M)         |

|       |                    |      | 5: PAL(CN)        |

|       |                    |      | 6: PAL60          |

|       |                    |      | 7:Not valid       |

| [7]   | Reserved           | R    | Reset to 0b       |

#### RESERVEDREGISTER - OFFSET 0FH/1FH/2FH/3FH

#### **RESERVED REGISTER - OFFSET 40H-50H**

### FBITINV REGISTER - OFFSET 51H(Default=00H)

| BIT   | FUNCTION | TYPE | DESCRIPTION                                                            |

|-------|----------|------|------------------------------------------------------------------------|

| [0]   | FBITINV0 | R/W  | 0: F-bit in the 4th byte of 656 EAV/SAV for channel 1 is not inverted. |

|       |          |      | 1: F-bit in the 4th byte for channel 0 is inverted.                    |

| [1]   | FBITINV1 | R/W  | 0: F-bit in the 4th byte of 656 EAV/SAV for channel 2 is not inverted. |

|       |          |      | 1: F-bit in the 4th byte for channel 1is inverted.                     |

| [2]   | FBITINV2 | R/W  | 0: F-bit in the 4th byte of 656 EAV/SAV for channel 3 is not inverted. |

|       |          |      | 1: F-bit in the 4th byte for channel 2is inverted.                     |

| [3]   | FBITINV3 | R/W  | 0: F-bit in the 4th byte of 656 EAV/SAV for channel 4 is not inverted. |

|       |          |      | 1: F-bit in the 4th byte for channel 3is inverted.                     |

| [7:4] | Reserved | R    | Reset to 0b                                                            |

#### **RESERVED REGISTER - OFFSET 52H-56H**

Adaptive EQ 8-channel 960H Video Decoder

**High HBLEN REGISTER - OFFSET 56H (Default=00H)**

| BIT   | FUNCTION  | ТҮРЕ | DESCRIPTION                                                |

|-------|-----------|------|------------------------------------------------------------|

| [0]   | HBLEN1[8] | R    | Display the blanking length starting from EAV to SAV code. |

| [1]   | HBLEN2[8] | R    | Display the blanking length starting from EAV to SAV code. |

| [2]   | HBLEN3[8] | R    | Display the blanking length starting from EAV to SAV code. |

| [3]   | HBLEN4[8] | R    | Display the blanking length starting from EAV to SAV code. |

| [7:4] | Reserved  | R    | Reset to 0b                                                |

#### LOW HBLEN REGISTER - OFFSET 57H/58H/59H/5AH(Default=90H)

| BIT   | FUNCTION    | ТҮРЕ | DESCRIPTION                                                |

|-------|-------------|------|------------------------------------------------------------|

| [7:0] | HBLENn[7:0] | R    | Display the blanking length starting from EAV to SAV code. |

|       | n=1,2,3,4   |      | (1) In 27MHz D1 Mode: 90H for PAL while 8AH for NTSC       |

|       |             |      | (2) In 36MHz WD1 Mode: C0H for PAL while B8H for NTSC      |

#### **RESERVED REGISTER - OFFSET 5BH-5CH**

#### VIN2 COLOR KILL ENABLE-REGISTER - OFFSET 5DH(Default=C0H)

| BIT   | FUNCTION      | ТҮРЕ | DESCRIPTION                       |

|-------|---------------|------|-----------------------------------|

| [5:0] | Reserved      | RW   | Reset to 0h                       |

| [6]   | PAL CKILL EN  | RW   | 1:enable color kill mode in PAL   |

|       |               |      | 0:disable color kill mode in PAL  |

| [7]   | NTSC CKILL EN | RW   | 1:enable color kill mode in NTSC  |

|       |               |      | 0:disable color kill mode in NTSC |

#### VIN3 COLOR KILL ENABLE-REGISTER - OFFSET 5EH(Default=C0H)

| BIT   | FUNCTION      | TYPE | DESCRIPTION                       |

|-------|---------------|------|-----------------------------------|

| [5:0] | Reserved      | RW   | Reset to 0h                       |

| [6]   | PAL CKILL EN  | RW   | 1:enable color kill mode in PAL   |

|       |               |      | 0:disable color kill mode in PAL  |

| [7]   | NTSC CKILL EN | RW   | 1:enable color kill mode in NTSC  |

|       |               |      | 0:disable color kill mode in NTSC |

### VIN4 COLOR KILL ENABLE-REGISTER - OFFSET 5FH(Default=C0H)

| BIT   | FUNCTION     | ТҮРЕ | DESCRIPTION                      |

|-------|--------------|------|----------------------------------|

| [5:0] | Reserved     | RW   | Reset to 0h                      |

| [6]   | PAL CKILL EN | RW   | 1:enable color kill mode in PAL  |

|       |              |      | 0:disable color kill mode in PAL |

| [7] | NTSC CKILL EN | RW | 1:enable color kill mode in NTSC  |

|-----|---------------|----|-----------------------------------|

|     |               |    | 0:disable color kill mode in NTSC |

#### **RESERVED REGISTER - OFFSET 60H**

## CRYSTAL CLOCK SELECT REGISTER - OFFSET 61H(Default=03H)

| BIT   | FUNCTION | ТҮРЕ | DESCRIPTION         |

|-------|----------|------|---------------------|

| [1:0] | XINMD    | RW   | XIN input frequency |

|       |          |      | 0:27Mhz             |

|       |          |      | 1:54Mhz             |

|       |          |      | 2:108Mhz            |

|       |          |      | 3:27Mhz             |

| [7:2] | Reserved | RW   | Reset to 00h        |

#### GPIO OE REGISTER - OFFSET 62H(Default=00H)

| BIT   | FUNCTION | ТҮРЕ | DESCRIPTION              |

|-------|----------|------|--------------------------|

| [0]   | GPIO_0OE | RW   | 0: GPIO_0 pin is input.  |

|       |          |      | 1: GPIO_0 pin is output. |

| [1]   | GPIO_1OE | RW   | 0: GPIO_1 pin is input.  |

|       |          |      | 1: GPIO_1 pin is output. |

| [2]   | GPIO_2OE | RW   | 0: GPIO_2 pin is input.  |

|       |          |      | 1: GPIO_2 pin is output. |

| [3]   | GPIO_3OE | RW   | 0: GPIO_3 pin is input.  |

|       |          |      | 1: GPIO_3 pin is output. |

| [7:4] | Reserved | RW   | Reset to 00h             |

#### CHANNEL ID01 REGISTER - OFFSET 63H(Default=10H)

| BIT   | FUNCTION | ТҮРЕ | DESCRIPTION                                           |

|-------|----------|------|-------------------------------------------------------|

| [3:0] | CH0NUM   | RW   | Assign channel ID number in CV_IN0A video data output |

| [7:4] | CH1NUM   | RW   | Assign channel ID number in CV_IN1A video data output |

### CHANNEL ID23 REGISTER - OFFSET 64H(Default=32H)

| BIT   | FUNCTION | ТҮРЕ | DESCRIPTION                                           |

|-------|----------|------|-------------------------------------------------------|

| [3:0] | CH2NUM   | RW   | Assign channel ID number in CV_IN2A video data output |

| [7:4] | CH3NUM   | RW   | Assign channel ID number in CV_IN3A video data output |

Adaptive EQ 8-channel 960H Video Decoder

#### CHANNEL ID45 REGISTER - OFFSET 65H(Default=54H)

| BIT   | FUNCTION | ТҮРЕ | DESCRIPTION                                           |

|-------|----------|------|-------------------------------------------------------|

| [3:0] | CH4NUM   | RW   | Assign channel ID number in CV_IN4A video data output |

| [7:4] | CH5NUM   | RW   | Assign channel ID number in CV_IN5A video data output |

#### CHANNEL ID67 REGISTER - OFFSET 66H(Default=76H)

| BIT   | FUNCTION | ТҮРЕ | DESCRIPTION                                           |

|-------|----------|------|-------------------------------------------------------|

| [3:0] | CH6NUM   | RW   | Assign channel ID number in CV_IN6A video data output |

| [7:4] | CH7NUM   | RW   | Assign channel ID number in CV_IN7A video data output |

#### HZOOM ENABLE REGISTER - OFFSET 67H(Default=80H)

| BIT   | FUNCTION     | ТҮРЕ | DESCRIPTION               |

|-------|--------------|------|---------------------------|

| [6:0] | Reserved     | R    | Reset to 00h              |

| [7]   | HZOOM ENABLE | RW   | 1: Enable HZOOM function  |

|       |              |      | 0: Disable HZOOM function |

#### HI -Bits HZOOM REGISTER - OFFSET 68H(Default=00H)

| BIT   | FUNCTION    | ТҮРЕ | DESCRIPTION  |

|-------|-------------|------|--------------|

| [1:0] | HZOOM1[9:8] | RW   | MSB of reg69 |

| [3:2] | HZOOM2[9:8] | RW   | MSB of reg6A |

| [5:4] | HZOOM3[9:8] | RW   | MSB of reg6B |

| [7:6] | HZOOM4[9:8] | RW   | MSB of reg6C |

#### LOW-Bits HZOOM VIN1 REGISTER - OFFSET 69H(Default=00H)

| BIT   | FUNCTION    | ТҮРЕ | DESCRIPTION                                     |

|-------|-------------|------|-------------------------------------------------|

| [7:0] | HZOOM1[7:0] | R/W  | HZOOM UP register the number is from            |

|       |             |      | 3DE to 3FF if HZOOM1[9:0]=00h No HZOOM Function |

#### LOW-Bits HZOOM VIN2 REGISTER - OFFSET 6AH(Default=00H)

| BIT   | FUNCTION    | TYPE | DESCRIPTION                                     |

|-------|-------------|------|-------------------------------------------------|

| [7:0] | HZOOM2[7:0] | R/W  | HZOOM UP register the number is from            |

|       |             |      | 3DE to 3FF if HZOOM2[9:0]=00h No HZOOM Function |

#### LOW-Bits HZOOM VIN3 REGISTER - OFFSET 6BH(Default=00H)

| BIT   | FUNCTION    | ТҮРЕ | DESCRIPTION                                     |

|-------|-------------|------|-------------------------------------------------|

| [7:0] | HZOOM3[7:0] | R/W  | HZOOM UP register the number is from            |

|       |             |      | 3DE to 3FF if HZOOM3[9:0]=00h No HZOOM Function |

## LOW-Bits HZOOM VIN4 REGISTER - OFFSET 6CH(Default=00H)

| BIT   | FUNCTION    | TYPE | DESCRIPTION                                     |

|-------|-------------|------|-------------------------------------------------|

| [7:0] | HZOOM4[7:0] | R/W  | HZOOM UP register the number is from            |

|       |             |      | 3DE to 3FF if HZOOM4[9:0]=00h No HZOOM Function |

#### **RESERVED REGISTER - OFFSET 6DH-6EH**

#### PIXOUT OUTPUT ENABLE REGISTER - OFFSET 6FH(Default=00H)

| BIT   | FUNCTION    | ТҮРЕ | DESCRIPTION       |

|-------|-------------|------|-------------------|

| [0]   | PIXOUT0_OEB | R    | 0: enable output  |

|       |             |      | 1: disable output |

| [1]   | PIXOUT1_OEB | R    | 0: enable output  |

|       |             |      | 1: disable output |

| [2]   | PIXOUT2_OEB | R    | 0: enable output  |

|       |             |      | 1: disable output |

| [3]   | PIXOUT3_OEB | R    | 0: enable output  |

|       |             |      | 1: disable output |

| [7:4] | Reserved    | R    | Reset to 0b       |

#### AUDIO CLOCK CONTROL REGISTER - OFFSET 70H(Default=08H)

| BIT   | FUNCTION | ТҮРЕ | DESCRIPTION                                      |

|-------|----------|------|--------------------------------------------------|

| [2:0] | AFMD     | RW   | 0: 8KHz                                          |

|       |          |      | 1: 16KHz                                         |

|       |          |      | 2: 32KHz                                         |

|       |          |      | 3: 44.1KHz                                       |

|       |          |      | 4: 48KHz                                         |

| [3]   | Reserved | R    | Reset to 1b                                      |

| [5:4] | Reserved | R    | Reset to 0b                                      |

| [6]   | S2I_8BIT | RW   | 0:SCLK_P/LRCK_P/SDOUT_P pin input 16-bit control |

|       |          |      | 1: SCLK_P/LRCK_P/SDOUT_P pin input 8-bit control |

| [7]   | Reserved | R    | Reset to 0b                                      |

#### I2S AUDIO INPUT CONTROL REGISTER - OFFSET 71H(Default=00H)

| BIT   | FUNCTION | ТҮРЕ | DESCRIPTION                                                                     |

|-------|----------|------|---------------------------------------------------------------------------------|

| [1:0] | Reserved | R    | Reset to 00b                                                                    |

| [2]   | SDINPDLY | RW   | SDIN_P input data delay by one SCLK_P clock                                     |

|       |          |      | 0:No delay; 1T delay for I2S interface                                          |

|       |          |      | 1:Add 1 SCLK_P clock delay in SDIN_P input.; 0T delay for left-justified inter- |

|       |          |      | face.                                                                           |

| [7:3] | Reserved | R    | Reset to 00h                                                                    |

#### **RESERVED REGISTER - OFFSET72H**

#### LINE\_IN4 CONTROL REGISTER - OFFSET 73H(Default=00H)

| BIT   | FUNCTION          | ТҮРЕ | DESCRIPTION                                                     |

|-------|-------------------|------|-----------------------------------------------------------------|

| [0]   | LINE_IN4 DET_EN   | RW   | 0 : Disable LINE_IN4 status register update and interrupt       |

|       |                   |      | 1: Enable LINE_IN4 status register update and interrupt         |

| [1]   | Reserved          | R    | Reset to 00b                                                    |

| [2]   | LINE_IN4 Location | RW   | LINE_IN4OUTOFF is set to 0                                      |

|       | In data sequence  |      | 0:                                                              |

|       |                   |      | I2S Mode:                                                       |

|       |                   |      | L: d0 d1 d2 d3 d4 d5 d6 d7 d51 d52                              |

|       |                   |      | R :d8 d9 dA dB dC dD dE dF d53 d54                              |

|       |                   |      | DSP mode                                                        |

|       |                   |      | d0 d1 d2 d3 d4 d5 d6 d7 d8 d9 dA dB dC dD dE dF                 |

|       |                   |      | d51 d52 d53 d54                                                 |

|       |                   |      | 1:                                                              |

|       |                   |      | I2S Mode:                                                       |

|       |                   |      | L: d0 d1 d2 d3 d51 d4 d5 d6 d7 d52                              |

|       |                   |      | R :d8 d9 dA dB d53 dC dD dE dF d54                              |

|       |                   |      | DSP mode                                                        |

|       |                   |      | d0 d1 d2 d3 d51 d4 d5 d6 d7 d52 d8 d9 dA dB d53 dC dD dE dF d54 |

| [7:3] | Reserved          | R    | Reset to 00h                                                    |

### LINE\_IN4 DETECT ENABLE REGISTER - OFFSET 74H(Default=00H)

| BIT   | FUNCTION         | TYPE | DESCRIPTION           |

|-------|------------------|------|-----------------------|

| [0]   | LINE_IN4 DETECT_ | RW   | Audio LINE_IN4 detect |

|       | STATE            |      | 0:Disable             |

|       |                  |      | 1:Enable              |

| [7:1] | Reserved         | R    | Reset to 00h          |

#### **RESERVED REGISTER - OFFSET75H-7AH**

### SDOUT\_M SELECT (R) REGISTER - OFFSET 7BH(Default=00H)

| FUNCTION  | TYPE | DESCRIPTION                                                             |

|-----------|------|-------------------------------------------------------------------------|

| I2SO_RSEL | RW   | Select R channel output on SDOUT_M pin when SDOUTM_I2SOEN=1             |

|           |      | 0:Select record audio channel LINE_IN0                                  |

|           |      | 1:Select record audio channel LINE_IN1                                  |

|           |      | 2:Select record audio channel LINE_IN2                                  |

|           |      | 3:Select record audio channel LINE_IN3                                  |

|           |      | 4:Select record audio channel LINE_IN5                                  |

|           |      | 5:Select record audio channel LINE_IN6                                  |

|           |      | 6:Select record audio channelLINE_IN7                                   |

|           |      | 7:Select record audio channel LINE_IN8                                  |

|           |      | 8:Select record audio channel LINE_IN10                                 |

|           |      | 9:Select record audio channel LINE_IN11                                 |

|           |      | A:Select record audio channel LINE_IN12                                 |

|           |      | B:Select record audio channel LINE_IN13                                 |

|           |      | C:Select record audio channel LINE_IN15                                 |

|           |      | D:Select record audio channel LINE_IN16                                 |

|           |      | E:Select record audio channel LINE_IN17                                 |

|           |      | F:Select record audio channel LINE_IN18                                 |

|           |      | 10h:Select playback audio of the master chip                            |

|           |      | 11h:Reserved                                                            |

|           |      | 12h:Select playback audio of the slave chip                             |

|           |      | 13h:Reserved                                                            |

|           |      | 14h:Playback data output and playback data can adjust volume by DF[3:0] |

|           |      | 15h:Select record audio of channel LINE_IN4                             |

|           |      | 16h:Select record audio of channel LINE_IN9                             |

|           |      | 17h:Select record audio of channel LINE_IN14                            |

|           |      | 18h:Select record audio of channel LINE_IN19                            |

|           |      | Others:No audio output                                                  |

| Reserved  | R    | Reset to 0h                                                             |

|           |      | I2SO_RSEL RW                                                            |

### SDOUT\_M SELECT (L) REGISTER - OFFSET 7CH(Default=00H)

| BIT   | FUNCTION  | TYPE | DESCRIPTION                                                             |

|-------|-----------|------|-------------------------------------------------------------------------|

| [4:0] | I2SO_RSEL | RW   | Select L channel output on SDOUT_M pin when SDOUTM_I2SOEN=1:            |

|       |           |      | 0:Select record audio channel LINE_IN0                                  |

|       |           |      | 1:Select record audio channel LINE_IN1                                  |

|       |           |      | 2:Select record audio channel LINE_IN2                                  |

|       |           |      | 3:Select record audio channel LINE_IN3                                  |

|       |           |      | 4:Select record audio channel LINE_IN5                                  |

|       |           |      | 5:Select record audio channel LINE_IN6                                  |

|       |           |      | 6:Select record audio channelLINE_IN7                                   |

|       |           |      | 7:Select record audio channel LINE_IN8                                  |

|       |           |      | 8:Select record audio channel LINE_IN10                                 |

|       |           |      | 9:Select record audio channel LINE_IN11                                 |

|       |           |      | A:Select record audio channel LINE_IN12                                 |

|       |           |      | B:Select record audio channel LINE_IN13                                 |

|       |           |      | C:Select record audio channel LINE_IN15                                 |

|       |           |      | D:Select record audio channel LINE_IN16                                 |

|       |           |      | E:Select record audio channel LINE_IN17                                 |

|       |           |      | F:Select record audio channel LINE_IN18                                 |

|       |           |      | 10h:Select playback audio of the master chip                            |

|       |           |      | 11h:Reserved                                                            |

|       |           |      | 12h:Select playback audio of the slave chip                             |

|       |           |      | 13h:Reserved                                                            |

|       |           |      | 14h:Playback data output and playback data can adjust volume by DF[3:0] |

|       |           |      | 15h:Select record audio of channel LINE_IN4                             |

|       |           |      | 16h:Select record audio of channel LINE_IN9                             |

|       |           |      | 17h:Select record audio of channel LINE_IN14                            |

|       |           |      | 18h:Select record audio of channel LINE_IN19                            |

|       |           |      | Others:No audio output Others:No audio output                           |

| [7:5] | Reserved  | R    | Reset to 000b                                                           |

### EXTENDED LINE SELECT REGISTER - OFFSET 7DH(Default=E4H)

| BIT   | FUNCTION              | ТҮРЕ | DESCRIPTION  |

|-------|-----------------------|------|--------------|

| [1:0] | Select Output Data In | RW   | 0: LINE_IN4  |

|       | Data51 Position       |      | 1: LINE_IN9  |

|       |                       |      | 2: LINE_IN14 |

|       |                       |      | 3: LINE_IN19 |

| [3:2] | Select Output Data In | RW | 0: LINE_IN4  |

|-------|-----------------------|----|--------------|

|       | Data52 Position       |    | 1: LINE_IN9  |

|       |                       |    | 2: LINE_IN14 |

|       |                       |    | 3: LINE_IN19 |

| [5:4] | Select Output Data In | RW | 0: LINE_IN4  |

|       | Data53 Position       |    | 1: LINE_IN9  |

|       |                       |    | 2: LINE_IN14 |

|       |                       |    | 3: LINE_IN19 |

| [7:6] | Select Output Data In | RW | 0: LINE_IN4  |

|       | Data54 Position       |    | 1: LINE_IN9  |

|       |                       |    | 2: LINE_IN14 |

|       |                       |    | 3: LINE_IN19 |

### SDOUT\_M REGISTER- OFFSET 7EH(Default=00H)

| BIT   | FUNCTION | ТҮРЕ | DESCRIPTION                                                      |

|-------|----------|------|------------------------------------------------------------------|

| [5:0] | Reserved | R    | Reset to 00b                                                     |

| [6]   | SDOUT_M  | R/W  | Define SDOUT_M pin output 2 word data                            |

|       | I2S OEN  |      | to make standard I2S output                                      |

|       |          |      | 0: Mixing Data or Playback input data are only output on SDOUT_M |

|       |          |      | 1:L/R data on SDOUT_M pin is selected by 0x7B and 0x7C           |

| [7]   | A5OUTOFF | R/W  | 0:LINE_IN4/LINE_IN9/LINE_IN14                                    |

|       |          |      | /LINE_IN19 output on SDOUT_R                                     |

|       |          |      | 1:LINE_IN4/LINE_IN9/LINE_IN14                                    |

|       |          |      | /LINE_IN19 not output on SDOUT_R                                 |

#### MIX RATIO VALUE FOR LINE\_IN4 REGISTER - OFFSET 7FH(Default=00H)

| BIT   | FUNCTION   | TYPE | DESCRIPTION                                    |

|-------|------------|------|------------------------------------------------|

| [3:0] | Mix_Ratio4 | RW   | LINE_IN4 ratio value for audio mixing function |

|       |            |      | 0:1/2^8                                        |

|       |            |      | 1:1/2^7                                        |

|       |            |      | 2:1/2^6                                        |

|       |            |      | 3:1/2^5                                        |

|       |            |      | 4:1/2^4                                        |

|       |            |      | 5:1/2^3                                        |

|       |            |      | 6:1/2^2                                        |

|       |            |      | 7:1/2^1                                        |

|       |            |      | other: 100%                                    |

| [7:4] | Reserved   | R    | Reset to 00b                                   |

Adaptive EQ 8-channel 960H Video Decoder

## SOFTWARE RESET REGISTER- OFFSET 80H(Default=00H)

| BIT   | FUNCTION | ТҮРЕ | DESCRIPTION                                                                                                                      |

|-------|----------|------|----------------------------------------------------------------------------------------------------------------------------------|

| [0]   | VDEC0RST | W    | Writing one reset the video decoder 0 to its default state but all registercontent remain unchanged. This bit is self-resetting  |

| [1]   | VDEC1RST | W    | Writing one reset the video decoder 1 to its default state but all register content remain unchanged. This bit is self-resetting |

| [2]   | VDEC2RST | W    | Writing one reset the video decoder 2 to its default state but all register content remain unchanged. This bit is self-resetting |

| [3]   | VDEC3RST | W    | Writing one reset the video decoder 3 to its default state but all register content remain unchanged. This bit is self-resetting |

| [4]   | Reserved | R    | Reset to 00b                                                                                                                     |

| [5]   | AUDIORST | W    | Writing one reset the audio portion to its default state but all register content remain unchanged. This bit is self-resetting   |

| [7:6] | Reserved | R    | Reset to 00b                                                                                                                     |

#### **RESERVED REGISTER - OFFSET 81H-88H**

### AUDIO FS MODE REGISTER- OFFSET 89H(Default=00H)

| BIT   | FUNCTION             | ТҮРЕ | DESCRIPTION  |

|-------|----------------------|------|--------------|

| [1:0] | Reserved             | R    | Reset to 00b |

| [2]   | Audio FS Mode Select | RW   | 0: 256fs     |

|       |                      |      | 1: 320fs     |

| [7:3] | Reserved             | R    | Reset to 00h |

#### **RESERVED REGISTER - OFFSET 8AH-95H**

### VIN1 COLOR KILL ENABLE-REGISTER - OFFSET 96H(Default=C0H)

| BIT   | FUNCTION      | ТҮРЕ | DESCRIPTION                       |

|-------|---------------|------|-----------------------------------|

| [5:0] | Reserved      | RW   | Reset to 0h                       |

| [6]   | PAL CKILL EN  | RW   | 1:enable color kill mode in PAL   |

|       |               |      | 0:disable color kill mode in PAL  |

| [7]   | NTSC CKILL EN | RW   | 1:enable color kill mode in NTSC  |

|       |               |      | 0:disable color kill mode in NTSC |

#### **RESERVED REGISTER - OFFSET 97H-9EH**

PIXCLK 0 DELAY REGISTER- OFFSET 9FH(Default=00H)

| BIT   | FUNCTION               | ТҮРЕ | DESCRIPTION                |

|-------|------------------------|------|----------------------------|

| [3:0] | Control Clock Delay Of | RW   | 0h: No clock delay         |

|       | PIXCLK_P0 Pin          |      | 1h: About 1ns more delay,  |

|       |                        |      | 2h : About 2ns more delay, |

|       |                        |      |                            |

|       |                        |      |                            |

|       |                        |      | Fh: About 15ns more delay  |

| [7:4] | Control Clock Delay Of | RW   | 0h: No clock delay         |

|       | PIXCLK_N0 Pin          |      | 1h: About 1ns more delay,  |

|       |                        |      | 2h : About 2ns more delay, |

|       |                        |      |                            |

|       |                        |      |                            |

|       |                        |      | Fh: About 15ns more delay  |

#### **RESERVED REGISTER - OFFSET A0H-B1H**

## VIDEO LOSS STATUS REGISTER - OFFSET B2H(Default=00H)

| BIT | FUNCTION  | TYPE | DESCRIPTION                           |

|-----|-----------|------|---------------------------------------|

| [0] | VDLOSS1EN | R/W  | 0: disable                            |

|     |           |      | 1: MPP1 output VIN1 video loss status |

| [1] | VDLOSS2EN | R/W  | 0: disable                            |

|     |           |      | 1: MPP2 output VIN2 video loss status |

| [2] | VDLOSS3EN | R/W  | 0: disable                            |

|     |           |      | 1: MPP3 output VIN3 video loss status |

| [3] | VDLOSS4EN | R/W  | 0: disable                            |

|     |           |      | 1: MPP4 output VIN4 video loss status |

| [4] | VDLOSS5EN | R/W  | 0: disable                            |

|     |           |      | 1: MPP5 output VIN5 video loss status |

| [5] | VDLOSS6EN | R/W  | 0: disable                            |

|     |           |      | 1: MPP6 output VIN6 video loss status |

| [6] | VDLOSS7EN | R/W  | 0: disable                            |

|     |           |      | 1: MPP7 output VIN7 video loss status |

| [7] | VDLOSS8EN | R/W  | 0: disable                            |

|     |           |      | 1: MPP8 output VIN8 video loss status |

#### **RESERVED REGISTER - OFFSET B3H-C7H**

#### GPIO 0 1 MODE REGISTER- OFFSET C8H(Default=00H)

| BIT   | FUNCTION                      | ТҮРЕ | DESCRIPTION                             |

|-------|-------------------------------|------|-----------------------------------------|

| [2:0] | Output Mode For               | RW   | Select output mode for GPIO_0 pin       |

|       | GPIO_0Pin                     |      | 0: Output HSYNC                         |

|       |                               |      | 1: Output VSYNC                         |

|       |                               |      | 2:Field                                 |

|       |                               |      | 3:H-active                              |

|       |                               |      | 4:VH-active                             |

|       |                               |      | 5:27MHz clock output                    |

|       |                               |      | 6:VH-sync                               |

|       |                               |      | 7:GPP_VA1                               |

| [3]   | General Purpose Value         | RW   | Set general purpose value in GPIO_0 pin |

| [6:4] | In GPIO_0 Pin Output Mode For | RW   | Select output mode for GPIO_1 pin       |

|       | GPIO_1 Pin                    |      | 0: Output HSYNC                         |

|       |                               |      | 1: Output VSYNC                         |

|       |                               |      | 2:Field                                 |

|       |                               |      | 3:H-active                              |

|       |                               |      | 4:VH-active                             |

|       |                               |      | 5:27MHz clock output                    |

|       |                               |      | 6: VH-sync                              |

|       |                               |      | 7:GPP_VA2                               |

| [7]   | General Purpose Value         | RW   | Set general purpose value in GPIO_1 pin |

|       | In GPIO_1 Pin                 |      |                                         |

#### GPIO\_2\_3 MODE REGISTER- OFFSET C9H(Default=00H)

| BIT   | FUNCTION                               | TYPE | DESCRIPTION                             |

|-------|----------------------------------------|------|-----------------------------------------|

| [2:0] | Output Mode For                        | RW   | Select output mode for GPIO_2 pin       |

|       | GPIO_2 Pin                             |      | 0: Output HSYNC                         |

|       |                                        |      | 1: Output VSYNC                         |

|       |                                        |      | 2:Field                                 |

|       |                                        |      | 3:H-active                              |

|       |                                        |      | 4:VH-active                             |

|       |                                        |      | 5:27MHz clock output                    |

|       |                                        |      | 6:VH-sync                               |

|       |                                        |      | 7:GPP_VA1                               |