# High Voltage ICs HIGH SIDE DRIVER IC

# **AUIRS2123S/AUIRS2124S**

#### **Features**

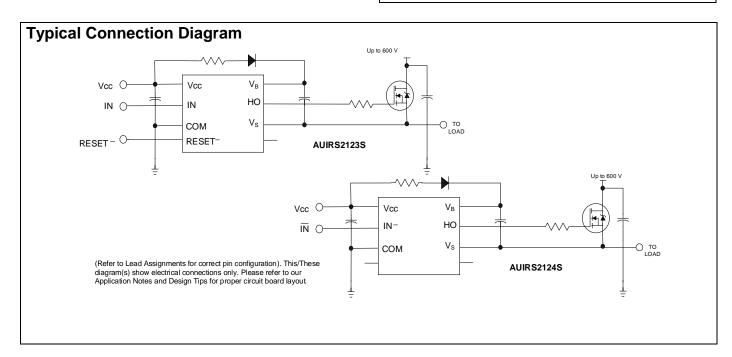

- Floating channel designed for bootstrap operation

- Fully operational to +600 V

- Tolerant to negative transient voltage dV/dt immune

- Gate drive supply range from 10 V to 20 V

- Undervoltage lockout

- CMOS Schmitt-triggered inputs with pull-down (AUIRS2123S)

- CMOS Schmitt-triggered inputs with pull-up (AUIRS2124S)

- Output in phase with input (AUIRS2123S) or out of Phase with input (AUIRS2124S)

- RESET- input is 3.3V and 5V logic compatible (AUIRS2123S only)

- Leadfree, RoHS compliant

- Automotive qualified

#### **Typical Applications**

- General purpose single high side driver

- Automotive injection

- Automotive inverters

- **Automotive SMPS**

#### **Product Summary**

| Topology                                     | Single high side |

|----------------------------------------------|------------------|

| V <sub>OFFSET</sub>                          | ≤ 600 V          |

| V <sub>OUT</sub>                             | 10 V – 20 V      |

| I <sub>o+</sub> & I <sub>o-</sub> (typical)  | 500 mA           |

| t <sub>ON</sub> & t <sub>OFF</sub> (typical) | 140 ns & 140 ns  |

**Package Options**

2017-07-28

# **Ordering Information**

| Danie Bard Namelana | aco Part Number   Packago Type |               | ack  | Occupation Board Named and |

|---------------------|--------------------------------|---------------|------|----------------------------|

| Base Part Number    | Package Type                   | Form Quantity |      | Complete Part Number       |

| AUIRS2123S          | SOIC8                          | Tape and Reel | 2500 | AUIRS2123STR               |

| AUIRS2124S          | SOIC8                          | Tape and Reel | 2500 | AUIRS2124STR               |

| Table of Contents                              | Page |

|------------------------------------------------|------|

| Description                                    | 3    |

| Qualification Information                      | 4    |

| Absolute Maximum Ratings                       | 4    |

| Recommended Operating Conditions               | 5    |

| Static Electrical Characteristics              | 6    |

| Dynamic Electrical Characteristics             | 7    |

| Functional Block Diagram                       | 8    |

| Input/Output Pin Equivalent Circuit Diagram    | 9    |

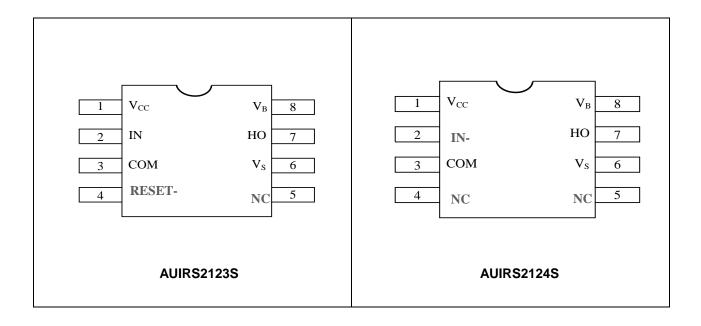

| Lead Definitions                               | 10   |

| Lead Assignments                               | 10   |

| Application Information and Additional Details | 11   |

| Parameter Temperature Trends                   | 12   |

| Package Details                                | 16   |

| Tape and Reel Details                          | 17   |

| Part Marking Information                       | 18   |

| Publisher notes                                |      |

#### **Description**

The AUIRS2123S/AUIRS2124S are high voltage, high speed power MOSFET and IGBT drivers. Proprietary HVIC and latch immune CMOS technologies enable ruggedized monolithic construction.

The RESET- input is compatible with standard CMOS outputs (AUIRS2123S only). The output drivers feature a high pulse current buffer stage designed for minimum cross-conduction.

The floating channel can be used to drive an N-channel power MOSFET or IGBT in the high-side configuration which operates up to 600 V.

#### **Qualification Information**

| Qualification Level        |                      | Automotive (per AEC-Q100)  Comments: This family of ICs has passed an Automotive qualification. IR's Industrial and Consumer qualification level is granted by extension of the higher Automotive level. |                                           |  |

|----------------------------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|--|

|                            |                      | level is granted by exten                                                                                                                                                                                |                                           |  |

| Moisture Sensitivity Level |                      | SOIC8                                                                                                                                                                                                    | MSL3 - 260°C<br>(per IPC/JEDEC J-STD-020) |  |

|                            | Machine Model        | Class M3                                                                                                                                                                                                 |                                           |  |

|                            | Widomine Wieder      | (per AEC-Q100-003)                                                                                                                                                                                       |                                           |  |

| ESD                        | Human Body Model     | Class H1C                                                                                                                                                                                                |                                           |  |

|                            | Traman Body Woder    | (per AEC-Q100-002)                                                                                                                                                                                       |                                           |  |

|                            | Charged Device Model | Class C5                                                                                                                                                                                                 |                                           |  |

| Charged Device Model       |                      | (per AEC-Q100-011)                                                                                                                                                                                       |                                           |  |

| IC Latch-Up Test           |                      | Class II, Level A                                                                                                                                                                                        |                                           |  |

| ic Laten-op Test           | ic Later-op rest     |                                                                                                                                                                                                          | r AEC-Q100-004)                           |  |

| RoHS Compliant             |                      |                                                                                                                                                                                                          | Yes                                       |  |

#### **Absolute Maximum Ratings**

Absolute Maximum Ratings indicate sustained limits beyond which damage to the device may occur. All voltage parameters are absolute voltages referenced to GND, all currents are defined positive into any lead. This is a stress only rating and operation of the device at these or any conditions exceeding those indicated in the operational sections of this specification is not implied

| Symbol           | Definition                               | Min.                | Max.           | Units  |

|------------------|------------------------------------------|---------------------|----------------|--------|

| $V_{BS}$         | High Side Floating Supply Voltage        | -0.3                | 25             | V      |

| V <sub>B</sub>   | High Side Driver Output Stage Voltage    | -0.3                | 625            | V      |

| Vs               | High Side Floating Supply Offset Voltage | V <sub>B</sub> - 25 | $V_{B} + 0.3$  | V      |

| $V_{Ho}$         | Output Voltage Gate Connection           | $V_{S} - 0.3$       | $V_B + 0.3$    | V      |

| V <sub>CC</sub>  | Supply Voltage                           | -0.3                | 25             | V      |

| V <sub>IN</sub>  | Input Voltage                            | -0.3                | $V_{CC} + 0.3$ | V      |

| V <sub>RES</sub> | Reset Input Voltage                      | -0.3                | $V_{CC} + 0.3$ | V      |

| dV/dt            | Allowable Offset Voltage Slew Rate       | -50                 | 50             | V/nsec |

| TJ               | Junction Temperature                     | -55                 | 150            | °C     |

| Ts               | Storage Temperature                      | -55                 | 150            |        |

#### **Recommended Operating Conditions**

For proper operations the device should be used within the recommended conditions.

| Symbol           | Definition                                                                                           | Min.               | Max.               | Units |

|------------------|------------------------------------------------------------------------------------------------------|--------------------|--------------------|-------|

| V <sub>B</sub>   | High Side Driver Output Stage Voltage -10V Transient 0.4 us                                          | V <sub>S</sub> +10 | V <sub>S</sub> +20 | V     |

| Vs               | V <sub>S</sub> High Side Floating Supply Offset Voltage -25V Transient 0.4 μs                        |                    | 600                | V     |

| $V_{Ho}$         | Output Voltage Gate Connection                                                                       | $V_S$              | $V_{B}$            | V     |

| V <sub>CC</sub>  | Supply Voltage                                                                                       | 10                 | 20                 | V     |

| $V_{IN}$         | Input Voltage                                                                                        | 0                  | $V_{CC}$           | V     |

| V <sub>RES</sub> | Reset Input Voltage                                                                                  | 0                  | Vcc                | V     |

| T <sub>A</sub>   | Ambient Temperature (f <sub>s</sub> <60kHz, V <sub>BS</sub> =14V, C <sub>load</sub> =2,5nF, R=50Ohm) | -40                | 125                | °C    |

Logic operational for  $V_S$  of -5 to +600 V. Logic state held for  $V_S$  of -5 V to  $-V_{BS}$ . † (Please refer to the Design Tip DT97-3 for more details).

#### **Static Electrical Characteristics**

$V_{BIAS}$  ( $V_{CC}$ ,  $V_{BS}$ ) = 15 V and  $T_A$  = 25°C unless otherwise specified. The  $V_{IL}$ ,  $V_{IH}$  and  $I_{IN}$  parameters are referenced to COM. The  $V_O$  and  $I_O$  parameters are referenced to COM and are applicable to the respective output leads: HO and LO.

| Symbol              | Definition                                                    |                          |                          | Тур | Max              | Units | Test<br>Conditions                                          |                       |

|---------------------|---------------------------------------------------------------|--------------------------|--------------------------|-----|------------------|-------|-------------------------------------------------------------|-----------------------|

| V <sub>IHIN</sub>   | IN Logic "1" input voltage IN Logic "0" input voltage         | AUIRS2123S<br>AUIRS2124S | 0.70<br>*V <sub>CC</sub> | _   | _                |       |                                                             |                       |

|                     | IN Logic "0" input voltage                                    | AUIRS2123S               | v CC                     |     | 0.35             |       |                                                             |                       |

| V <sub>ILIN</sub>   | IN Logic "1" input voltage                                    | AUIRS2124S               | <del> </del>             |     | *V <sub>CC</sub> |       |                                                             |                       |

| V <sub>IHRST</sub>  | RESET- Logic "1" input voltage                                | AUIRS2123S               | _                        |     | 1.5              | V     |                                                             |                       |

| VILRST              | RESET- Logic "0" input voltage                                | AUIRS2123S               | 2.9                      |     |                  |       |                                                             |                       |

| V <sub>OH</sub>     | High level output voltage, V <sub>BIAS</sub> - V <sub>O</sub> |                          | _                        |     | 2                |       | 1 40 1                                                      |                       |

| V <sub>OL</sub>     | Low level output voltage, Vo                                  |                          | _                        | 0.1 | 0.2              |       | $I_O = 10 \text{ mA}$                                       |                       |

| I <sub>LK</sub>     | Offset supply leakage current                                 |                          | _                        |     | 50               |       | $V_{B} = V_{S} = 600 \text{ V}$                             |                       |

| $I_{QBS}$           | Quiescent V <sub>BS</sub> supply current                      |                          | _                        | _   | 240              |       | $V_{IN} = 0 \text{ V or } V_{CC}$                           |                       |

| I <sub>QCC</sub>    | Quiescent V <sub>CC</sub> supply current                      |                          | _                        | _   | 500              |       | Vreset = 5V                                                 |                       |

|                     | V <sub>IN</sub> = 5V Pull Down Input Current                  | AUIRS2123S               |                          | 125 |                  | μΑ    | $V_{IN} = 5V$                                               |                       |

| I <sub>IN+</sub>    | V <sub>IN</sub> =0 V IN Pull Up Input Current                 | AUIRS2124S               |                          | 123 |                  |       | $V_{IN} = 0 V$                                              |                       |

|                     | V <sub>IN</sub> =0 V IN Pull Down Input Current               | AUIRS2123S               |                          | _   |                  | 5.0   |                                                             | v <sub>IN</sub> = 0 v |

| I <sub>IN-</sub>    | V <sub>IN</sub> = 15V Pull Up Input Current                   | AUIRS2124S               |                          |     | 5.0              |       | $V_{IN} = 15V$                                              |                       |

| I <sub>RES-</sub>   | V <sub>RESET</sub> = 5V Pull Down Input Current               | AUIRS2123S               | _                        | 125 | _                |       | $V_{RESET} = 5V$                                            |                       |

| I <sub>RES+</sub>   | V <sub>RESET</sub> =0V Pull Down Input Current                | AUIRS2123S               | _                        | _   | 5.0              |       | $V_{RESET} = 0 V$                                           |                       |

| $V_{BSUV+}$         | V <sub>BS</sub> supply undervoltage positive goir             | ng threshold             | 7.2                      |     |                  |       |                                                             |                       |

| $V_{BSUV}$          | V <sub>BS</sub> supply undervoltage negative go               | ing threshold            | 6.6                      | 8.0 | 9.0              |       |                                                             |                       |

| V <sub>CCUV+</sub>  | V <sub>CC</sub> supply undervoltage positive goi              | ng threshold             | 7.2                      | 8.6 | 9.6              |       |                                                             |                       |

| V <sub>CCUV</sub> - | V <sub>CC</sub> supply undervoltage negative going threshold  |                          |                          | 8.0 | 9.0              |       |                                                             |                       |

| I <sub>O+</sub>     | Output high short circuit pulsed current (†)                  |                          |                          | 500 | _                | mA    | $V_O = 0 V$ ,<br>$V_{IN} = Logic "1"$<br>$PW \le 10 \mu s$  |                       |

| I <sub>O-</sub>     | Output low short circuit pulsed current                       | nt(†)                    | 250                      | 500 |                  | IIIA  | $V_O = 15 V$ ,<br>$V_{IN} = Logic "0"$<br>$PW \le 10 \mu s$ |                       |

(†): guaranteed by design.

Dynamic Electrical Characteristics  $V_{BIAS} \ (V_{CC}, \, V_{BS}) = 15 \ V, \, C_L = 1000 \ pF, \, T_A = 25 ^{\circ}C \ unless \ otherwise \ specified. \ The \ dynamic \ electrical \ characteristics \ are \ measured \ using \ the \ test \ circuit \ shown \ in \ Fig. 3.$

| Symbol           | Definition                                                   | Min | Тур | Max | Units | <b>Test Conditions</b>  |

|------------------|--------------------------------------------------------------|-----|-----|-----|-------|-------------------------|

| t <sub>on</sub>  | Turn-on propagation delay                                    | _   | 140 | 240 |       | $V_S = 0 V$ and         |

| t <sub>off</sub> | Turn-off propagation delay                                   | _   | 140 | 240 |       | $V_{S} = 600 \text{ V}$ |

| t <sub>r</sub>   | Turn-on rise time                                            | _   | 80  | 200 | ns    |                         |

| t <sub>f</sub>   | Turn-off fall time                                           | _   | 80  | 200 |       |                         |

| t <sub>RES</sub> | RESET to output turn off propagation delay (AUIRS2123S only) | _   | 170 | 300 |       |                         |

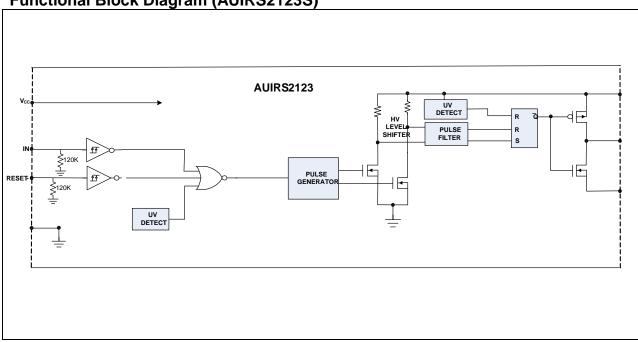

**Functional Block Diagram (AUIRS2123S)**

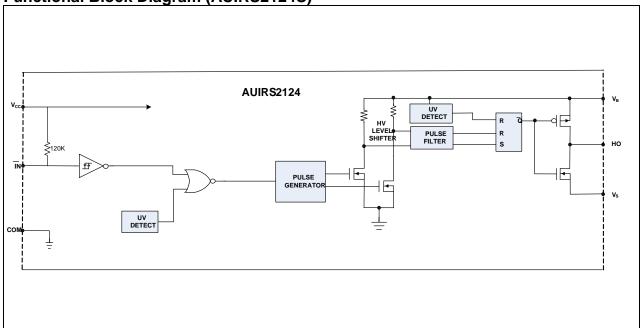

**Functional Block Diagram (AUIRS2124S)**

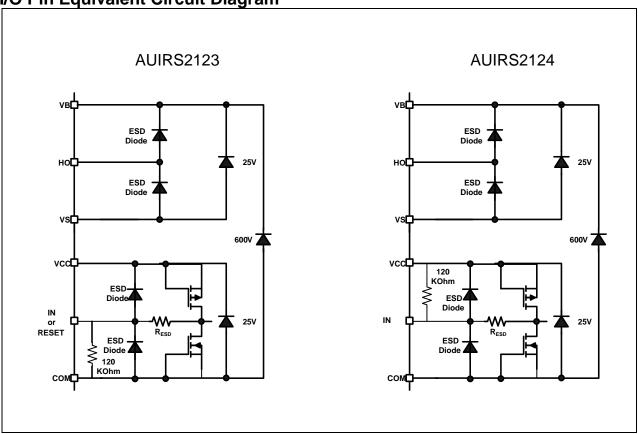

I/O Pin Equivalent Circuit Diagram

### **Lead Definitions**

| Pin | Symbol         | Pin description                                                            |

|-----|----------------|----------------------------------------------------------------------------|

| 1   | VCC            | Low side and logic fixed supply                                            |

| 2   | IN             | Logic input for gate driver output (HO), in phase with HO (AUIRS2123S)     |

| 2   | IN-            | Logic input for gate driver output (HO), out of phase with HO (AUIRS2124S) |

| 3   | COM            | Logic Ground                                                               |

| 4   | RESET-         | Driver Enable Signal Input (negative logic) (AUIRS2123S)                   |

| 4   | NC             | No connection (AUIRS2124S)                                                 |

| 5   | NC             | No connection                                                              |

| 6   | V <sub>s</sub> | High-side floating supply return                                           |

| 7   | Ho             | High-side gate drive output                                                |

| 8   | $V_{B}$        | High-side floating supply                                                  |

## **Application Information and Additional Details**

AUIRS2123S logic table for  $V_{CC}$ ,  $V_{BS}$ , RESET, IN, and  $H_{O}$

| Vcc                                                                     | VBS                                                           | RESET- | IN   | H <sub>O</sub> |

|-------------------------------------------------------------------------|---------------------------------------------------------------|--------|------|----------------|

| Х                                                                       | X                                                             | X      | LOW  | OFF            |

| X                                                                       | X                                                             | LOW    | X    | OFF            |

| <vccuvlo-< td=""><td>X</td><td>X</td><td>X</td><td>OFF</td></vccuvlo-<> | X                                                             | X      | X    | OFF            |

| X                                                                       | <vbsuvlo-< td=""><td>X</td><td>X</td><td>OFF</td></vbsuvlo-<> | X      | X    | OFF            |

| >VccUVLO+                                                               | >VBSUVLO+                                                     | HIGH   | HIGH | ON             |

RESET = HIGH indicates that high side NMOS is allowed to be turned on.

RESET = LOW indicates that high side NMOS is OFF.

IN = HIGH indicates that high side NMOS is on.

IN = LOW indicates that high side NMOS is off.

X = independent

AUIRS2124S logic table for  $V_{CC}$ ,  $V_{BS}$ , RESET, IN, and  $H_{O}$

| Vcc                                                           | VBS                                                 | IN-  | Ho  |

|---------------------------------------------------------------|-----------------------------------------------------|------|-----|

| X                                                             | X                                                   | HIGH | OFF |

| <vccuvlo-< td=""><td>X</td><td>X</td><td>OFF</td></vccuvlo-<> | X                                                   | X    | OFF |

| X                                                             | <vbsuvlo-< td=""><td>X</td><td>OFF</td></vbsuvlo-<> | X    | OFF |

| >VccUVLO+                                                     | >VBSUVLO+                                           | LOW  | ON  |

IN- = HIGH indicates that high side NMOS is on.

IN- = LOW indicates that high side NMOS is off.

X = independent

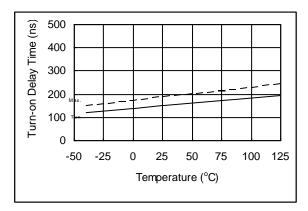

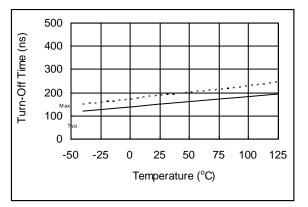

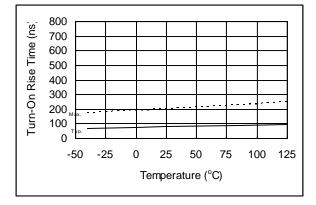

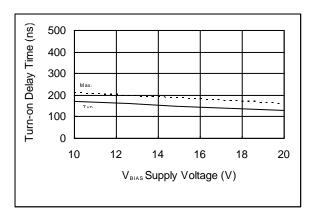

#### **Parameter Temperature Trends**

Figure 1A. Turn-on Delay Time vs. Temperature

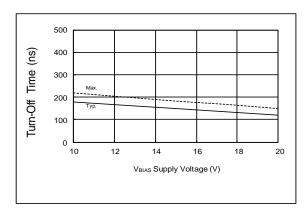

Figure 2A. Turn-Off Time vs. Temperature

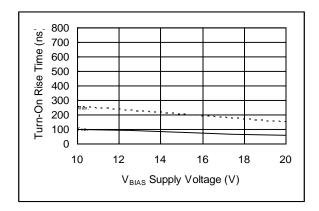

Figure 3A. Turn-On Rise Time (VBS=17V) vs.Temperature

Figure 1B. Turn-on Delay Time vs. Supply Voltage

Figure 2B. Turn-Off Time vs. Supply Voltage

Figure 3B. Turn-On Rise Time (VBS=17V) vs. Supply Voltage

11 Rev. 2.1 2017-07-28

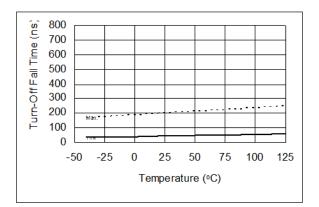

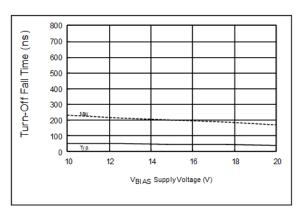

Figure 4A. Turn-Off Fall Time (VBS=17V) vs. Temperature

Figure 4B. Turn-Off Fall Time (VBS=17) vs. Supply Voltage

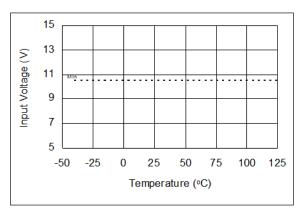

Figure 5A. Logic "1" Input Voltage vs. Temperature

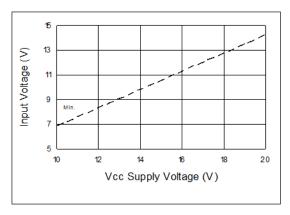

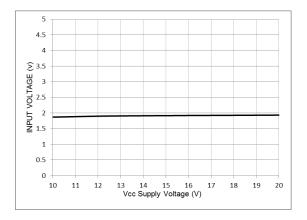

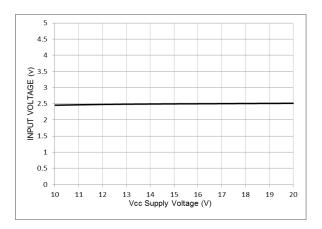

Figure 5B. Logic "1" Input Voltage vs. Supply Voltage

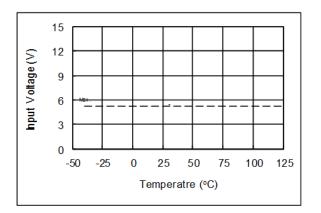

Figure 5C. Logic "1" Input Voltage ( RESET pin ) versus Temperature

Figure 5D. Logic "1" Input Voltage ( RESET pin ) versus Supply Voltage

12 Rev. 2.1 2017-07-28

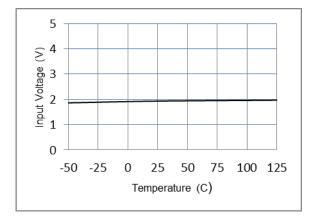

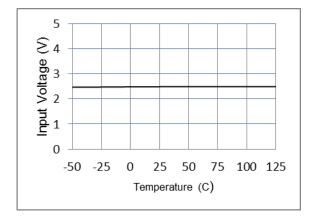

Figure 6A. Logic "0" Input Voltage vs. Temperature

Figure 6C. Logic "0" Input Voltage (RESET pin) versus Temperature

Figure 6B. Logic "0" Input Voltage vs. Supply Voltage

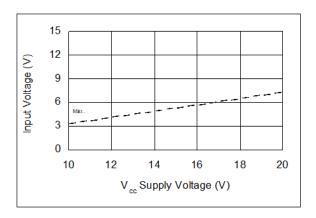

Figure 6D. Logic "0" Input Voltage (RESET pin) versus Supply Voltage

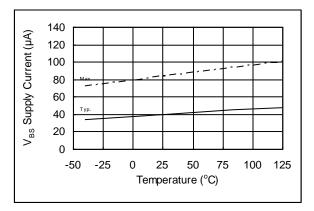

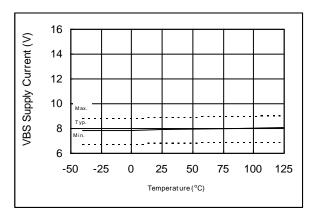

Figure 7A. VBS Supply Current vs. Temperature

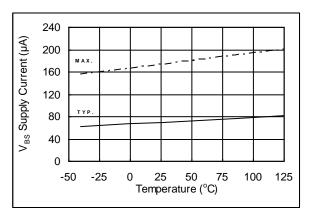

Figure 8A. VBS Supply Current vs. Temperature

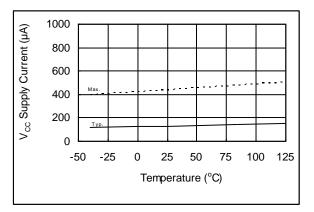

Figure 9A. Vcc Supply Current vs. Temperature

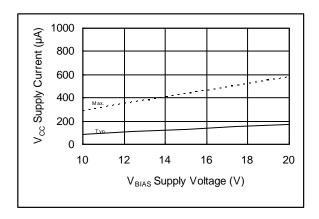

Figure 9B. Vcc Supply Current vs. Supply Voltage

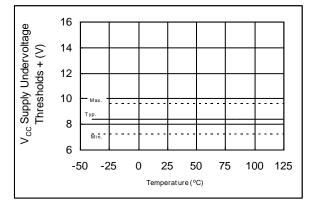

Figure 10A. Vcc Supply Undervoltage Threshold (+) vs. Temperature

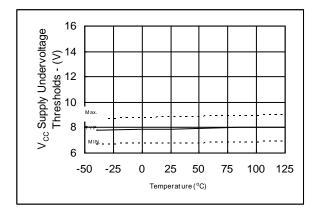

Figure 10B. Vcc Supply Undervoltage Threshold (-) vs. Temperature

14 Rev. 2.1 2017-07-28

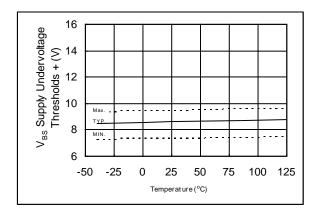

Figure 11A. VBS Supply Undervoltage Threshold (+) vs. Temperature

Figure 11B. VBS Supply Undervoltage Threshold (-) vs. Temperature

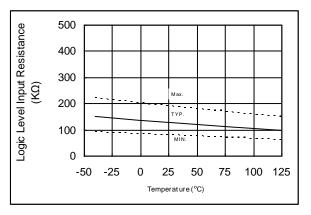

Figure 12. Logic Level Input Resistance vs. Temperature

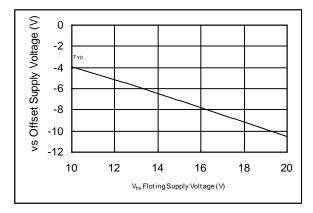

Figure 13. Maximum VS Negative Offset vs. Supply Voltage

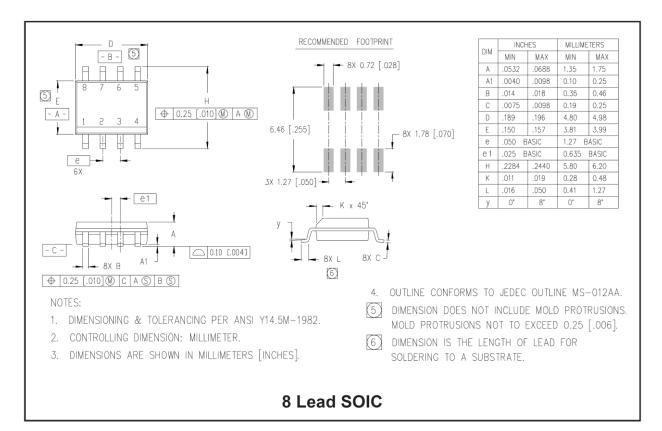

### **Package Details**

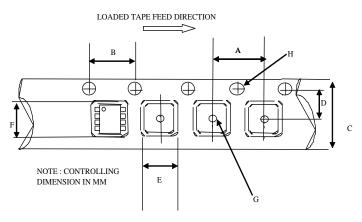

# **Tape and Reel Details**

CARRIER TAPE DIMENSION FOR 8SOICN

|      | Me    | tric  | Imp   | erial |  |

|------|-------|-------|-------|-------|--|

| Code | Min   | Max   | Min   | Max   |  |

| Α    | 7.90  | 8.10  | 0.311 | 0.318 |  |

| В    | 3.90  | 4.10  | 0.153 | 0.161 |  |

| С    | 11.70 | 12.30 | 0.46  | 0.484 |  |

| D    | 5.45  | 5.55  | 0.214 | 0.218 |  |

| E    | 6.30  | 6.50  | 0.248 | 0.255 |  |

| F    | 5.10  | 5.30  | 0.200 | 0.208 |  |

| G    | 1.50  | n/a   | 0.059 | n/a   |  |

| Н    | 1.50  | 1.60  | 0.059 | 0.062 |  |

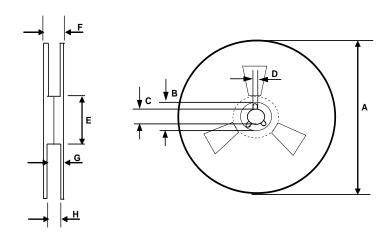

REEL DIMENSIONS FOR 8SOICN

|      | Metric |        | Imperial |        |

|------|--------|--------|----------|--------|

| Code | Min    | Max    | Min      | Max    |

| Α    | 329.60 | 330.25 | 12.976   | 13.001 |

| В    | 20.95  | 21.45  | 0.824    | 0.844  |

| С    | 12.80  | 13.20  | 0.503    | 0.519  |

| D    | 1.95   | 2.45   | 0.767    | 0.096  |

| E    | 98.00  | 102.00 | 3.858    | 4.015  |

| F    | n/a    | 18.40  | n/a      | 0.724  |

| G    | 14.50  | 17.10  | 0.570    | 0.673  |

| H    | 12.40  | 14.40  | 0.488    | 0.566  |

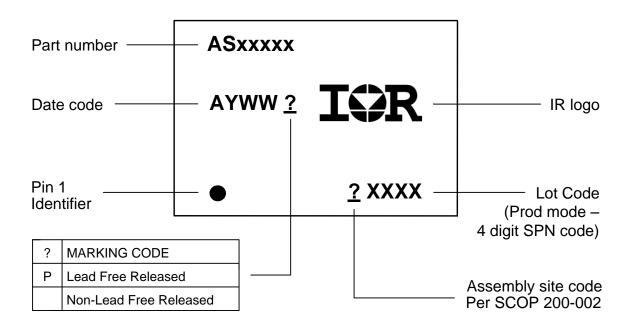

# **Part Marking Information**

Published by Infineon Technologies AG 81726 München, Germany © Infineon Technologies AG 2015 All Rights Reserved.

#### **IMPORTANT NOTICE**

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics ("Beschaffenheitsgarantie"). With respect to any examples, hints or any typical values stated herein and/or any information regarding the application of the product, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation warranties of non-infringement of intellectual property rights of any third party.

In addition, any information given in this document is subject to customer's compliance with its obligations stated in this document and any applicable legal requirements, norms and standards concerning customer's products and any use of the product of Infineon Technologies in customer's applications.

The data contained in this document is exclusively intended for technically trained staff. It is the responsibility of customer's technical departments to evaluate the suitability of the product for the intended application and the completeness of the product information given in this document with respect to such application.

For further information on the product, technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies office (www.infineon.com).

#### **WARNINGS**

Due to technical requirements products may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies office.

Except as otherwise explicitly approved by Infineon Technologies in a written document signed by authorized representatives of Infineon Technologies, Infineon Technologies' products may not be used in any applications where a failure of the product or any consequences of the use thereof can reasonably be expected to result in personal injury.