# High Performance 1:10 Multi-Voltage CMOS Buffer

#### **Features**

- 10 single-ended outputs Fanout Buffer

- Up to 200MHz output frequency

- Ultra low output additive jitter = 0.05ps (typ.)

- Selectable reference inputs support Xtal (10~50MHz), singleended and differential

- Low output skew ~ 50ps (typ.)

- Propagation delay ~2ns (typ@3.3V)

- 2.5V / 3.3V operation

- User configurable output VDD in different banks:

- Mixed 3.3V core/2.5V output operating supply

- Mixed 3.3V core/1.8V output operating supply

- Mixed 3.3V core/1.5V output operating supply

- Mixed 2.5V core/1.8V output operating supply

- Mixed 2.5V core/1.5V output operating supply

- Industrial temperature range: -40°C to +85°C

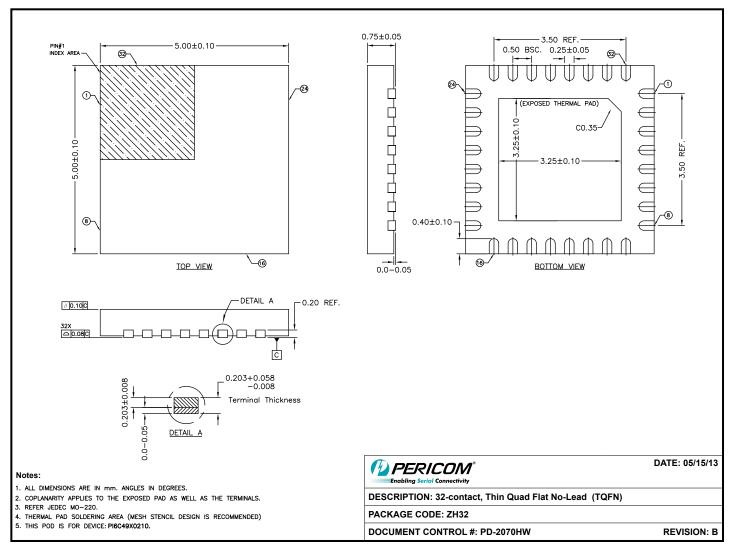

- Packaging (Pb-free & Green available):

- 32-pin TQFN (ZH)

### **Applications**

- · Networking systems including switches and Routers

- High frequency backplane based computing and telecom platforms

### **Description**

The PI6C49X0210 is a high performance multi-voltage 10-outputs CMOS Fanout Buffer with internal Crystal Oscillator. The XTAL range is from 10MHz to 50MHz. The device has a wide range of operating voltages of 2.5V and 3.3V. The device also provides user selectable output VDD option, which provides excellent flexibilities to users. This device is ideal for systems that need to distribute low jitter clock signals to multiple destinations.

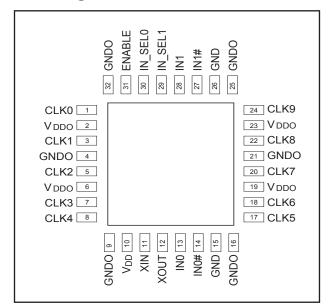

### **Pin Configuration**

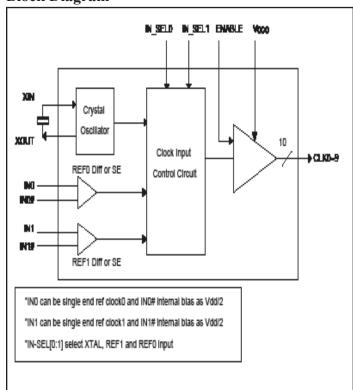

### **Block Diagram**

1

www.pericom.com PI6C49X0210 Rev F 12/13/13

# **Pin Description**

| Pin#                                 | Pin Name          | Ту     | pe                     | Description                                                                  |

|--------------------------------------|-------------------|--------|------------------------|------------------------------------------------------------------------------|

| 1, 3, 5, 7, 8, 17,<br>18, 20, 22, 24 | CLK0~9            | Output |                        | Clock Outputs                                                                |

| 2, 6, 19, 23                         | $V_{ m DDO}$      | Power  |                        | Output Power Supplier                                                        |

| 15, 26                               | GND               | Power  |                        | Output Ground                                                                |

| 4, 9, 16, 21, 25,<br>32              | GNDO              | Power  |                        | Core Ground                                                                  |

| 10                                   | $V_{\mathrm{DD}}$ | Power  |                        | Core Power Supplier                                                          |

| 11                                   | XIN               | Input  |                        | Crystal interface                                                            |

| 12                                   | XOUT              | Output |                        | Crystal interface                                                            |

| 13                                   | IN0               | Input  | Pull-down              | REF0 Diff or Single End                                                      |

| 14                                   | IN0#              | Input  | Pull-up/ Pull-<br>down | REF0 Diff, When IN0 is single end ref clock0 and IN0# internal bias as Vdd/2 |

| 27                                   | IN1#              | Input  | Pull-up/ Pull-<br>down | REF1 Diff, When IN1 is single end ref clock1 and IN1# internal bias as Vdd/2 |

| 28                                   | IN1               | Input  | Pull-down              | REF1 Diff or Single End                                                      |

| 30, 29                               | IN_SEL[0:1]       | Input  | Pull-down              | IN-SEL[0:1] select XTAL, REF1 and REF0 input                                 |

| 31                                   | ENABLE            | Input  |                        | Active High Output Enable                                                    |

# **Input Mode Selection Logic**

| IN_SEL0 | IN_SEL1 | Selected Input          |

|---------|---------|-------------------------|

| 1       | 1       | XTAL                    |

| 0       | 1       | XTAL                    |

| 1       | 0       | REF1 Diff or Single End |

| 0       | 0       | REF0 Diff or Single End |

# **Input/Output Operation State**

| Input State                      | Output State |

|----------------------------------|--------------|

| IN[0:1], IN[0:1]# open           | Logic Low    |

| IN[0:1], IN[0:1]# both to ground | Logic Low    |

| IN[0:1]=High, IN[0:1]# =Low      | Logic High   |

| IN[0:1]=Low, IN[0:1]# =High      | Logic Low    |

# **Output Mode Selection**

| ENABLE | Output CLK0~9  |

|--------|----------------|

| GND    | High-impedance |

| VDD    | Enabled        |

# **Power Supply DC Characteristics** $(V_{DD}/V_{DDO} = 3.3V \pm 5\%, T_A = -40^{\circ}C \text{ to } 85^{\circ}C)$

| Symbols            | Parameters            | Test Conditions | Min.  | Тур | Max.  | Units |

|--------------------|-----------------------|-----------------|-------|-----|-------|-------|

| $V_{\mathrm{DD}}$  | Core Supply Voltage   |                 | 3.135 | 3.3 | 3.465 | V     |

| $V_{ m DDO}$       | Output Supply Voltage |                 | 3.135 | 3.3 | 3.465 | V     |

| $I_{\mathrm{DD}}$  | Power Supply Current  | ENABLE = '0'    |       |     | 32    | mA    |

| $I_{\mathrm{DDO}}$ | Output Supply Current | ENABLE = '0'    |       |     | 1     | mA    |

# **Power Supply DC Characteristics** $(V_{DD}/V_{DDO} = 2.5V \pm 5\%, T_A = -40$ °C to 85°C)

| Symbols            | Parameters            | Test Conditions | Min.  | Тур | Max.  | Units |

|--------------------|-----------------------|-----------------|-------|-----|-------|-------|

| $V_{\mathrm{DD}}$  | Core Supply Voltage   |                 | 2.375 | 2.5 | 2.625 | V     |

| $V_{\mathrm{DDO}}$ | Output Supply Voltage |                 | 2.375 | 2.5 | 2.625 | V     |

| $I_{DD}$           | Power Supply Current  | ENABLE = '0'    |       |     | 15    | mA    |

| $I_{DDO}$          | Output Supply Current | ENABLE = '0'    |       |     | 0.7   | mA    |

### Power Supply DC Characteristics ( $V_{DD} = 3.3V \pm 5\%$ , $V_{DDO} = 2.5V \pm 5\%$ , $T_A = -40$ °C to 85°C)

| Symbols            | Parameters            | Test Conditions | Min.  | Тур | Max.  | Units |

|--------------------|-----------------------|-----------------|-------|-----|-------|-------|

| $V_{\mathrm{DD}}$  | Core Supply Voltage   |                 | 3.135 | 3.3 | 3.465 | V     |

| $V_{ m DDO}$       | Output Supply Voltage |                 | 2.375 | 2.5 | 2.625 | V     |

| $I_{\mathrm{DD}}$  | Power Supply Current  | ENABLE = '0'    |       |     | 29    | mA    |

| $I_{\mathrm{DDO}}$ | Output Supply Current | ENABLE = '0'    |       |     | 0.6   | mA    |

# Power Supply DC Characteristics ( $V_{DD} = 3.3V \pm 5\%$ , $V_{DDO} = 1.8V \pm 0.2V$ , $T_A = -40$ °C to 85°C)

| Symbols            | Parameters            | Test Conditions | Min.  | Тур | Max.  | Units |

|--------------------|-----------------------|-----------------|-------|-----|-------|-------|

| $V_{\mathrm{DD}}$  | Core Supply Voltage   |                 | 3.135 | 3.3 | 3.465 | V     |

| $V_{ m DDO}$       | Output Supply Voltage |                 | 1.6   | 1.8 | 2.0   | V     |

| $I_{\mathrm{DD}}$  | Power Supply Current  | ENABLE = '0'    |       |     | 29    | mA    |

| $I_{\mathrm{DDO}}$ | Output Supply Current | ENABLE = '0'    |       |     | 0.4   | mA    |

# **Power Supply DC Characteristics** ( $V_{DD} = 3.3V \pm 5\%$ , $V_{DDO} = 1.5V \pm 0.15V$ , $T_A = -40$ °C to 85°C)

| 11 0               | ( BB                  | DDO             | , , , |     |       |       |

|--------------------|-----------------------|-----------------|-------|-----|-------|-------|

| Symbols            | Parameters            | Test Conditions | Min.  | Тур | Max.  | Units |

| $V_{\mathrm{DD}}$  | Core Supply Voltage   |                 | 3.135 | 3.3 | 3.465 | V     |

| $V_{\mathrm{DDO}}$ | Output Supply Voltage |                 | 1.35  | 1.5 | 1.65  | V     |

| $I_{DD}$           | Power Supply Current  | ENABLE = '0'    |       |     | 29    | mA    |

| $I_{\mathrm{DDO}}$ | Output Supply Current | ENABLE = '0'    |       |     | 0.3   | mA    |

13-0169 3 www.pericom.com PI6C49X0210 Rev F 12/13/13

# **Power Supply DC Characteristics** ( $V_{DD} = 2.5V \pm 5\%$ , $V_{DDO} = 1.8V \pm 0.2V$ , $T_A = -40$ °C to 85°C)

| Symbols            | Parameters            | Test Conditions | Min.  | Тур | Max.  | Units |

|--------------------|-----------------------|-----------------|-------|-----|-------|-------|

| $V_{\mathrm{DD}}$  | Core Supply Voltage   |                 | 2.375 | 2.5 | 2.625 | V     |

| $V_{\mathrm{DDO}}$ | Output Supply Voltage |                 | 1.6   | 1.8 | 2.0   | V     |

| $I_{DD}$           | Power Supply Current  | ENABLE = '0'    |       |     | 13    | mA    |

| $I_{\mathrm{DDO}}$ | Output Supply Current | ENABLE = '0'    |       |     | 0.4   | mA    |

# Power Supply DC Characteristics ( $V_{DD}$ = 2.5V $\pm$ 5%, $V_{DDO}$ = 1.5V $\pm$ 0.15V, $T_A$ = -40°C to 85°C)

| Symbols           | Parameters            | Test Conditions | Min.  | Тур | Max.  | Units |

|-------------------|-----------------------|-----------------|-------|-----|-------|-------|

| $V_{\mathrm{DD}}$ | Core Supply Voltage   |                 | 2.375 | 2.5 | 2.625 | V     |

| $V_{ m DDO}$      | Output Supply Voltage |                 | 1.35  | 1.5 | 1.65  | V     |

| $I_{\mathrm{DD}}$ | Power Supply Current  | ENABLE = '0'    |       |     | 13    | mA    |

| $I_{DDO}$         | Output Supply Current | ENABLE = '0'    |       |     | 0.3   | mA    |

# **Single-Ended DC Characteristics** $(T_A = -40^{\circ}C \text{ to } 85^{\circ}C)$

| Symbols          | Parameters                                       | Test Conditions                              | Min. | Тур | Max.               | Units |

|------------------|--------------------------------------------------|----------------------------------------------|------|-----|--------------------|-------|

| V                | Innut II ah Valta aa                             | $V_{DD} = 3.3V \pm 5\%$                      | 2    |     | $V_{\rm DD} + 0.3$ | V     |

| V <sub>IH</sub>  | Input High Voltage                               | $V_{\rm DD} = 2.5 V \pm 5\%$                 | 1.7  |     | $V_{DD} + 0.3$     | V     |

| V                | Innut I am Valtage                               | $V_{DD} = 3.3V \pm 5\%$                      | -0.3 |     | 0.8                | V     |

| $V_{\rm IL}$     | Input Low Voltage                                | $V_{DD} = 2.5V \pm 5\%$                      | -0.3 |     | 0.7                | V     |

|                  |                                                  | $V_{\rm DDO} = 3.3 V \pm 5\%^{(1)}$          | 2.6  |     |                    | V     |

|                  |                                                  | $V_{DDO} = 2.5V \pm 5\%$                     | 2    |     |                    | V     |

|                  | Output High Voltage                              | $V_{\rm DDO} = 2.5 V \pm 5\%^{(1)}$          | 1.8  |     |                    | V     |

|                  | $(I_{OH} = -8mA)$                                | $V_{\rm DDO} = 1.8V \pm 0.2V^{(1)}$          | 1.5  |     |                    | V     |

| $V_{ m OH}$      |                                                  | $V_{DDO} = 1.5V \pm 0.15V^{(1)}$             | 1.0  |     |                    | V     |

|                  |                                                  | $V_{\rm DDO} = 3.3 V \pm 5\%$ (1)            | 3.0  |     |                    | V     |

|                  |                                                  | $V_{\rm DDO} = 2.5 V \pm 5\%$                | 2.0  |     |                    | V     |

|                  | Output High Voltage<br>(I <sub>OH</sub> = -12mA) | $V_{DDO} = 1.8V \pm 0.2V^{(1)}$              | 1.5  |     |                    | V     |

|                  |                                                  | $V_{DDO} = 1.5V \pm 0.15V^{(1)}$             | 1.0  |     |                    | V     |

|                  |                                                  | $V_{DD} = 3.3V \pm 5\%$ <sup>(1)</sup>       |      |     | 0.5                | V     |

|                  |                                                  | $V_{\rm DDO} = 2.5 V \pm 5\%$                |      |     | 0.5                | V     |

|                  | Output Low Voltage (I <sub>OH</sub> = 8mA)       | $V_{DDO} = 1.8V \pm 0.2V$                    |      |     | 0.4                | V     |

|                  |                                                  | $V_{\rm DDO} = 1.5V \pm 0.15V$               |      |     | 0.35               | V     |

| $V_{OL}$         |                                                  | $V_{\rm DDO} = 3.3 V \pm 5\%$ <sup>(1)</sup> |      |     | 0.25               | V     |

|                  |                                                  | $V_{\rm DDO} = 2.5 V \pm 5\%$                |      |     | 0.25               | V     |

|                  | Output Low Voltage (I <sub>OL</sub> = 12mA)      | $V_{DDO} = 1.8V \pm 0.2V$                    |      |     | 0.3                | V     |

|                  | ,                                                | $V_{\rm DDO} = 1.5 V \pm 0.15 V$             |      |     | 0.35               | V     |

| D                | Outroot Invest                                   | $V_{\rm DDO} = 3.3 V \pm 5\%$                | 7    |     | 10                 | Ω     |

| R <sub>OUT</sub> | Output Impedence                                 | $V_{\rm DDO} = 1.8V \pm 5\%$                 | 12   | 17  | 20                 | Ω     |

### **Notes:**

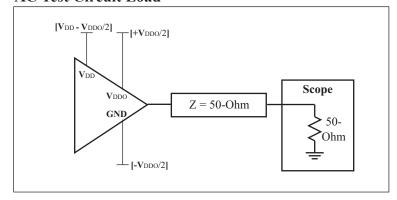

1. Outputs terminated with  $50\Omega$  to  $V_{DDO}$  /2. See Parameter Measurement section, "Load Test Circuit" diagrams.

# **Differential input DC Characteristics** $(T_A = -40^{\circ}C \text{ to } 85^{\circ}C)$

| Symbols                          | Parameters            |                      | Test Conditions                                         | Min. | Тур | Max.                   | Units |

|----------------------------------|-----------------------|----------------------|---------------------------------------------------------|------|-----|------------------------|-------|

| I <sub>IH</sub>                  | Input High<br>Current | IN[0:1],<br>IN[0:1]# | $V_{DD} = V_{IN} = 3.465V$<br>or 2.625V                 |      |     | 100                    | uA    |

| ī                                | Input Low             | IN[0:1]              | $V_{DD} = 3.465 V \text{ or}$<br>2.625 V $V_{IN} = 0 V$ | -1   |     |                        | uA    |

| $ m I_{IL}$                      | Current               | IN[0:1]#             | $V_{DD} = 3.465 V \text{ or}$<br>2.625 V $V_{IN} = 0 V$ | -50  |     |                        | uA    |

| V                                | Dools to Dools Is     | anut Valtaga (1)     | $V_{DD} = 3.3V$                                         | 0.25 |     | 1.3                    | V     |

| $V_{PP}$                         | Peak-to-Peak Input    |                      | $V_{\rm DD} = 2.5 V$                                    | 0.25 |     | 1.3                    | V     |

| V <sub>CMR</sub> Common Mode Inp |                       | e Input Voltage      | $V_{DD} = 3.3V$                                         | 0.5  |     | V <sub>DD</sub> -1.35V | V     |

|                                  |                       |                      | $V_{\rm DD} = 2.5 V$                                    | 0.5  |     | V <sub>DD</sub> -0.85V | v     |

- 1.  $V_{IL}$  should not be less than -0.3V.

- 2. Common mode voltage is defined as  $V_{IH}$ .

# 3.3V Absolute Maximum Ratings (Above which the useful life may be impaired. For user guidelines only, not tested.)

| Storage Temperature                        | -65°C to +150°C                |

|--------------------------------------------|--------------------------------|

| V <sub>DD</sub> , V <sub>DDO</sub> Voltage | -0.5V to +3.6V                 |

| Output Voltage (max. 4.6V)                 | -0.5V to V <sub>DD</sub> +0.5V |

| Input Voltage (max 4.6V)                   | -0.5V to V <sub>DD</sub> +0.5V |

#### Note:

Stresses greater than those listed under MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

### **AC Characteristics** (Over Operating Range: $V_{DD}/V_{DDO} = 3.3V \pm 5\%$ , $T_A = -40^{\circ}$ to 85°C)

| Parameters                 | De                     | scription                          | Test Conditions <sup>(1)</sup>                                        | Min. | Тур  | Max. | Units  |

|----------------------------|------------------------|------------------------------------|-----------------------------------------------------------------------|------|------|------|--------|

|                            |                        | Using External Crystal             |                                                                       | 10   |      | 50   |        |

| $f_{MAX}$                  | Output Frequency       | Using External Clock<br>Source (2) |                                                                       | DC   |      | 200  | MHz    |

| ode                        | Output Duty Cycle      |                                    | 125MHz                                                                | 45   |      | 55   | %      |

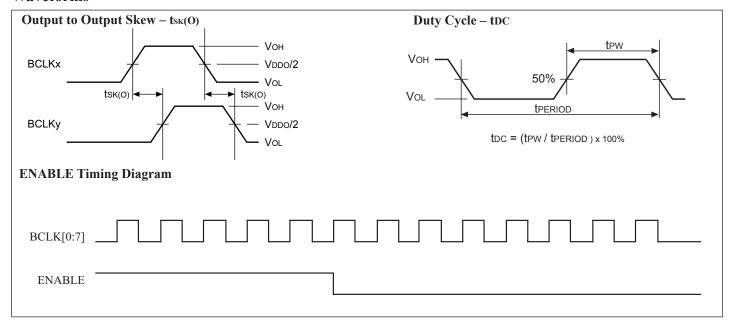

| t <sub>sk(o)</sub>         | Output Skew (3)        |                                    |                                                                       |      |      | 80   | ps     |

| tjit(Ø)                    | RMS Phase Jitter (I    | Random)                            | 25MHz crystal @<br>(Integration Range:<br>100Hz-1MHz)                 |      | 0.05 |      | ps     |

| <sup>†</sup> jit(additive) | Additive RMS Phas      | se Jitter (Random)                 | 125MHz reference<br>input @ (Integra-<br>tion Range: 12kHz-<br>20MHz) |      | 0.05 |      | ps     |

| $t_{ m R}/t_{ m F}$        | Output Rise/Fall Ti    | me                                 | 20% to 80%                                                            | 200  |      | 800  | ps     |

| t <sub>EN</sub>            | Output Enable Time (4) | ENABLE                             |                                                                       |      |      | 5    | cycles |

| t <sub>DIS</sub>           | Output Disable Tim     | e ENABLE                           |                                                                       |      |      | 5    | cycles |

| MUXisolation               | MUX Isolation          |                                    | 155.52MHz                                                             |      | 64   |      | dB     |

- 1. Unless noted otherwise, all parameters are tested with xtal @ f <= Fxtal\_max,; outputs are terminated @  $50\Omega$  to  $V_{DDO}/2$ , see waveforms.

- 2. Diff external clock source is driving IN0/IN0# and IN1/IN1# input. IN0/IN1 can be single end ref clock when IN0# /IN1# set as  $V_{DD}/2$

- 3. Identical conditions: loading, transitions, supply voltage, temperature, package type and speed grade.

- 4. These parameters are guaranteed, but not tested. Max delay is 4 cycles. Min. setup time = 3ns.

### **2.5V** Absolute Maximum Ratings (Above which the useful life may be impaired. For user guidelines only, not tested.)

| Storage Temperature                        | -65°C to +150°C                |

|--------------------------------------------|--------------------------------|

| V <sub>DD</sub> , V <sub>DDO</sub> Voltage | -0.5V to +3.6V                 |

| Output Voltage (max. 4.6V)                 | -0.5V to V <sub>DD</sub> +0.5V |

| Input Voltage (max 4.6V)                   | -0.5V to V <sub>DD</sub> +0.5V |

#### Note:

Stresses greater than those listed under MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

### **AC Characteristics** (Over Operating Range: $V_{DD}/V_{DDO} = 2.5V \pm 5\%$ , $T_A = -40^{\circ}$ to 85°C)

| Parameters          | De                  | scription                          | Test Conditions <sup>(1)</sup>            | Min. | Тур  | Max. | Units  |

|---------------------|---------------------|------------------------------------|-------------------------------------------|------|------|------|--------|

|                     |                     | Using External Crystal             |                                           | 10   |      | 50   |        |

| $f_{MAX}$           | Output Frequency    | Using External Clock<br>Source (2) |                                           | DC   |      | 200  | MHz    |

| odc                 | Output Duty Cycle   |                                    | 125MHz                                    | 45   |      | 55   | %      |

| t <sub>sk(o)</sub>  | Output Skew (3)     |                                    |                                           |      |      | 80   | ps     |

| t <sub>jit(Ø)</sub> | RMS Phase Jitter (I | Random)                            | 25MHz @ (Integration Range: 100Hz-1MHz)   |      | 0.06 |      | ps     |

| tjit(additive)      | Additive RMS Phas   | ee Jitter (Random)                 | 125MHz @ (Integration Range: 12kHz-20MHz) |      | 0.05 |      | ps     |

| $t_{ m R}/t_{ m F}$ | Output Rise/Fall Ti | me                                 | 20% to 80%                                | 200  |      | 800  | ps     |

| t <sub>EN</sub>     | Output Enable Time  | ENABLE                             |                                           |      |      | 5    | cycles |

| t <sub>DIS</sub>    | Output Disable Tim  | e ENABLE                           |                                           |      |      | 5    | cycles |

| MUXisolation        | MUX Isolation       |                                    | 155.52MHz                                 |      | 63   |      | dB     |

- 1. Unless noted otherwise, all parameters are tested with xtal @ f <= Fxtal max,; outputs are terminated @  $50\Omega$  to  $V_{DDO}/2$ , see waveforms.

- $2.\ \ Diff\ external\ clock\ source\ is\ driving\ IN0/IN0\#\ and\ IN1/IN1\#\ input.\ IN0/IN1\ can\ be\ single\ end\ ref\ clock\ when\ IN0\#\ /IN1\#\ set\ as\ V_{DD}/2$

- 3. Identical conditions: loading, transitions, supply voltage, temperature, package type and speed grade.

- 4. These parameters are guaranteed, but not tested. Max delay is 4 cycles. Min. setup time = 3ns.

# **AC Characteristics** (Over Operating Range: $V_{DD} = 3.3V \pm 5\%$ , $V_{DDO} = 2.5V \pm 5\%$ , $T_A = -40^{\circ}$ to $85^{\circ}$ C)

| Parameters                 | De                  | scription                          | Test Conditions <sup>(1)</sup>            | Min. | Тур  | Max. | Units  |

|----------------------------|---------------------|------------------------------------|-------------------------------------------|------|------|------|--------|

|                            |                     | Using External Crystal             |                                           | 10   |      | 50   |        |

| $f_{MAX}$                  | Output Frequency    | Using External Clock<br>Source (2) |                                           | DC   |      | 200  | MHz    |

| odc                        | Output Duty Cycle   |                                    | 125MHz                                    | 45   |      | 55   | %      |

| t <sub>sk(o)</sub>         | Output Skew (3)     | '                                  |                                           |      |      | 80   | ps     |

| t <sub>jit(Ø)</sub>        | RMS Phase Jitter (I | Random)                            | 25MHz @ (Integration Range: 100Hz-1MHz)   |      | 0.05 |      | ps     |

| <sup>†</sup> jit(additive) | Additive RMS Phas   | ee Jitter (Random)                 | 125MHz @ (Integration Range: 12kHz-20MHz) |      | 0.05 |      | ps     |

| $t_{ m R}/t_{ m F}$        | Output Rise/Fall Ti | me                                 | 20% to 80%                                | 200  |      | 800  | ps     |

| t <sub>EN</sub>            | Output Enable Time  | ENABLE                             |                                           |      |      | 5    | cycles |

| $t_{ m DIS}$               | Output Disable Tim  | e ENABLE                           |                                           |      |      | 5    | cycles |

| MUX <sub>isolation</sub>   | MUX Isolation       |                                    | 155.52MHz                                 |      | 62   |      | dB     |

- 1. Unless noted otherwise, all parameters are tested with xtal @  $f \le Fxtal_max$ ; outputs are terminated @  $50\Omega$  to  $V_{DDO}/2$ , see waveforms.

- 2. Diff external clock source is driving IN0/IN0# and IN1/IN1# input. IN0/IN1 can be single end ref clock when IN0# /IN1# set as  $V_{DD}/2$

- 3. Identical conditions: loading, transitions, supply voltage, temperature, package type and speed grade.

- 4. These parameters are guaranteed, but not tested. Max delay is 4 cycles. Min. setup time = 3ns.

### **AC Characteristics** (Over Operating Range: $V_{DD} = 3.3V \pm 5\%$ , $V_{DDO} = 1.8V \pm 0.2V$ , $T_A = -40^{\circ}$ to 85°C)

| Parameters               | De                  | scription                          | Test Conditions <sup>(1)</sup>            | Min. | Тур  | Max. | Units  |

|--------------------------|---------------------|------------------------------------|-------------------------------------------|------|------|------|--------|

|                          |                     | Using External Crystal             |                                           | 10   |      | 50   |        |

| $f_{MAX}$                | Output Frequency    | Using External Clock<br>Source (2) |                                           | DC   |      | 200  | MHz    |

| ode                      | Output Duty Cycle   |                                    | 125MHz                                    | 45   |      | 55   | %      |

| t <sub>sk(o)</sub>       | Output Skew (3)     |                                    |                                           |      |      | 80   | ps     |

| tjit(Ø)                  | RMS Phase Jitter (I | Random)                            | 25MHz @ (Integration Range: 100Hz-1MHz)   |      | 0.06 |      | ps     |

| tjit(additive)           | Additive RMS Phas   | se Jitter (Random)                 | 125MHz @ (Integration Range: 12kHz-20MHz) |      | 0.05 |      | ps     |

| $t_{ m R}/t_{ m F}$      | Output Rise/Fall Ti | me                                 | 20% to 80%                                | 200  |      | 900  | ps     |

| t <sub>EN</sub>          | Output Enable Time  | ENABLE                             |                                           |      |      | 5    | cycles |

| t <sub>DIS</sub>         | Output Disable Tim  | e ENABLE                           |                                           |      |      | 5    | cycles |

| MUX <sub>isolation</sub> | MUX Isolation       |                                    | 155.52MHz                                 |      | 58   |      | dB     |

- 1. Unless noted otherwise, all parameters are tested with xtal @  $f \le Fxtal_max$ ; outputs are terminated @  $50\Omega$  to  $V_{DDO}/2$ , see waveforms.

- 2. Diff external clock source is driving IN0/IN0# and IN1/IN1# input. IN0/IN1 can be single end ref clock when IN0# /IN1# set as  $V_{DD}/2$

- 3. Identical conditions: loading, transitions, supply voltage, temperature, package type and speed grade.

- 4. These parameters are guaranteed, but not tested. Max delay is 4 cycles. Min. setup time = 3ns.

### **AC Characteristics** (Over Operating Range: $V_{DD} = 3.3V \pm 5\%$ , $V_{DDO} = 1.5V \pm 0.15V$ , $T_A = -40^{\circ}$ to $85^{\circ}$ C)

| Parameters               | De                  | scription                          | Test Conditions <sup>(1)</sup>            | Min. | Тур  | Max. | Units  |

|--------------------------|---------------------|------------------------------------|-------------------------------------------|------|------|------|--------|

|                          |                     | Using External Crystal             |                                           | 10   |      | 50   |        |

| $f_{MAX}$                | Output Frequency    | Using External Clock<br>Source (2) |                                           | DC   |      | 200  | MHz    |

| ode                      | Output Duty Cycle   |                                    | 125MHz                                    | 45   |      | 55   | %      |

| t <sub>sk(o)</sub>       | Output Skew (3)     |                                    |                                           |      |      | 80   | ps     |

| tjit(Ø)                  | RMS Phase Jitter (I | Random)                            | 25MHz @ (Integration Range: 100Hz-1MHz)   |      | 0.07 |      | ps     |

| tjit(additive)           | Additive RMS Phas   | se Jitter (Random)                 | 125MHz @ (Integration Range: 12kHz-20MHz) |      | 0.05 |      | ps     |

| $t_{ m R}/t_{ m F}$      | Output Rise/Fall Ti | me                                 | 20% to 80%                                | 200  |      | 900  | ps     |

| t <sub>EN</sub>          | Output Enable Time  | ENABLE                             |                                           |      |      | 5    | cycles |

| t <sub>DIS</sub>         | Output Disable Tim  | e ENABLE                           |                                           |      |      | 5    | cycles |

| MUX <sub>isolation</sub> | MUX Isolation       |                                    | 155.52MHz                                 |      | 53   |      | dB     |

- 1. Unless noted otherwise, all parameters are tested with xtal @  $f \le Fxtal_max$ ; outputs are terminated @  $50\Omega$  to  $V_{DDO}/2$ , see waveforms.

- 2. Diff external clock source is driving IN0/IN0# and IN1/IN1# input. IN0/IN1 can be single end ref clock when IN0# /IN1# set as  $V_{DD}/2$

- 3. Identical conditions: loading, transitions, supply voltage, temperature, package type and speed grade.

- 4. These parameters are guaranteed, but not tested. Max delay is 4 cycles. Min. setup time = 3ns.

### **AC Characteristics** (Over Operating Range: $V_{DD} = 2.5V \pm 5\%$ , $V_{DDO} = 1.8V \pm 0.2V$ , $T_A = -40^{\circ}$ to $85^{\circ}$ C)

| Parameters          | De                  | scription                          | Test Conditions <sup>(1)</sup>            | Min. | Тур  | Max. | Units  |

|---------------------|---------------------|------------------------------------|-------------------------------------------|------|------|------|--------|

|                     |                     | Using External Crystal             |                                           | 10   |      | 50   |        |

| $f_{MAX}$           | Output Frequency    | Using External Clock<br>Source (2) |                                           | DC   |      | 200  | MHz    |

| odc                 | Output Duty Cycle   |                                    | 125MHz                                    | 45   |      | 55   | %      |

| t <sub>sk(o)</sub>  | Output Skew (3)     |                                    |                                           |      |      | 80   | ps     |

| t <sub>jit(Ø)</sub> | RMS Phase Jitter (F | Random)                            | 25MHz @ (Integration Range: 100Hz-1MHz)   |      | 0.06 |      | ps     |

| tjit(additive)      | Additive RMS Phas   | se Jitter (Random)                 | 125MHz @ (Integration Range: 12kHz-20MHz) |      | 0.05 |      | ps     |

| $t_{ m R}/t_{ m F}$ | Output Rise/Fall Ti | me                                 | 20% to 80%                                | 200  |      | 900  | ps     |

| $t_{\rm EN}$        | Output Enable Time  | ENABLE                             |                                           |      |      | 5    | cycles |

| t <sub>DIS</sub>    | Output Disable Tim  | e ENABLE                           |                                           |      |      | 5    | cycles |

| MUXisolation        | MUX Isolation       |                                    | 155.52MHz                                 |      | 59   |      | dB     |

- 1. Unless noted otherwise, all parameters are tested with xtal @  $f \le Fxtal_max$ ; outputs are terminated @  $50\Omega$  to  $V_{DDO}/2$ , see waveforms.

- 2. Diff external clock source is driving IN0/IN0# and IN1/IN1# input. IN0/IN1 can be single end ref clock when IN0# /IN1# set as  $V_{DD}/2$

- 3. Identical conditions: loading, transitions, supply voltage, temperature, package type and speed grade.

- 4. These parameters are guaranteed, but not tested. Max delay is 4 cycles. Min. setup time = 3ns.

### **AC Characteristics** (Over Operating Range: $V_{DD} = 2.5V \pm 5\%$ , $V_{DDO} = 1.5V \pm 0.15V$ , $T_A = -40^{\circ}$ to 85°C)

| Parameters                 | Des                  | scription                          | Test Conditions <sup>(1)</sup>            | Min. | Тур  | Max. | Units  |

|----------------------------|----------------------|------------------------------------|-------------------------------------------|------|------|------|--------|

|                            |                      | Using External Crystal             |                                           | 10   |      | 50   |        |

| $f_{MAX}$                  | Output Frequency     | Using External Clock<br>Source (2) |                                           | DC   |      | 200  | MHz    |

| odc                        | Output Duty Cycle    |                                    | 125MHz                                    | 45   |      | 55   | %      |

| t <sub>sk(o)</sub>         | Output Skew (3)      | ,                                  |                                           |      |      | 80   | ps     |

| $t_{jit(\emptyset)}$       | RMS Phase Jitter (F  | andom)                             | 25MHz @ (Integration Range: 100Hz-1MHz)   |      | 0.08 |      | ps     |

| <sup>†</sup> jit(additive) | Additive RMS Phas    | e Jitter (Random)                  | 125MHz @ (Integration Range: 12kHz-20MHz) |      | 0.05 |      | ps     |

| $t_{\rm R}/t_{\rm F}$      | Output Rise/Fall Tir | me                                 | 20% to 80%                                | 200  |      | 900  | ps     |

| t <sub>EN</sub>            | Output Enable Time   | ENABLE                             |                                           |      |      | 5    | cycles |

| t <sub>DIS</sub>           | Output Disable Tim   | e ENABLE                           |                                           |      |      | 5    | cycles |

| MUX <sub>isolation</sub>   | MUX Isolation        | <del>-</del>                       | 155.52MHz                                 |      | 55   |      | dB     |

- 1. Unless noted otherwise, all parameters are tested with xtal @  $f \le Fxtal_max$ ; outputs are terminated @  $50\Omega$  to  $V_{DDO}/2$ , see waveforms.

- 2. Diff external clock source is driving IN0/IN0# and IN1/IN1# input. IN0/IN1 can be single end ref clock when IN0# /IN1# set as  $V_{DD}/2$

- 3. Identical conditions: loading, transitions, supply voltage, temperature, package type and speed grade.

- 4. These parameters are guaranteed, but not tested. Max delay is 4 cycles. Min. setup time = 3ns.

### Waveforms

### **AC Test Circuit Load**

Note:  $V_{DD}/V_{DDO} = 1.8V \pm 0.2V,$   $2.5V \pm 5\%,$   $3.3V \pm 5\%$

**Crystal Characteristic** (link to "http://www.pericom.com/products/timing/crystals/index.php" for more detailed and different size crystal specifications)

| Parameters         | Description                  | Min | Тур | Max. | Units |

|--------------------|------------------------------|-----|-----|------|-------|

| OSCMODE            | Mode of Oscillation          | 1   |     |      |       |

| FREQ               | Frequency                    | 10  | 25  | 50   | MHz   |

| ESR <sup>(1)</sup> | Equivalent Series Resistance | 30  |     | 50   | Ohm   |

| CLOAD              | Load Capacitance             |     | 18  |      | pF    |

| CSHUNT             | Shunt Capacitance            |     |     | 7    | pF    |

| DRIVE level        |                              |     |     | 1    | mW    |

Note: 1. ESR value is dependent upon frequency of oscillation

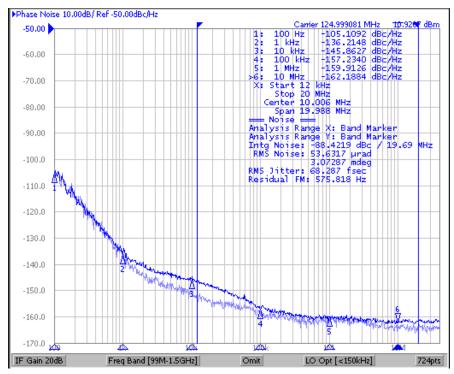

### Phase Noise and Additive Jitter

Output phase noise (Dark Blue) vs Input Phase noise (light blue)

Additive jitter is calculated at ~47fs RMS (12kHz to 20MHz). Additive jitter =  $\sqrt{\text{Output jitter}^2 - \text{Input jitter}^2}$

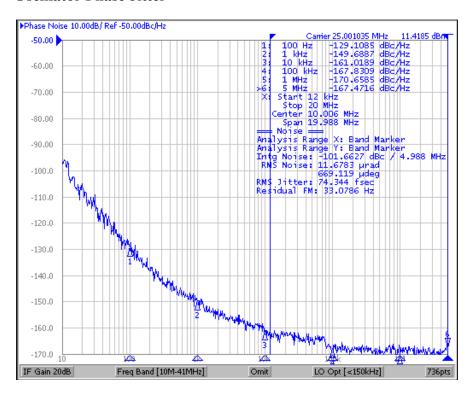

### **Oscillator Phase Jitter**

### **Application Information**

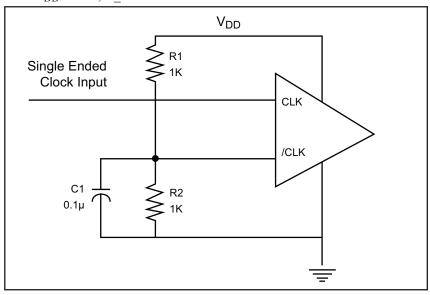

### Wiring the differential input to accept single ended levels

Figure 1 shows how the differential input can be wired to accept single ended levels. The reference voltage  $V_REF = V_{DD}/2$  is generated by the bias resistors R1, R2 and C1. This bias circuit should be located as close as possible to the input pin. The ratio of R1 and R2 might need to be adjusted to postion the  $V_REF$  in the center of the input voltage swing. For example, if the input clock swing is only 2.5V and  $V_{DD} = 3.3V$ ,  $V_REF$  should be 1.25V and R1/R2 = 0.609.

Figure 1. Single-ended input to Differential input device

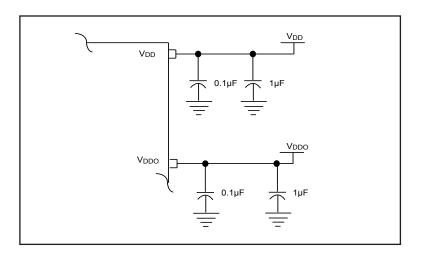

### **Power Supply Filtering Techniques**

As in any high speed analog circuitry, the power supply pins are vulnerable to random noise. To achieve optimum jitter performance, power supply isolation is required. All power pins should be individually connected to the power supply plane through vias,  $0.1\mu F$  and  $1\mu F$  bypass capacitors should be used for each pin.

### **Application Notes**

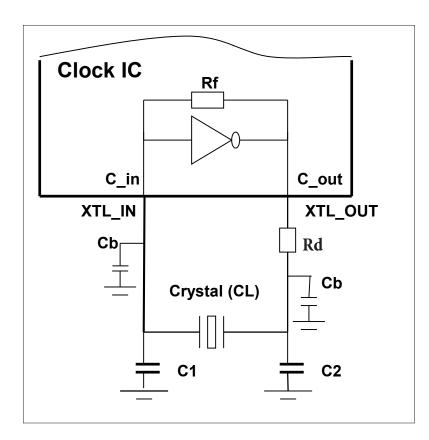

# Clock IC Crystal loading cap. design guide

CL = crystal spec. loading cap.

$C_{in}/out = (3\sim 5pF)$  of IC pin cap.

$Cb = PCB \text{ trace } (2\sim4pF)$

C1,C2 = load cap. of design

Rd = 50 to 100ohm drive level limit (Optimized for 25MHz 18pf XTAL without Rd)

Design guide:  $C1=C2=2 *CL - (Cb + C_in/out)$  to meet target +/-ppm < 20 ppm

Example1: Select CL=18 pF crystal, C1=C2=2\*(18pF) - (4pF+5pF)=27pF, check datasheet too

Example2: For higher frequency crystal ( $\Rightarrow$ 20MHz), can use formula C1=C2=2\*(CL-6), can do fine tune of C1, C2 for more accurate ppm if necessary

### Thermal Information

| Symbol           | Description                            | Condition |           |

|------------------|----------------------------------------|-----------|-----------|

| $\Theta_{ m JA}$ | Junction-to-ambient thermal resistance | Still air | 44.7 °C/W |

| $\Theta_{ m JC}$ | Junction-to-case thermal resistance    |           | 21.7 °C/W |

#### Note:

• For latest package info, please check: http://www.pericom.com/products/packaging/mechanicals.php

# Ordering Information<sup>(1,2,3)</sup>

| Ordering Code   | Package Code | Package Description           |

|-----------------|--------------|-------------------------------|

| PI6C49X0210ZHIE | ZH           | Pb-Free and Green 32-pin TQFN |

#### **Notes:**

- 1. Thermal characteristics can be found on the company web site at www.pericom.com/packaging/

- 2. E = Pb-free and Green

- 3. X suffix = Tape/Reel

Pericom Semiconductor Corporation • 1-800-435-2336 • www.pericom.com

Downloaded from Arrow.com.