# Low Voltage, Micropower, Quad Operational Amplifier

**OP490**

#### **FEATURES**

Single/dual-supply operation

1.6 V to 36 V

±0.8 V to ±18 V

Single-supply operation; input and output voltage ranges include ground

Low supply current: 80 µA maximum

High output drive: 5 mA minimum

Low offset voltage: 1.0 mV maximum

High open-loop gain: 800 V/mV typical

Industry-standard quad pinouts

### **GENERAL DESCRIPTION**

The OP490 is a high performance micropower quad op amp that operates from a single supply of 1.6 V to 36 V or from dual supplies of  $\pm 0.8$  V to  $\pm 18$  V. The input voltage range includes the negative rail allowing the OP490 to accommodate input signals down to ground in single-supply operation. The output swing of the OP490 also includes ground when operating from a single supply, enabling zero-in, zero-out operation.

The quad OP490 draws less than 20  $\mu A$  of quiescent supply current per amplifier, but each amplifier is able to deliver over 5 mA of output current to a load. Input offset voltage is under

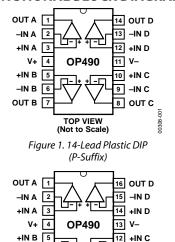

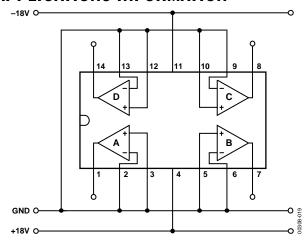

#### **FUNCTIONAL BLOCK DIAGRAMS**

NC = NO CONNECT

Figure 2. 16-Lead SOIC

(S-Suffix)

TOP VIEW

11 -IN C 10 OUT C

0.5 mV. Gain exceeds over 400,000 and CMR is better than 90 dB. A PSRR of under 5.6  $\mu$ V/V minimizes offset voltage changes experienced in battery-powered systems.

-IN B 6

OUT B 7

The quad OP490 combines high performance with the space and cost savings of quad amplifiers. The minimal voltage and current requirements of the OP490 make it ideal for battery and solar-powered applications, such as portable instruments and remote sensors.

## **OP490\* Product Page Quick Links**

Last Content Update: 08/30/2016

## Comparable Parts <a> □</a>

View a parametric search of comparable parts

## Documentation <a>□</a>

### **Application Notes**

AN-649: Using the Analog Devices Active Filter Design Tool

#### **Data Sheet**

- OP490: Low Voltage Micropower Quad Operational Amplifier Data Sheet

- OP490: Military Data Sheet

## Tools and Simulations

• OP490 SPICE Macro-Model

## Design Resources <a>□</a>

- OP490 Material Declaration

- PCN-PDN Information

- · Quality And Reliability

- · Symbols and Footprints

### Discussions <a>□</a>

View all OP490 EngineerZone Discussions

## Sample and Buy -

Visit the product page to see pricing options

## Technical Support <a> □</a>

Submit a technical question or find your regional support number

<sup>\*</sup> This page was dynamically generated by Analog Devices, Inc. and inserted into this data sheet. Note: Dynamic changes to the content on this page does not constitute a change to the revision number of the product data sheet. This content may be frequently modified.

## **TABLE OF CONTENTS**

| Features                                                |

|---------------------------------------------------------|

| Functional Block Diagrams                               |

| General Description                                     |

| Revision History                                        |

| Specifications                                          |

| Electrical Characteristics                              |

| Absolute Maximum Ratings 5                              |

| Thermal Resistance                                      |

| ESD Caution                                             |

| Typical Performance Characteristics 6                   |

| Applications Information9                               |

|                                                         |

| REVISION HISTORY                                        |

| 5/10—Rev. D to Rev. E                                   |

| Changes to Features Section                             |

| Changes to Figure 24                                    |

| 7/09—Rev. C to Rev. D                                   |

| Deleted 14-Lead CERDIP (Y-Suffix)                       |

| Deleted Figure 1, Renumbered Figures Sequentially 1     |

| Changes to Table 1                                      |

| Changes to Table 2                                      |

| Changes to Figure 16                                    |

| Updated Outline Dimensions                              |

| Changes to Ordering Guide                               |

| 4/02—Rev. B to Rev. C                                   |

| Deleted 28-Pin LCC (TC-Suffix) Pin Connection Diagram 1 |

| Deleted Electrical Characteristics                      |

| Edits to Absolute Maximum Ratings 6                     |

| Edits to Ordering Guide                                 |

|    | Battery-Powered Applications                          | 9  |

|----|-------------------------------------------------------|----|

|    | Single-Supply Output Voltage Range                    | 9  |

|    | Input Voltage Protection                              | 10 |

|    | Micropower Voltage-Controlled Oscillator              | 10 |

|    | Micropower Single-Supply Quad Voltage-Output 8-Bit DA | С  |

|    |                                                       | 11 |

|    | High Output Amplifier                                 | 12 |

|    | Single-Supply Micropower Quad Programmable Gain       |    |

|    | Amplifier                                             | 12 |

| Oı | utline Dimensions                                     | 14 |

|    | Ordering Guide                                        | 15 |

## **SPECIFICATIONS**

### **ELECTRICAL CHARACTERISTICS**

@  $V_{\text{S}}$  =  $\pm 1.5$  V to  $\pm 15$  V,  $T_{\text{A}}$  =  $25^{\circ}\text{C}$  , unless otherwise noted.

Table 1.

| Parameter                          | Symbol             | Conditions                                                            | Min   | Тур   | Max | Unit   |

|------------------------------------|--------------------|-----------------------------------------------------------------------|-------|-------|-----|--------|

| INPUT CHARACTERISTICS              |                    |                                                                       |       |       |     |        |

| Input Offset Voltage               | Vos                |                                                                       |       | 0.6   | 1.0 | mV     |

| Input Offset Current               | los                | $V_{CM} = 0 V$                                                        |       | 0.4   | 5   | nA     |

| Input Bias Current                 | I <sub>B</sub>     | $V_{CM} = 0 V$                                                        |       | 4.2   | 25  | nA     |

| Large Signal Voltage Gain          | Avo                | $V_S = \pm 15 \text{ V}, V_O = \pm 10 \text{ V}$                      |       |       |     |        |

|                                    |                    | $R_L = 100 \text{ k}\Omega$                                           | 400   | 800   |     | V/mV   |

|                                    |                    | $R_L = 10 \text{ k}\Omega$                                            | 200   | 400   |     | V/mV   |

|                                    |                    | $R_L = 2 k\Omega$                                                     | 100   | 200   |     | V/mV   |

|                                    |                    | $V+=5 V, V-=0 V, 1 V < V_0 < 4 V$                                     |       |       |     |        |

|                                    |                    | $R_L = 100 \text{ k}\Omega$                                           | 100   | 250   |     | V/mV   |

|                                    |                    | $R_L = 10 \text{ k}\Omega$                                            | 70    | 140   |     | V/mV   |

| Input Voltage Range <sup>1</sup>   | IVR                | V+=5 V, V-=0 V                                                        | 0     |       | 4   | V      |

| Common-Mode Rejection Ratio        | CMRR               | $V+=5V, V-=0V, 0V < V_{CM} < 4V$                                      | 80    | 100   |     | dB     |

| ·                                  |                    | $V_S = \pm 15 \text{ V}, -15 \text{ V} < V_{CM} < +13.5 \text{ V}$    | 90    | 120   |     | dB     |

| Input Resistance Differential Mode | R <sub>IN</sub>    | $V_{S} = \pm 15 \text{ V}$                                            |       | 30    |     | ΜΩ     |

| Input Resistance Common-Mode       | R <sub>INCM</sub>  | $V_{S} = \pm 15 \text{ V}$                                            |       | 20    |     | GΩ     |

| •                                  |                    |                                                                       |       |       |     |        |

| OUTPUT CHARACTERISTICS             |                    |                                                                       |       |       |     |        |

| Output Voltage Swing               | V <sub>O L</sub>   | $V_S = \pm 15 \text{ V}, R_L = 10 \text{ k}\Omega$                    | ±13.5 | ±14.2 |     | ٧      |

|                                    |                    | $V_S = \pm 15 \text{ V}, R_L = 2 \text{ k}\Omega$                     | ±10.5 | ±11.5 |     | V      |

| Output Voltage High                | V <sub>OH</sub>    | $V+ = 5 V, V- = 0 V, R_L = 2 k\Omega$                                 | 4.0   | 4.2   |     | ٧      |

| Output Voltage Low                 | V <sub>OL</sub>    | $V+ = 5 V, V- = 0 V, R_L = 10 k\Omega$                                |       | 100   | 500 | μV     |

| Capacitive Load Stability          |                    | $A_V = 1$                                                             |       | 650   |     | pF     |

|                                    |                    |                                                                       |       |       |     |        |

| DYNAMIC PERFORMANCE                |                    |                                                                       |       |       |     |        |

| Slew Rate                          | SR                 | $V_S = \pm 15 \text{ V}$                                              | 5     | 12    |     | V/ms   |

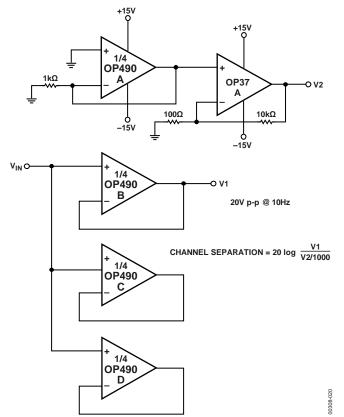

| Channel Separation <sup>2</sup>    | CS                 | $f_0 = 10 \text{ Hz}, V_0 = 20 \text{ V p-p}, V_S = \pm 15 \text{ V}$ | 120   | 150   |     | dB     |

| Gain Bandwidth Product             | GBWP               | $A_V = 1$                                                             |       | 20    |     | kHz    |

| POWER SUPPLY                       |                    |                                                                       |       |       |     |        |

| Power Supply Rejection Ratio       | PSRR               |                                                                       |       | 3.2   | 10  | μV/V   |

| Supply Current (All Amplifiers)    | Isy                | $V_s = \pm 1.5 V$ , no load                                           |       | 40    | 60  | μΑ     |

|                                    |                    | $V_s = \pm 15 \text{ V}$ , no load                                    |       | 60    | 80  | μA     |

|                                    |                    | 13 2.3 1,110 1044                                                     |       | •     | -   | P'' '  |

| NOISE PERFORMANCE                  |                    |                                                                       |       |       |     |        |

| Voltage Noise                      | e <sub>n</sub> p-p | $f_0 = 0.1 \text{ Hz to } 10 \text{ Hz}, V_S = \pm 15 \text{ V}$      |       | 3     |     | μV p-p |

| Voltage Noise Density              | e <sub>n</sub>     | f = 1 kHz                                                             |       | 60    |     | nV/√Hz |

| Current Noise Density              | İn                 | f = 1 kHz                                                             |       | 0.07  |     | pA/√Hz |

<sup>&</sup>lt;sup>1</sup> Guaranteed by CMRR test. <sup>2</sup> Guaranteed but not 100% tested.

@  $V_{\text{S}} = \pm 1.5~V$  to  $\pm 15~V,\, -40 ^{\circ}C \leq T_{\text{A}} \leq +85 ^{\circ}C$

Table 2.

| Parameter                          | Symbol          | Conditions                                                         | Min | Тур | Max   | Unit  |

|------------------------------------|-----------------|--------------------------------------------------------------------|-----|-----|-------|-------|

| INPUT CHARACTERISTICS              |                 |                                                                    |     |     |       |       |

| Input Offset Voltage               | Vos             |                                                                    |     | 0.8 | 1.5   | mV    |

| Average Input Offset Voltage Drift | TCVos           | $V_S = \pm 15 \text{ V}$                                           |     | 4   |       | μV/°C |

| Input Offset Current               | los             | $V_{CM} = 0 V$                                                     |     | 1.3 | 7     | nA    |

| Input Bias Current                 | I <sub>B</sub>  | $V_{CM} = 0 V$                                                     |     | 4.4 | 25    | nA    |

| Large Signal Voltage Gain          | Avo             | $V_S = \pm 15 \text{ V}, V_O = \pm 10 \text{ V}$                   |     |     |       |       |

|                                    |                 | $R_L = 100 \text{ k}\Omega$                                        | 300 | 600 |       | V/mV  |

|                                    |                 | $R_L = 10 \text{ k}\Omega$                                         | 150 | 250 |       | V/mV  |

|                                    |                 | $R_L = 2 k\Omega$                                                  | 75  | 125 |       | V/mV  |

|                                    |                 | $V+ = 5 V, V- = 0 V, 1 V < V_0 < 4 V$                              |     |     |       |       |

|                                    |                 | $R_L = 100 \text{ k}\Omega$                                        | 80  | 160 |       | V/mV  |

|                                    |                 | $R_L = 10 \text{ k}\Omega$                                         | 40  | 90  |       | V/mV  |

| Input Voltage Range <sup>1</sup>   | IVR             | V+ = 5 V, V- = 0 V                                                 | 0.3 |     | 5     | V     |

|                                    |                 |                                                                    | -15 |     | +13.5 | V     |

| Common-Mode Rejection Ratio        | CMRR            | $V+=5V, V-=0V, 0V < V_{CM} < 3.5V$                                 | 80  | 100 |       | dB    |

|                                    |                 | $V_S = \pm 15 \text{ V}, -15 \text{ V} < V_{CM} < +13.5 \text{ V}$ | 90  | 110 |       | dB    |

| OUTPUT CHARACTERISTICS             |                 |                                                                    |     |     |       |       |

| Output Voltage Swing               | Vo              | $V_S = \pm 15 \text{ V}$                                           | ±13 | ±14 |       | V     |

|                                    |                 | $R_L = 2 k\Omega$                                                  | ±10 | ±11 |       | ٧     |

| Output Voltage High                | V <sub>OH</sub> | $V+ = 5 V, V- = 0 V, R_L = 2 k\Omega$                              | 3.9 | 4.1 |       | V     |

| Output Voltage Low                 | V <sub>OL</sub> | $V+ = 5 V, V- = 0 V, R_L = 10 k\Omega$                             |     | 100 | 500   | μV    |

| POWER SUPPLY                       |                 |                                                                    |     |     |       |       |

| Power Supply Rejection Ratio       | PSRR            |                                                                    |     | 5.6 | 17.8  | μV/V  |

| Supply Current (All Amplifiers)    | I <sub>SY</sub> | $V_S = \pm 1.5 V$ , no load                                        |     | 60  | 100   | mA    |

|                                    |                 | $V_S = \pm 15 \text{ V}$ , no load                                 |     | 75  | 120   | mA    |

<sup>&</sup>lt;sup>1</sup> Guaranteed by CMRR test.

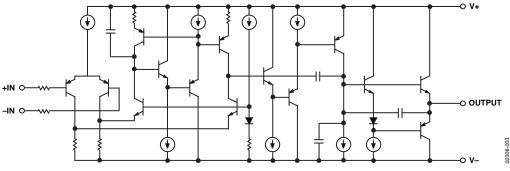

Figure 3. Simplified Schematic

## **ABSOLUTE MAXIMUM RATINGS**

Table 3.

| Parameter                                    | Rating                           |

|----------------------------------------------|----------------------------------|

| Supply Voltage                               | ±18 V                            |

| Digital Input Voltage                        | [(V-) - 20 V] to $[(V+) + 20 V]$ |

| Common-Mode Input Voltage                    | [(V-) - 20 V] to $[(V+) + 20 V]$ |

| Output Short-Circuit Duration                | Continuous                       |

| Storage Temperature Range                    | −65°C to +150°C                  |

| Operating Temperature Range                  | -40°C to +85°C                   |

| Junction Temperature (T <sub>J</sub> ) Range | −65°C to +150°C                  |

| Lead Temperature (Soldering,                 | 300°C                            |

| 60 sec)                                      |                                  |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### THERMAL RESISTANCE

$\theta_{JA}$  is specified for worst-case mounting conditions, that is,  $\theta_{JA}$  is specified for a device in socket for the PDIP package;  $\theta_{JA}$  is specified for a device soldered to a printed circuit board (PCB) for the SOIC package.

Table 4.

| Package Type              | θја | <b>Ө</b> лс | Unit |

|---------------------------|-----|-------------|------|

| 14-Lead PDIP_N (S-Suffix) | 76  | 33          | °C/W |

| 16-Lead SOIC_R (S-Suffix) | 92  | 27          | °C/W |

#### **ESD CAUTION**

**ESD (electrostatic discharge) sensitive device.**Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

## TYPICAL PERFORMANCE CHARACTERISTICS

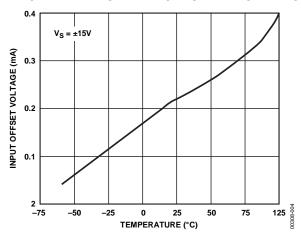

Figure 4. Input Offset Voltage vs. Temperature

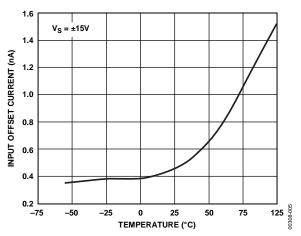

Figure 5. Input Offset Current vs. Temperature

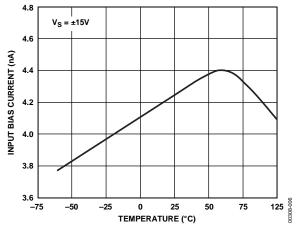

Figure 6. Input Bias Current vs. Temperature

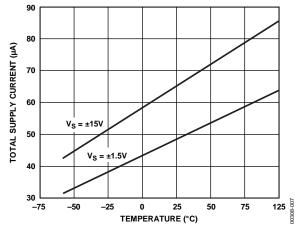

Figure 7. Total Supply Current vs. Temperature

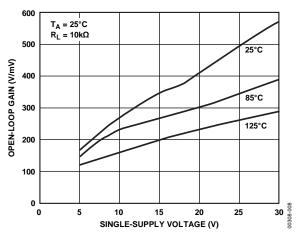

Figure 8. Open-Loop Gain vs. Single-Supply Voltage

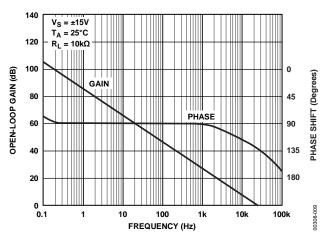

Figure 9. Open-Loop Gain and Phase Shift vs. Frequency

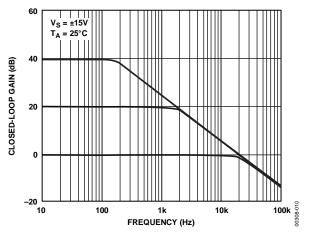

Figure 10. Closed-Loop Gain vs. Frequency

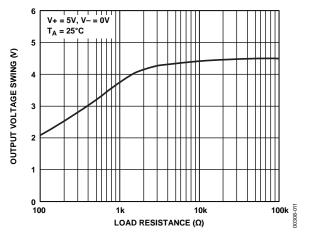

Figure 11. Output Voltage Swing vs. Load Resistance

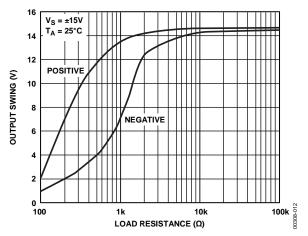

Figure 12. Output Voltage Swing vs. Load Resistance

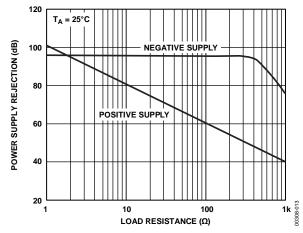

Figure 13. Power Supply Rejection vs. Frequency

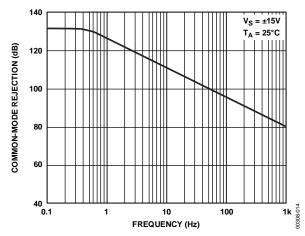

Figure 14. Common-Mode Rejection vs. Frequency

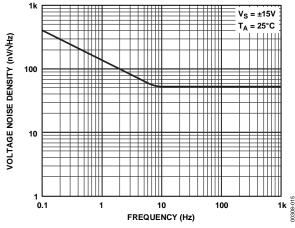

Figure 15. Voltage Noise Density vs. Frequency

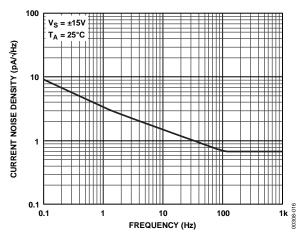

Figure 16. Current Noise Density vs. Frequency

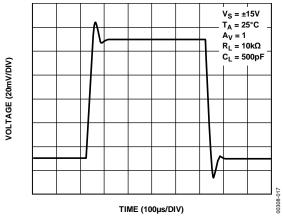

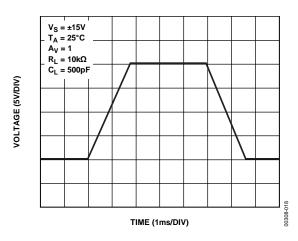

Figure 17. Small Signal Transient Response

Figure 18. Large Signal Transient Response

### APPLICATIONS INFORMATION

Figure 19. Burn-In Circuit

Figure 20. Channel Separation Test Circuit

#### **BATTERY-POWERED APPLICATIONS**

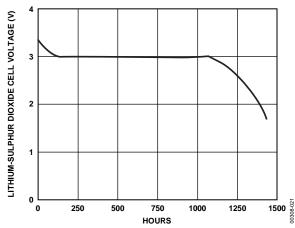

The OP490 can be operated on a minimum supply voltage of 1.6 V or with dual supplies of  $\pm 0.8$  V drawing only 60  $\mu A$  of supply current. In many battery-powered circuits, the OP490 can be continuously operated for hundreds of hours before requiring battery replacement, thereby reducing equipment downtime and operating costs.

High performance portable equipment and instruments frequently use lithium cells because of their long shelf life, light weight, and high energy density relative to older primary cells. Most lithium cells have a nominal output voltage of 3 V and are noted for a flat discharge characteristic. The low supply current requirement of the OP490, combined with the flat discharge characteristic of the lithium cell, indicates that the OP490 can be operated over the entire useful life of the cell. Figure 21 shows the typical discharge characteristic of a 1 Ah lithium cell powering an OP490 with each amplifier, in turn, driving full output swing into a 100  $k\Omega$  load.

Figure 21. Lithium-Sulphur Dioxide Cell Discharge Characteristic with OP490 and  $100 \, k\Omega$  Loads

#### SINGLE-SUPPLY OUTPUT VOLTAGE RANGE

In single-supply operation the input and output ranges of the OP490 include ground. This allows true zero-in, zero-out operation. The output stage provides an active pull-down to around 0.8 V above ground. Below this level, a load resistance of up to 1  $M\Omega$  to ground is required to pull the output down to zero.

In the region from ground to 0.8 V, the OP490 has voltage gain equal to the data sheet specification. Output current source capability is maintained over the entire voltage range including ground.

#### INPUT VOLTAGE PROTECTION

The OP490 uses a PNP input stage with protection resistors in series with the inverting and noninverting inputs. The high breakdown of the PNP transistors coupled with the protection resistors provides a large amount of input protection, allowing the inputs to be taken 20 V beyond either supply without damaging the amplifier.

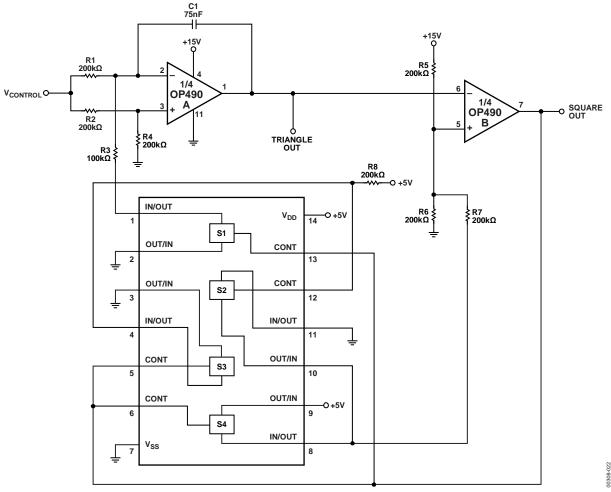

# MICROPOWER VOLTAGE-CONTROLLED OSCILLATOR

An OP490 in combination with an inexpensive quad CMOS switch comprise the precision  $V_{\rm CO}$  of Figure 22. This circuit provides triangle and square wave outputs and draws only 75  $\mu$ A from a 5 V supply. A acts as an integrator; S1 switches the

charging current symmetrically to yield positive and negative ramps. The integrator is bounded by B, which acts as a Schmitt trigger with a precise hysteresis of 1.67 V, set by Resistors R5, R6, and R7, and the associated CMOS switches. The resulting output of A is a triangle wave with upper and lower levels of 3.33 V and 1.67 V. The output of B is a square wave with almost rail-to-rail swing. With the components shown, frequency of operation is given by the equation

$$f_{OUT} = V_{CONTROL} \text{ (Volts)} \times 10 \text{ Hz/V}$$

but this is easily changed by varying C1. The circuit operates well up to a few hundred hertz.

Figure 22. Micropower Voltage Controlled Oscillator

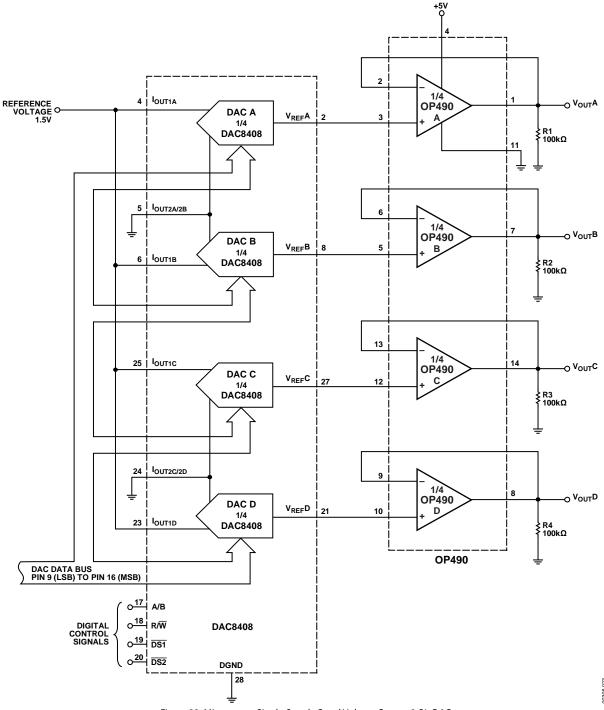

### MICROPOWER SINGLE-SUPPLY QUAD VOLTAGE-**OUTPUT 8-BIT DAC**

The circuit shown in Figure 23 uses the DAC8408 CMOS quad 8-bit DAC, and the OP490 to form a single-supply quad voltage output DAC with a supply drain of only 140  $\mu$ A. The DAC8408 is used in voltage switching mode and each DAC has an output resistance ( $\approx$ 10 k $\Omega$ ) independent of the digital input code. The output amplifiers act as buffers to avoid loading the DACs. The  $100~k\Omega$  resistors ensure that the OP490 outputs swing below 0.8 V when required.

Figure 23. Micropower Single-Supply Quad Voltage Output 8-Bit DAC Rev. E | Page 11 of 16

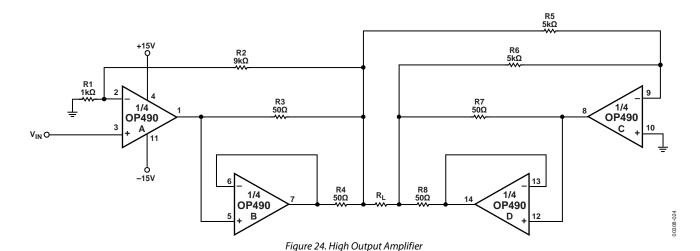

#### **HIGH OUTPUT AMPLIFIER**

The amplifier shown in Figure 24 is capable of driving 25 V p-p into a 1 k $\Omega$  load. Design of the amplifier is based on a bridge configuration. A amplifies the input signal and drives the load with the help of B. Amplifier C is a unity-gain inverter which drives the load with help from D. Gain of the high output amplifier with the component values shown is 10, but can easily be changed by varying R1 or R2.

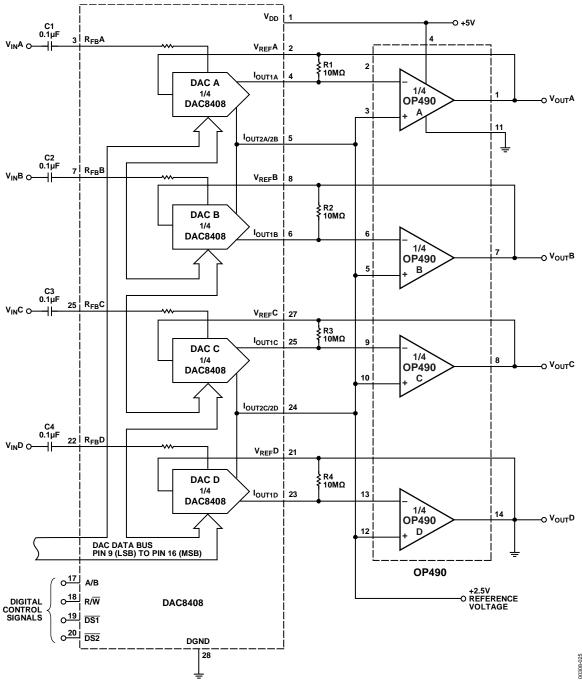

# SINGLE-SUPPLY MICROPOWER QUAD PROGRAMMABLE GAIN AMPLIFIER

The combination of a quad OP490 and the DAC8408 quad 8-bit CMOS DAC creates a quad programmable-gain amplifier with a quiescent supply drain of only 140  $\mu$ A. The digital code present at the DAC, which is easily set by a microprocessor,

determines the ratio between the fixed DAC feedback resistor and the resistance of the DAC ladder seen by the op amp feedback loop. The gain of each amplifier is:

$$\frac{V_{OUT}}{V_{IN}} = -\frac{256}{n}$$

where n equals the decimal equivalent of the 8-bit digital code present at the DAC. If the digital code present at the DAC consists of all zeros, the feedback loop opens causing the op amp output to saturate. The  $10~\rm M\Omega$  resistors placed in parallel with the DAC feedback loop eliminate this problem with a very small reduction in gain accuracy. The 2.5 V reference biases the amplifiers to the center of the linear region providing maximum output swing.

Figure 25. Single-Supply Micropower Quad Programmable Gain Amplifier

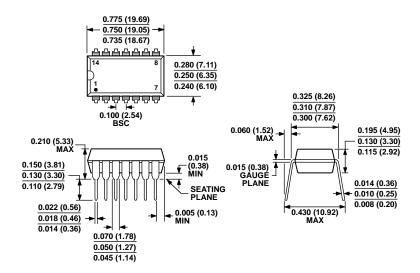

## **OUTLINE DIMENSIONS**

#### **COMPLIANT TO JEDEC STANDARDS MS-001**

CONTROLLING DIMENSIONS ARE IN INCHES; MILLIMETER DIMENSIONS (IN PARENTHESES) ARE ROUNDED-OFF INCH EQUIVALENTS FOR REFERENCE ONLY AND ARE NOT APPROPRIATE FOR USE IN DESIGN. CORNER LEADS MAY BE CONFIGURED AS WHOLE OR HALF LEADS.

Figure 26. 14-Lead Plastic Dual In-Line Package [PDIP]

Narrow Body

P-Suffix

(N-14)

Dimensions shown in inches and (millimeters)

10.50 (0.4134) 10.10 (0.3976) 8 8 8 8 8 8 7.60 (0.2992) 7.40 (0.2913) 10.65 (0.4193) 10.00 (0.3937) -⇒ -1.27 (0.0500) BSC 0.75 (0.0295) 0.25 (0.0098) 2.65 (0.1043) 2.35 (0.0925) 0.30 (0.0118) 0.10 (0.0039) COPLANARITY -►|-0.51 (0.0201) → <del>| </del> 1.27 (0.0500) SEATING 0.10 0.33 (0.0130) PLANE 0.31 (0.0122) 0.40 (0.0157) 0.20 (0.0079)

COMPLIANT TO JEDEC STANDARDS MS-013-AA

CONTROLLING DIMENSIONS ARE IN MILLIMETERS; INCH DIMENSIONS

(IN PARENTHESES) ARE ROUNDED-OFF MILLIMETER EQUIVALENTS FOR

REFERENCE ONLY AND ARE NOT APPROPRIATE FOR USE IN DESIGN.

Figure 27. 16-Lead Standard Small Outline Package [SOIC\_W] Wide Body S-Suffix (RW-16) Dimensions shown in millimeters and (inches)

Rev. E | Page 14 of 16

### **ORDERING GUIDE**

| Model <sup>1</sup> | Temperature Range | Package Description | Package Option   |

|--------------------|-------------------|---------------------|------------------|

| OP490GP            | −40°C to +85°C    | 14-Lead PDIP_N      | N-14 (P-Suffix)  |

| OP490GPZ           | −40°C to +85°C    | 14-Lead PDIP_N      | N-14 (P-Suffix)  |

| OP490GS            | −40°C to +85°C    | 16-Lead SOIC_W      | RW-16 (S-Suffix) |

| OP490GSZ           | −40°C to +85°C    | 16-Lead SOIC_W      | RW-16 (S-Suffix) |

| OP490GSZ-REEL      | −40°C to +85°C    | 16-Lead SOIC_W      | RW-16 (S-Suffix) |

$<sup>^{1}</sup>$  Z = RoHS Compliant Part.

NOTES