# **CY3682 Design Notes**

### Introduction

The SX2 USB interface works with any standard microprocessor or digital signal processor and adds USB 2.0 support for any peripheral design. The EZ-USB 3682 SX2 Development kit includes a Cypress FX 8051 processor and example firmware to master the SX2. This document describes the FX example firmware, fx2sx2. This firmware can be used as a starting point for development with the SX2 using another processor as external master.

This example firmware has the following sections: Initialization, Interrupt Service Routine, Read Register, Write Register, Write Descriptor, Data Loopback, and Endpoint 0. The firmware is written in the C language and structured so that most of it can be reused in any application.

The functions:

- low\_level\_command\_write

- low\_level\_command\_read

- low\_level\_fifo\_write

- low\_level\_fifo\_read

are specific to the FX processor. These functions generate the proper timing as described in the SX2 Datasheet for asynchronous command and FIFO reads and writes. These functions must be replaced by hardware specific routines for the particular external master used to control the SX2. It is up to the system designer to change or replace these functions with their own hardware specific functions which generate the proper timing as outlined in the SX2 datasheet.

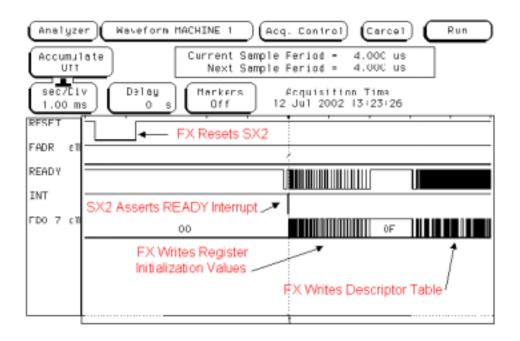

#### Initialization

This example creates four 512-byte double buffered endpoints. The FX uses an asynchronous interface and default SX2 polarities and it enables all the SX2 interrupts. A list of the registers and values used in this example is shown in *Table 1*. The external master can perform other tasks while waiting for the SX2 to initialize. For more details, consult the SX2 datasheet. The description of the initialization process follows.

After any hardware or FX processor initialization, the FX brings the SX2 out of reset by sending a signal using an FX general purpose I/O pin. Then the FX waits until the SX2 is ready to accept commands; the READY interrupt signals when the SX2 is ready.

Once the SX2 is ready, the FX turns on LED0 and writes all of the SX2 register values it needs to setup the SX2 for the application. Next, the FX writes its descriptor string to the SX2. Note: if the EEPROM initialization is used, then the READY interrupt is replaced by the ENUM\_OK interrupt, and the host processor can then write the SX2 registers.

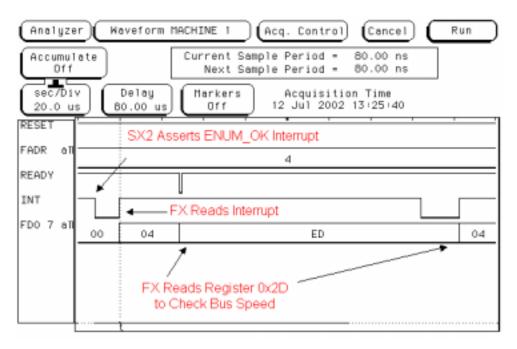

After the SX2 has its descriptor information, it connects and enumerates. The FX firmware waits for the ENUM\_OK interrupt then, after the FX receives the ENUM\_OK interrupt, it turns on LED1 on the FX PCB.

Once the SX2 completes enumeration, the external master must check and see whether the SX2 enumerated at High or Full speed. After the FX checks the HSGRANT bit, it adjusts the IN PACKET LENGTH so that the SX2 knows when to automatically send packets to the USB host. The FX will turn on LED2 if the SX2 enumerated at High speed.

The last initialization task is for the FX to flush all of the SX2 FIFOs.

The initialization process is shown in *Figure 1* and *Figure 2*.

August 1, 2002

#### Initialization Code

```

1

OUTA = 0;

//Reset the SX2 with a FX GPIO

2

EZUSB_Delay(1);

//Wait a minimum of 200 microseconds

3

OUTA = 1;

//Bring the SX2 out of reset

4

EZUSB Delay(1);

//Wait until SX2 is going

5

б

//This code is for self powered devices which do not use the EEPROM to enumerate

7

#ifndef BUSPOWER

8

9

while (!sx2_ready);

//Wait until SX2 gives us a ready interrupt

10

11

ledX_rdvar = LED0_ON;

//Light LED0 to indicate SX2 is ready

12

13

for (i = 0; i < sizeof(regs); i++)

//Setup SX2 with all default values

14

{

15

WriteRegister (regs[i], regsvalue[i]);

16

}

```

```

17

WriteDescriptor();

18

//Load entire descriptor into SX2

19

20

#endif

21

22

while (!enum_ok);

//Wait until the SX2 has enumerated

23

24

ledX_rdvar = LED1_ON;

//Light LED1 to indicate that we're enumerated

25

26

if (!(ReadRegister (0x2D) & 0x80)) //Check if we have not enumerated at Highspeed

27

{

28

WriteRegister (0x0A, 0x20);

//Set IN packet length to 64

29

WriteRegister (0x0B, 0x40);

WriteRegister (0x0C, 0x20);

30

//Set IN packet length to 64

WriteRegister (0x0D, 0x40);

31

32

WriteRegister (0x0E, 0x20);

//Set IN packet length to 64

33

WriteRegister (0x0F, 0x40);

WriteRegister (0x10, 0x20);

//Set IN packet length to 64

34

35

WriteRegister (0x11, 0x40);

ledX_rdvar = LED2_OFF;

36

//Dim LED2 to indicate full speed

37

}

38

else

39

{

40

ledX_rdvar = LED2_ON;

//Light LED2 to indicate high speed

41

}

42

43

WriteRegister (0x20, 0xF0);

44

//Flush the FIFOs to start

```

|        | i          |       |

|--------|------------|-------|

| Number | Register   | Value |

| 0x01   | IFCONFIG   | 0xC8  |

| 0x02   | FLAGSAB    | 0x00  |

| 0x03   | FLAGSCD    | 0x00  |

| 0x04   | POLAR      | 0x00  |

| 0x06   | EP2CFG     | 0xA2  |

| 0x07   | EP4CFG     | 0xA0  |

| 0x08   | EP6CFG     | 0xE2  |

| 0x09   | EP8CFG     | 0xE0  |

| 0x0A   | EP2PKTLENH | 0x02  |

| 0x0B   | EP2PKTLENL | 0x00  |

| 0x0C   | EP4PKTLENH | 0x02  |

| 0x0D   | EP4PKTLENL | 0x00  |

| 0x0E   | EP6PKTLENH | 0x22  |

| 0x0F   | EP6PKTLENL | 0x00  |

| 0x10   | EP8PKTLENH | 0x22  |

|        |            |       |

| Number | Register     | Value |

|--------|--------------|-------|

| 0x11   | EP8PKTLENL   | 0x00  |

| 0x12   | EP2PFH       | 0x81  |

| 0x13   | EP2PFL       | 0x00  |

| 0x14   | EP4PFH       | 0x81  |

| 0x15   | EP4PFL       | 0x00  |

| 0x16   | EP6PFH       | 0x81  |

| 0x17   | EP6PFL       | 0x00  |

| 0x18   | EP8PFH       | 0x81  |

| 0x19   | EP8PFL       | 0x00  |

| 0x1A   | EP2ISOINPKTS | 0x01  |

| 0x1B   | EP4ISOINPKTS | 0x01  |

| 0x1C   | EP6ISOINPKTS | 0x01  |

| 0x1D   | EP8ISOINPKTS | 0x01  |

| 0x2E   | INTENABLE    | 0xFF  |

Table 1.Initial Register Values From Header File

Figure 1. SX2 Initialization From Reset to Descriptor

Figure 2. SX2 Initialization Continued

#### **WriteRegister**

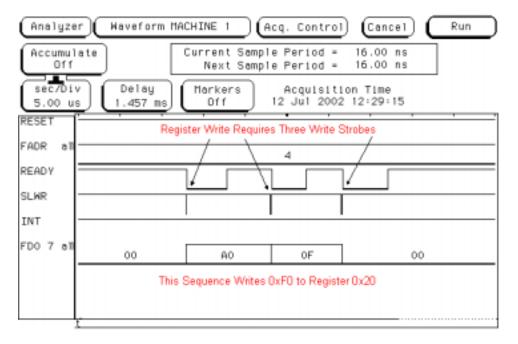

The WriteRegister function calls the hardware specific function low\_level\_command\_write. The first byte write is the 6-bit address of the register, with the most significant bit set and the next MSB cleared. The next write is the upper nibble of the data, with the four most significant bits cleared. The last write is the lower nibble of the data, with the four most significant bits cleared. The complete Write Register Function Sequence is shown in *Figure 3*.

### WriteRegister Code

```

45 void WriteRegister (BYTE r, BYTE d) //r = register number, d = data to be written

46 {

47 low_level_command_write (0x04, (r | 0x80)); //Write request, bit7 = 1, bit6 = 0

48 low_level_command_write (0x04, (d & 0xF0) >> 4); //Write data high nibble

49 low_level_command_write (0x04, (d & 0x0F)); //Write data low nibble

50 }

```

Figure 3. Write Register Sequence

#### ReadRegister

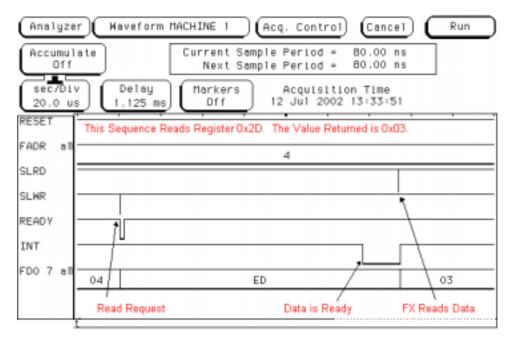

The ReadRegister function calls the hardware specific function low\_level\_command\_write and low\_level\_command \_read. The first write is the address of the register, with the two most significant bits set. The FX waits until it receives an interrupt from the SX2 indicating that the data is ready. The FX then performs a hardware specific read and returns the data. The complete Read Register Sequence is shown in *Figure 4*.

# ReadRegister Code

```

51 BYTE ReadRegister (BYTE r)

//r = register number

52

{

53

BYTE d;

//d holds read data

read interrupt = TRUE;

54

low_level_command_write (0x04, (r | 0x80 | 0x40));

//Read request, bit7 = 1, bit6 = 1

55

56

while (read_interrupt)

//Wait until SX2 has data

57

;

58

d = low_level_command_read (0x04);

//Read Data

59

return (d);

60 }

```

Figure 4. Read Register Sequence

#### **Interrupt Service Routine**

The Interrupt Service Routine distinguishes between the two types of interrupts (requested data ready or asynchronous interrupt) by examining the read\_interrupt flag. If the ISR finds read\_interrupt to be true, it clears the interrupt and does no further processing. This indicates to the ReadRegister function that the data is available to read.

If read\_interrupt is FALSE, then this interrupt is an asynchronous interrupt that needs to be parsed. Depending on the source of the interrupt, some flags are set or toggled to tell the main loop what is happening.

The INTERRUPT pin on the SX2 is connected to a hardware interrupt source on the FX so that all SX2 interrupts are immediately serviced by the FX. Data may be immediately processed in the interrupt service routine or may be stored for background processing by the main loop.

Every time the INTERRUPT signal is asserted by the SX2, data is ready to be read, and the FX calls the low\_level\_command\_read function. This is true whether it is requested data or an interrupt source.

# ISR Code

```

61 void int0_isr (void) interrupt 0

62

{

63

BYTE i;

64

65

if (read_interrupt)

//If we are expecting data

66

{

67

read_interrupt = FALSE;

//Clear flag

68

return;

//Don't go any further

69

}

70

71

i = low_level_command_read (0x04);

72

switch (i)

73

{

74

case 0x01:

//Ready

75

sx2_ready = TRUE;

76

break;

77

//Bus Activity

case 0x02:

78

no_activity = !no_activity;

79

break;

```

```

80

case 0x04:

//Enumeration complete

81

enum_ok = TRUE;

82

break;

83

case 0x20:

//Flags

84

got_out_data = TRUE;

85

break;

86

case 0x40:

//EP0Buf

87

ep0buf_ready = TRUE;

88

break;

89

case 0x80:

//Setup

90

got_setup = TRUE;

91

break;

92

}

93

}

```

# WriteDescriptor

The WriteDescriptor function uses the hardware specific function low\_level\_command\_write to write the descriptor data to the SX2's 500 bytes of descriptor RAM. To load the descriptor, the WriteDescriptor function does the following:

- Initiate a Command Address Transfer to register 0x30. This Command Address Transfer must conform to the Command Protocol specified in the SX2 Data Sheet–bit seven of the byte set to one, bit six set to zero, and the remaining bits zero through five indicating the address of the descriptor register (i.e., 0x30).

- 2. Perform four Command Data Transfers representing the LSB and MSB of the word value that defines the length of the entire descriptor about to be transferred. These Command Data Transfers and all other data transfers must conform to the Command Protocol-bit seven of each byte set to zero, bits four through six are don't cares, and bits zero through three are the lower or upper nibble of the byte being transferred.

- Write the descriptor one byte at a time (perform two Command Data Transfers at a time), until complete.

Note: the Command Address Transfer is only performed once.

# WriteDescriptor Code

```

94 void WriteDescriptor (void)

95

{

96

WORD len, i;

97

98

len = sizeof(descriptor);

99

100

low_level_command_write (0x04, (0x30 | 0x80));

//Write request, bit7 = 1, bit6 = 0

low_level_command_write (0x04, (len & 0x00F0) >> 4); //Write length high nibble of lsb

101

//Write length low nibble of lsb

102

low_level_command_write (0x04, (len & 0x000F));

103

low_level_command_write (0x04, (len & 0xF000) >> 12);//Write length high nibble of msb

104

low_level_command_write (0x04, (len & 0x0F00) >> 8); //Write length low nibble of msb

105

for (i = 0; i < len; i++)</pre>

106

{

107

low_level_command_write (0x04, (descriptor[i] & 0xF0) >> 4);//Write data high nibble

low_level_command_write (0x04, (descriptor[i] & 0x0F));

108

//Write data low nibble

109

}

110 }

```

# **Endpoint 0**

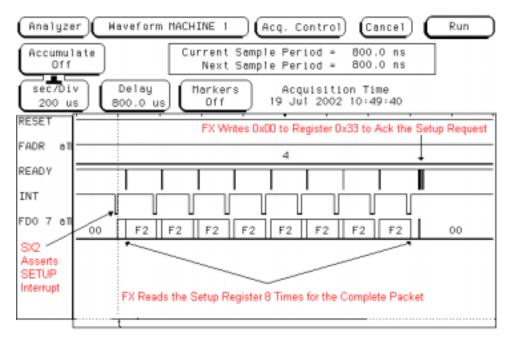

This section of code demonstrates how to handle endpoint 0 USB traffic. If the SX2 receives a setup request that it cannot handle automatically, it fires a SETUP interrupt. The FX ISR sets the got\_setup flag when it sees a setup interrupt. This flag is checked in the main loop. For more information on SETUP requests, consult the USB Specification.

After reading a SETUP interrupt, the FX clears the flag and reads the eight bytes of setup data. For more information on the format of the setup data, consult the USB specification.

After receiving the setup data, the FX determines the direction, length, and type of request--standard, class, vendor, or unknown. Not all applications use every request type. This example acknowledges the vendor request 0xAA if it is a zero-length request. This vendor request could be used by the host application to indicate application specific status and is illustrated in *Figure 5*.

The example also responds to the vendor request 0xAB. This command can have a data stage. If the size is less than 64 bytes, the FX example loops back the data it receives.

The example also uses vendor requests 0xB6 and 0xB8 to signify a short packet, as described in the Data Loopback section.

All other requests are stalled. To stall a request, the external master initiates a write request for the SETUP register, 0x32, and writes any non-zero value to the register.

to the ep0buffer, then writes the byte count to the bytecount register. If it's an OUT request, the FX firmware reads the

bytecount register to determine how much data to read, then

reads the ep0buffer. This example only handles a maximum

transfer of 64 bytes, but could be repeated for larger trans-

fers. The SETUP and EP0 interrupts are illustrated in Figure

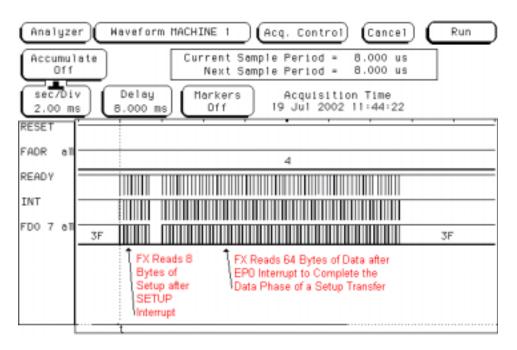

To complete endpoint zero data transfers, the ep0buf\_ready flag is used. If the SX2 receives a setup request with a non-zero length, it fires the EP0BUF interrupt. For an IN request, this interrupt indicates that the EP0 buffer is available to be written to. For an OUT request, this interrupt indicates that a packet was transferred from the host to the SX2.

The FX firmware first clears the ep0buf\_ready flag that was set in the ISR. If it's an IN request, the FX firmware writes data

# Setup Code

```

111 if (got_setup)

//Received setup interrupt

112 {

113

got_setup = FALSE;

//Clear flag

114

for (i = 0; i < 8; i++)

115

{

116

setup[i] = ReadRegister(0x32);

//Read setup data

117

}

setupdirection = setup[0] & 0x80;

//Find direction, In = 1, Out = 0

118

119

setuplength = setup[6];

//Get length of setup

120

setuplength |= setup[7] << 8;</pre>

121

if ((setup[0] & 0x60) == 0)

//This is a standard request

122

{

123

//******TODO: Handle or keep track of any standard requests

124

switch (setup[1])

125

{

126

case 0x01:

// *** Clear Feature

127

switch(setup[0])

128

{

case 0x02:

129

// End Point

130

if(setup[2] == 0)

131

{

132

switch(setup[4] & 0x7F)

133

{

134

case 2:

135

WriteRegister (0x06, 0xA2);

//Clear stall bit in EPxCFG

136

137

WriteRegister (0x33, 0);

138

//Ack this request

139

break;

case 4:

140

141

WriteRegister (0x07, 0xA0);

142

//Clear stall bit in EPxCFG

143

WriteRegister (0x33, 0);

144

//Ack this request

145

break;

146

case 6:

147

WriteRegister (0x08, 0xE2);

//Clear stall bit in EPxCFG

148

149

WriteRegister (0x33, 0);

150

//Ack this request

151

break;

152

case 8:

153

WriteRegister (0x09, 0xE0);

//Clear stall bit in EPxCFG

154

155

WriteRegister (0x33, 0);

156

//Ack this request

157

break;

158

default:

WriteRegister (0x32, 0xFF);

159

//Stall the request

160

161

}

}

162

```

6.

```

163

else

164

WriteRegister (0x32, 0xFF); //Stall the request

165

break;

166

}

167

break;

168

case 0x03:

// *** Set Feature

169

switch(setup[0])

170

{

case 0x02:

171

// End Point

if(setup[2] == 0)

172

173

{

174

switch(setup[4] & 0x7F)

175

{

176

case 2:

177

WriteRegister (0x06, 0xA6);

178

//Set stall bit in EPxCFG

179

WriteRegister (0x33, 0);

180

//Ack this request

181

break;

182

case 4:

183

WriteRegister (0x07, 0xA4);

184

//Set stall bit in EPxCFG

185

WriteRegister (0x33, 0);

186

//Ack this request

187

break;

188

case 6:

WriteRegister (0x08, 0xE6);

189

//Set stall bit in EPxCFG

190

191

WriteRegister (0x33, 0);

192

//Ack this request

193

break;

194

case 8:

195

WriteRegister (0x09, 0xE4);

196

//Set stall bit in EPxCFG

WriteRegister (0x33, 0);

197

198

//Ack this request

199

break;

200

default:

WriteRegister (0x32, 0xFF);

201

202

//Stall the request

}

203

204

}

205

else

WriteRegister (0x32, 0xFF); //Stall the request

206

207

break;

208

}

209

break;

210

}

211

}

else if ((setup[0] & 0x60) == 0x20)

212

//This is a class request

213

{

//******TODO: Handle or keep track of any class requests

214

215

}

216

else if ((setup[0] & 0x60) == 0x40)

//This is a vendor request

217

{

switch (setup[1])

218

219

{

220

//********TODO: Add specific cases that you handle

221

case 0xAA:

//We handle this vendor command if zero length

222

if (!setuplength)

223

WriteRegister (0x33, 0);

//Ack this request

224

else

225

WriteRegister (0x32, 0xFF); //Stall the request

226

break;

```

| 227     |           | case 0xAB:                                                                    |

|---------|-----------|-------------------------------------------------------------------------------|

| 228     |           | if (setuplength > 64) //We want to handle vendor 0xAB                         |

| 229     |           | WriteRegister (0x32, 0xFF); //But only if less than 64                        |

| 230     |           | else                                                                          |

| 231     |           | {                                                                             |

| 232     |           | while (!ep0buf_ready); //Wait for buffer to become available                  |

| 233     |           | epObuf_ready = FALSE; //Clear the flag                                        |

| 234     |           | //This example loops back any data that we receive with a 0xAB vendor request |

| 235     |           | //Note: this example only handles 64 bytes                                    |

| 236     |           | if (setupdirection) //In request                                              |

| 237     |           | {                                                                             |

| 238     |           | for ( $i = 0; i < setuplength; i++$ )                                         |

| 239     |           | {                                                                             |

| 240     |           | <pre>WriteRegister( 0x31, setupdata[i] );</pre>                               |

| 241     |           | //Write data to buffer                                                        |

| 242     |           | }                                                                             |

| 243     |           | WriteRegister (0x33, len); //Write bytecount                                  |

| 244     |           | //Note: This routine can be modified for multiple packets of 64               |

| 245     |           | }                                                                             |

| 246     |           | else //Out request                                                            |

| 247     |           | {                                                                             |

| 248     |           | <pre>len = ReadRegister (0x33); //Read the bytecount</pre>                    |

| 249     |           | for $(i = 0; i < len; i++)$                                                   |

| 250     |           | {                                                                             |

| 251     |           | <pre>setupdata[i] = ReadRegister (0x31);</pre>                                |

| 252     |           | }                                                                             |

| 253     |           | //Note: This routine can be modified for multiple packets of 64               |

| 254     |           | }                                                                             |

| 255     |           | }                                                                             |

| 256     |           | break;                                                                        |

| 257     |           | case 0xB6:                                                                    |

| 258     |           | ep6shortpacket = TRUE;                                                        |

| 259     |           | /Set a flag so that the main loop commits what data it has                    |

| 260     |           | WriteRegister (0x33, 0); //Ack this request                                   |

| 261     |           | break;                                                                        |

| 262     |           | case 0xB8:                                                                    |

| 263     |           | ep8shortpacket = TRUE;                                                        |

| 264     |           | //Set a flag so that the main loop commits what data it has                   |

| 265     |           | WriteRegister (0x33, 0); //Ack this request                                   |

| 266     |           | break;                                                                        |

| 267     |           | default: //We don't recognize the request                                     |

| 268     |           | WriteRegister (0x32, 0xFF); //Stall the request                               |

| 269     |           | break;                                                                        |

| 270     |           | }                                                                             |

| 270     | }         | ,                                                                             |

| 272     | ,<br>else | //Reserved or undefined request                                               |

| 272     | 0100      | WriteRegister (0x32, 0xFF); //Stall the request                               |

| 274 }   |           | Allocations, and, and, and a second second request                            |

| , r , r |           |                                                                               |

Figure 5. Setup Interrupt and Ack

Figure 6. Setup and EP0 Interrupts and Data

#### **Data Loopback**

If there is bus activity, then the FX firmware checks to see if the SX2 asserted the FLAGS interrupt. This indicates that the host sent data to one of the OUT endpoints, EP2 or EP4. If there is OUT data available, the FX firmware reads the EP24FLAGS register. This register checks the empty status of EP2 and EP4. If one of the endpoints contains data, the FX firmware reads data out of the endpoint, one byte at a time, and subsequently writes the bytes into one of the endpoints used for USB IN data. EP2 data is looped into EP6, and EP4 data is looped into EP8. The FX firmware continues to read and write data until the endpoint becomes empty.

This is a very simple data loopback example and can be exercised using the EZ-USB Control Panel PC program. Bulk Transfers of data can be sent OUT on EP2 or EP4 and then requested IN on EP6 or EP8.

The FX firmware also has an example of how to send an IN data packet which is less than the configured IN packet size. To do this, use the vendor request 0xB6 or 0xB8 which will write to the INPKTEND register, thereby committing any data already in EP6 or EP8 to the USB, regardless of the configured IN packet size.

This can also be exercised using the EZ-USB Control Panel program. First, send a small amount of data to EP2 (e.g., 30 bytes). Then, request a larger amount of data from EP6 (e.g., 64 bytes). The SX2 will not send the 30 bytes because the

configured IN packet size has not been received. To send the 30 bytes, use the Control Panel to send the vendor request 0xB6 to the SX2. The FX firmware will see this request and commit the short packet.

The FX firmware checks the no\_activity flag in its main loop. This flag is toggled in the ISR. If TRUE, the device has either been unplugged (self-powered), or suspended (bus-powered). If the device is bus-powered, then the FX firmware should put the SX2, then the FX into a low-power mode. Another BUSACTIVITY interrupt will wake up the FX. If the device supports remote wakeup, then the FX can wakeup the SX2 through a general purpose I/O pin instead of waiting for the host to resume.

#### Data Loopback Code

| 275 |                                                                              | (If we are not augmended or upplugged       |  |

|-----|------------------------------------------------------------------------------|---------------------------------------------|--|

| 275 | if (!no_activity) /,                                                         | /If we are not suspended or unplugged       |  |

| 277 | l                                                                            |                                             |  |

| 278 | <pre>ledX_rdvar = LED3_ON; if (ret out data)</pre>                           | /The FLAGS int tells us we have out data    |  |

| 278 |                                                                              | The FLAGS int terrs us we have out data     |  |

| 280 | {<br>got_out_data = FALSE;                                                   |                                             |  |

| 281 | temp = ReadRegister (0x1E); /,                                               | (Pood ED24 Elogg Pogistor                   |  |

| 282 | if (!(temp & 0x02))                                                          |                                             |  |

| 282 | 11 (:(temp & 0x0z)) /,                                                       | II EP2 IS NOT Empty (Has data)              |  |

| 284 | do                                                                           |                                             |  |

| 285 | {                                                                            |                                             |  |

| 285 |                                                                              | ta_read (0x00, &dataloopback))              |  |

| 287 |                                                                              | ta to read from FIFO2                       |  |

| 288 |                                                                              | .ow_level_data_write (0x02, dataloopback)); |  |

| 289 |                                                                              | _                                           |  |

| 289 | -                                                                            | back into FIFO6                             |  |

| 290 | l temp = ReadRegis                                                           | ster (0x1E); //Read EP24 Flags Register     |  |

| 292 | <pre> while (!(temp &amp; 0x02));</pre>                                      |                                             |  |

| 292 |                                                                              | of EP2 until it is empty                    |  |

| 293 | }                                                                            | OI EPZ UNCII IC IS EMPLY                    |  |

| 294 | if (!(temp & 0x20)) //                                                       | (If ED4 is NOT ompty (bas data)             |  |

| 295 |                                                                              | II EPA IS NOT Empty (has data)              |  |

| 297 | {<br>do                                                                      |                                             |  |

| 298 | {                                                                            |                                             |  |

| 299 |                                                                              | ta_read (0x01, &dataloopback))              |  |

| 300 |                                                                              | ta to read from FIF04                       |  |

| 301 |                                                                              | .ow_level_data_write (0x03, dataloopback)); |  |

| 302 |                                                                              | back into FIF08                             |  |

| 303 | -                                                                            | ster (0x1E); //Read EP24 Flags Register     |  |

| 304 | }                                                                            | beer (onil), ,, nead brar ridgs negister    |  |

| 305 | while (!(temp & 0x20));                                                      |                                             |  |

| 306 |                                                                              | of EP4 until it is empty                    |  |

| 307 | }                                                                            |                                             |  |

| 308 | }                                                                            |                                             |  |

| 309 | if (ep6shortpacket)                                                          |                                             |  |

| 310 | //Sometimes we need to send an amount o                                      | of data < the autoinlength                  |  |

| 311 | {                                                                            |                                             |  |

| 312 | ep6shortpacket = FALSE;                                                      |                                             |  |

| 313 | WriteRegister (0x20, 0x06);                                                  |                                             |  |

| 314 | //Write EP6 packet end bit to INPKTEND register                              |                                             |  |

| 315 | //Alternatively, the FX hardware could strobe the INPKTEND pin after setting |                                             |  |

| 316 | //the address pins to endpoint (                                             |                                             |  |

| 317 | }                                                                            |                                             |  |

|     | ·                                                                            |                                             |  |

```

Revision : August 1, 2002

```

```

318

if (ep8shortpacket)

319

//Sometimes we need to send an amount of data < the autoinlength

320

{

321

ep8shortpacket = FALSE;

322

WriteRegister (0x20, 0x08);

323

//Write EP8 packet end bit to INPKTEND register

324

//Alternatively, the FX hardware could strobe the INPKTEND pin after setting

325

// the address pins to endpoint 8

}

326

327

}

328

else

//If we are bus powered, then power down the SX2 and ourselves

329

{

330

ledX_rdvar = LED3_OFF;

331 //

temp = ReadRegister (0x01);

//Read the IFCONFIG register

WriteRegister (0x01, temp | 0x04);

//Set the SX2 standby bit

332 //

333 //

while (no_activity)

334 //

{

335 //

sleep();

//Stay asleep until the host resumes us

336 //

}

337

//********If the device supports remote wake-up, then it can

//wake up the SX2 instead of waiting for resume

338

339

}

```

# Conclusion

The SX2 is a powerful, intelligent peripheral chip that is easy to use and fits in a number of applications. This example shows standard initialization and data handling for a typical SX2 application. Most of the non-hardware-specific C code can be reused in other SX2 projects, making this example an excellent starting point for SX2 development.

© Cypress Semiconductor Corporation, 2002. The information contained herein is subject to change without notice. Cypress Semiconductor Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in a Cypress Semiconductor product. Nor does it convey or imply any license under patent or other rights. Cypress Semiconductor product nor does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress Semiconductor products in life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress Semiconductor against all charges.