# **Precision RRIO Dual Operational Amplifier**

Enhanced Product OP284-EP

#### **FEATURES**

Single-supply operation Wide bandwidth: 4.25 MHz Low offset voltage: 100 µV

Unity-gain stable High slew rate: 4.0 V/µs Low noise: 3.9 nV/√Hz

#### **ENHANCED PRODUCT FEATURES**

Supports defense and aerospace applications (AQEC standard)

Military temperature range (-55°C to +125°C)

Controlled manufacturing baseline

1 assembly/test site

1 fabrication site

Enhanced product change notification

Qualification data available on request

#### **APPLICATIONS**

Battery-powered instrumentation Power supply control and protection Telecommunications DAC output amplifier ADC input buffer

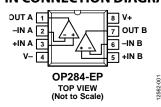

### PIN CONNECTION DIAGRAM

Figure 1.

### **GENERAL DESCRIPTION**

The OP284-EP is a dual, single-supply, 4.25 MHz bandwidth amplifier featuring rail-to-rail inputs and outputs (RRIO).

The OP284-EP is guaranteed to operate from 5 V to 36 V (or  $\pm 2.5$  V to  $\pm 18$  V).

This amplifier is superb for single-supply applications requiring both ac and precision dc performance. The combination of wide bandwidth, low noise, and precision makes the OP284-EP useful in a wide variety of applications, including filters and instrumentation.

Other applications for this amplifier include portable telecommunications equipment, power supply control and protection,

and use as an amplifier or buffer for transducers with wide output ranges. Sensors requiring a rail-to-rail input amplifier include Hall effect, piezoelectric, and resistive transducers.

The ability to swing rail to rail at both the input and output enables designers to build multistage filters in single-supply systems and to maintain high signal-to-noise ratios.

The OP284-EP is specified over the extended industrial temperature range of -55°C to +125°C. The OP284-EP is available in a SOIC surface-mount package.

Rev. 0

**Document Feedback**

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 ©2015 Analog Devices, Inc. All rights reserved.

Technical Support www.analog.com

## **TABLE OF CONTENTS**

| Features                   | 1 |

|----------------------------|---|

| Enhanced Product Features  | 1 |

| Applications               | 1 |

| Pin Configuration          | 1 |

| General Description        | 1 |

| Revision History           | 2 |

| Specifications             | 3 |

| Electrical Characteristics | 3 |

| Absolute Maximum Ratings            |    |

|-------------------------------------|----|

| Thermal Resistance                  |    |

| ESD Caution                         |    |

| Typical Performance Characteristics |    |

| Outline Dimensions                  |    |

| Ordering Guide                      | 13 |

### **REVISION HISTORY**

5/15—Revision 0: Initial Version

## **SPECIFICATIONS**

### **ELECTRICAL CHARACTERISTICS**

$V_S = 5.0 \text{ V}$ ,  $V_{CM} = 2.5 \text{ V}$ ,  $T_A = 25 ^{\circ}\text{C}$ , unless otherwise noted.

Table 1.

| Parameter                   | Symbol                   | Test Conditions/Comments                                                                           | Min  | Тур  | Max  | Unit    |

|-----------------------------|--------------------------|----------------------------------------------------------------------------------------------------|------|------|------|---------|

| INPUT CHARACTERISTICS       |                          |                                                                                                    |      |      |      |         |

| Offset Voltage              | V <sub>os</sub>          |                                                                                                    |      |      | 125  | μV      |

|                             |                          | -55°C ≤ T <sub>A</sub> ≤ +125°C                                                                    |      |      | 250  | μV      |

| Input Bias Current          | I <sub>B</sub>           |                                                                                                    |      | 60   | 450  | nA      |

|                             |                          | -55°C ≤ T <sub>A</sub> ≤ +125°C                                                                    |      |      | 600  | nA      |

| Input Offset Current        | I <sub>os</sub>          |                                                                                                    |      |      |      |         |

|                             |                          | $-55^{\circ}\text{C} \le \text{T}_{A} \le +125^{\circ}\text{C}$                                    |      |      | 50   | nA      |

| Input Voltage Range         |                          |                                                                                                    | 0    |      | 5    | V       |

| Common-Mode Rejection Ratio | CMRR                     | $V_{CM} = 1.0 \text{ V to } 4.0 \text{ V}, -55^{\circ}\text{C} \le T_{A} \le +125^{\circ}\text{C}$ | 86   |      |      | dB      |

| Large Signal Voltage Gain   | $A_{VO}$                 | $R_L = 2 \text{ k}\Omega$ , $1 \text{ V} \le V_{OUT} \le 4 \text{ V}$                              | 50   | 240  |      | V/mV    |

|                             |                          | $R_L = 2 \text{ k}\Omega, -55^{\circ}\text{C} \le T_A \le +125^{\circ}\text{C}$                    | 25   |      |      | V/mV    |

| Offset Voltage Drift        | $\Delta V_{OS}/\Delta T$ |                                                                                                    |      | 0.2  | 2.00 | μV/°C   |

| Bias Current Drift          | $\Delta I_B/\Delta T$    |                                                                                                    |      | 150  |      | pA/°C   |

| OUTPUT CHARACTERISTICS      |                          |                                                                                                    |      |      |      |         |

| Output Voltage High         | $V_{OH}$                 | $I_{L} = 1.0 \text{ mA}$                                                                           | 4.80 |      |      | V       |

| Output Voltage Low          | $V_{OL}$                 | $I_{L} = 1.0 \text{ mA}$                                                                           |      |      | 125  | mV      |

| Output Current              | I <sub>OUT</sub>         |                                                                                                    | ±6.5 |      |      | mA      |

| POWER SUPPLY                |                          |                                                                                                    |      |      |      |         |

| Supply Current/Amplifier    | I <sub>SY</sub>          | $V_{OUT} = 2.5 \text{ V}, -55^{\circ}\text{C} \le T_{A} \le +125^{\circ}\text{C}$                  |      |      | 1.45 | mA      |

| DYNAMIC PERFORMANCE         |                          |                                                                                                    |      |      |      |         |

| Slew Rate                   | SR                       | $R_L = 2 k\Omega$                                                                                  | 1.65 | 2.4  |      | V/µs    |

| Settling Time               | t <sub>s</sub>           | To 0.01%, 1.0 V step                                                                               |      | 2.5  |      | μs      |

| Gain Bandwidth Product      | GBP                      |                                                                                                    |      | 3.25 |      | MHz     |

| Phase Margin                | $\Phi_{M}$               |                                                                                                    |      | 45   |      | Degrees |

| NOISE PERFORMANCE           |                          |                                                                                                    |      |      |      |         |

| Voltage Noise               | e <sub>n</sub> p-p       | 0.1 Hz to 10 Hz                                                                                    |      | 0.3  |      | μV p-p  |

| Voltage Noise Density       | e <sub>n</sub>           | f = 1 kHz                                                                                          |      | 3.9  |      | nV/√Hz  |

| Current Noise Density       | i <sub>n</sub>           |                                                                                                    |      | 0.4  |      | pA/√Hz  |

$V_{\text{S}}$  = ±15.0 V,  $V_{\text{CM}}$  = 0 V,  $T_{\text{A}}$  = 25°C, unless otherwise noted.

Table 2.

| Parameter                    | Symbol                   | Test Conditions/Comments                                                                               | Min  | Тур  | Max     | Unit    |

|------------------------------|--------------------------|--------------------------------------------------------------------------------------------------------|------|------|---------|---------|

| INPUT CHARACTERISTICS        |                          |                                                                                                        |      |      |         |         |

| Offset Voltage               | Vos                      |                                                                                                        |      |      | 100     | μV      |

|                              |                          | $-55^{\circ}\text{C} \le \text{T}_{\text{A}} \le +125^{\circ}\text{C}$                                 |      |      | 200     | μV      |

| Input Bias Current           | I <sub>B</sub>           |                                                                                                        |      | 80   | 450     | nA      |

|                              |                          | $-55^{\circ}\text{C} \le \text{T}_{\text{A}} \le +125^{\circ}\text{C}$                                 |      |      | 600     | nA      |

| Input Offset Current         | I <sub>OS</sub>          | $-55^{\circ}\text{C} \le \text{T}_{\text{A}} \le +125^{\circ}\text{C}$                                 |      |      | 50      | nA      |

| Input Voltage Range          |                          |                                                                                                        | -15  |      | +15     | V       |

| Common-Mode Rejection Ratio  | CMRR                     | $V_{CM} = -14.0 \text{ V to } +14.0 \text{ V}, -55^{\circ}\text{C} \le T_{A} \le +125^{\circ}\text{C}$ | 86   | 90   |         | dB      |

| Large Signal Voltage Gain    | $A_{VO}$                 | $R_L = 2 k\Omega, -10 V \le V_{OUT} \le 10 V$                                                          | 150  | 1000 |         | V/mV    |

|                              |                          | $R_L = 2 \text{ k}\Omega, -55^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$                  | 75   |      |         | V/mV    |

| Offset Voltage Drift         | $\Delta V_{OS}/\Delta T$ |                                                                                                        |      | 0.2  | 2.00    | μV/°C   |

| Bias Current Drift           | $\Delta V_B/\Delta T$    |                                                                                                        |      | 150  |         | pA/°C   |

| OUTPUT CHARACTERISTICS       |                          |                                                                                                        |      |      |         |         |

| Output Voltage High          | V <sub>OH</sub>          | $I_{L} = 1.0 \text{ mA}$                                                                               | 14.8 |      |         | V       |

| Output Voltage Low           | V <sub>OL</sub>          | $I_{L} = 1.0 \text{ mA}$                                                                               |      |      | -14.875 | V       |

| Output Current               | I <sub>OUT</sub>         |                                                                                                        | ±10  |      |         | mA      |

| POWER SUPPLY                 |                          |                                                                                                        |      |      |         |         |

| Power Supply Rejection Ratio | PSRR                     | $V_S = \pm 2.0 \text{ V to } \pm 18 \text{ V}, -55^{\circ}\text{C} \le T_A \le +125^{\circ}\text{C}$   | 90   |      |         | dB      |

| Supply Current/Amplifier     | I <sub>SY</sub>          | $V_{OUT} = 0 \text{ V}, -55^{\circ}\text{C} \le T_{A} \le +125^{\circ}\text{C}$                        |      |      | 2.0     | mA      |

|                              |                          | $V_S = \pm 18 \text{ V}, -55^{\circ}\text{C} \le T_A \le +125^{\circ}\text{C}$                         |      |      | 2.25    | mA      |

| DYNAMIC PERFORMANCE          |                          |                                                                                                        |      |      |         |         |

| Slew Rate                    | SR                       | $R_L = 2 k\Omega$                                                                                      | 2.4  | 4.0  |         | V/µs    |

| Full Power Bandwidth         | $BW_p$                   | 1% distortion, $R_L = 2 \text{ k}\Omega$ , $V_{OUT} = 29 \text{ V p-p}$                                |      | 35   |         | kHz     |

| Settling Time                | t <sub>s</sub>           | To 0.01%, 10 V step                                                                                    |      | 4    |         | μs      |

| Gain Bandwidth Product       | GBP                      |                                                                                                        |      | 4.25 |         | MHz     |

| Phase Margin                 | $\Phi_{M}$               |                                                                                                        |      | 50   |         | Degrees |

| NOISE PERFORMANCE            |                          |                                                                                                        |      |      |         |         |

| Voltage Noise                | e <sub>n</sub> p-p       | 0.1 Hz to 10 Hz                                                                                        |      | 0.3  |         | μV p-p  |

| Voltage Noise Density        | e <sub>n</sub>           | f = 1 kHz                                                                                              |      | 3.9  |         | nV/√Hz  |

| Current Noise Density        | i <sub>n</sub>           |                                                                                                        |      | 0.4  |         | pA/√Hz  |

### **ABSOLUTE MAXIMUM RATINGS**

Table 3.

| Parameter                               | Rating          |

|-----------------------------------------|-----------------|

| Supply Voltage                          | ±18 V           |

| Input Voltage                           | ±18 V           |

| Differential Input Voltage <sup>1</sup> | ±0.6 V          |

| Output Short-Circuit Duration to GND    | Indefinite      |

| Storage Temperature Range               | −65°C to +150°C |

| Operating Temperature Range             | −55°C to +125°C |

| Junction Temperature Range              | −65°C to +150°C |

| Lead Temperature (Soldering 60 sec)     | 300°C           |

<sup>&</sup>lt;sup>1</sup> For input voltages greater than 0.6 V, the input current must be limited to less than 5 mA to prevent degradation or destruction of the input devices.

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

### THERMAL RESISTANCE

$\theta_{JA}$  is specified for the worst-case conditions; that is,  $\theta_{JA}$  is specified for a device soldered in the circuit board for the SOIC package.

**Table 4. Thermal Resistance**

| Package Type | $\theta_{JA}$ | θ <sub>JC</sub> | Unit |

|--------------|---------------|-----------------|------|

| 8-Lead SOIC  | 158           | 43              | °C/W |

### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

## PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 2. Pin Configuration

**Table 5. Pin Function Descriptions**

| Pin No. | Mnemonic | Description                   |

|---------|----------|-------------------------------|

| 1       | OUT A    | Output Channel A.             |

| 2       | −IN A    | Inverting Input Channel A.    |

| 3       | +INA     | Noninverting Input Channel A. |

| 4       | V-       | Negative Supply Voltage.      |

| 5       | +IN B    | Noninverting Input Channel B. |

| 6       | −IN B    | Inverting Input Channel B.    |

| 7       | OUT B    | Output Channel B.             |

| 8       | V+       | Positive Supply Voltage.      |

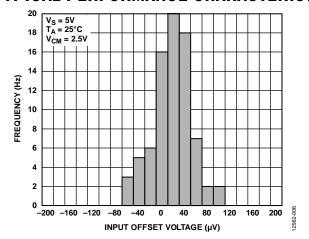

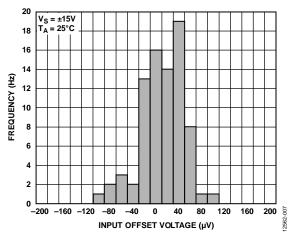

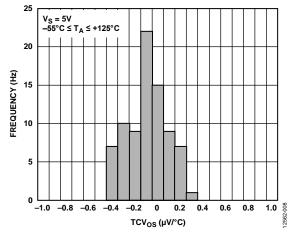

## TYPICAL PERFORMANCE CHARACTERISTICS

Figure 3. Input Offset Voltage Distribution,  $V_s = 5 V$

Figure 4. Input Offset Voltage Distribution,  $V_s = \pm 15 \text{ V}$

Figure 5. Input Offset Voltage Drift Distribution,  $V_s = 5 \text{ V}$

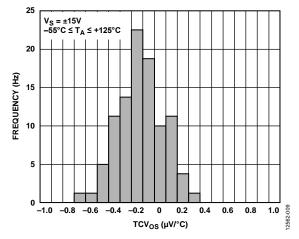

Figure 6. Input Offset Voltage Drift Distribution,  $V_S = \pm 15 \text{ V}$

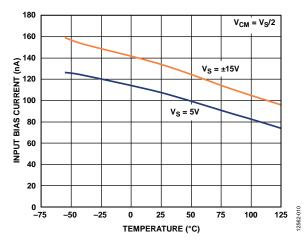

Figure 7. Bias Current vs. Temperature

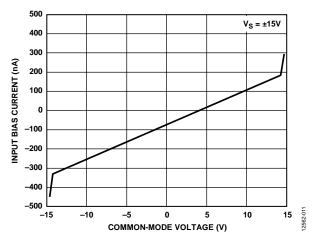

Figure 8. Input Bias Current vs. Common-Mode Voltage

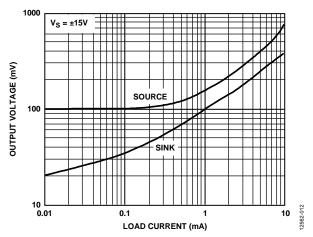

Figure 9. Output Voltage to Supply Rail vs. Load Current

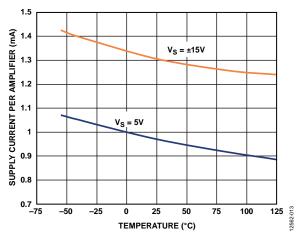

Figure 10. Supply Current vs. Temperature

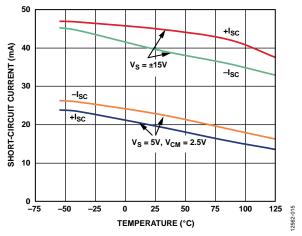

Figure 11. Short-Circuit Current vs. Temperature

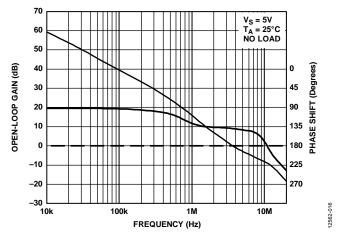

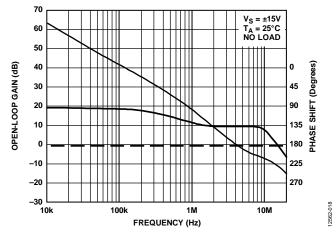

Figure 12. Open-Loop Gain and Phase vs. Frequency (No Load),  $V_s = 5 V$

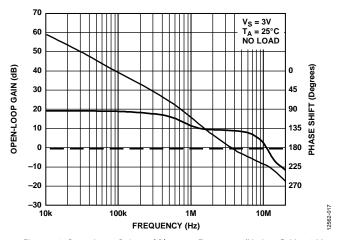

Figure 13. Open-Loop Gain and Phase vs. Frequency (No Load),  $V_S = 3 V$

Figure 14. Open-Loop Gain and Phase vs. Frequency (No Load),  $V_S = \pm 15 \text{ V}$

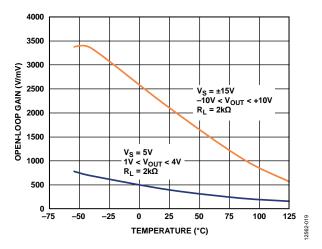

Figure 15. Open-Loop Gain vs. Temperature

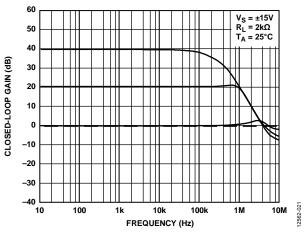

Figure 16. Closed-Loop Gain vs. Frequency (2  $k\Omega$  Load)

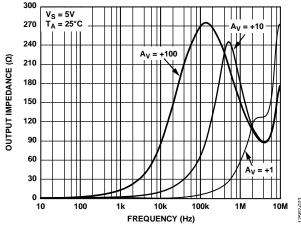

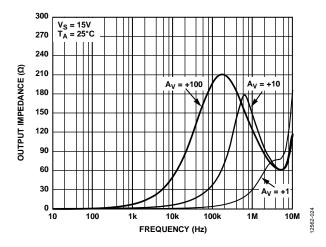

Figure 17. Output Impedance vs. Frequency

Figure 18. Output Impedance vs. Frequency

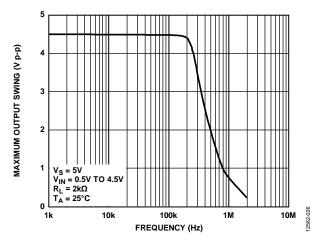

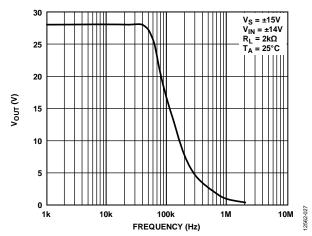

Figure 19. Maximum Output Swing vs. Frequency

Figure 20. Maximum Output Swing vs. Frequency

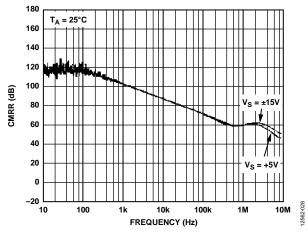

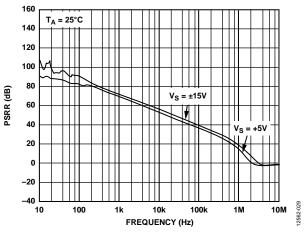

Figure 21. CMRR vs. Frequency

Figure 22. PSRR vs. Frequency

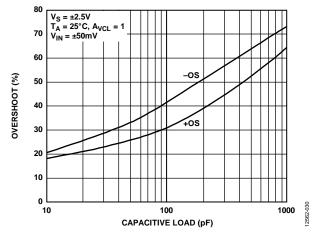

Figure 23. Small Signal Overshoot vs. Capacitive Load

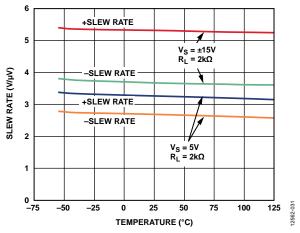

Figure 24. Slew Rate vs. Temperature

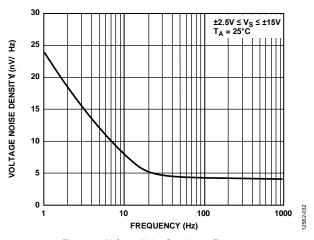

Figure 25. Voltage Noise Density vs. Frequency

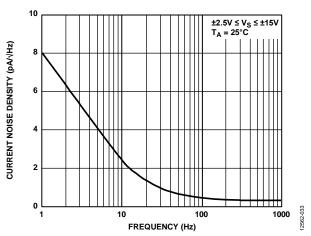

Figure 26. Current Noise Density vs. Frequency

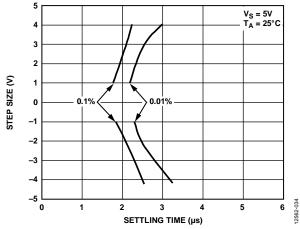

Figure 27. Step Size vs. Settling Time,  $V_S = 5 V$

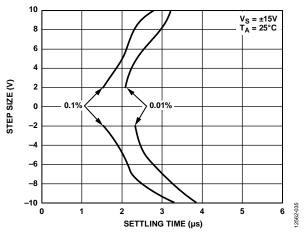

Figure 28. Step Size vs. Settling Time,  $V_S = \pm 15 \text{ V}$

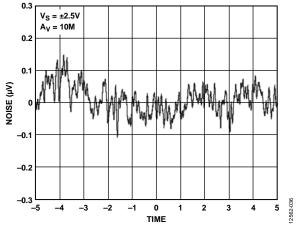

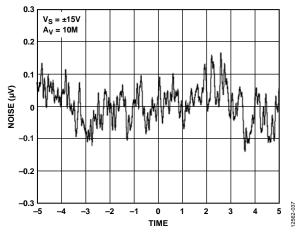

Figure 29. 0.1 Hz to 10 Hz Noise,  $V_S = \pm 2.5 V$

Figure 30. 0.1 Hz to 10 Hz Noise,  $V_S = \pm 15 V$

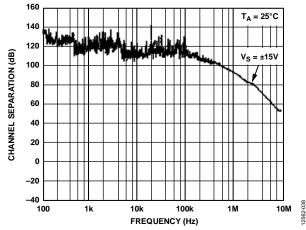

Figure 31. Channel Separation vs. Frequency

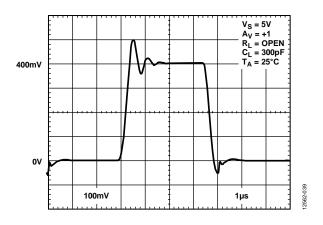

Figure 32. Small Signal Transient Response

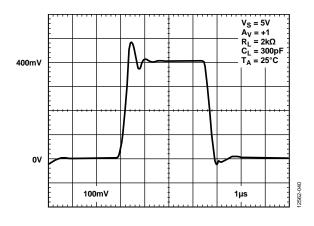

Figure 33. Small Signal Transient Response

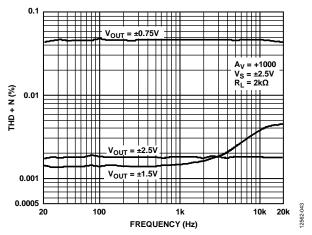

Figure 34. Total Harmonic Distortion + Noise vs. Frequency

## **OUTLINE DIMENSIONS**

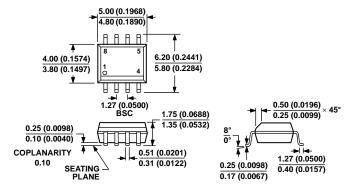

**COMPLIANT TO JEDEC STANDARDS MS-012-AA** CONTROLLING DIMENSIONS ARE IN MILLIMETERS; INCH DIMENSIONS (IN PARENTHESES) ARE ROUNDED-OFF MILLIMETER EQUIVALENTS FOR REFERENCE ONLY AND ARE NOT APPROPRIATE FOR USE IN DESIGN.

Figure 35. 8-Lead Standard Small Outline Package [SOIC\_N] Narrow Body (R-8)

Dimensions shown in millimeters and (inches)

### **ORDERING GUIDE**

| Model <sup>1</sup> | Temperature Range | Package Description                            | Package Option |

|--------------------|-------------------|------------------------------------------------|----------------|

| OP284TRZ-EP-R7     | −55°C to +125°C   | 8-Lead Standard Small Outline Package [SOIC_N] | R-8            |

<sup>&</sup>lt;sup>1</sup> Z = RoHS Compliant Part.

Rev. 0 | Page 13 of 13