# FCR4 FAMILY FCR4 CLUSTER SERIES STARTERKIT SK-MB9DF120-001 / -002

# **USER GUIDE**

# **Revision History**

| Date       | Issue                                                                                                                                              |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| 2011-06-21 | V0.1, OBe                                                                                                                                          |

|            | First draft                                                                                                                                        |

| 2011-09-29 | V1.0, OBe                                                                                                                                          |

|            | First release                                                                                                                                      |

| 2011-10-18 | V1.1 OBe / MSt                                                                                                                                     |

|            | Corrected some typos, chapter Abbreviations added                                                                                                  |

| 2011-11-22 | V1.2, MSt                                                                                                                                          |

|            | Corrected Pin numbers in Table 6-9                                                                                                                 |

| 2012-01-05 | V1.3 MSt                                                                                                                                           |

|            | Added further description for clock changes in chapter 2.4.1                                                                                       |

| 2012-03-20 | V1.4, MNa                                                                                                                                          |

|            | Added EU declaration of conformity chapter, updated recycling chapter, updated information in the WWW chapter, updated warranty disclaimer chapter |

| 2012-07-31 | V1.5, MSt                                                                                                                                          |

|            | Chapter 7 Known Issues: Added information Trace connector not useable in SK-MB9DF120-002 PCB V1.0                                                  |

| 2013-07-12 | V1.6, MSt                                                                                                                                          |

|            | Corrected chapter 1.2 Features, Information of power supply corrected                                                                              |

|            |                                                                                                                                                    |

# Applies To

| Order-No.       | Reference | Description                                              |

|-----------------|-----------|----------------------------------------------------------|

| SK-MB9DF120-001 | TRACE     | Full-featured variant with independent trace-capability. |

| SK-MB9DF120-002 | SOCKET    | 176-pin socket variant. Tracing blocks some MCU-ports.   |

If not mentioned otherwise, this guide applies to all boards listed in the table above. Variant-specific features/differences are tagged by the name listed under "Reference".

This document contains 44 pages.

## **Abbreviations**

ARM<sup>®</sup> is a registered trademark of ARM Limited in the EU and other countries

APIX<sup>®</sup> Automotive Pixel Link is a registered mark of INOVA Semiconductors GmbH

CAN Controller Area Network

FSEU Fujitsu Semiconductor Europe GmbH

MCU Microcontroller Unit

UART Universal Asynchronous Receiver Transmitter

USB Universal Serial Bus

## Warranty and Disclaimer

The use of the deliverables (e.g. software, application examples, target boards, evaluation boards, starter kits, schematics, engineering samples of IC's etc.) is subject to the conditions of Fujitsu Semiconductor Europe GmbH ("FSEU") as set out in (i) the terms of the License Agreement and/or the Sale and Purchase Agreement under which agreements the Product has been delivered, (ii) the technical descriptions and (iii) all accompanying written materials.

Please note that the deliverables are intended for and must only be used for reference in an evaluation laboratory environment.

The software deliverables are provided on an as-is basis without charge and are subject to alterations. It is the user's obligation to fully test the software in its environment and to ensure proper functionality, qualification and compliance with component specifications.

Regarding hardware deliverables, FSEU warrants that they will be free from defects in material and workmanship under use and service as specified in the accompanying written materials for a duration of 1 year from the date of receipt by the customer.

Should a hardware deliverable turn out to be defect, FSEU's entire liability and the customer's exclusive remedy shall be, at FSEU's sole discretion, either return of the purchase price and the license fee, or replacement of the hardware deliverable or parts thereof, if the deliverable is returned to FSEU in original packing and without further defects resulting from the customer's use or the transport. However, this warranty is excluded if the defect has resulted from an accident not attributable to FSEU, or abuse or misapplication attributable to the customer or any other third party not relating to FSEU or to unauthorised decompiling and/or reverse engineering and/or disassembling.

FSEU does not warrant that the deliverables do not infringe any third party intellectual property right (IPR). In the event that the deliverables infringe a third party IPR it is the sole responsibility of the customer to obtain necessary licenses to continue the usage of the deliverable.

In the event the software deliverables include the use of open source components, the provisions of the governing open source license agreement shall apply with respect to such software deliverables.

To the maximum extent permitted by applicable law FSEU disclaims all other warranties, whether express or implied, in particular, but not limited to, warranties of merchantability and fitness for a particular purpose for which the deliverables are not designated.

To the maximum extent permitted by applicable law, FSEU's liability is restricted to intention and gross negligence. FSEU is not liable for consequential damages.

Should one of the above stipulations be or become invalid and/or unenforceable, the remaining stipulations shall stay in full effect.

The contents of this document are subject to change without a prior notice, thus contact FSEU about the latest one.

This board and its deliverables must only be used for test applications in an evaluation laboratory environment.

# Contents

| RI | EVISIO | ON HIST   | ORY                             | 2    |

|----|--------|-----------|---------------------------------|------|

| ΑI | PPLIE  | S TO      |                                 | 2    |

| ΑI | BBRE   | VIATION   | IS                              | 3    |

| W  | ARRA   | ANTY AN   | ID DISCLAIMER                   | 4    |

| C  | ONTE   | NTS       |                                 | 5    |

| 1  | OVE    | RVIEW     |                                 | 7    |

|    | 1.1    | Introduc  | tion                            | 7    |

|    | 1.2    | Feature   | S                               | 7    |

|    | 1.3    | Kit conte | ents                            | 8    |

| 2  | HAR    | DWARE     |                                 | 9    |

|    | 2.1    | PCB Ov    | rerview                         | 9    |

|    |        | 2.1.1     | Top-View                        | 9    |

|    |        | 2.1.2     | Bottom View                     | . 11 |

|    | 2.2    | Power S   | Supply                          | . 11 |

|    |        | 2.2.1     | Input-stage                     | . 12 |

|    |        | 2.2.2     | I/O Supplies                    | . 12 |

|    |        | 2.2.3     | MCU Core supply                 | . 12 |

|    |        | 2.2.4     | Supply-Rail Monitors (LEDs)     | . 12 |

|    |        | 2.2.5     | Power distribution              | . 12 |

|    | 2.3    | Reset     |                                 | . 12 |

|    | 2.4    | MCU CI    | ocks                            | . 13 |

|    |        | 2.4.1     | Main Clock                      | . 13 |

|    |        | 2.4.2     | Sub-Clock (RTC-Clock)           | . 13 |

|    | 2.5    | On-Boa    | rd Peripherals                  | . 13 |

|    |        | 2.5.1     | UART/USB-Serial Interface       | . 14 |

|    |        | 2.5.2     | CAN-Bus Interface               | . 14 |

|    |        | 2.5.3     | APIX                            | . 14 |

|    | 2.6    | Expansi   | on Connectors                   | . 14 |

|    |        | 2.6.1     | Board-to-Board (B2B) Connectors | . 14 |

|    |        | 2.6.2     | Riser-Board Connector           | . 14 |

|    |        | 2.6.3     | IPC Connector                   | . 15 |

|    | 2.7    | Debugg    | ing Facilities                  | . 15 |

| 3  | INST   | ALLATIO   | ON                              | . 16 |

|    | 3.1    | First Co  | ntact                           | . 16 |

|    | 3.2    | Engage    |                                 | . 16 |

|    | 3.3    | Lifesign  | s                               | . 16 |

|    |        |           |                                 |      |

| 4  | CON  | FIGURATION AND TEST-POINTS                           | 17 |

|----|------|------------------------------------------------------|----|

|    | 4.1  | Jumpers                                              | 17 |

|    | 4.2  | Headers                                              | 19 |

|    | 4.3  | Test Points                                          | 19 |

| 5  | STA  | TUS DISPLAY                                          | 21 |

| 6  | CON  | NECTORS                                              | 22 |

|    | 6.1  | B2B Connectors (J5, J6)                              | 23 |

|    |      | 6.1.1 J5 Pinout                                      | 23 |

|    |      | 6.1.2 J6 Pinout                                      | 26 |

|    | 6.2  | IPC Connector (X8)                                   | 29 |

|    | 6.3  | Debug Connector (X2)                                 | 30 |

|    | 6.4  | Trace Connector (X3)                                 | 31 |

|    | 6.5  | Riser-Board Connector (X6)                           | 32 |

|    | 6.6  | DC In Plug (X4)                                      | 35 |

|    | 6.7  | CAN-Bus Connector (X5)                               | 35 |

|    | 6.8  | USB Connector (X7)                                   | 35 |

|    | 6.9  | APIX Connector (X1)                                  | 36 |

| 7  | KNO  | WN ISSUES                                            | 37 |

| 8  | TRO  | UBLE SHOOTING                                        | 38 |

| 9  | REL  | ATED PRODUCTS                                        | 39 |

| 10 | APP  | ENDIX                                                | 40 |

|    | 10.1 | Tables 40                                            |    |

|    | 10.2 | Figures 40                                           |    |

| 11 | INFC | RMATION IN THE WWW                                   | 41 |

| 12 | EU-K | CONFORMITÄTSERKLÄRUNG / EU DECLARATION OF CONFORMITY | 42 |

| 13 | CHIN | IA-ROHS REGULATION                                   | 43 |

| 14 | REC  | YCLING                                               | 44 |

## 1 Overview

#### 1.1 Introduction

The SK-MB9DF120-001 is a quick evaluation board for the Fujitsu FCR4 Cluster series flash microcontroller MB96DF126 (Atlas). It can be used stand-alone for software development and testing or as a simple target board to work with the debug system.

Optionally, the adapter board ADA-FCR4-MULTIIO-001 is available as plug-under. It extends the capabilities by additional interfaces and headers which provide easy access to the MCU-signals.

As an addition to the Multi-IO board, the ADA-FCR4-CLUSTER-001 is available. It provides a complete automotive dashboard solution without separate microcontroller (all signals are controlled from the SK-MB9DE120). It is connected to the Multi-IO board using a flat-cable.

## 1.2 Features

- Supports Fujitsu's FCR4 Cluster series MB9DF126 (Atlas) microcontrollers

- Requires 12V external DC power supply (e.g. PSU FIX12V-24W)

- On-board 5V, 3V3 and 1V2 voltage regulators for I/O- and MCU supply

- Power-LEDs for all regulated supply-rails

- Selectable 5V and 3V3 voltage for specific digital (VDP5 and DVCC) and analogue (AVCC5 and AVRH5) power domains

- Reset-button with LED-indicator

- On-board voltage supply supervisor

- In-Circuit serial Flash programming using the JTAG port

- 4-20MHz main crystal oscillator for APIX and MCU clock.

- 32 kHz crystal for sub clock operation (realtime clock, low-power operation)

- Full APIX high-speed serial interface on-board. An RJ-45 connector allows to connect a standard Cat6e/Cat7 network-cable.

- Riser-card connector for external bus-interface (EBI) and high-speed QSPI. Signals not used on Riser-card are routed to b2b connectors.

- Riser-cards with various memory-types (QSPI NOR-Flash, NAND-Flash, SDRAM) available, passive (all signals passed back to SK-board) card included.

- All GPIO-pins not used on-board are available thru Board-to-Board connectors on the bottomside.

- Fujitsu IPC connector with AIC-, SPI-ports and some GPIOs/interrupt-lines providing connection to UI-boards (LCD, instrumentation, etc.) or customer solutions.

- USB to serial converter (FT232R) connected to USART0 provides direct PC-serial connection using a standard USB-A (PC) to Mini-B (SK) cable.

- One CAN-Bus interface on male D-Sub-09 connector with industry-standard pinout

- ARM standard 20 pin IDC JTAG connector for flash-programming and debugging

- Trace-probe connector for 8 (variant SOCKET) or 16 (variant TRACE) bit wide tracing

- Test-points for internal signals

## 1.3 Kit contents

- Variant TRACE or variant SOCKET PCB.

- USB-A to Mini-B cable.

- Screws with spacers to mount onto a carrier-board or place on the table.

- MEM-FCR4-001 pass-through Riser-Board.

## 2 Hardware

## 2.1 PCB Overview

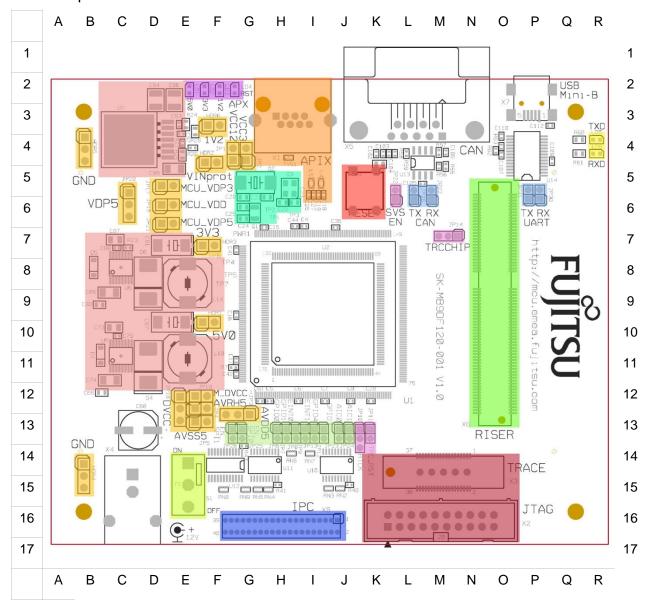

## 2.1.1 Top-View

Figure 2-1: Top View PCB-Rev.1.0

- Variant TRACE U1: MCU MB9DF126 (Atlas) microcontroller in QFP296 package

- Variant SOCKET U2: MCU MB9DF126 (Atlas) microcontroller in QFP176 socket (removable)

- Q1: 32768Hz RTC-crystal (SubClk)

- Variant SOCKET Q2/Q4: 4..20MHz crystal (Q4 only PCB-Rev.1.1 for 20MHz crystal) for MainClk.

- Variant TRACE Q3: 20MHz crystal for MainClk (values down to 4MHz possible, if same package).

- 12V external DC power supply, 5V, 3V3 and 1V2 voltage regulators, S1 power switch

- Power-LEDs for the 5V0, 3V3 and 1V2 power rails, SW1 Reset-button, Reset-LED

- X2, X3: debug and trace ports for standard connectors

- APIX, USB (UART-emulation) and CAN (native) connectors

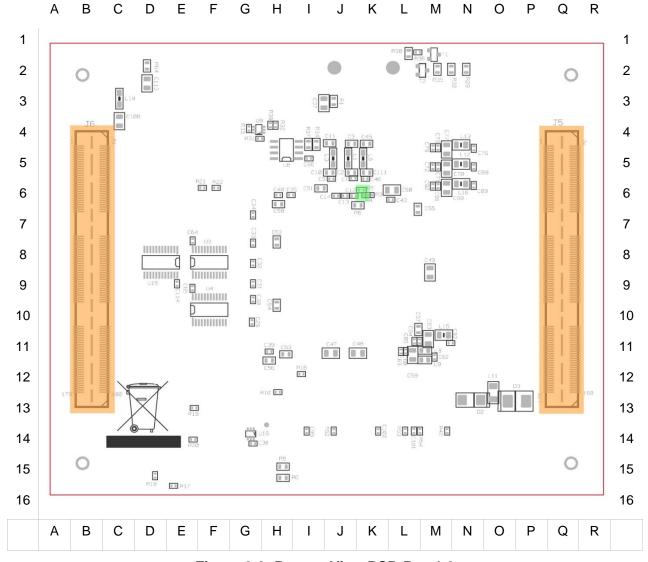

#### 2.1.2 Bottom View

Figure 2-2: Bottom View PCB-Rev.1.0

- J5, J6 Board-to-Board connectors to Multi-IO

- R4, R5: Solder-Jumper to select 4MHz Fallback-Oscillator (defaults to 20MHz Osc.)

## 2.2 Power Supply

The power supply circuit consists of the input-stage and three voltage-regulators. The regulators are switch-mode types (step-down).

Having the enables of the lower voltage supplies tied to the next higher voltage supply guarantees correct sequencing in the order required (5V0  $\rightarrow$  3V3  $\rightarrow$  1V2). Power-down/disconnect of power-domains and/or -rails is not supported.

All regulators are supplied from the input-rail Vin\_prot (filtered input voltage, no regulator-staggering).

Headers are connected to each voltage-rail to allow measuring the voltages. They should not be used to power custom electronics. Each stage provides a header connected to connect to the

corresponding domain. Care must be taken when connecting to the 1V2-domain as noise on this rail will have much more impact on this rail due to the low absolute voltage.

## 2.2.1 Input-stage

The power-supply connector is a standard DC-plug for a wall-cube adapter. Allowed input voltage ranges from 9 to 12V, the adaptor should have a minimum power-rating of 6W (500mA @ 12V).

After the power-switch, a reverse-voltage protection diode (D2) and a TVS (D3) follow. The latter suppresses/damps high voltage surges from the wall-cube which would otherwise pass the following inductor and capacitors.

The inductor (L11) filters noise generated on-board, before it reaches the supply-cable which presents a good antenna for EMI. Filtering incoming noise is a bonus.

## 2.2.2 I/O Supplies

The 5V0 and 3V3 supplies use the same regulator-type, each fixed to the desired output-voltage. As with all switching regulators, the designs are critical in terms of switching noise radiation (over the air and along the traces).

Each regulator provides up to 3A on its rail.

## 2.2.3 MCU Core supply

The 1V2 supply for the MCU core is generated by a DC/DC switching module providing up to 3A.

## 2.2.4 Supply-Rail Monitors (LEDs)

Each supply-rail has its own LED-indicator. For the 1V2 rail, the LED is driven from the 3V3 rail and just switched from the 1V2 rail.

All three rails are additionally monitored by a system-voltage supervisor which generates reset if any rail fails.

#### 2.2.5 Power distribution

The three stabilized voltages drive the various MCU power-domains either directly (single-voltage domains MCU\_VDD, MCU\_VDP3) or through a 3-pin jumper (dual-voltage domains VDP5, DVCC).

Additionally, there is a jumper before each domain's EMI-filter to allow injection of external power or measuring current-consumption of the domain.

#### 2.3 Reset

Board-Reset can be generated by basically two sources. Both are connected to the system-reset which includes the MCU RST\_X signal. Both sources can be disconnected from the reset-net by separate jumpers, thus excluding them from generating the reset-signal,

U8 generates the reset to the MCU and all other devices if one of the three system-voltages fails (System Voltage Supervisor). It also monitors a push-button, generating a short reset-pulse (~100µs) if this reset-button is pressed shortly. A longer pulse will be generated if the button is pressed for some seconds. Caution: the SVS monitors the on-board generated voltages, not the MCU power-domains. If any of the domains is supplied externally, it is left to the user to provide a proper reset signal (if required).

Another reset source comes from the two debugging connectors JTAG and TRACE. Their shared signal can also be disconnected from the internal net.

Having the reset-pin on the MCU belonging to the VDP5 domain and the memory-interface pins driven by the VDP3 domain, two reset-signals are required.

While RST\_X\_3V3 is driven together with RST\_X\_VDP5, it cannot generate a reset by itself. Therefore, all resets must originate from RST\_X\_VDP5. Both signals are open-drain with a 10kR pull-up to the corresponding MCU power-domain.

RST\_X\_3V3 is only available on the riser-board connector. The b2b-connectors on the rear-side only provide RST\_X\_VDP5.

RST\_X\_VDP5 also drives a LED which lights when the signal is active (low). On power-up or a press of the reset-button, the LED will flash according to the pulse generated by the SVS. If the reset-button is pressed only for a short time, although the LED also flashes, this cannot be observed directly as this pulse is too short to be detected by the human eye.

#### 2.4 MCU Clocks

#### 2.4.1 Main Clock

The MCU is clocked using its internal 4-20MHz oscillator as this is the MainClk net, it controls all timing of the MCU, including the APIX-Phy.

Variant TRACE: The default delivery is a 20MHz crystal at Q3. A 4MHz alternative oscillator is available using Q2 (Q4 is not to be used for this variant). The oscillator to be used is determined by the solder-jumper R4/R5 (defaults to the 20MHz-oscillator).

#### Default:

- R4: 0R, R5 open

- C20 = 0R

Change to 4MHz (Q2) Chrystal:

- Open R4, solder 0R to R5

- Replace C22 (0R) with 8pF

- Replace C20 (8pF) with 0R

Variant SOCKET: Q2/Q4 (Q4 with board-rev. 1.1) are used as clock-references. Either one can be populated, not both. The default crystal-frequency is a 20MHz (Q4 for board-rev. 1.1) oscillator.

## Default: 20MHz:

Q2 (PCB V1.0) or Q4 (PCBV1.0)

#### Change to 4MHz:

- Solder 4MHz crystal to Q2

- In case of PCB V1.1: Remove Q4 before soldering Q2.

Caution: changing the crystal requires special soldering-tools. Otherwise the PCB may be damaged. Warranty will be void if soldering has been done on the PCB.

When replacing the crystal, make sure to choose the correct load-capacitors for the new crystal. See the crystal's datasheet for specifications.

#### 2.4.2 Sub-Clock (RTC-Clock)

Q1 is a 32.768kHz crystal connected to the MCU's real-time clock oscillator. This clock is used to track time, while the other crystal oscillator is disabled.

## 2.5 On-Board Peripherals

The board provides three interfaces for external communication.

#### 2.5.1 UART/USB-Serial Interface

Two port-signals (P0\_45, P0\_47) are connected to a USB-Serial converter chip (FT232R). The ports can be controlled by USART0, thus allowing a serial interface between the MCU and a PC.

For the interface-converter, drivers exist for all major operating systems (OSX, Linux, Windows) either built-in (Linux) or for download (Windows). They provide a standard serial interface ("COMport"/"ttyUSB") to the applications, so any terminal program can be used to transmit data between the MCU and a PC.

The interface does not provide hardware-handshake, thus it is left to the software to provide some kind of flow-control and/or resynchronization, if necessary.

There is one LED per direction (RX, TX) signalling data-transmission.

The two ports can be disconnected from the converter by two jumpers, freeing them for other usage (the two signals are also available on the B2B connector J5).

The converter chip is powered from the USB-connector, making its operation independent on the power-status of the board. However, as the supply of the serial interface I/O lines is powered from VDP5, the voltages here always match the requirements of the connected port-signals.

## 2.5.2 CAN-Bus Interface

Two ports from the MCU (P2\_40, P2\_41) are connected to a CAN-Bus transceiver. The CAN-bus itself is connected to a standard D-sub connector. The two signals are also RX and TX of the internal CAN0-controller.

As with the UART, jumpers are available for each port to disconnect them from the interface, freeing them for use from the B2B connector J5.

#### 2.5.3 APIX

The MB96DF126 (Atlas) provides a dedicated (non-multiplexed) PHY for the APIX high-speed serial interface. The signals are routed to a RJ-45 connector allowing standard twisted-pair cable to be used.

## 2.6 Expansion Connectors

## 2.6.1 Board-to-Board (B2B) Connectors

On the bottom-side, there are two board-to-board (b2b) connectors (J5, J6). All MCU ports are available here, along with power-supply and additional control-signals like reset.

Layout and placement of the SK-MB9DF120-xxx allows to plug a Fujitsu Multi-I/O board (ADA-FCR4-MULTIIO-001) under the board, providing direct access to the ports via standard-raster headers along with other features.

Alternatively, a custom PCB can be connected.

## 2.6.2 Riser-Board Connector

X6 is a double-sided card-edge connector with 2\*70 contacts. All ports providing either HSSPI (high-speed QSPI) or external bus interface (EBI) signals are routed to one side of this connector together with VDP3 and RST\_X\_VDP3 (VDP3-based reset-signal).

The pins opposite of the each port-signal are routed to the B2B connectors.

This structure allows to insert various PCBs ("Riser-Cards") requiring the external bus or high-speed SPI without passing the long path through the expansion connectors and a plug-under board. With the optimized routing of all signals, the full speed of the two interfaces can be utilized, allowing connection to fast QSPI Flash-devices, SDRAMs or other critical hardware.

Ports not used for a particular application must be passed-through by the riser-card. For example, the default card shipped with the starter kit consists completely of direct connections between the front- and rear-side pads, passing all ports to the bottom B2B connectors.

#### 2.6.3 IPC Connector

This is a 1.27mm (0.05in) header which is used to connect a Fujitsu graphics-card like Emerald or Jade to the SK-MB9DF120-xxx. It provides two normal SPI interfaces along with two AIC ports and some GPIO signals with interrupt-capabilities.

As all signals are also available on the rear B2B-connectors, bus-switches (for AICs and SPIs) and jumpers (for GPIOs) are provided to disconnect the signals from the header. The bus-switches are controlled by jumpers, so each group of signals can be (dis-)connected separately.

## 2.7 Debugging Facilities

The Starter-kit provides a JTAG-Interface on a 20-pin 2.54mm (0.1in) IDC-header for debugging. The header uses the ARM standard pin out.

The second facility is an ARM-standard trace-connector. This combines the JTAG-interface with an up to 16-bit trace-port for extended debugging features.

Only one connector may be used at the same time, as some signals are shared between them. Debugging requires a proper interface and corresponding software on the host system.

## 3 Installation

#### 3.1 First Contact

After opening the box, please check first if all parts are included. If any parts are missing, ask your vendor.

The kit includes electrostatic sensitive devices. Unpacking should be done in an anti-static environment.

After removing the packing-material, check all parts and especially the PCB for damages. Also check the jumper-settings before initial powering up the board.

## 3.2 Engage

To power-up the board, first change the slider-switch (S1) to the "off"-position. Then connect an AC-adaptor Connect the DC-plug (inner is positive) to the board (X4), then turn on the slider-switch.

The AC-adaptor must provide 9-12V/1A min. The positive (+) supply must be on the inner tip, while the negative supply (-/GND) is on the outer ring. The power-input includes reverse-polarity protection.

## 3.3 Lifesigns

After powering-up by turning switch S1, the power-LEDs should turn on without noticeable delay.

Additionally, the reset-LED flashes once, signalling release of the reset-signal by the voltage supervisor.

If no LED lights op, turn off the power switch and check the polarity of the supply. If this is ok, or if some power-LEDs are missing, flicker or show otherwise strange behaviour, check the power-rails for shorts to GND and each other before retrying.

If the reset-LED flashes from time to time (maybe with a constant frequency), the power-supply may be too weak to supply the required current. Also check the voltages to detect drop. Most times this occurs, one or multiple power-rails are at the edge of the SVS' trigger-level and drop below, eq. if more current is drawn by a device.

Use HDR1, 3 and 6 to measure voltages. **Never short these Headers!**

## 4 Configuration and Test-Points

## 4.1 Jumpers

The SK-MB9DF-120-001 provides multiple options to access signals and configure its properties. For this, it has two variants of jumpers:

- (regular) Jumpers consist of two or three pin-headers and a small cap. They can be changed without

extra tools. They are used where changes are likely to occur. Wide jumpers (W) use a 2.54mm raster,

while small jumpers use 2.00mm. The former are used for power-connections where also measuring

may be required, while the latter are sole configuration jumpers.

- solder-jumpers change more basic options, the vast majority of applications do not require changing them from their defaults. A solder-jumper is either a single 0R0 resistor or two resistors of which only one may be placed. For the latter, a shared pad is often used to avoid placing both resistors accidentally.

| Name | Label     | Description                                                                                                                                                             | Туре        | Default | Position          |

|------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|---------|-------------------|

| JP1  | APX_VCC12 | open = access 1.2V supply for APIX.  Caution: the APIX is an analog subsystem and therefore sensitive to noise induced from the power-supply lines.                     | 2-pin wide  | closed  | top G-4           |

| JP2  | APX_VCC3  | open = access 3.3V supply for APIX.  Caution: the APIX is an analog subsystem and therefore sensitive to noise induced from the power-supply lines.                     | 2-pin wide  | closed  | top G-4           |

| JP3  | AVDD5     | select ADC-supply: 1-2 = AVRH5 2-3 = VDP5 open = external Caution: the ADC is an analog subsystem and therefore sensitive to noise induced from the power-supply lines. | 3-pin wide  | 2-3     | top G-11          |

| JP4  | AVRH5     | open = access ADC VRH5 (reference input). Caution: the ADC is an analog subsystem and therefore sensitive to noise induced from the power-supply lines.                 | 2-pin wide  | closed  | top E/F-11        |

| JP5  | AVSS5     | open = access ADC VSS.  Caution: the APIX is an analog subsystem and therefore sensitive to noise induced from the power-supply lines.                                  | 2-pin wide  | closed  | top E/F-<br>11/12 |

| JP20 | VDP5      | select VDP5 supply-rail:<br>1-2 = 3V3 (3.3V on-board rail)<br>2-3 = 5V0 (5.0V on-board rail)<br>open = external                                                         | 3-pin wide  | 2-3     | top C/D-5/6       |

| JP18 | DVCC      | select DVCC supply-rail:<br>1-2 = 3V3 (3.3V on-board rail)<br>2-3 = 5V0 (5.0V on-board rail)<br>open = external                                                         | 3-pin wide  | 2-3     | top E-11          |

| JP15 | MCU_VDD   | open = access 1.2V supply for MCU.                                                                                                                                      | 2-pin wide  | closed  | top D/E-5/6       |

| JP17 | MCU_VDP3  | open = access VDP3 domain for MCU.                                                                                                                                      | 2-pin wide  | closed  | top D/E-5         |

| JP21 | MCU_VDP5  | open = access VDP5 domain for MCU.                                                                                                                                      | 2-pin wide  | closed  | top D/E-6         |

| JP19 | MCU_DVCC  | open = access DVCC domain for MCU.                                                                                                                                      | 2-pin wide  | closed  | top E/F-11        |

| JP14 | TRCCHIP   | Select trace-signals for trace-port:  1-2 = dedicated trace-port/disable  2-3 = multiplexed ports (176pin pkg) open = none (should not be used)                         | 3-pin small | 1-2     | top M-6           |

| Name | Label     | Description                                                                                                                                                                                                                                                                                                                                     | Туре        | Default | Position          |

|------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|---------|-------------------|

|      |           | For the 296-pin package, there is no reason to choose any other setting than 1-2. For any package, any other than this setting also disconnects the multiplexed port-signals from their normal connection, rendering these ports unusable. Therefore, the 2-3 setting should never be chosen unless tracing with a 176-pin package is required. |             |         |                   |

| JP10 | RTCK-sel  | enable/disable RTCK on JTAG: 1-2 = disable (pulled to GND) 2-3 = enable open = invalid see also solder-jumper R7                                                                                                                                                                                                                                | 3-pin small | 1-2     | top J/K-<br>11/12 |

| JP11 | TRC_RST   | closed = enable resets from debug and trace connector.  Quite likely not to be changed.                                                                                                                                                                                                                                                         | 2-pin small | closed  | top K-11/12       |

| JP22 | SVS_EN    | closed = enable resets from system-voltage supervisor chip. As the SVS also monitors the reset-button, this also disables manual reset if open.  Quite likely not to be changed.                                                                                                                                                                | 2-pin small | closed  | top K/L-5         |

|      |           |                                                                                                                                                                                                                                                                                                                                                 |             |         |                   |

| JP6  | IPC_GPIO0 | closed = connect GPIO0 on IPC connector to MCU-port P1_8                                                                                                                                                                                                                                                                                        | 2-pin small | open    | top H-11/12       |

| JP7  | IPC_GPIO1 | closed = connect GPIO1 on IPC connector to MCU-port P1_9                                                                                                                                                                                                                                                                                        | 2-pin small | open    | top H-11/12       |

| JP8  | IPC_EINT0 | closed = connect EINT0 on IPC connector to MCU-port P1_10                                                                                                                                                                                                                                                                                       | 2-pin small | open    | top H/I-11/12     |

| JP9  | IPC_EINT1 | closed = connect EINT on IPC connector to MCU-port P1_11                                                                                                                                                                                                                                                                                        | 2-pin small | open    | top I-11/12       |

| JP12 | IPC_GPIO3 | closed = connect GPIO0 on IPC connector to MCU-port P3_16 (via Riser-Board) <sup>1</sup>                                                                                                                                                                                                                                                        | 2-pin small | open    | top I-11/12       |

| JP13 | IPC_GPIO4 | closed = connect GPIO0 on IPC connector to MCU-port P3_14 (via Riser-Board) <sup>1</sup>                                                                                                                                                                                                                                                        | 2-pin small | open    | top I-11/12       |

| JP23 | AIC0_EN   | closed = connect AIC0 on IPC connector to MCU-ports P1_0 to P1_5                                                                                                                                                                                                                                                                                | 2-pin small | open    | top J-11/12       |

| JP24 | AIC1_EN   | closed = connect AIC0 on IPC connector to MCU-ports P1_6, P1_7, P1_20 to P1_23.                                                                                                                                                                                                                                                                 | 2-pin small | open    | top J-11/12       |

| JP25 | SPI0_EN   | closed = connect SPI0 on IPC connector to MCU-ports P1_12 to P1_15.                                                                                                                                                                                                                                                                             | 2-pin small | open    | top G-11/12       |

| JP26 | SPI1_EN   | closed = connect SPI1 on IPC connector to MCU-ports P1_16 to P1_19.                                                                                                                                                                                                                                                                             | 2-pin small | open    | top G-11/12       |

| JP27 | CAN_RXD   | closed = connect RXD on CAN-Interface to MCU-port P2_41                                                                                                                                                                                                                                                                                         | 2-pin small | closed  | top L/M-5         |

| JP28 | CAN_TXD   | closed = connect TXD on CAN-Interface to MCU-port P2_40                                                                                                                                                                                                                                                                                         | 2-pin small | closed  | top L-5           |

|      |           |                                                                                                                                                                                                                                                                                                                                                 |             |         |                   |

<sup>1</sup> If no Riser-Board is plugged into, or if the port is not passed through from the Riser-Board, the signal is not available here (same as opening the jumper). Furthermore, the Riser-Board may connect this signal to a different MCU-signal (this latter will not happen for regular Fujitsu Riser-Boards).

| Name  | Label    | Description                                                                                                                                                             | Туре        | Default | Position                                         |

|-------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|---------|--------------------------------------------------|

| JP30  | UART_RXD | closed = connect RXD on UART-Interface to MCU-port P0_45                                                                                                                | 2-pin small | closed  | top P-5                                          |

| JP31  | UART_TXD | closed = connect TXD on UART-Interface to MCU-port P0_47                                                                                                                | 2-pin small | closed  | top O/P-5                                        |

|       |          |                                                                                                                                                                         |             |         |                                                  |

| R7    |          | closed = enable RTCK open to avoid disturbance on TCK line if RTCK is not used. If operating on lower frequencies, can be left connected if no problems arise with TCK. | solder, 1R  | closed  | top G-10<br>(directly at<br>296pin<br>footprint) |

| R4/R5 |          | Variant TRACE only: R4 = 20MHz oscillator selected R5 = 4MHz oscillator selected                                                                                        | solder, 2R  | R4      | top J-5/6                                        |

Table 4-1: Default Jumper settings and location

On wide jumpers, the cap can be replaced by an amperemeter to measure current. However, care must be taken to avoid inducing noise into the connected cables. Alternatively, if the cap is removed, external power can be feed into the corresponding domain. Caution: do not backdrive current into the supply-rails. Check the schematics before connecting an external power-supply to a jumper's output pin (the pin which drives the power-domain). Double-check before powering up!

DVCC, AVCC5 and VDP5 (see further description below) must be set to the same voltage-rail when zero point detection (ZPD) on any of the SMC ports is to be used. Check the datasheet for further requirements on the combination of voltages.

#### 4.2 Headers

Headers are intended to access interesting nets on the PCB. They have the same sizes as wide jumpers, but may <u>never</u> be shortened.

| Name    | Label    | Description                                                                                                           | Туре              | Position      |

|---------|----------|-----------------------------------------------------------------------------------------------------------------------|-------------------|---------------|

| HDR1    | 5V0      | 5.0V rail voltage measuring header.  Do not inject any current here!                                                  | 2-pin wide        | top F-9       |

| HDR2    | VIN_prot | Filtered and protected (against surges and reverse polarity) input voltage. May be used to inject an external supply. | 2-pin wide        | top F-4       |

| HDR3    | 3V3      | 3.3V rail voltage measuring header.  Do not inject any current here!                                                  | 2-pin wide        | top F-6/7     |

| HDR4, 5 | GND      | Access-points to the GND-plane. Can be used as reference for scopes, logic-analyzers, voltmeters, etc.                | 3-pin wide (each) | top B-4, B-13 |

| HDR6    | 1V2      | 1.2V rail voltage measuring header.  Do not inject any current here!                                                  | 2-pin wide        | top F-3       |

**Table 4-2: Header location**

#### 4.3 Test Points

Test points are not for permanent connection, but mostly for failure-tracking. Normally, there is no need to access them.

| Name Label Description Position |  |

|---------------------------------|--|

|---------------------------------|--|

| Name | Label       | Description                                                          | Position  |

|------|-------------|----------------------------------------------------------------------|-----------|

| TP1  | SubClk      | input of 32768Hz crystal-oscillator (RTC, etc.).                     | top H-6   |

| TP2  | MainClk     | MainClk frequency for variant SOCKET (Q2/Q4).                        | top H-5/6 |

| TP3  | APIXCIk     | MainClk frequency for variant TRACE (Q3).                            | top H-6   |

| TP4  | SYSC_CKOT   | MCU-port P0_41 which can have this signal multiplexed on its output. | top F-7   |

| TP5  | SYSC_CKOTX  | MCU-port P0_42 which can have this signal multiplexed on its output. | top F-7   |

| TP6  | RTC_WOT     | MCU-port P0_40 which can have this signal multiplexed on its output. | top F-7   |

| TP7  | WDG_OBSERVE | MCU-port P0_43 which can have this signal multiplexed on its output. | top F-7   |

**Table 4-3: Test point location**

The crystal test points TP1-3 are very sensitive to noise and load-factors, especially capacitive loads can change the frequency dramatically. If possible, the clocks should be measured indirectly using a high-speed timer or SYSC\_CKOT.

# 5 Status Display

For user information, there are four LEDs on the board. Each power-rail (the supply generated on-board), is monitored by a single LED.

In addition, the reset-LED shows the status of the reset-line. For the default configuration and no external reset (JTAG, button or from a plugged-under PCB), this is the status of the system-voltage supervisor (SVS). It will be lit if any voltage-rail is out of its allowed limits.

| Name | Label  | Description (when lit)           | Position |

|------|--------|----------------------------------|----------|

| LD1  | orange | 5V0 rail up                      | top E-2  |

| LD2  | yellow | 3V3 rail up                      | top F-2  |

| LD3  | green  | 1V2 rail up (driven by 3V3-rail) | top F-2  |

| LD4  | red    | reset active                     | top G-2  |

Table 5-1: LED position and meaning

## 6 Connectors

The following table lists the location of all connectors on the board. The pin-out of each connector is listed in separate sections.

| Name | Туре                             | Description                                                                                                                                                                             | Position          |

|------|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| J5   | SAMTEC QSH-<br>090-01-L-D-A      | board-to-board connector. Allows to connect a Multi-IO board or any other matching I/O-board.                                                                                           | bottom Q-<br>4:12 |

| J6   | SAMTEC QSH-<br>090-01-L-D-A      | B2B, Further signals from the MCU.                                                                                                                                                      | bottom B-<br>4:12 |

| X8   | SAMTEC FTSH-<br>120-04-L-D       | IPC connector. 2*20pin 1.27mm*1.27mm pin-header for IDC cable. Allows connection of a emerald display board (or any other board supporting the provided connections).                   | F:J-14            |

| X2   | 2*10 2.54mm IDC<br>header (male) | Standard ARM 20pin debug-header with JTAG-interface. Must not be connected at the same time as X3.                                                                                      | K:O-14            |

| X3   | TYCO 5767054-1                   | 38pin connector for standard ARM trace interface (16 bits). Includes also JTAG. Must not be connected at the same time as X2.                                                           | K:O-12/13         |

| X6   | SAMTEC<br>MEC617002-<br>SDVA     | 2*70pin card-edge connector for Riser-Board. Used for high-speed interfaces like QSPI-Flash and/or SDRAM. Can also be used for custom extensions requiring the external bus of the MCU. | N/O-5:11          |

| X4   | DC-plug                          | 2.1mm pin DC plug for external power-supply.                                                                                                                                            | C/D-13/14         |

| X5   | 9pin Dsub male                   | CAN-Bus connector with standard-pinout.                                                                                                                                                 | J:N-1:3           |

| X7   | USB Mini-B plug                  | Standard USB plug to connect a PC whith USB-Serial protocol driver.                                                                                                                     | O/P-2/3           |

| X1   | RJ-45 plug                       | High-Speed differential APIX interface signals (RX, TX).                                                                                                                                | H/I-2:4           |

**Table 6-1: Connector location**

The two B2B connectors provide all MCU ports, power supplies and control-signals.

## **6.1** B2B Connectors (J5, J6)

These two connectors provide all signals to a plug-under board like the Multi-IO-Board. Signals include all MCU ports as well as reset and power supplies from the SK-board.

Signals are always routed to these connectors, even if they are used on the SK-MB9DF120-001 themselves. When using a signal on a plug-under board which is also connected to an on-board peripheral or connector (like the IPC-connector), it must be disconnected from the on-board resource by pulling the corresponding jumper. Some signals can be disconnected separately, while other signals are disconnected as a whole function-block.

Fitting mates for the other board are SAMTEC QTH type connectors.

# 6.1.1 J5 Pinout Special Signals

| Pin(s)                                                                                             | Signal     | Description                                                                                    |

|----------------------------------------------------------------------------------------------------|------------|------------------------------------------------------------------------------------------------|

| 1,2,6,7,12,13,54,55,<br>65,66,97,98,101,102,109,110,11<br>3,<br>137,138,162,167,171,172,<br>Shield | GND        | System Ground                                                                                  |

| 3-5,8-11,14-53,99,100,112,119                                                                      | n.c.       | not connected                                                                                  |

| 103,105,107                                                                                        | reserved   | do not use                                                                                     |

| 104,106,108                                                                                        | VDP5       | VDP5 power domain                                                                              |

| 164,166,168,170                                                                                    | 5V0        | 5.0V power rail                                                                                |

| 173,175,177,179                                                                                    | Vin        | Raw input power (after the power-switch, but before any filter/protection. Should not be used. |

| 174, 176, 178, 180                                                                                 | Vin_prot   | Vin after the filter. May be used to supply SK-MB9DF120 from a plug-under board.               |

| 169                                                                                                | RST_X_VDP5 | System-Reset. Open-Collector (pull-up on SK-MB9DF120). input/output                            |

Table 6-2: LED position and meaning

#### **MCU-Ports**

| ADA-FCR4-MULTIIO-<br>001 Signal | MCU<br>Port | J5 Pin | J5 Pin | MCU<br>Port | ADA-FCR4-MULTIIO-<br>001 Signal |

|---------------------------------|-------------|--------|--------|-------------|---------------------------------|

| GND                             | -           | 55     | 56     | P2_38       | GPIO0                           |

| UARTA_RX                        | P0_45       | 57     | 58     | P0_40       | UARTB_RX                        |

| UARTA_TX                        | P0_47       | 59     | 60     | P0_42       | UARTB_TX                        |

| CANA_RX                         | P2_41       | 61     | 62     | P2_45       | CANB_RX                         |

| CANA_TX                         | P2_40       | 63     | 64     | P2_44       | CANB_TX                         |

| GND                             | -           | 65     | 66     | -           | GND                             |

| EXTN2_GPIO00                    | R_P3_0      | 67     | 68     | R_P3_1      | EXTN2_GPIO01                    |

| ADA-FCR4-MULTIIO-<br>001 Signal | MCU<br>Port | J5 Pin | J5 Pin | MCU<br>Port | ADA-FCR4-MULTIIO-<br>001 Signal |

|---------------------------------|-------------|--------|--------|-------------|---------------------------------|

| EXTN2_GPIO02                    | R_P3_2      | 69     | 70     | R_P3_3      | EXTN2_GPIO03                    |

| EXTN2_GPIO04                    | R_P3_4      | 71     | 72     | R_P3_5      | EXTN2_GPIO05                    |

| EXTN2_GPIO06                    | R_P3_6      | 73     | 74     | R_P3_7      | EXTN2_GPIO07                    |

| EXTN2_GPIO08                    | R_P3_8      | 75     | 76     | R_P3_9      | EXTN2_GPIO09                    |

| EXTN2_GPIO10                    | R_P3_10     | 77     | 78     | R_P3_11     | EXTN2_GPIO11                    |

| EXTN2_GPIO12                    | R_P3_12     | 79     | 80     | R_P3_13     | EXTN2_GPIO13                    |

| EXTN2_GPIO14                    | R_P3_14     | 81     | 82     | R_P3_15     | EXTN2_GPIO15                    |

| EXTN2_GPIO16                    | R_P3_16     | 83     | 84     | R_P3_17     | EXTN2_GPIO17                    |

| EXTN2_GPIO18                    | R_P3_18     | 85     | 86     | R_P3_19     | EXTN2_GPIO19                    |

| EXTN2_GPIO20                    | R_P3_20     | 87     | 88     | R_P3_21     | EXTN2_GPIO21                    |

| EXTN2_GPIO22                    | R_P3_22     | 89     | 90     | R_P3_23     | EXTN2_GPIO23                    |

| EXTN2_GPIO24                    | R_P3_24     | 91     | 92     | R_P3_25     | EXTN2_GPIO25                    |

| EXTN2_GPIO26                    | R_P3_26     | 93     | 94     | R_P3_27     | EXTN2_GPIO27                    |

| EXTN2_GPIO28                    | R_P3_28     | 95     | 96     | R_P3_29     | EXTN2_GPIO29                    |

| GND                             | -           | 97     | 98     | -           | GND                             |

| GPIO1                           | NC          | 99     | 100    | NC          | GPIO2                           |

| GND                             | -           | 101    | 102    | -           | GND                             |

| P_1V2                           | -           | 103    | 104    | -           | VDP5                            |

| P_1V2                           | -           | 105    | 106    | -           | VDP5                            |

| P_1V2                           | -           | 107    | 108    | -           | VDP5                            |

| GND                             | -           | 109    | 110    | -           | GND                             |

| POTI_AN                         | P0_44       | 111    | 112    | NC          | SOUND_SGA                       |

| GND                             | -           | 113    | 114    | P2_47       | SOUND_SGO                       |

| CLUSTER_EXT_INT0                | P0_46       | 115    | 116    | P2_36       | CLUSTER_PWM0                    |

| CLUSTER_EXT_INT1                | P2_39       | 117    | 118    | P2_37       | CLUSTER_PWM1                    |

| GPIO3                           | NC          | 119    | 120    | P2_38       | CLUSTER_PWM2                    |

| CLUSTER_SMC00                   | P1_0        | 121    | 122    | P1_4        | CLUSTER_SMC10                   |

| CLUSTER_SMC01                   | P1_1        | 123    | 124    | P1_5        | CLUSTER_SMC11                   |

| CLUSTER_SMC02                   | P1_2        | 125    | 126    | P1_6        | CLUSTER_SMC12                   |

| CLUSTER_SMC03                   | P1_3        | 127    | 128    | P1_7        | CLUSTER_SMC13                   |

| CLUSTER_SMC20                   | P1_8        | 129    | 130    | P1_12       | CLUSTER_SMC30                   |

| CLUSTER_SMC21                   | P1_9        | 131    | 132    | P1_13       | CLUSTER_SMC31                   |

| CLUSTER_SMC22                   | P1_10       | 133    | 134    | P1_14       | CLUSTER_SMC32                   |

| ADA-FCR4-MULTIIO-<br>001 Signal | MCU<br>Port | J5 Pin | J5 Pin | MCU<br>Port | ADA-FCR4-MULTIIO-<br>001 Signal |

|---------------------------------|-------------|--------|--------|-------------|---------------------------------|

| CLUSTER_SMC23                   | P1_11       | 135    | 136    | P1_15       | CLUSTER_SMC33                   |

| GND                             | -           | 137    | 138    | -           | GND                             |

| CLUSTER_GPIO0                   | P0_41       | 139    | 140    | R_P3_33     | LED0                            |

| CLUSTER_GPIO1                   | P0_43       | 141    | 142    | R_P3_34     | LED1                            |

| CLUSTER_GPIO2                   | P2_42       | 143    | 144    | R_P3_35     | LED2                            |

| CLUSTER_GPIO3                   | P2_43       | 145    | 146    | R_P3_36     | LED3                            |

| CLUSTER_GPIO4                   | P2_46       | 147    | 148    | R_P3_37     | LED4                            |

| CLUSTER_GPIO5                   | P1_16       | 149    | 150    | R_P3_38     | LED5                            |

| CLUSTER_GPIO6                   | P1_17       | 151    | 152    | R_P3_39     | LED6                            |

| CLUSTER_GPIO7                   | P1_18       | 153    | 154    | R_P3_40     | LED7                            |

| CLUSTER_GPIO8                   | P1_19       | 155    | 156    | P0_48       | BUTTON_EXT_INT0                 |

| CLUSTER_GPIO9                   | P1_20       | 157    | 158    | P0_49       | BUTTON_EXT_INT1                 |

| CLUSTER_GPIO10                  | P1_21       | 159    | 160    | P0_50       | BUTTON_EXT_INT2                 |

| CLUSTER_GPIO11                  | P1_22       | 161    | 162    | -           | GND                             |

| CLUSTER_GPIO12                  | P1_23       | 163    | 164    | -           | P_5V                            |

| BUTTON_EXT_INT3                 | P0_51       | 165    | 166    | -           | P_5V                            |

| GND                             | -           | 167    | 168    | -           | P_5V                            |

| BOARD_RST_X                     | -           | 169    | 170    | -           | P_5V                            |

| GND                             | -           | 171    | 172    | -           | GND                             |

| P_12V                           | -           | 173    | 174    | -           | P_12V_P                         |

| P_12V                           | -           | 175    | 176    | -           | P_12V_P                         |

| P_12V                           | -           | 177    | 178    | -           | P_12V_P                         |

| P_12V                           | -           | 179    | 180    | -           | P_12V_P                         |

Table 6-3: J5 signal assignment

Signals R\_P\* are indirect connections. They come from the "output"-side of the Riser-Board, thus are not connected anywhere unless the Riser-Board connects them the corresponding MCU-port. The numbering used here is for a standard Riser-Board (MEM-FCR4-001) which connects all MCU-ports to the adjacent "output" R\_P\*-signal without any crossover. For other Riser-Boards, some to all of the R\_P\*-signals are not available (unconnected). Although possible, a Riser-Board should not pass an input-port from the MCU on a different R\_P\*-signal.

## Note:

MCU Port Pin P2\_28 is connected twice at J5: Pin 56 (GPIO Signal) and Pin 120 (CLUSTER\_PWM2).

## 6.1.2 J6 Pinout

## Special Signals

| Pin(s)                                                                                                                                                                            | Signal | Description      |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------------------|

| 5,6,25,26,31,32,37,38,46,47,51,52,<br>65,66,71,72,77,78,83,84,,89,90,95,<br>96,100,101,114,115,<br>125,126,131,132,137,138,143,144,<br>149,150,155,156,160-162,175,176,<br>Shield | GND    | System Ground    |

| 7-24,33-36,41-44,53-60,<br>61-64,67-70,73-76,79-82,85-88,91-<br>94,97,99,103,105,107,<br>121-124,127-130,133-136,139-<br>142,145-148,151-154,157-159,163-<br>168,170,172-174      | n.c.   | not connected    |

| 1-4,177-180                                                                                                                                                                       | 3V3    | 3.3V power rail. |

Table 6-4: J6 power supply pins

## **MCU-Ports**

| ADA-FCR4-MULTIIO-<br>001 Signal | MCU Port<br>Pin | J6<br>Pin | J6<br>Pin | MCU Port<br>Pin | ADA-FCR4-MULTIIO-<br>001 Signal |

|---------------------------------|-----------------|-----------|-----------|-----------------|---------------------------------|

| I2SA_ECLK                       | P2_32           | 27        | 28        | P2_35           | I2SA_SCK                        |

| I2SA_SD                         | P2_33           | 29        | 30        | P2_34           | I2SA_WS                         |

| GND                             | -               | 31        | 32        | -               | GND                             |

| I2SB_ECLK                       | NC              | 33        | 34        | NC              | I2SB_SCK                        |

| I2SB_SD                         | NC              | 35        | 36        | NC              | I2SB_WS                         |

| GND                             | -               | 37        | 38        | -               | GND                             |

| I2CA_SDA                        | P0_63           | 39        | 40        | P0_62           | I2CA_SCL                        |

| I2CC_SDA                        | NC              | 41        | 42        | NC              | I2CB_SCL                        |

| P3V3_EXT_INT2                   | NC              | 43        | 44        | NC              | I2CC_SCL                        |

| P3V3_EXT_INT2                   | R_P3_32         | 45        | 46        | -               | GND                             |

| GND                             | -               | 47        | 48        | R_P3_41         | P3V3_EXT_INT0                   |

| CAP_CLK                         | NC              | 49        | 50        | R_P3_42         | P3V3_EXT_INT1                   |

| GND                             | -               | 51        | 52        | -               | GND                             |

| CAP_VI0                         | NC              | 53        | 54        | NC              | CAP_VI1                         |

| CAP_VI2                         | NC              | 55        | 56        | NC              | CAP_VI3                         |

| CAP_VI4                         | NC              | 57        | 58        | NC              | CAP_VI5                         |

| CAP_VI6                         | NC              | 59        | 60        | NC              | CAP_VI7                         |

| DISP1_R0                        | NC              | 61        | 62        | NC              | DISP1_R2                        |

| DISP1_R1                        | NC              | 63        | 64        | NC              | DISP1_R3                        |

| ADA-FCR4-MULTIIO-<br>001 Signal | MCU Port<br>Pin | J6<br>Pin | J6<br>Pin | MCU Port<br>Pin | ADA-FCR4-MULTIIO-<br>001 Signal |

|---------------------------------|-----------------|-----------|-----------|-----------------|---------------------------------|

| GND                             | -               | 65        | 66        | -               | GND                             |

| DISP1_R4                        | NC              | 67        | 68        | NC              | DISP1_R6                        |

| DISP1_R5                        | NC              | 69        | 70        | NC              | DISP1_R7                        |

| GND                             | -               | 71        | 72        | -               | GND                             |

| DISP1_G0                        | NC              | 73        | 74        | NC              | DISP1_G2                        |

| DISP1_G1                        | NC              | 75        | 76        | NC              | DISP1_G3                        |

| GND                             | -               | 77        | 78        | -               | GND                             |

| DISP1_G4                        | NC              | 79        | 80        | NC              | DISP1_G6                        |

| DISP1_G5                        | NC              | 81        | 82        | NC              | DISP1_G7                        |

| GND                             | -               | 83        | 84        | -               | GND                             |

| DISP1_B0                        | NC              | 85        | 86        | NC              | DISP1_B2                        |

| DISP1_B1                        | NC              | 87        | 88        | NC              | DISP1_B3                        |

| GND                             | -               | 89        | 90        | -               | GND                             |

| DISP1_B4                        | NC              | 91        | 92        | NC              | DISP1_B6                        |

| DISP1_B5                        | NC              | 93        | 94        | NC              | DISP1_B7                        |

| GND                             | -               | 95        | 96        | -               | GND                             |

| DISP1_DCLK                      | NC              | 97        | 98        | R_P1_24         | DISP1_DCLKI                     |

| DISP1_DISP25                    | NC              | 99        | 100       | -               | GND                             |

| GND                             | -               | 101       | 102       | R_P1_25         | DISP1_TSIG6                     |

| DISP1_HSYNC                     | NC              | 103       | 104       | R_P1_26         | DISP1_TSIG7                     |

| DISP1_VSYNC                     | NC              | 105       | 106       | R_P1_27         | DISP1_TSIG8                     |

| DISP1_DE                        | NC              | 107       | 108       | R_P1_28         | DISP1_TSIG9                     |

| DISP1_TSIG3                     | R_P1_29         | 109       | 110       | R_P1_30         | DISP1_TSIG10                    |

| DISP1_TSIG4                     | R_P1_31         | 111       | 112       | R_P1_32         | DISP1_TSIG11                    |

| DISP1_TSIG5                     | R_P1_33         | 113       | 114       | -               | GND                             |

| GND                             | -               | 115       | 116       | R_P1_34         | P3V3_GPIO00                     |

| P3V3_GPIO03                     | R_P1_35         | 117       | 118       | R_P1_36         | P3V3_GPIO01                     |

| P3V3_GPIO04                     | R_P1_37         | 119       | 120       | R_P1_38         | P3V3_GPIO02                     |

| DISP0_R0                        | NC              | 121       | 122       | NC              | DISP0_R2                        |

| DISP0_R1                        | NC              | 123       | 124       | NC              | DISP0_R3                        |

| GND                             | -               | 125       | 126       | -               | GND                             |

| DISP0_R4                        | NC              | 127       | 128       | NC              | DISP0_R6                        |

| DISP0_R5                        | NC              | 129       | 130       | NC              | DISP0_R7                        |

| GND                             | -               | 131       | 132       | -               | GND                             |

| DISP0_G0                        | NC              | 133       | 134       | NC              | DISP0_G2                        |

| ADA-FCR4-MULTIIO-<br>001 Signal | MCU Port<br>Pin | J6<br>Pin | J6<br>Pin | MCU Port<br>Pin | ADA-FCR4-MULTIIO-<br>001 Signal |

|---------------------------------|-----------------|-----------|-----------|-----------------|---------------------------------|

| DISP0_G1                        | NC              | 135       | 136       | NC              | DISP0_G3                        |

| GND                             | -               | 137       | 138       | -               | GND                             |

| DISP0_G4                        | NC              | 139       | 140       | NC              | DISP0_G6                        |

| DISP0_G5                        | NC              | 141       | 142       | NC              | DISP0_G7                        |

| GND                             | -               | 143       | 144       | -               | GND                             |

| DISP0_B0                        | NC              | 145       | 146       | NC              | DISP0_B2                        |

| DISP0_B1                        | NC              | 147       | 148       | NC              | DISP0_B3                        |

| GND                             | -               | 149       | 150       | -               | GND                             |

| DISP0_B4                        | NC              | 151       | 152       | NC              | DISP0_B6                        |

| DISP0_B5                        | NC              | 153       | 154       | NC              | DISP0_B7                        |

| GND                             | -               | 155       | 156       | -               | GND                             |

| DISP0_DCLK                      | NC              | 157       | 158       | NC              | DISP0_DCLKI                     |

| DISP0_DISP25                    | NC              | 159       | 160       | -               | GND                             |

| GND                             | -               | 161       | 162       | -               | GND                             |

| DISP0_HSYNC                     | NC              | 163       | 164       | NC              | DISP0_TSIG6                     |

| DISP0_VSYNC                     | NC              | 165       | 166       | NC              | DISP0_TSIG7                     |

| DISP0_DE                        | NC              | 167       | 168       | NC              | DISP0_TSIG8                     |

| DISP0_TSIG3                     | R_P3_30         | 169       | 170       | NC              | DISP0_TSIG9                     |

| DISP0_TSIG4                     | R_P3_31         | 171       | 172       | NC              | DISP0_TSIG10                    |

| DISP0_TSIG5                     | NC              | 173       | 174       | NC              | DISP0_TSIG11                    |

| GND                             | -               | 175       | 176       | -               | GND                             |

| P_3V3                           | -               | 177       | 178       | -               | P_3V3                           |

| P_3V3                           | -               | 179       | 180       | -               | P_3V3                           |

Table 6-5: J6 signal assignment

Signals  $R_P^*$  are indirect connections. They come from the "output"-side of the Riser-Board, thus are not connected anywhere unless the Riser-Board connects them the corresponding MCU-port. The numbering used here is for a standard Riser-Board (MEM-FCR4-001) which connects all MCU-ports to the adjacent "output"  $R_P^*$ -signal without any crossover. For other Riser-Boards, some to all of the  $R_P^*$ -signals are not available (unconnected). Although possible, a Riser-Board should not pass an input-port from the MCU on a different  $R_P^*$ -signal.

## 6.2 IPC Connector (X8)

This is a standard 2\*20pin, 1.27mm pitch IDC-header.

| MCU Port | Signal    | Pin | Pin | Signal    | MCU Port |

|----------|-----------|-----|-----|-----------|----------|

| P1_5     | AIC0_TDA0 | 1   | 2   | AIC0_TDA1 | P1_4     |

| P1_0     | AIC0_CLK  | 3   | 4   | GND       |          |

|          | GND       | 5   | 6   | AIC0_RCLK | P1_1     |

| P1_2     | AIC0_RDA0 | 7   | 8   | AIC0_RDA1 | P1_3     |

|          | GND       | 9   | 10  | GND       |          |

| P1_7     | AIC1_TDA0 | 11  | 12  | AIC1_TDA1 | P1_6     |

| P1_20    | AIC1_CLK  | 13  | 14  | GND       |          |

|          | GND       | 15  | 16  | AIC1_RCLK | P1_21    |

| P1_22    | AIC1_RDA0 | 17  | 18  | AIC1_RDA1 | P1_23    |

|          | GND       | 19  | 20  | GND       |          |

| P1_8     | GPIO0     | 21  | 22  | GPIO1     | P1_9     |

| P1_10    | EXTINT0   | 23  | 24  | EXTINT1   | P1_11    |

| R_P3_16  | GPIO3     | 25  | 26  | GPIO4     | R_P3_14  |

|          | n.c.      | 27  | 28  | n.c.      |          |

|          | GND       | 29  | 30  | GND       |          |

| P1_15    | SPI0_CLK  | 31  | 32  | SPI0_TDI  | P1_14    |

| P1_13    | SPI0_TDO  | 33  | 34  | SPI0_CS   | P1_12    |

|          | GND       | 35  | 36  | GND       |          |

| P1_19    | SPI1_CLK  | 37  | 38  | SPI1_TDI  | P1_18    |

| P1_17    | SPI1_TDO  | 39  | 40  | SPI1_CS   | P1_16    |

Table 6-6: X8 signal assignment

All Signals are also available on the B2B connectors. However, a group of signals must not be used if they are used on the IPC-header. Signal-groups (AIC0/1, SPI0/1 and each single GPIO/EXTINT) can be disconnected from the IPC independently of each other by jumpers. For the single-pin functions (GPIOs and EXTINTs), there is a single jumper for each signal, while the peripheral-groups AIC and SPI have one jumper per group. The actual (dis)connection is done by voltage-limiting bus-switches. These allow the usage of the IPC (which is always 3.3V) even if P1 operates at 5.0V and introduce almost no extra delay. Observe that for 5.0V operation of the port while using 3.3V IPC, the input-cells of the MCU must be programmed for TTL-threshold.

## 6.3 Debug Connector (X2)

This is an ARM standard 20 pin JTAG connector.

| Pin | Signal | Description                             |

|-----|--------|-----------------------------------------|

| 1   | Vsns   | Target voltage reference                |

| 2   | VCCt   | Target power                            |

| 3   | nTRST  | JTAG TAP reset, active low              |

| 4   | GND    | Ground                                  |

| 5   | TDI    | JTAG Test Data In                       |