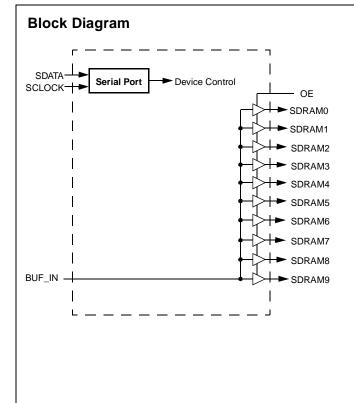

# SDRAM Buffer - 2 DIMM (Mobile)

### Features

- Ten skew-controlled CMOS outputs (SDRAM0:9)

- Supports two SDRAM DIMMs

- Ideal for high-performance systems designed around Intel®'s latest Mobile chip set

- I<sup>2</sup>C Serial configuration interface

- · Skew between any two outputs is less than 250 ps

- 1 to 5 ns propagation delay

- DC to 133-MHz operation

- Single 3.3V supply voltage

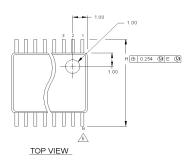

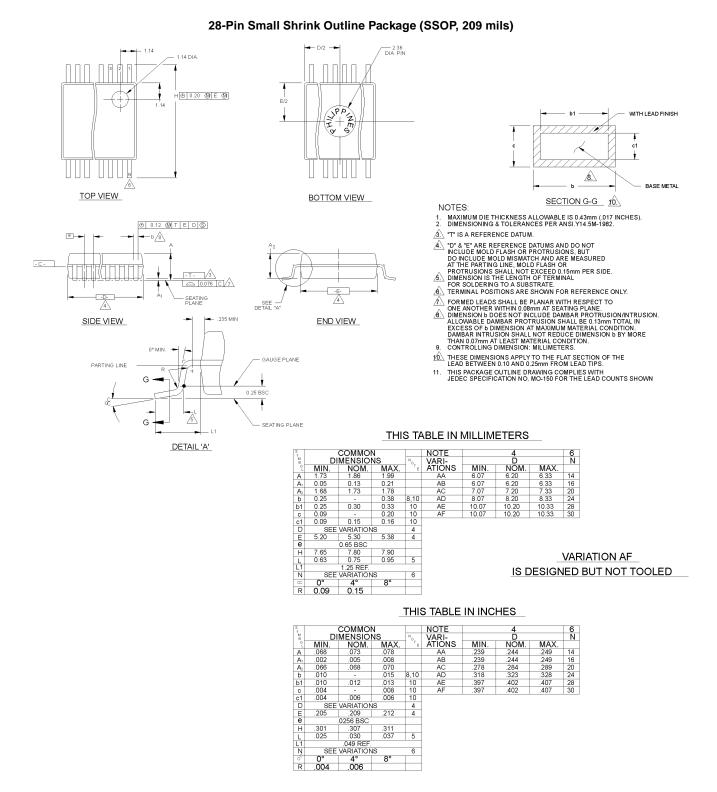

- Low power CMOS design packaged in a 28-pin, 209-mil SSOP (Shrink Small Outline Package)

### **Overview**

The Cypress W40S11-02 is a low-voltage, ten-output clock buffer. Output buffer impedance is approximately  $15\Omega$ , which is ideal for driving SDRAM DIMMs.

#### Intel is a registered trademark of Intel Corporation.

# Key Specifications

| Supply Voltages: $V_{DD} = 3.3V \pm 5\%$           |

|----------------------------------------------------|

| Operating Temperature:                             |

| Input Threshold: 1.5V typical                      |

| Maximum Input Voltage:V <sub>DD</sub> + 0.5V       |

| Input Frequency:0 to 133 MHz                       |

| BUF_IN to SDRAM0:9 Propagation Delay:1.0 to 5.0 ns |

| Output Edge Rate: ≥1.5 V/ns                        |

| Output Skew: ±250 ps                               |

| Output Duty Cycle: 45/55% worst case               |

| Output Impedance:                                  |

| Output Type: CMOS rail-to-rail                     |

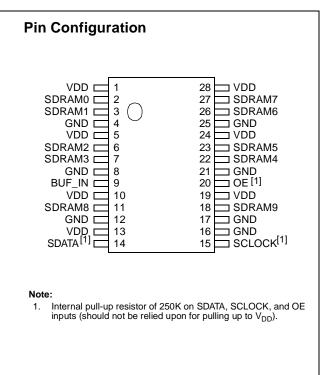

# **Pin Definitions**

| Pin Name | Pin<br>No.                               | Pin<br>Type | Pin Description                                                                                                                                                                                                |

|----------|------------------------------------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SDRAM0:9 | 2, 3, 6, 7,<br>22, 23, 26,<br>27, 11, 18 | 0           | <b>SDRAM Outputs:</b> Provides buffered copy of BUF_IN. The propagation delay from a rising input edge to a rising output edge is 1 to 5 ns. All outputs are skew controlled to within ± 250 ps of each other. |

| BUF_IN   | 9                                        | I           | Clock Input: This clock input has an input threshold voltage of 1.5V (typ).                                                                                                                                    |

| SDATA    | 14                                       | I/O         | <b><i>PC Data Input:</i></b> Data should be presented to this input as described in the I <sup>2</sup> C section of this data sheet. Internal 250-k $\Omega$ pull-up resistor.                                 |

| SCLOCK   | 15                                       | I           | <b><i>PC Clock Input:</i></b> The I <sup>2</sup> C Data clock should be presented to this input as described in the I <sup>2</sup> C section of this data sheet. Internal 250-k $\Omega$ pull-up resistor.     |

| VDD      | 1,5,10,13,<br>19,24,28                   | Р           | <b>Power Connection:</b> Power supply for core logic and output buffers. Connected to 3.3V supply.                                                                                                             |

| GND      | 4, 8, 12, 16,<br>17, 21, 25              | G           | Ground Connection: Connect all ground pins to the common system ground plane.                                                                                                                                  |

| OE       | 20                                       | I           | <b>Output Enable:</b> Internal 250-k $\Omega$ pull-up resistor. Three-states outputs when LOW.                                                                                                                 |

# **Functional Description**

### **Output Control Pins**

Outputs three-stated when OE = 0, and toggle when OE = 1. Outputs are in phase with BUF\_IN but are phase delayed by 1 to 5 ns. Outputs can also be controlled via the  $I^2C$  interface.

### Output Drivers

The W40S11-02 output buffers are CMOS type which deliver a rail-to-rail (GND to  $V_{DD}$ ) output voltage swing into a nominal capacitive load. Thus, output signaling is both TTL and CMOS level compatible. Nominal output buffer impedance is 15 ohms.

### Operation

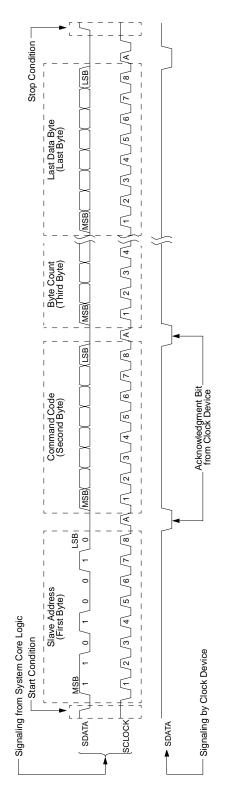

Data is written to the W40S11-02 in ten bytes of eight bits each. Bytes are written in the order shown in *Table 1*.

| Byte<br>Sequence | Byte Name       | Bit Sequence     | Byte Description                                                                                                                                                                                                                                                                                                                                                                                                                           |

|------------------|-----------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                | Slave Address   | 11010010         | Commands the W40S11-02 to accept the bits in Data Bytes 0–6 for in-<br>ternal register configuration. Since other devices may exist on the same<br>common serial data bus, it is necessary to have a specific slave address<br>for each potential receiver. The slave receiver address for the W40S11-02<br>is 11010010. Register setting will not be made if the Slave Address is not<br>correct (or is for an alternate slave receiver). |

| 2                | Command<br>Code | Don't Care       | Unused by the W40S11-02, therefore bit values are ignored (don't care).<br>This byte must be included in the data write sequence to maintain proper<br>byte allocation. The Command Code Byte is part of the standard serial<br>communication protocol and may be used when writing to another ad-<br>dressed slave receiver on the serial data bus.                                                                                       |

| 3                | Byte Count      | Don't Care       | Unused by the W40S11-02, therefore bit values are ignored (don't care).<br>This byte must be included in the data write sequence to maintain proper<br>byte allocation. The Byte Count Byte is part of the standard serial com-<br>munication protocol and may be used when writing to another addressed<br>slave receiver on the serial data bus.                                                                                         |

| 4                | Data Byte 0     | Refer to Table 2 | The data bits in these bytes set internal W40S11-23 registers that control                                                                                                                                                                                                                                                                                                                                                                 |

| 5                | Data Byte 1     |                  | device operation. The data bits are only accepted when the Address Byte bit sequence is 11010010, as noted above. For description of bit control                                                                                                                                                                                                                                                                                           |

| 6                | Data Byte 2     |                  | functions, refer to Table 2, Data Byte Serial Configuration Map.                                                                                                                                                                                                                                                                                                                                                                           |

| 7                | Data Byte 3     | Don't Care       | Refer to Cypress clock drivers.                                                                                                                                                                                                                                                                                                                                                                                                            |

| 8                | Data Byte 4     |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 9                | Data Byte 5     | ]                |                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 10               | Data Byte 6     |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                            |

#### Table 1. Byte Writing Sequence

### Writing Data Bytes

Each bit in the data bytes control a particular device function. Bits are written MSB (most significant bit) first, which is bit 7. *Table 2* gives the bit formats for registers located in Data Bytes 0–6.

|             | Affe       | cted Pin         |                             | Bit C | ontrol |

|-------------|------------|------------------|-----------------------------|-------|--------|

| Bit(s)      | Pin No.    | Pin Name         | Control Function            | 0     | 1      |

| Data Byte 0 | SDRAM Acti | ive/Inactive Reg | ister (1=Enable, 0=Disable) |       |        |

| 7           | N/A        | Reserved         | (Reserved)                  |       |        |

| 6           | N/A        | Reserved         | (Reserved)                  |       |        |

| 5           | N/A        | Reserved         | (Reserved)                  |       |        |

| 4           | N/A        | Reserved         | (Reserved)                  |       |        |

| 3           | 7          | SDRAM3           | Clock Output Disable        | Low   | Active |

| 2           | 6          | SDRAM2           | Clock Output Disable        | Low   | Active |

| 1           | 3          | SDRAM1           | Clock Output Disable        | Low   | Active |

| 0           | 2          | SDRAM0           | Clock Output Disable        | Low   | Active |

| Data Byte 1 | SDRAM Acti | ve/Inactive Reg  | ister (1=Enable, 0=Disable) | ·     | ·      |

| 7           | 27         | SDRAM7           | Clock Output Disable        | Low   | Active |

| 6           | 26         | SDRAM6           | Clock Output Disable        | Low   | Active |

| 5           | 23         | SDRAM5           | Clock Output Disable        | Low   | Active |

| 4           | 22         | SDRAM4           | Clock Output Disable        | Low   | Active |

| 3           | N/A        | Reserved         | (Reserved)                  |       |        |

| 2           | N/A        | Reserved         | (Reserved)                  |       |        |

| 1           | N/A        | Reserved         | (Reserved)                  |       |        |

| 0           | N/A        | Reserved         | (Reserved)                  |       |        |

| Data Byte 2 | SDRAM Acti | ve/Inactive Reg  | ister (1=Enable, 0=Disable) | -     | ·      |

| 7           | 18         | SDRAM9           | Clock Output Disable        | Low   | Active |

| 6           | 11         | SDRAM8           | Clock Output Disable        | Low   | Active |

| 5           | N/A        | Reserved         | (Reserved)                  |       |        |

| 4           | N/A        | Reserved         | (Reserved)                  |       |        |

| 3           | N/A        | Reserved         | (Reserved)                  |       |        |

| 2           | N/A        | Reserved         | (Reserved)                  |       |        |

| 1           | N/A        | Reserved         | (Reserved)                  |       |        |

| 0           | N/A        | Reserved         | (Reserved)                  |       |        |

Table 2. Data Bytes 0–2 Serial Configuration Map<sup>[2]</sup>

Note:

At power-up all SDRAM outputs are enabled and active. It is recommended to program Bits 4–7 of Byte0 and Bits 0–3 of Byte1 to a "0" to save power and reduce noise.

### How To Use the Serial Data Interface

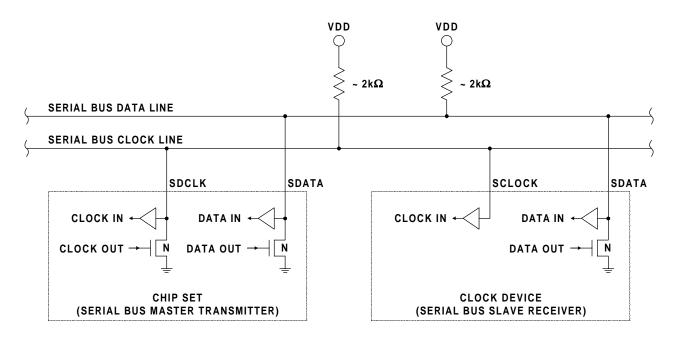

#### **Electrical Requirements**

*Figure 1* illustrates electrical characteristics for the serial interface bus used with the W40S11-02. Devices send data over the bus with an open drain logic output that can (a) pull the bus line LOW, or (b) let the bus default to logic 1. The pull-up resistor on the bus (both clock and data lines) establish a default logic 1. All bus devices generally have logic inputs to receive data.

Although the W40S11-02 is a receive-only device (no data write-back capability), it does transmit an "acknowledge" data pulse after each byte is received. Thus, the SDATA line can both transmit and receive data.

The pull-up resistor should be sized to meet the rise and fall times specified in AC parameters, taking into consideration total bus line capacitance.

Figure 1. Serial Interface Bus Electrical Characteristics

#### **Signaling Requirements**

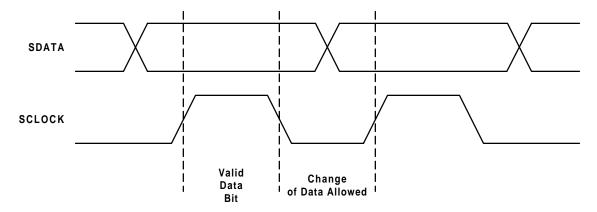

As shown in *Figure 2*, valid data bits are defined as stable logic 0 or 1 condition on the data line during a clock HIGH (logic 1) pulse. A transitioning data line during a clock HIGH pulse may be interpreted as a start or stop pulse (it will be interpreted as a start or stop pulse if the start/stop timing parameters are met).

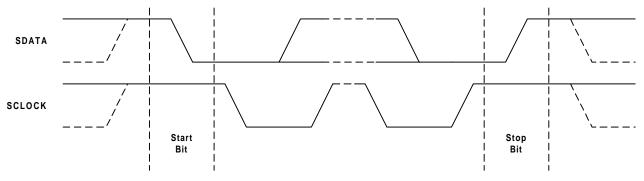

A write sequence is initiated by a "start bit" as shown in *Figure* 3. A "stop bit" signifies that a transmission has ended.

As stated previously, the W40S11-02 sends an "acknowledge" pulse after receiving eight data bits in each byte as shown in *Figure 4.*

#### Sending Data to the W40S11-02

The device accepts data once it has detected a valid start bit and address byte sequence. Device functionality is changed upon the receipt of each data bit (registers are not double buffered). Partial transmission is allowed meaning that a transmission can be truncated as soon as the desired data bits are transmitted (remaining registers will be unmodified). Transmission is truncated with either a stop bit or new start bit (restart condition).

Figure 2. Serial Data Bus Valid Data Bit

Figure 3. Serial Data Bus Start and Stop Bit

[+] Feedback

Figure 4. Serial Data Bus Write Sequence

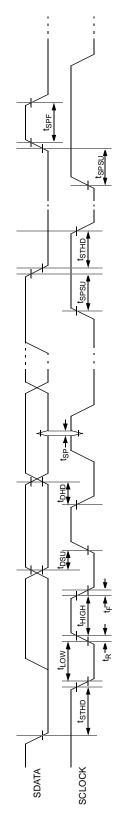

Figure 5. Serial Data Bus Timing Diagram

# **Absolute Maximum Ratings**

Stresses greater than those listed in this table may cause permanent damage to the device. These represent a stress rating only. Operation of the device at these or any other conditions above those specified in the operating sections of this specification is not implied. Maximum conditions for extended periods may affect reliability.

| Parameter                         | Description                            | Rating       | Unit |

|-----------------------------------|----------------------------------------|--------------|------|

| V <sub>DD</sub> , V <sub>IN</sub> | Voltage on any pin with respect to GND | -0.5 to +7.0 | V    |

| T <sub>STG</sub>                  | Storage Temperature                    | -65 to +150  | °C   |

| T <sub>A</sub>                    | Operating Temperature                  | 0 to +70     | °C   |

| Т <sub>В</sub>                    | Ambient Temperature under Bias         | -55 to +125  | °C   |

## **DC Electrical Characteristics:** $T_A = 0^{\circ}C$ to +70°C, $V_{DD} = 3.3V \pm 5\%$

| Parameter                | Description                           | Test Condition/Comments | Min                  | Тур | Мах                  | Unit |

|--------------------------|---------------------------------------|-------------------------|----------------------|-----|----------------------|------|

| I <sub>DD</sub>          | 3.3V Supply Current                   | at 66 MHz               |                      | 120 | 160                  | mA   |

| I <sub>DD</sub>          | 3.3V Supply Current                   | at 100 MHz              |                      | 185 | 220                  | mA   |

| I <sub>DD Tristate</sub> | 3.3V Supply Current in<br>Three-State |                         |                      | 5   | 10                   | mA   |

| Logic Inputs             |                                       | ·                       |                      |     |                      | •    |

| V <sub>IL</sub>          | Input Low Voltage                     |                         | V <sub>SS</sub> -0.3 |     | 0.8                  | V    |

| V <sub>IH</sub>          | Input High Voltage                    |                         | 2.0                  |     | V <sub>DD</sub> +0.5 | V    |

| I <sub>ILEAK</sub>       | Input Leakage Current, BUF_IN         |                         | -5                   |     | +5                   | μA   |

| I <sub>ILEAK</sub>       | Input Leakage Current <sup>[3]</sup>  |                         | -20                  |     | +5                   | μA   |

| Logic Outpu              | ts (SDRAM0:9) <sup>[4]</sup>          | ·                       |                      |     |                      | •    |

| V <sub>OL</sub>          | Output Low Voltage                    | I <sub>OL</sub> = 1 mA  |                      |     | 50                   | mV   |

| V <sub>OH</sub>          | Output High Voltage                   | I <sub>OH</sub> = -1 mA | 3.1                  |     |                      | V    |

| I <sub>OL</sub>          | Output Low Current                    | V <sub>OL</sub> = 1.5V  | 70                   | 110 | 185                  | mA   |

| I <sub>OH</sub>          | Output High Current                   | V <sub>OH</sub> = 1.5V  | 65                   | 100 | 160                  | mA   |

| Pin Capacita             | ince/Inductance                       |                         |                      |     |                      |      |

| C <sub>IN</sub>          | Input Pin Capacitance                 |                         |                      |     | 5                    | pF   |

| C <sub>OUT</sub>         | Output Pin Capacitance                |                         |                      |     | 6                    | pF   |

| L <sub>IN</sub>          | Input Pin Inductance                  |                         |                      |     | 7                    | nH   |

Note:

OE, SDATA, and SCLOCK logic pins have a 250-kΩ internal pull-up resistor (V<sub>DD</sub> – 0.8V).

All SDRAM outputs loaded by 6" transmission lines with 22-pF capacitors on ends.

# **AC Electrical Characteristics:** T<sub>A</sub> = 0°C to +70°C, V<sub>DD</sub> = 3.3V±5% (Lump Capacitance Test Load = 30 pF)

| Parameter        | Description                    | Test Condition             | Min | Тур | Max | Unit |

|------------------|--------------------------------|----------------------------|-----|-----|-----|------|

| f <sub>IN</sub>  | Input Frequency                |                            | 0   |     | 133 | MHz  |

| t <sub>R</sub>   | Output Rise Edge Rate          | Measured from 0.4V to 2.4V | 1.5 |     | 4.0 | V/ns |

| t <sub>F</sub>   | Output Fall Edge Rate          | Measured from 2.4V to 0.4V | 1.5 |     | 4.0 | V/ns |

| t <sub>SR</sub>  | Output Skew, Rising Edges      |                            |     |     | 250 | ps   |

| t <sub>SF</sub>  | Output Skew, Falling Edges     |                            |     |     | 250 | ps   |

| t <sub>EN</sub>  | Output Enable Time             |                            | 1.0 |     | 8.0 | ns   |

| t <sub>DIS</sub> | Output Disable Time            |                            | 1.0 |     | 8.0 | ns   |

| t <sub>PR</sub>  | Rising Edge Propagation Delay  |                            | 1.0 |     | 5.0 | ns   |

| t <sub>PF</sub>  | Falling Edge Propagation Delay |                            | 1.0 |     | 5.0 | ns   |

| t <sub>D</sub>   | Duty Cycle                     | Measured at 1.5V           | 45  |     | 55  | %    |

| Z <sub>o</sub>   | AC Output Impedance            |                            |     | 15  |     | Ω    |

# **Ordering Information**

| Ordering Code | Freq. Mask<br>Code | Package<br>Name | Package Type                                    |

|---------------|--------------------|-----------------|-------------------------------------------------|

| W40S11        | -02                | H<br>X          | 28-pin SSOP (209-mil)<br>28-pin TSSOP (173-mil) |

Document #: 38-00805

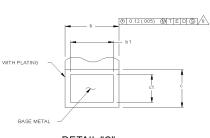

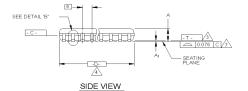

# **Package Diagrams**

### 28-Pin Shrink Small Outline Package (TSSOP, 173-mil)

DETAIL "C" (SEE NOTE 9)

END VIEW

#### NOTES:

- DIE THICKNESS ALLOWABLE IS 0.279±0.0127 (.0110±.0005 INCHES) DIMENSIONING & TOLERANCES PER ANSI.Y14.5M-1982. 2. DIMENSIONER ALLOYTAGLE IS U 279-0 0127 (0110) 0005 INC 2. DIMENSIONE & TOLERANCES PER ANSI Y 14 5M-1982. Magnetic transmission of the tran

- ▲ TERMINIAL POSITIONS ARE SHOWN FOR REFERENCE ONLY.

▲ FORME LADS SHALL BE LIVAIRA WITH RESPECT TO ONE ANOTHER WITHIN 0.076mm AT SEATING PLANE.

▲ THE LEAD WOTH DIMENSION DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.076mm TOTAL INTERCESSOF THE LEAD WOTH DIMENSION LOCATED ON THE LOWER RADIUS OR THE FOOT. NMININUM SPACE BED 14mm SEE DETAILS TE AND ADACENT LEAD TO DE 0.14mm SEE DETAILS TE AND CC 10 TO 0.25 MERCINIC SHOLD AN ADACENT LEAD TO TO 0.25 MERCINIC TO 10 TO 0.05 MERCINIC TO 10 TO 0.05 MENSION. MILLIMETERS 11. THIS PART IS COMPLANT WITH JEDEC SPECIFICATION MO-153. VARIATIONS AA, AB, AC, AD AND AE

DETAIL 'A'

DETAIL "B" (SCALE: 30/1) DAMBAR PROTRUSION

DETAIL "C"

### THIS TABLE IN MILLIMETERS

| S              |                | соммоі     | N     |                               | NOTE   |      | 4    |      | 6  |

|----------------|----------------|------------|-------|-------------------------------|--------|------|------|------|----|

| B              | DI             | DIMENSIONS |       |                               | VARI-  |      | D    |      | N  |

| °L             | MIN.           | NOM.       | MAX.  | <sup>N</sup> о <sub>т</sub> е | ATIONS | MIN. | NOM. | MAX. |    |

| A              |                |            | 1.10  |                               | AA     | 2.90 | 3.00 | 3.10 | 8  |

| A <sub>1</sub> | 0.05           | 0.10       | 0.15  |                               | AB     | 4.90 | 5.00 | 5.10 | 14 |

| A <sub>2</sub> | 0.85           | 0.90       | 0.95  |                               | AC     | 4.90 | 5.00 | 5.10 | 16 |

| b              | 0.19           | -          | 0.30  | 8                             | AD     | 6.40 | 6.50 | 6.60 | 20 |

| b1             | 0.19           | 0.22       | 0.25  |                               | AE     | 7.70 | 7.80 | 7.90 | 24 |

| С              | 0.090          | -          | 0.20  |                               | AF     | 9.60 | 9.70 | 9.80 | 28 |

| c1             | 0.090          | 0.127      | 0.135 |                               |        |      |      |      |    |

| D              | SEE            | VARIATION  | IS    | 4                             |        |      |      |      |    |

| E              | 4.30           | 4.40       | 4.50  | 4                             |        |      |      |      |    |

| е              |                | 0.65 BSC   |       |                               |        |      |      |      |    |

| H              | 6.25           | 6.40       | 6.50  |                               |        |      |      |      |    |

| L              | 0.50           | 0.60       | 0.70  | 5                             |        |      |      |      |    |

| N              | SEE VARIATIONS |            |       | 6                             |        |      |      |      |    |

| ő              | 0°             | 4°         | 8°    |                               |        |      |      |      |    |

### THIS TABLE IN INCHES

| S<br>Y         |                | соммоі     | N     |                               | NOTE   |      | 4    |      | 6  |

|----------------|----------------|------------|-------|-------------------------------|--------|------|------|------|----|

| B              | DI             | DIMENSIONS |       |                               | VARI-  |      | D    |      | N  |

| 1              | MIN.           | NOM.       | MAX.  | <sup>N</sup> о <sub>т</sub> е | ATIONS | MIN. | NOM. | MAX. |    |

| A              |                |            | .0433 |                               | AA     | .114 | .118 | .122 | 8  |

| A <sub>1</sub> | .002           | .004       | .006  |                               | AB     | .193 | .197 | .201 | 14 |

| A2             | .0335          | .0354      | .0374 |                               | AC     | .193 | .197 | .201 | 16 |

| b              | .0075          | -          | .0118 | 8                             | AD     | .252 | .256 | .260 | 20 |

| b1             | .0075          | .0087      | .0098 |                               | AE     | .303 | .307 | .311 | 24 |

| С              | .0035          | -          | .0079 |                               | AF     | .378 | .382 | .386 | 28 |

| c1             | .0035          | .0050      | .0053 |                               |        |      |      |      |    |

| D              | SEE            | VARIATION  | IS    | 4                             |        |      |      |      |    |

| E              | .169           | .173       | .177  | 4                             |        |      |      |      |    |

| e              |                | .0256 BSC  |       |                               |        |      |      |      |    |

| H              | .246           | .252       | .256  |                               |        |      |      |      |    |

| L              | .020           | .024       | .028  | 5                             |        |      |      |      |    |

| N              | SEE VARIATIONS |            |       | 6                             |        |      |      |      |    |

| ŭ              | 0°             | 4°         | 8°    |                               |        |      |      |      |    |

\*VARIATION AF IS DESIGNED BUT NOT TOOLED\*

# Package Diagrams (continued)

© Cypress Semiconductor Corporation, 1999. The information contained herein is subject to change without notice. Cypress Semiconductor Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in a Cypress Semiconductor product. Nor does it convey or imply any license under patent or other rights. Cypress Semiconductor does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress Semiconductor products in life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress Semiconductor against all charges.