# Power Management IC for Circuit Breaker Applications

Data Sheet ADP2450

#### **FEATURES**

**Boost shunt controller**

Adjustable output voltage range: 4.5 V to 36 V Integrated boost shunt driver

Programmable power detection threshold

**Buck regulator**

Input voltage range: 4.5 V to 36 V Continuous output current: 500 mA

Adjustable output voltage down to 0.6 V

Fixed output options: 3.3 V and 5 V

1.2 MHz fixed switching frequency

Voltage monitoring and open-drain reset output

4 programmable gain amplifiers

Low power consumption

Programmable gain and output dc common voltage

Low offset operation amplifier for leakage and grounding fault current detection

Analog trip circuit with programmable trip threshold Actuator driver output

#### **APPLICATIONS**

Low voltage circuit breaker CT powered supply

#### **GENERAL DESCRIPTION**

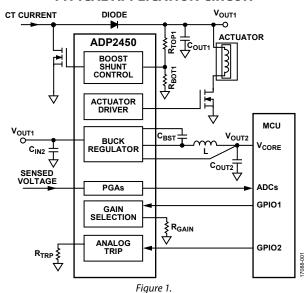

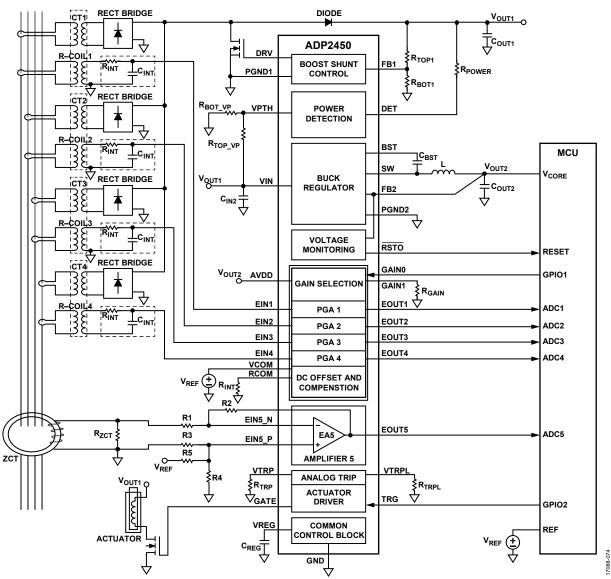

The ADP2450 integrates one boost shunt controller with power detection, one high efficiency buck regulator, four low offset, low power consumption programmable gain amplifiers (PGAs), one low offset operation amplifier, a fast analog trip circuit, and an actuator driver. The ADP2450 is targeted for low voltage circuit breakers, such as the molded case circuit breaker (MCCB), and current transformer (CT) powered supply applications.

The boost output voltage can be up to 36 V and integrates a power detection circuit that prevents the circuit from power hiccups. The power detection threshold is programmable with resistors.

The buck regulator operates over a wide input voltage range of 4.5 V to 36 V, and the output voltage can be adjusted down to 0.6 V. The buck regulator provides output currents of up to 500 mA. The buck regulator works in pulse-width modulation (PWM) mode with a fixed 1.2 MHz switching frequency, providing low output ripple voltage to the system.

The output voltage of the buck regulator is monitored by the supervisory circuit. When the output voltage is below the monitoring threshold, 88% of  $V_{\text{FB2}}$  (FB2 regulation voltage), the

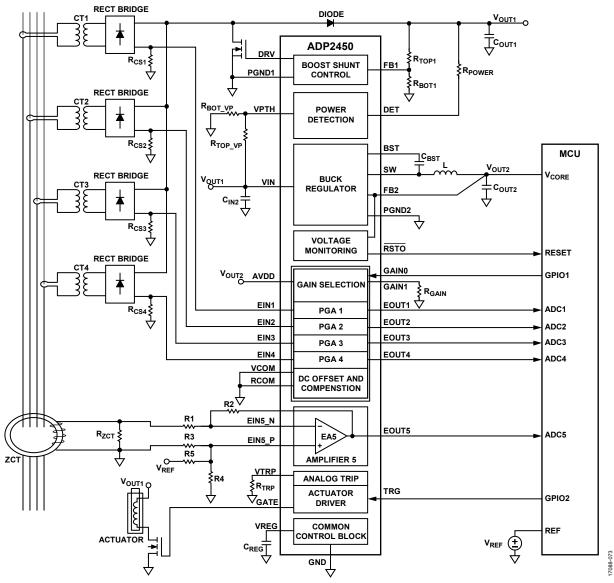

#### TYPICAL APPLICATION CIRCUIT

reset signal is pulled low and can be used to reset the microprocessor. The monitoring supervisory circuit makes the system more reliable.

The ADP2450 integrates four low offset, low power consumption amplifiers. With the programmable gain features, the ADP2450 provides accuracy measurement over a wide current input range based on the CT turn ratio.

A low offset operation amplifier is integrated in the ADP2450 for leakage current detection.

The ADP2450 also integrates an analog trip circuit, which provides fast trip response and enhances system reliability.

Additional protection includes buck overcurrent protection (OCP) and system thermal shutdown (TSD).

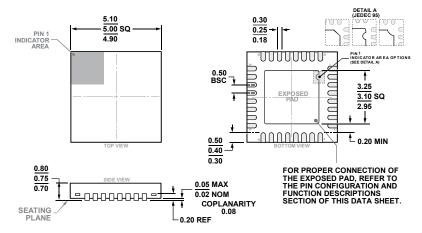

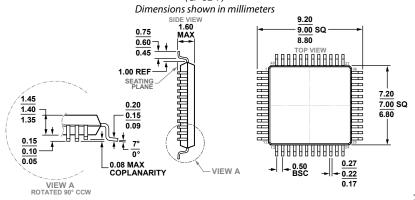

The ADP2450 operates over the  $-40^{\circ}$ C to  $+125^{\circ}$ C junction temperature range and is available in either a 32-lead LFCSP package or a 48-lead LQFP package.

Rev. B

Document Feedback

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 ©2018–2019 Analog Devices, Inc. All rights reserved.

Technical Support www.analog.com

## **TABLE OF CONTENTS**

| Features 1                                                   | External MOSFET for Boost Shunt Controller                 | 27 |

|--------------------------------------------------------------|------------------------------------------------------------|----|

| Applications1                                                | Boost Shunt Diode Selection                                | 27 |

| Typical Application Circuit                                  | Input Capacitor of Buck Regulator                          | 27 |

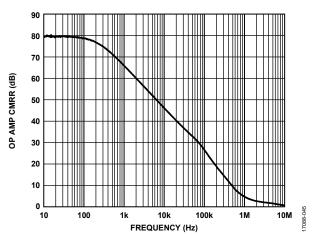

| General Description1                                         | Inductor Selection                                         | 27 |

| Revision History 2                                           | Output Capacitor of Buck Regulator                         | 28 |

| Functional Block Diagram4                                    | Output Voltage Setting                                     | 28 |

| Specifications5                                              | External MOSFET for Actuator                               | 29 |

| Boost Shunt Controller and Power Detection Specifications. 5 | Design Example                                             |    |

| Buck Regulator Specifications                                | Boost Shunt Output Voltage Setting                         |    |

| Programmable Gain Amplifier and Analog Trip                  | Boost Shunt Output Capacitor Setting                       |    |

| Specifications6                                              | Boost Shunt MOSFET Setting                                 |    |

| Operation Amplifier Specifications8                          | Boost Shunt Diode Setting                                  |    |

| Absolute Maximum Ratings9                                    | Buck Regulator Output Voltage Setting                      |    |

| Thermal Resistance9                                          | Inductor Setting                                           |    |

| ESD Caution 9                                                | Buck Regulator Output Capacitor Setting                    |    |

| Pin Configurations and Function Descriptions 10              | VPTH Resistor Divider Setting                              |    |

| Typical Performance Characteristics                          | -                                                          |    |

| 71 Theory of Operation22                                     | Dummy Load Resistor Setting<br>PGA Gain Setting            |    |

| Boost Shunt Controller                                       | -                                                          |    |

| Power Detection                                              | Sense Resistor Setting                                     |    |

| Internal Regulator                                           | Analog Trip Threshold Setting                              |    |

| Buck Regulator                                               | Actuator MOSFET Setting                                    |    |

| Bootstrap Circuit                                            | Circuit Board Layout Recommendations                       |    |

| Power Monitor and Reset                                      | Ground Planes                                              |    |

|                                                              | Switch Node                                                |    |

| Programmable Gain Amplifier                                  | Feedback Paths                                             | 33 |

| Operational Amplifier                                        | Power Traces                                               |    |

| Analog Trip Protection                                       | Signal Paths                                               | 33 |

| Actuator Driver                                              | Gate Driver Paths                                          | 33 |

| Thermal Shutdown                                             | Typical Application Circuits                               | 35 |

| Applications Information                                     | Factory-Programmable Options                               | 37 |

| Output Capacitor of Boost Shunt Controller26                 | Outline Dimensions                                         | 38 |

| Bridge Rectifier                                             | Ordering Guide                                             | 39 |

| Sense Resistor Selection                                     |                                                            |    |

| REVISION HISTORY                                             |                                                            |    |

| 7/2019—Rev. A to Rev. B                                      | Changes to Switch Node Parameter, Valley Current Limit     | t  |

| Changes to Ordering Guide                                    | Parameter, and Reset Threshold Hysteresis Parameter, Table |    |

| 4/2019—Rev. 0 to Rev. A                                      | Change to Gain Drift Parameter, Table 3                    |    |

| Added 48-lead LQFPUniversal                                  | Analog Trip, VTRPL Current Parameter, Table 3; Renum       |    |

| Change to General Description Section                        | Sequentially                                               |    |

| Change to Figure 24                                          | Change to Input Offset Parameter, Table 4                  |    |

| Change to DET Output Low Voltage Parameter, Table 1 5        | Changes to Table 5 and Table 6                             |    |

|                                                              |                                                            |    |

| Added Figure 4; Renumbered Sequentially                 | 10 |

|---------------------------------------------------------|----|

| Changes to Table 7                                      | 10 |

| Changes to Typical Performance Characteristics Section, |    |

| Figure 6, and Figure 9                                  | 12 |

| Change to Figure 13                                     | 13 |

| Change to Figure 18 and Figure 21                       | 14 |

| Replaced Figure 23                                      | 15 |

| Changes to Theory of Operation Section and Power        |    |

| Detection Section                                       | 22 |

| Changes to Analog Trip Protection Section and Figure 68 | 24 |

| Added Endnote 1 and Endnote 2 to Table 13               |    |

| Changes to Boost Shunt Controller Output Voltage Section     |     |

|--------------------------------------------------------------|-----|

| and Buck Regulator Output Voltage Section                    | .28 |

| Changes to VPTH Resistor Divider Section, Dummy Load         |     |

| Resistor Setting Section, and Sense Resistor Setting Section | .31 |

| Changes to Circuit Board Layout Recommendations Section      | .33 |

| Changes to Figure 75                                         | .36 |

| Updated Outline Dimensions                                   | .38 |

| Changes to Ordering Guide                                    | .38 |

9/2018—Revision 0: Initial Version

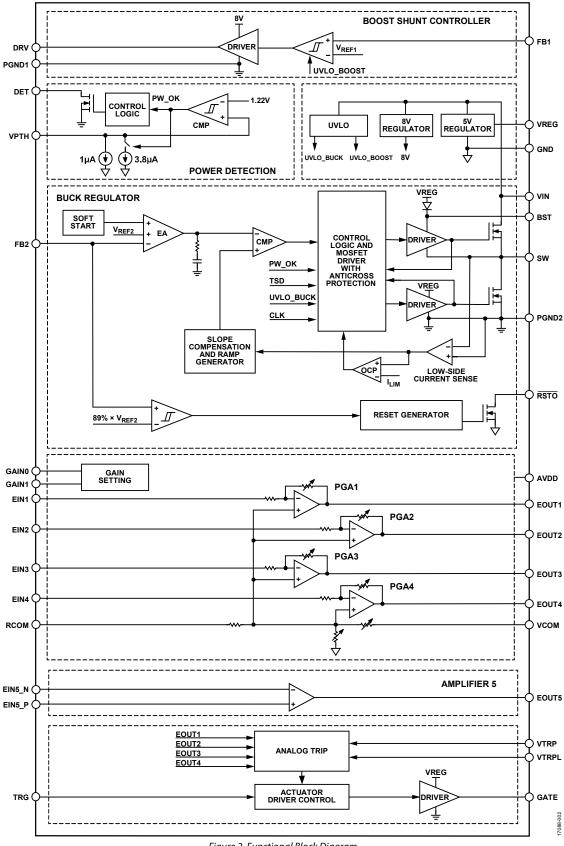

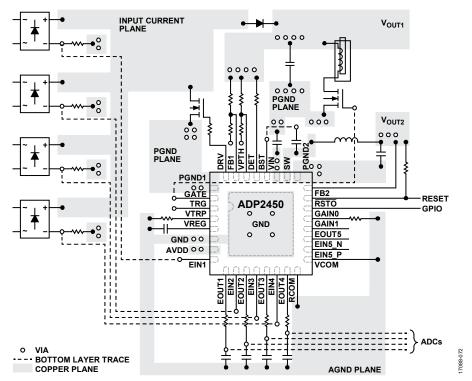

## **FUNCTIONAL BLOCK DIAGRAM**

Figure 2. Functional Block Diagram

Rev. B | Page 4 of 40

## **SPECIFICATIONS**

## **BOOST SHUNT CONTROLLER AND POWER DETECTION SPECIFICATIONS**

$V_{\rm IN} = 12 \; V, T_{\rm J} = -40 ^{\circ} C \; to \; +125 ^{\circ} C \; for \; minimum \; and \; maximum \; specifications, \; and \; T_{\rm A} = 25 ^{\circ} C \; for \; typical \; specifications, \; unless \; otherwise \; noted.$

Table 1.

| Parameter                                          | Symbol               | Test Conditions/Comments                                          | Min   | Тур  | Max   | Unit |

|----------------------------------------------------|----------------------|-------------------------------------------------------------------|-------|------|-------|------|

| POWER INPUT                                        |                      | VIN pin                                                           |       |      |       |      |

| Input Voltage Range                                | V <sub>IN</sub>      |                                                                   | 4.5   |      | 36    | ٧    |

| Quiescent Current <sup>1</sup>                     | $I_{Q\_VIN}$         | $V_{IN} = 12 \text{ V}$ , FB1 = GND, FB2 = 0.65 V, no switching   |       | 1.35 |       | mA   |

| Undervoltage Lockout Threshold (UVLO) <sup>2</sup> |                      |                                                                   |       |      |       |      |

| VIN Rising                                         |                      |                                                                   |       | 2.5  | 2.7   | ٧    |

| VIN Falling                                        |                      |                                                                   | 2.2   | 2.4  |       | ٧    |

| FEEDBACK (FB1)                                     |                      |                                                                   |       |      |       |      |

| FB1 Regulation Voltage                             | $V_{FB1}$            | Falling                                                           | 1.182 | 1.2  | 1.218 | ٧    |

| FB1 Hysteresis                                     |                      |                                                                   |       | 19   |       | mV   |

| FB1 Bias Current                                   | I <sub>FB1</sub>     |                                                                   |       | 0.01 | 0.1   | μΑ   |

| Hysteresis Comparator Response Time                |                      |                                                                   |       | 100  |       | ns   |

| BOOST SHUNT DRIVER (DRV)                           |                      |                                                                   |       |      |       |      |

| Rising Time <sup>3</sup>                           |                      | $C_{DRV} = 2.2 \text{ nF, from } 0.8 \text{ V to } 7.2 \text{ V}$ |       | 80   |       | ns   |

| Falling Time <sup>3</sup>                          |                      | $C_{DRV} = 2.2 \text{ nF, from } 7.2 \text{ V to } 0.8 \text{ V}$ |       | 35   |       | ns   |

| Sourcing Resistor                                  |                      |                                                                   |       | 4    |       | Ω    |

| Sinking Resistor                                   |                      |                                                                   |       | 2    |       | Ω    |

| Peak Source Current <sup>4</sup>                   |                      |                                                                   |       | 1    |       | Α    |

| Sink Source Current⁴                               |                      |                                                                   |       | 1    |       | Α    |

| DRV Output High Voltage                            | $V_{DRV\_H}$         |                                                                   | 7.6   | 8    | 8.4   | ٧    |

| INTERNAL REGULATOR (VREG)                          |                      |                                                                   |       |      |       |      |

| VREG Voltage                                       | $V_{VREG}$           | $I_{VREG} = 5 \text{ mA}$                                         | 4.7   | 5    | 5.3   | V    |

| Dropout Voltage                                    |                      | $I_{VREG} = 5 \text{ mA}$                                         |       | 27   |       | mV   |

| Regulator Current Limit                            |                      |                                                                   |       | 200  |       | mA   |

| POWER DETECTION                                    |                      |                                                                   |       |      |       |      |

| VPTH Rising Threshold                              | V <sub>PTH R</sub>   |                                                                   |       | 1.22 | 1.25  | ٧    |

| VPTH Falling Threshold                             | V <sub>PTH_F</sub>   |                                                                   | 1.05  | 1.09 |       | ٧    |

| VPTH Source Current                                |                      | VPTH voltage < 1.09 V                                             |       | 4.8  |       | μΑ   |

|                                                    |                      | VPTH voltage > 1.22 V                                             |       | 1    |       | μΑ   |

| Power Detection Deglitch Time                      |                      | _                                                                 |       | 10   |       | μs   |

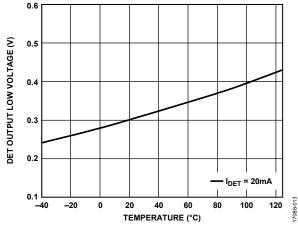

| DET Output Low Voltage                             |                      | I <sub>DET</sub> = 20 mA                                          |       | 0.3  | 0.55  | ٧    |

| Maximum Sink Current on DET                        | I <sub>DET_MAX</sub> |                                                                   |       | 100  |       | mA   |

| ACTUATOR DRIVER (TRG AND GATE)                     |                      |                                                                   |       |      |       |      |

| Input High Voltage                                 |                      | TRG pin                                                           | 1.2   |      |       | ٧    |

| Input Low Voltage                                  |                      | TRG pin                                                           |       |      | 0.4   | ٧    |

| Deglitch Time                                      |                      | TRG pin                                                           |       | 30   |       | μs   |

| GATE Maximum Source Current                        |                      | GATE pin                                                          |       | 85   |       | mA   |

| GATE Driver Output Voltage                         |                      | GATE pin                                                          |       | 5    |       | V    |

| THERMAL                                            |                      |                                                                   |       |      |       |      |

| Thermal Shutdown Threshold⁴                        |                      |                                                                   |       | 150  |       | °C   |

|                                                    | 1                    | II                                                                |       |      |       | °C   |

<sup>&</sup>lt;sup>1</sup> This current is measured from the VIN pin.

<sup>2</sup> This UVLO threshold is only for the boost control block.

<sup>&</sup>lt;sup>3</sup> Bench measurement result.

<sup>&</sup>lt;sup>4</sup> Guaranteed by design, not production tested.

#### **BUCK REGULATOR SPECIFICATIONS**

$V_{\rm IN}$  = 12 V,  $T_{\rm J}$  = -40°C to +125°C for minimum and maximum specifications, and  $T_{\rm A}$  = 25°C for typical specifications, unless otherwise noted.

Table 2.

| Parameter                                    | Symbol                    | <b>Test Conditions/Comments</b> | Min   | Тур  | Max   | Unit |

|----------------------------------------------|---------------------------|---------------------------------|-------|------|-------|------|

| POWER INPUT                                  |                           | VIN pin                         |       |      |       |      |

| Undervoltage Lockout Threshold <sup>1</sup>  |                           |                                 |       |      |       |      |

| VIN Rising                                   |                           |                                 |       | 4.2  | 4.4   | ٧    |

| VIN Falling                                  |                           |                                 | 3.5   | 3.65 |       | ٧    |

| FEEDBACK (FB2)                               |                           |                                 |       |      |       |      |

| FB2 Regulation Voltage                       | V <sub>FB2</sub>          | Adjustable output version       | 0.591 | 0.6  | 0.609 | ٧    |

| Fixed Output Accuracy                        |                           | Fixed output version            | -1.5  |      | +1.5  | %    |

| FB2 Bias Current                             | I <sub>FB2</sub>          | Adjustable output version       |       | 0.01 | 0.1   | μΑ   |

|                                              |                           | Fixed output version            |       | 4.3  | 5     | μΑ   |

| SWITCH NODE                                  |                           |                                 |       |      |       |      |

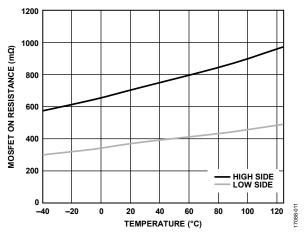

| High-Side On Resistance (LFCSP) <sup>2</sup> | R <sub>DSON_H_LFCSP</sub> | $I_{SW\_SOURCE} = 0.5 A$        |       | 700  | 1070  | mΩ   |

| Low-Side On Resistance (LFCSP) <sup>2</sup>  | R <sub>DSON_L_LFCSP</sub> | $I_{SW\_SINK} = 0.5 A$          |       | 380  | 540   | mΩ   |

| High-Side On Resistance (LQFP) <sup>2</sup>  | R <sub>DSON_H_LQFP</sub>  |                                 |       | 750  | 1210  | mΩ   |

| Low-Side On Resistance (LQFP) <sup>2</sup>   | R <sub>DSON_L_LQFP</sub>  |                                 |       | 430  | 620   | mΩ   |

| SW Leakage Current                           | I <sub>SW_LK_HS</sub>     | SW = PGND2                      |       | 0.1  |       | μΑ   |

|                                              | Isw_lk_ls                 | $SW = V_{IN}$                   |       | 42   |       | μΑ   |

| Minimum On Time                              | t <sub>ON_MIN</sub>       |                                 |       | 42   |       | ns   |

| Minimum Off Time                             | toff_min                  |                                 |       | 150  |       | ns   |

| BST                                          |                           |                                 |       |      |       |      |

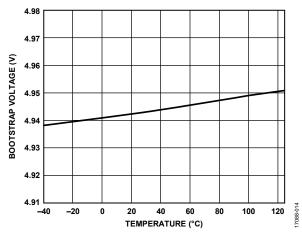

| Bootstrap Voltage                            | V <sub>BOOT</sub>         |                                 | 4.7   | 5    | 5.3   | ٧    |

| CURRENT LIMIT                                |                           |                                 |       |      |       |      |

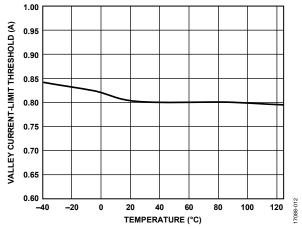

| Valley Current Limit                         |                           |                                 | 0.65  | 8.0  | 0.98  | Α    |

| Low-Side Sink Current Limit                  |                           |                                 |       | 0.2  |       | Α    |

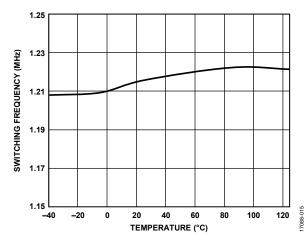

| PWM SWITCHING FREQUENCY                      | f <sub>sw</sub>           |                                 | 1.0   | 1.2  | 1.4   | MHz  |

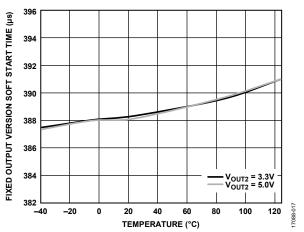

| SOFT START TIME                              | t <sub>SS</sub>           | Fixed output version            |       | 400  |       | μs   |

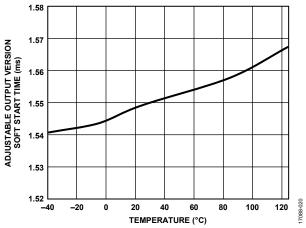

|                                              |                           | Adjustable output version       |       | 1.6  |       | ms   |

| RESET (RSTO)                                 |                           |                                 |       |      |       |      |

| Reset Rising Threshold Voltage               |                           | Refer to V <sub>FB2</sub>       | 85    | 89   | 94    | %    |

| Reset Threshold Hysteresis                   |                           |                                 |       | 1    |       | %    |

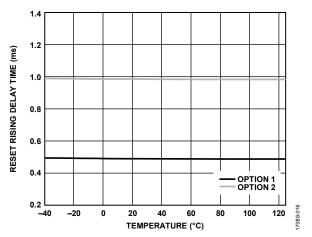

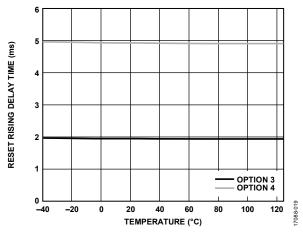

| Reset Rising Delay                           | trst_delay_r              | Option 1, default               | 0.42  | 0.5  | 0.56  | ms   |

| - ,                                          |                           | Option 2                        | 0.85  | 1    | 1.12  | ms   |

|                                              |                           | Option 3                        | 1.72  | 2    | 2.3   | ms   |

|                                              |                           | Option 4                        | 4.2   | 5    | 5.6   | ms   |

| Reset Falling Delay                          | trst_delay_f              |                                 |       | 10   |       | μs   |

| RSTO Output Low Voltage                      |                           | I <sub>RSTO</sub> = 3 mA        |       | 40   | 100   | mV   |

| RSTO Leakage Current                         |                           | $V_{RSTO} = 5 V$                |       | 0.01 | 0.3   | μΑ   |

$<sup>^{\</sup>mbox{\tiny $1$}}$  This UVLO threshold is only for the buck control block.

#### PROGRAMMABLE GAIN AMPLIFIER AND ANALOG TRIP SPECIFICATIONS

$V_{IN}$  = 12 V,  $V_{AVDD}$  = 5 V,  $T_J$  = -40°C to +125°C for minimum and maximum specifications, and  $T_A$  = 25°C for typical specifications, unless otherwise noted.

Table 3.

| Parameter                      | Symbol              | Test Conditions/Comments | Min | Тур | Max | Unit |

|--------------------------------|---------------------|--------------------------|-----|-----|-----|------|

| POWER INPUT                    |                     | AVDD pin                 |     |     |     |      |

| Input Voltage Range            | $V_{\text{AVDD}}$   |                          | 2.7 |     | 5.5 | V    |

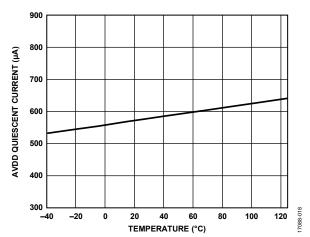

| Quiescent Current              | I <sub>Q_AVDD</sub> |                          |     | 575 |     | μΑ   |

| Undervoltage Lockout Threshold |                     |                          |     |     |     |      |

<sup>&</sup>lt;sup>2</sup> Pin to pin measurement.

| Parameter                                | Symbol                 | Test Conditions/Comments                                                   | Min                       | Тур                               | Max   | Unit    |

|------------------------------------------|------------------------|----------------------------------------------------------------------------|---------------------------|-----------------------------------|-------|---------|

| AVDD Rising                              |                        |                                                                            |                           | 2.6                               | 2.7   | V       |

| AVDD Falling                             |                        |                                                                            | 2.4                       | 2.5                               |       | V       |

| INPUT CHARACTERISTICS                    |                        |                                                                            |                           |                                   |       |         |

| Input Voltage Range                      |                        | $V_{VCOM} = GND$                                                           | -6.6                      |                                   | 0     | V       |

|                                          |                        | $V_{VCOM} = V_{AVDD}$                                                      | -3.3                      |                                   | +3.3  | V       |

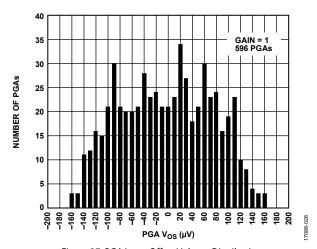

| Input Offset                             | $V_{OS\_PGA}$          | $T_J = 25$ °C, trimmed at gain = 1                                         |                           |                                   | 0.5   | mV      |

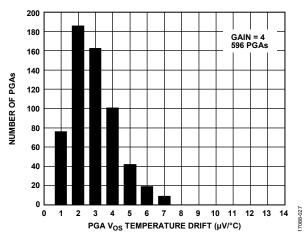

| Input Offset Temperature Drift           |                        | Gain < 4                                                                   |                           | 5.5                               | 17    | μV/°C   |

|                                          |                        | Gain ≥ 4                                                                   |                           | 3.5                               | 9.5   | μV/°C   |

| Input Capacitance <sup>1</sup>           | C <sub>IN_PGA</sub>    |                                                                            |                           | 2                                 |       | рF      |

| Input Impedance                          | R <sub>IN_PGA</sub>    |                                                                            |                           | 1                                 |       | ΜΩ      |

| OUTPUT CHARACTERISTICS                   |                        |                                                                            |                           |                                   |       |         |

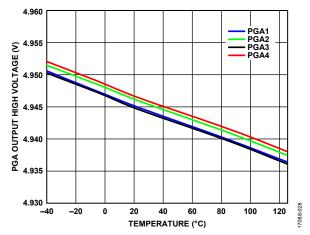

| Output Voltage High                      | $V_{OH\_PGA}$          | $I_{OH\_PGA} = -250 \mu\text{A}$                                           | V <sub>AVDD</sub> – 0.3 V | $V_{\text{AVDD}} - 0.1 \text{ V}$ |       | V       |

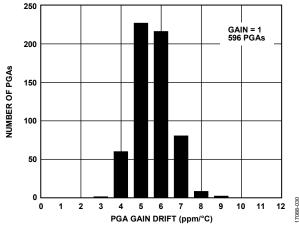

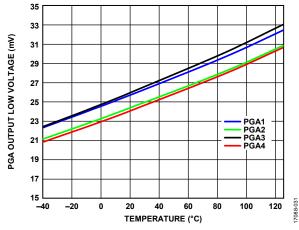

| Output Voltage Low                       | $V_{OL\_PGA}$          | $I_{OL\_PGA} = 250 \mu\text{A}$                                            |                           | 25                                | 40    | mV      |

| Short-Circuit Current                    | I <sub>SC_H_PGA</sub>  | Short to AVDD                                                              |                           | 17                                |       | mA      |

|                                          | I <sub>SC_L_PGA</sub>  | Short to GND                                                               |                           | 10                                |       | mA      |

| Close-Loop Output Impedance <sup>2</sup> | Z <sub>OUT_PGA</sub>   | f = 100 Hz, gain = 1                                                       |                           | 18                                |       | Ω       |

| DYNAMIC PERFORMANCE                      |                        |                                                                            |                           |                                   |       |         |

| Slew Rate <sup>2</sup>                   | SR <sub>PGA</sub>      | $R_{L\_PGA} = 10 \text{ k}\Omega$ , $C_{L\_PGA} = 35 \text{ pF, gain} = 1$ |                           | 1.7                               |       | V/µs    |

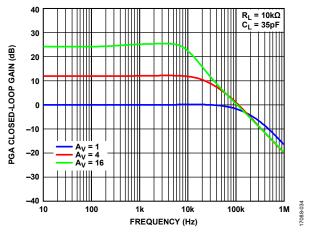

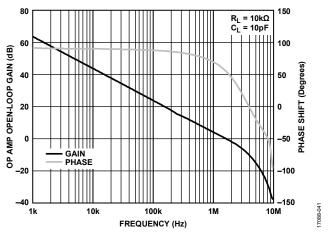

| Gain Bandwidth Product <sup>1</sup>      | $GBP_{PGA}$            | $R_{L\_PGA} = 10 \text{ k}\Omega$ , $C_{L\_PGA} = 35 \text{ pF}$           |                           | 1                                 |       | MHz     |

| Phase Margin <sup>1</sup>                | $\Phi_{M\_PGA}$        | $R_{L\_PGA} = 10 \text{ k}\Omega$ , $C_{L\_PGA} = 35 \text{ pF}$           |                           | 60                                |       | Degrees |

| NOISE PERFORMANCE                        | <u> </u>               |                                                                            |                           |                                   |       |         |

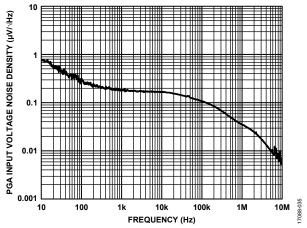

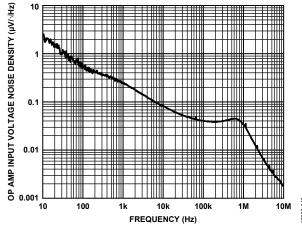

| Input Voltage Noise Density <sup>2</sup> | <b>e</b> ni PGA        | f = 1 kHz, gain = 1                                                        |                           | 180                               |       | nV/√Hz  |

| Input Voltage Noise <sup>2</sup>         | e <sub>n_PGA</sub> p-p | f = 0.1 Hz to 10 Hz, gain = 1                                              |                           | 34                                |       | μV p-p  |

| GAIN PROGRAM (GAIN0, GAIN1)              |                        |                                                                            |                           |                                   |       |         |

| Input High Voltage                       |                        | For GAIN0 pin                                                              | 1.2                       |                                   |       | V       |

| Input Low Voltage                        |                        | For GAIN0 pin                                                              |                           |                                   | 0.4   | V       |

| Voltage on GAIN1                         |                        | ·                                                                          | 0.792                     | 0.8                               | 0.808 | V       |

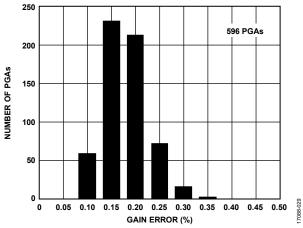

| Gain Error                               |                        | T₁=25 °C                                                                   |                           |                                   | 0.5   | %       |

| Gain Drift                               |                        | Gain < 4                                                                   |                           | 7                                 | 12    | ppm/°C  |

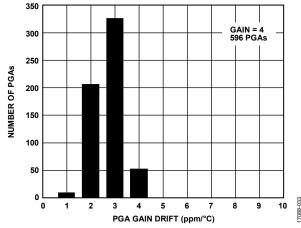

|                                          |                        | Gain ≥ 4                                                                   |                           | 4                                 | 8.5   | ppm/°C  |

| ANALOGTRIP                               | 1                      |                                                                            |                           |                                   |       | 1       |

| Analog Trip Disable Voltage Threshold    | $V_{TRP\_DIS}$         |                                                                            |                           |                                   |       |         |

| Rising                                   |                        |                                                                            |                           | 4.75                              |       | V       |

| Falling                                  |                        |                                                                            |                           | 4.65                              |       | ٧       |

| VTRP Current                             | I <sub>TRP</sub>       |                                                                            | 9.5                       | 10                                | 10.4  | μΑ      |

| VTRPL Current <sup>3</sup>               | I <sub>TRPL</sub>      |                                                                            | 9.5                       | 10                                | 10.4  | μΑ      |

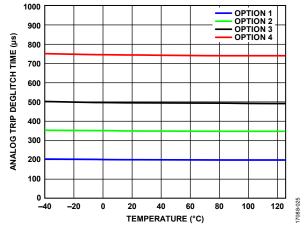

| Analog Trip Deglitch Time                | t <sub>TRP</sub>       | Option 1 (default)                                                         | 178                       | 200                               | 223   | μs      |

| 3 , 3                                    |                        | Option 2                                                                   | 310                       | 350                               | 387   | μs      |

|                                          |                        | Option 3                                                                   | 440                       | 500                               | 552   | μs      |

|                                          |                        | Option 4                                                                   | 660                       | 750                               | 826   | μs      |

|                                          |                        | Option 5                                                                   | 0.88                      | 1                                 | 1.1   | ms      |

|                                          |                        | Option 6                                                                   | 1.75                      | 2                                 | 2.2   | ms      |

|                                          |                        | Option 7                                                                   | 2.6                       | 3                                 | 3.3   | ms      |

|                                          |                        | Option 8                                                                   | 3.5                       | 4                                 | 4.4   | ms      |

<sup>&</sup>lt;sup>1</sup> Guaranteed by design, not production tested. <sup>2</sup> Bench measurement result. <sup>3</sup> Only available in the 48-lead LQFP package.

#### **OPERATION AMPLIFIER SPECIFICATIONS**

$V_{IN} = 12 \text{ V}, V_{AVDD} = 5 \text{ V}, T_J = -40 ^{\circ}\text{C}$  to  $+125 ^{\circ}\text{C}$  for minimum and maximum specifications, and  $T_A = 25 ^{\circ}\text{C}$  for typical specifications, unless otherwise noted.

Table 4.

| Parameter                        | Symbol                | Test Conditions/Comments                                  | Min                       | Тур                        | Max               | Unit    |

|----------------------------------|-----------------------|-----------------------------------------------------------|---------------------------|----------------------------|-------------------|---------|

| INPUT CHARACTERISTICS            |                       |                                                           |                           |                            |                   |         |

| Input Voltage Range              |                       |                                                           | 0                         |                            | $V_{\text{AVDD}}$ | V       |

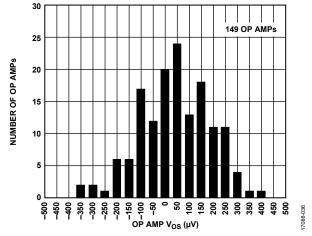

| Input Offset                     | V <sub>OS_EA</sub>    | T <sub>J</sub> = 25°C                                     |                           | 20                         | 850               | μV      |

| Input Offset Temperature Drift   |                       |                                                           |                           | 5.5                        | 19                | μV/°C   |

| Input Bias Current <sup>1</sup>  |                       |                                                           |                           | 1                          | 1000              | рА      |

| Input Capacitance <sup>1</sup>   | C <sub>IN_EA</sub>    |                                                           |                           | 2                          |                   | pF      |

| OUTPUT CHARACTERISTICS           |                       |                                                           |                           |                            |                   |         |

| Output Voltage High              | V <sub>OH_EA</sub>    | Ι <sub>ΟΗ_ΕΑ</sub> = -250 μΑ                              | V <sub>AVDD</sub> – 0.3 V | $V_{\text{AVDD}} - 0.1  V$ |                   | V       |

| Output Voltage Low               | $V_{OL\_EA}$          | $I_{OL\_EA} = +250 \mu\text{A}$                           |                           | 15                         | 35                | mV      |

| Short-Circuit Current            | I <sub>SC_H_EA</sub>  | Short to AVDD                                             |                           | 30                         |                   | mA      |

|                                  | I <sub>SC_L_EA</sub>  | Short to GND                                              |                           | 15                         |                   | mA      |

| DYNAMIC PERFORMANCE <sup>2</sup> |                       |                                                           |                           |                            |                   |         |

| Slew Rate                        | $SR_{EA}$             | $R_{L_EA} = 10 \text{ k}\Omega, C_{L_EA} = 35 \text{ pF}$ |                           | 0.5                        |                   | V/µs    |

| Gain Bandwidth Product           | GBPEA                 | $R_{L_EA} = 10 \text{ k}\Omega, C_{L_EA} = 35 \text{ pF}$ |                           | 1.6                        |                   | MHz     |

| Phase Margin                     | $\Phi_{M\_EA}$        | $R_{L_EA} = 10 \text{ k}\Omega, C_{L_EA} = 35 \text{ pF}$ |                           | 56                         |                   | Degrees |

| NOISE PERFORMANCE <sup>2</sup>   |                       |                                                           |                           |                            |                   |         |

| Input Voltage Noise Density      | e <sub>ni_EA</sub>    | f = 1 kHz                                                 |                           | 240                        |                   | nV/√Hz  |

| Input Voltage Noise              | e <sub>n_EA</sub> p-p | f = 0.1 Hz to 10 Hz                                       |                           | 46                         |                   | μV p-p  |

<sup>&</sup>lt;sup>1</sup> Guaranteed by design, not production tested. <sup>2</sup> Bench measurement result.

## **ABSOLUTE MAXIMUM RATINGS**

#### Table 5.

| Tuble 3.                                                                  |                                                                                                   |

|---------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|

| Parameter                                                                 | Rating                                                                                            |

| VIN, SW, DET, VPTH                                                        | -0.3 V to +40 V                                                                                   |

| AVDD                                                                      | −0.3 V to +6 V                                                                                    |

| BST                                                                       | The SW pin voltage $(V_{SW}) + 6 V$                                                               |

| DRV                                                                       | –0.3 V to +12 V                                                                                   |

| EIN1, EIN2, EIN3, EIN4                                                    | -8 V to +8 V                                                                                      |

| EIN5_P, EIN5_N                                                            | −8 V to +8 V                                                                                      |

| EOUT1, EOUT2, EOUT3, EOUT4, EOUT5, VCOM, RCOM                             | -0.3 V to V <sub>AVDD</sub>                                                                       |

| VR <u>EG, F</u> B1, FB2, VTRP, VTRPL,<br>RSTO, TRG, GATE, GAINO,<br>GAIN1 | −0.3 V to +6 V                                                                                    |

| PGNDx to GND                                                              | –0.3 V to +0.3 V                                                                                  |

| Operating Temperature Range (Junction)                                    | –40°C to +125°C                                                                                   |

| Storage Temperature Range                                                 | −65°C to +150°C                                                                                   |

| Soldering Conditions                                                      | JEDEC J-STD-020                                                                                   |

| Electrostatic Discharge (ESD)                                             |                                                                                                   |

| Human Body Mode                                                           | 4000 V (for EIN1, EIN2, EIN3,<br>EIN4, EIN5_P, and EIN5_N pins),<br>2000 V (for the rest of pins) |

| Charged Device Mode                                                       | 500 V                                                                                             |

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

#### THERMAL RESISTANCE

Thermal performance is directly linked to printed circuit board (PCB) design and operating environment. Close attention to PCB thermal design is required.

$\theta_{JA}$  is the natural convection junction to ambient thermal resistance measured in a one cubic foot sealed enclosure.

$\theta_{\text{JC}}$  is the junction to case thermal resistance.

**Table 6. Thermal Resistance**

| Package Type         | θ <sub>JA</sub> | θις  | Unit |

|----------------------|-----------------|------|------|

| CP-32-7 <sup>1</sup> | 32.7            | 1.4  | °C/W |

| ST-48 <sup>1</sup>   | 66.68           | 3.41 | °C/W |

$<sup>^1</sup>$   $\theta_{JA}$  is measured using natural convection on a JEDEC 4-layer board with the exposed pad soldered to the PCB and with thermal vias.

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

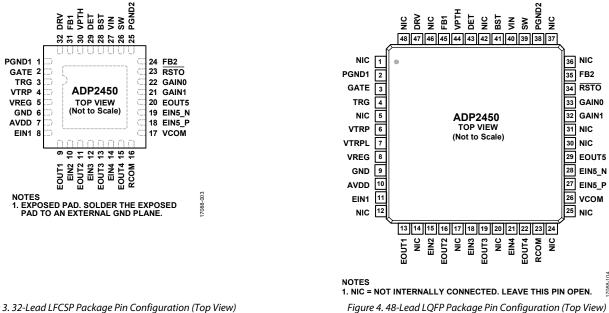

## PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS

Figure 3. 32-Lead LFCSP Package Pin Configuration (Top View)

**Table 7. Pin Function Descriptions**

| P                | in No.          |          |                                                                                                                                            |

|------------------|-----------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------|

| LFCSP<br>32-Lead | LQFP<br>48-Lead | Mnemonic | Description                                                                                                                                |

| 1                | 2               | PGND1    | Boost Shunt Driver and Actuator Driver Ground.                                                                                             |

| 2                | 3               | GATE     | Actuator Driver. This pin drives the silicon controlled rectifier (SCR), field-effect transistor (FET), or transistor.                     |

| 3                | 4               | TRG      | Actuator Trigger Signal. This signal comes from the microcontroller unit (MCU).                                                            |

| 4                | 6               | VTRP     | Analog Trip High Threshold Setting. Connect a resistor between this pin and ground to set the analog trip high threshold.                  |

|                  | 7               | VTRPL    | Analog Trip Low Threshold Setting. Connect a resistor between this pin and ground to set the analog trip low threshold.                    |

| 5                | 8               | VREG     | Internal 5 V Regulator Output. The IC control circuits are powered from this voltage. Place a 1 µF ceramic capacitor between VREG and GND. |

| 6                | 9               | GND      | Analog Ground. Connect this pin to the ground plane.                                                                                       |

| 7                | 10              | AVDD     | Power Supply for the Amplifier Block.                                                                                                      |

| 8                | 11              | EIN1     | Input of the Programmable Gain Amplifier 1.                                                                                                |

| 9                | 13              | EOUT1    | Output of the Programmable Gain Amplifier 1.                                                                                               |

| 10               | 15              | EIN2     | Input of the Programmable Gain Amplifier 2.                                                                                                |

| 11               | 16              | EOUT2    | Output of the Programmable Gain Amplifier 2.                                                                                               |

| 12               | 18              | EIN3     | Input of the Programmable Gain Amplifier 3.                                                                                                |

| 13               | 19              | EOUT3    | Output of the Programmable Gain Amplifier 3.                                                                                               |

| 14               | 21              | EIN4     | Input of the Programmable Gain Amplifier 4.                                                                                                |

| 15               | 22              | EOUT4    | Output of the Programmable Gain Amplifier 4.                                                                                               |

| 16               | 23              | RCOM     | External Resistance Compensation for Programmable Gain Amplifier 1 to Amplifier 4.                                                         |

| 17               | 26              | VCOM     | Setting for the Output Common Voltage of the Programmable Gain Amplifiers. This pin is connected to an external reference voltage.         |

| 18               | 27              | EIN5_P   | Positive Input of Amplifier 5.                                                                                                             |

| 19               | 28              | EIN5_N   | Negative Input of Amplifier 5.                                                                                                             |

| 20               | 29              | EOUT5    | Output of the Amplifier 5.                                                                                                                 |

| 21               | 32              | GAIN1    | Gain Setting for Programmable Gain Amplifier 1 to Amplifier 4. This pin is combined with GAIN0 to set the gain of the amplifier.           |

| Pi               | n No.                                                             |          |                                                                                                                                                                                                                               |

|------------------|-------------------------------------------------------------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LFCSP<br>32-Lead | LQFP<br>48-Lead                                                   | Mnemonic | Description                                                                                                                                                                                                                   |

| 22               | 33                                                                | GAIN0    | Gain Setting for Programmable Gain Amplifier 1 to Amplifier 4. This pin is combined with GAIN1 to set the gain of the amplifier.                                                                                              |

| 23               | 34                                                                | RSTO     | Reset Output (Open Drain). Connect this pin to a resistor to any pull-up voltage < 5.5 V.                                                                                                                                     |

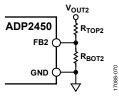

| 24               | 35                                                                | FB2      | Feedback Voltage Sense Input for Buck Regulator. Connect this pin to a resistor divider from buck output voltage, $V_{OUT2}$ , for adjustable version. For the fixed output version, connect this pin to $V_{OUT2}$ directly. |

| 25               | 38                                                                | PGND2    | Power Ground for Buck Regulator.                                                                                                                                                                                              |

| 26               | 39                                                                | SW       | Switch Node for Buck Regulator.                                                                                                                                                                                               |

| 27               | 40                                                                | VIN      | Power Input for Buck Regulator and Internal VREG. This voltage is monitored by the power detection circuit. Connect a bypass capacitor between this pin and PGND2.                                                            |

| 28               | 41                                                                | BST      | Supply Rail for the Gate Drive of Buck. Place a 0.1 µF capacitor between SW and BST.                                                                                                                                          |

| 29               | 43                                                                | DET      | Power Detection Output.                                                                                                                                                                                                       |

| 30               | 44                                                                | VPTH     | Power Detection Voltage Threshold Setting. Connect a resistor between this pin and ground to set the power rating detection voltage threshold.                                                                                |

| 31               | 45                                                                | FB1      | Feedback Voltage Sense Input for boost shunt. Connect this pin to a resistor divider from V <sub>OUT1</sub> .                                                                                                                 |

| 32               | 47                                                                | DRV      | Boost Shunt Driver.                                                                                                                                                                                                           |

|                  | 1, 5, 12, 14,<br>17, 20, 24, 25,<br>30, 31, 36, 37,<br>42, 46, 48 | NIC      | Not Internally Connected. Leave the pin open.                                                                                                                                                                                 |

| 33               |                                                                   | EP       | Exposed Pad. Solder the exposed pad to an external GND plane.                                                                                                                                                                 |

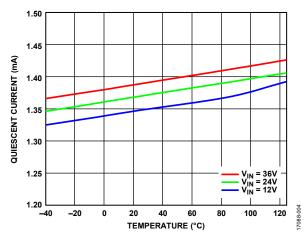

## TYPICAL PERFORMANCE CHARACTERISTICS

$T_A = 25$ °C,  $V_{IN} = 12$  V,  $V_{AVDD} = 5$  V,  $V_{VCOM} = V_{RCOM}$  (the RCOM pin voltage) = 0 V, unless otherwise noted.

Figure 5. Quiescent Current vs. Temperature

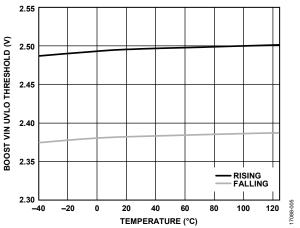

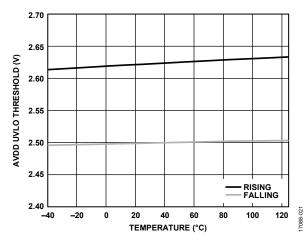

Figure 6. VIN UVLO Threshold for Boost Controller vs. Temperature

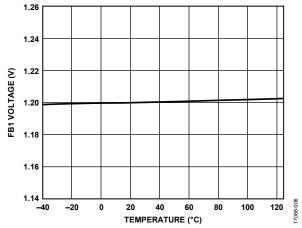

Figure 7. FB1 Voltage vs. Temperature

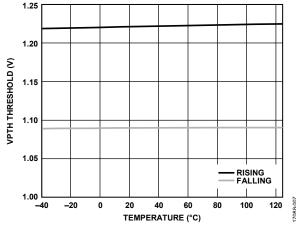

Figure 8. VPTH Threshold vs. Temperature

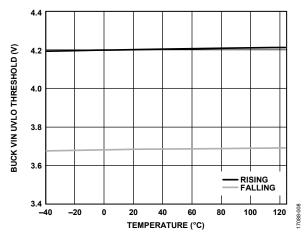

Figure 9. VIN UVLO Threshold for Buck Regulator vs. Temperature

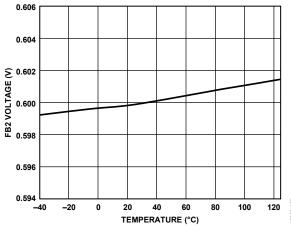

Figure 10. FB2 Voltage vs. Temperature

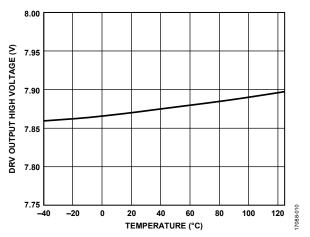

Figure 11. DRV Output High Voltage vs. Temperature

Figure 12. MOSFET On Resistance vs. Temperature

Figure 13. Valley Current-Limit Threshold vs. Temperature

Figure 14. DET Output Low Voltage vs. Temperature

Figure 15. Bootstrap Voltage vs. Temperature

Figure 16. Switching Frequency vs. Temperature

Figure 17. Reset Rising Delay Time (Option 1, Option 2) vs. Temperature

Figure 18. Fixed Output Version Soft Start Time vs. Temperature

Figure 19. AVDD Quiescent Current vs. Temperature

Figure 20. Reset Rising Delay Time (Option 3, Option 4) vs. Temperature

Figure 21. Adjustable Output Version Soft Start Time vs. Temperature

Figure 22. AVDD UVLO Threshold vs. Temperature

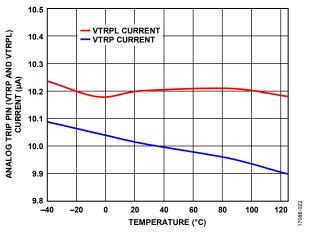

Figure 23. Analog Trip Pin (VTRP and VTRPL) Current vs. Temperature

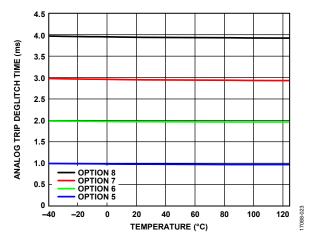

Figure 24. Analog Trip Deglitch Time vs. Temperature (Option 5 to Option 8)

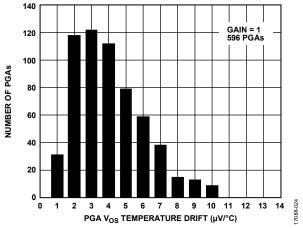

Figure 25. PGA Input Offset Voltage Drift Distribution, Gain = 1

Figure 26. Analog Trip Deglitch Time vs. Temperature (Option 1 to Option 4)

Figure 27. PGA Input Offset Voltage Distribution

Figure 28. PGA Input Offset Voltage Drift Distribution, Gain = 4

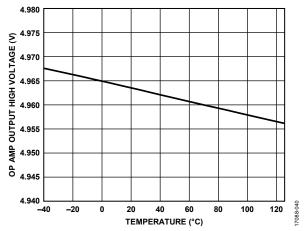

Figure 29. PGA Output High Voltage vs. Temperature

Figure 30. PGA Gain Error Distribution

Figure 31. PGA Gain Drift Distribution, Gain = 1

Figure 32. PGA Output Low Voltage vs. Temperature

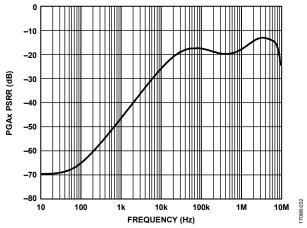

Figure 33. PGAx Power Supply Rejection Ratio (PSRR) vs. Frequency

Figure 34. PGA Gain Drift Distribution, Gain = 4

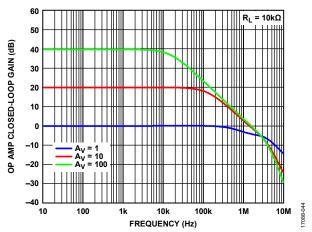

Figure 35. PGA Closed-Loop Gain vs. Frequency

Figure 36. PGA Input Voltage Noise Density vs. Frequency

Figure 37. Operational Amplifier (Op Amp) Input Offset Voltage Distribution

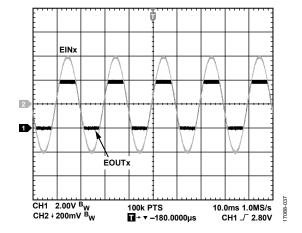

Figure 38. PGA No Phase Reversal,  $V_{VCOM} = V_{AVDD} = 4 V$ ,  $A_V = -10$

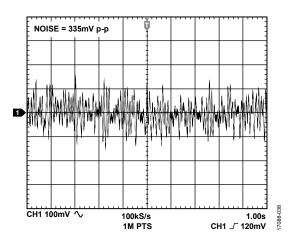

Figure 39. PGA 0.1 Hz to 10 Hz Noise, Amplification =  $10,000 \times$

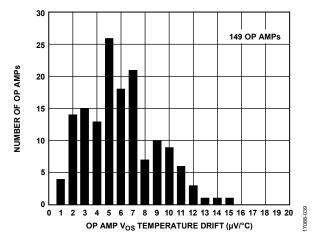

Figure 40. Op Amp Input Offset Voltage Temperature Drift Distribution

${\it Figure\,41.\,Op\,Amp\,Output\,High\,Voltage\,vs.\,Temperature}$

Figure 42. Op Amp Open-Loop Gain and Phase Shift vs. Frequency

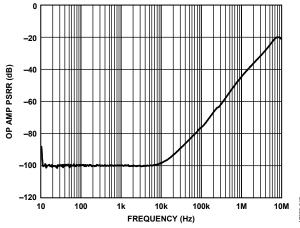

Figure 43. Op Amp PSRR vs. Frequency

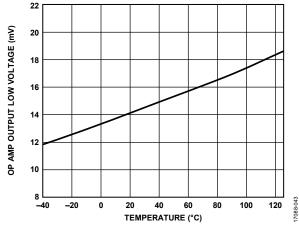

Figure 44. Op Amp Output Low Voltage vs. Temperature

Figure 45. Op Amp Close-Loop Gain vs. Frequency

Figure 46. Op Amp Common-Mode Rejection Ratio (CMRR) vs. Frequency

Figure 47. Op Amp No Phase Reversal,  $V_{AVDD} = 4 V$ ,  $A_V = -10$

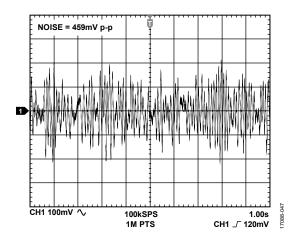

Figure 48. Op Amp 0.1 Hz to 10 Hz Noise, Amplification =  $10,000 \times$

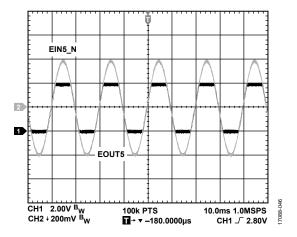

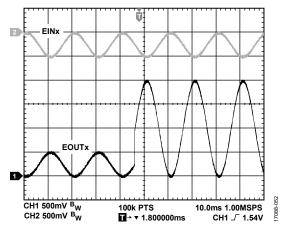

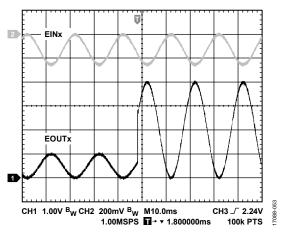

Figure 49. PGA Working Waveform, Gain = 1

Figure 50. Op Amp Input Voltage Noise Density vs. Frequency

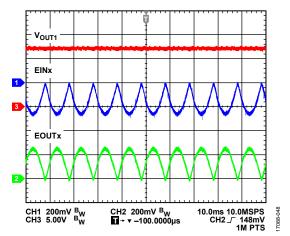

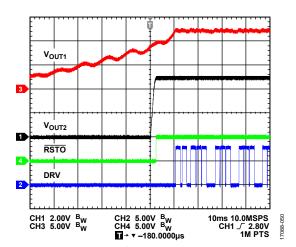

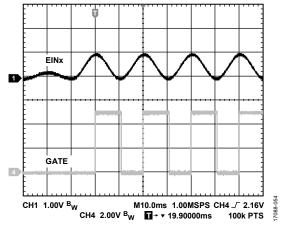

Figure 51. Start Up with AC Current Source, VCOM = GND

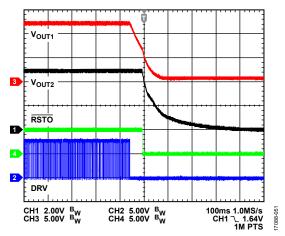

Figure 52. System Shutdown Waveform

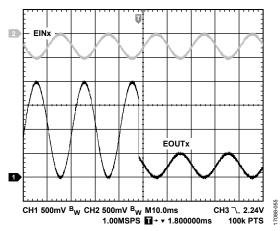

Figure 53. PGA Gain Switching from Gain = 1 to Gain = 4

Figure 54. PGA Gain Switching from Gain = 4 to Gain = 16

Figure 55. Analog Trip Threshold Triggered, VCOM = RCOM = 0 V

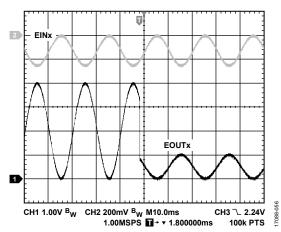

Figure 56. PGA Gain Switching from Gain = 4 to Gain = 1

Figure 57. PGA Gain Switching from Gain = 16 to Gain = 4

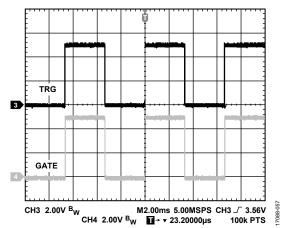

Figure 58. TRG Trigger Analog Trip Function

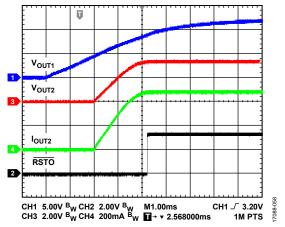

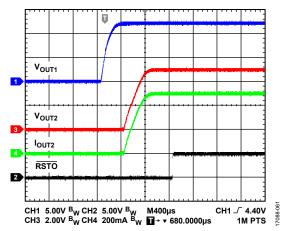

Figure 59. Buck Regulator Soft Start with Full Load  $(V_{OUT2} = 3.3 V, Adjustable Version)$

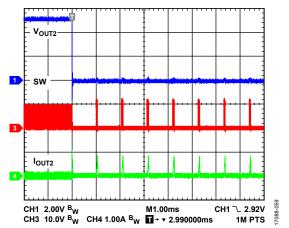

Figure 60. Buck Regulator OCP Triggered

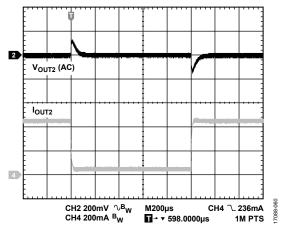

Figure 61. Buck Regulator Load Transient (50 mA to 450 mA)

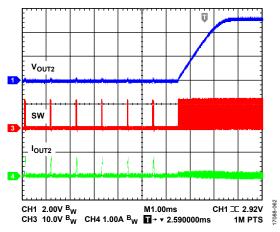

Figure 62. Buck Regulator Soft Start with Full Load  $(V_{OUT2} = 5 V, Fixed Version)$

Figure 63. Buck Regulator OCP Recovery

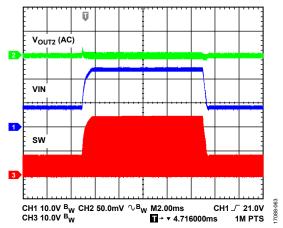

Figure 64. Buck Regulator Line Transient, V<sub>IN</sub> from 8 V to 24 V, Full Load

## THEORY OF OPERATION

The ADP2450 is a power management IC for circuit breaker and CT powered supply applications. The ADP2450 integrates one boost shunt controller with power detection, one high efficiency buck regulator, four programmable gain amplifiers, one low offset operation amplifier, a fast analog trip circuit, and an actuator driver in a 32-lead LFCSP or 48-lead LQFP package. With the high integration rate, the ADP2450 provides a compact, robust power supply and signal conditioning solution for size limited, high reliability systems.

#### **BOOST SHUNT CONTROLLER**

The ADP2450 integrates a boost shunt controller with a field-effect transistor (FET) driver. The boost shunt controller uses a hysteresis control scheme to regulate the output voltage. When the feedback voltage on the FB1 pin is lower than the reference voltage (typically 1.2 V), the FET driver turns off the external FET, and then the current from CT charges the output capacitor storing energy in the capacitor. When the output voltage rises and the feedback voltage on the FB1 pin is higher than the rising threshold (typically 1.219 V), the FET driver turns on the external FET and bypasses the CT current to ground through the external FET.

#### **POWER DETECTION**

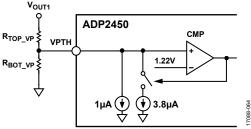

The ADP2450 integrates an input power detection function. During startup, when the voltage on the VPTH pin is lower than the VPTH rising threshold (typically 1.22 V), the power detection FET is turned on and the DET pin is pulled down to ground. Both the 1  $\mu A$  and 3.8  $\mu A$  internal current sources are added between VPTH and ground. When the voltage on the VPTH pin rises above the VPTH rising threshold (typical 1.22 V), the power detection FET is turned off and the DET pin is open. The 3.8  $\mu A$  current source is removed and only the 1  $\mu A$  current source is added.

When the voltage on the VPTH pin falls below the VPTH falling threshold (typically 1.09 V), the power detection FET is turned on again, which pulls the DET pin to ground, and the  $3.8 \,\mu\text{A}$  current source is added between VPTH and ground again.

The voltage threshold and hysteresis for power detection is programmable with external resistors on the VPTH pin, as shown in Figure 65.

Figure 65. Programmable Voltage of Power Detection

Use the following equation to calculate  $R_{TOP\_VP}$  and  $R_{BOT\_VP}$ :

$$R_{TOP\_VP} = \frac{1.09 \text{ V} \times V_{OUT1\_RISING} - 1.22 \text{ V} \times V_{OUT1\_FALLING}}{1.09 \text{ V} \times 4.8 \text{ } \mu\text{A} - 1.22 \text{ V} \times 1 \text{ } \mu\text{A}}$$

$$R_{BOT\_VP} = \frac{1.22 \text{ V} \times R_{TOP\_VP}}{V_{OUTI\_RISING} - R_{TOP\_VP} \times 4.8 \text{ } \mu\text{A} - 1.22 \text{ V}}$$

where:

$R_{TOP\_VP}$  is the top side resistor connected between the  $V_{OUT1}$  and VPTH pin.

$R_{BOT\_VP}$  is the bottom side resistor connected between the VPTH pin and ground.

$V_{\text{OUT1\_RISING}}$  is the  $V_{\text{OUT1}}$  rising threshold.

*V*<sub>OUT1\_FALLING</sub> is the V<sub>OUT1</sub> falling threshold.

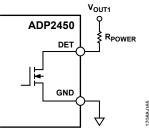

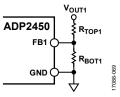

A dummy resistor load ( $R_{POWER}$ ) connected between  $V_{OUT1}$  and the DET pin ensures that the whole system is not enabled until there is enough power provided to the system by the current transformer, as shown in Figure 66.

Figure 66. Dummy Load Connection

Calculate the dummy load resistor value using the following equation:

$$R_{POWER} = \frac{V_{OUTI\_RISING}}{I_{DUMMY}}$$

where  $I_{DUMMY}$  is the minimum required current value before enabling the system.

Ensure that the selected dummy load resistor can handle the power before the DET pin is open. The power consumption on the dummy load resistor ( $P_{\text{DUMMY}}$ ) is calculated using the following equation:

$$P_{DUMMY} = I_{DUMMY}^2 \times R_{POWER}$$

#### **INTERNAL REGULATOR**

The internal 5 V regulator (VREG) provides a stable voltage supply for the internal control circuits. It is recommended to place a 1  $\mu$ F ceramic capacitor between VREG and GND. The internal regulator also includes a current-limit circuit for over-current protection.

The internal 8 V regulator provides the voltage supply for the boost shunt driver.

The VIN pin provides power supply for both the 5 V and 8 V internal regulators.

#### **BUCK REGULATOR**

The buck regulator in the ADP2450 uses a current mode control scheme for stability and transient response.

The buck regulator operates in a 1.2 MHz fixed switching frequency. The regulator integrates the soft start and compensation circuit to reduce the external components and provide an easy to use solution. The soft-start time is 400  $\mu$ s for the fixed output version and is 1.6 ms for the adjustable output version.

The ADP2450 uses the emulated current ramp voltage for cycle by cycle current-limit protection to prevent current runaway. When the emulated current ramp voltage reaches the current-limit threshold, the high-side MOSFET turns off and the low-side MOSFET turns on until the next cycle. The overcurrent counter increments during this cycling process. If the overcurrent does not occur in the next cycle, the overcurrent counter decreases. If the overcurrent counter reaches 10 or the voltage on the FB2 pin drops below 0.2 V after soft start, the buck regulator enters into hiccup mode. During hiccup mode, both the high-side MOSFET and low-side MOSFET are turned off. The buck regulator remains in hiccup mode for 1024 clock cycles and then attempts to restart with a soft start. If the current-limit fault is cleared, the buck regulator resumes normal operation. Otherwise, the buck regulator reenters hiccup mode.

The low-side MOSFET in the buck regulator also sinks current from the load. If the low-side sink current exceeds the sink current-limit threshold, both the low-side and high-side MOSFETs are turned off until the next cycle starts.

The buck regulator only works when the voltage on the VPTH pin is higher than the VPTH rising threshold.

#### **BOOTSTRAP CIRCUIT**

The ADP2450 includes a regulator to provide the gate driver voltage for the high-side N-MOSFET of the buck regulator. It uses differential sensing method to generate a 5 V bootstrap voltage between the BST and the SW pins.

It is recommended to place a 0.1  $\mu$ F, X7R or X5R ceramic capacitor between the BST and the SW pins.

#### **POWER MONITOR AND RESET**

The output voltage of the buck regulator is monitored through the FB2 pin. When the voltage on FB2 pin is below the reset threshold, the  $\overline{RSTO}$  pin is pulled down. When the voltage on FB2 pin is above the reset threshold, the  $\overline{RSTO}$  pin is released and can be pulled up by an external voltage source. A delay time is designed for the  $\overline{RSTO}$  pin to ensure that no glitch occurs on the  $\overline{RSTO}$  pin. There are four following options for the rising delay time: 0.5 ms, 1 ms, 2 ms, and 5 ms. The falling delay time is fixed at 10  $\mu s$ .

#### PROGRAMMABLE GAIN AMPLIFIER

The ADP2450 integrates four low offset, low power programmable gain amplifiers (PGA1, PGA2, PGA3, and PGA4). The gain of these amplifiers is programmable through the GAIN0 and GAIN1 pins.

Connect a resistor between the GAIN1 pin and ground to set different gains.

Pull up the GAIN0 pin to high or pull down the GAIN0 pin to low to choose different gain ranges.

A total of 15 gains can be obtained via different combinations of GAIN0 and GAIN1 settings. Table 8 shows the relationship between the gain and the GAIN0 and GAIN1 configurations.

Table 8. Gain Setting for PGAx

|                                   | GAIN        |              |  |

|-----------------------------------|-------------|--------------|--|

| Resistance on GAIN1 ( $k\Omega$ ) | GAIN0 = Low | GAIN0 = High |  |

| 0                                 | 0.75        | 3            |  |

| 42.2                              | 1           | 4            |  |

| 63.4                              | 1.25        | 5            |  |

| 95.3                              | 1.5         | 6            |  |

| 143                               | 1.75        | 7            |  |

| 215                               | 2           | 8            |  |

| 324                               | 2.5         | 10           |  |

| AVDD                              | 4           | 16           |  |

The AVDD pin provides the voltage supply for the programmable gain amplifiers, and the output voltage of the amplifiers are clamped between zero and  $V_{\rm AVDD}$ .

The output voltage of PGAx is calculated with the following equation:

$$V_{EOUTx} = \frac{V_{VCOM}}{2} - V_{EINx} \times GAIN$$

#### where:

$V_{EOUTx}$  is the voltage on the EOUTx pin.

$V_{VCOM}$  is the voltage on VCOM pin.

$V_{EINx}$  is the voltage on the EINx pin.

*GAIN* is the gain value programmed by the GAIN0 and GAIN1 pins according to Table 8.

In a Rogowski application, as shown in Figure 75, connect a resistor between RCOM and ground to compensate for the passive, integrated dc resistor. Connect VCOM to AVDD or to a reference voltage derived from AVDD for the proper start-up sequence.

In the CT current sense application, connect both the VCOM and RCOM pins to ground.

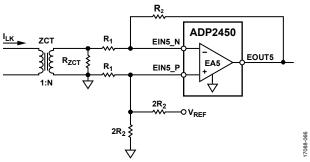

#### **OPERATIONAL AMPLIFIER**

The operational amplifier is a low offset amplifier. The amplifier is used for leakage current detection in circuit breaker application.

Figure 67 shows the circuit configuration with the operational amplifier for leakage current detection as well as R1 and R2. The output voltage of the operational amplifier is calculated with the following equation:

$$V_{EOUT5} = \frac{V_{REF}}{2} - \frac{I_{LK}}{N} \times R_{ZCT} \times \frac{R_2}{R_1}$$

where:

$V_{EOUT5}$  is the voltage on the EOUT5 pin.

$V_{REF}$  is the external reference voltage.

$I_{LK}$  is the leakage current.

N is the turn ratio of the zero-current transformer (ZCT).  $R_{ZCT}$  is the current sense resistor at the secondary side of the ZCT.

Figure 67. Typical Configuration for Leakage Current Detection

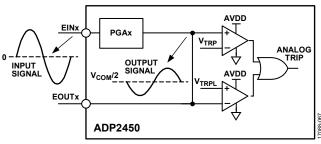

#### **ANALOG TRIP PROTECTION**

The ADP2450 integrates an analog trip circuit for fast protection in circuit breaker applications. The analog trip circuit monitors the output of each PGA. When any of the four PGA outputs exceeds the analog trip threshold,  $V_{TRP}$  or  $V_{TRPL}$ , for the deglitch time,  $t_{TRP}$ , the analog trip protection is triggered.

Two programmable analog trip thresholds,  $V_{TRP}$  and  $V_{TRPL}$ , support both half-sinusoid and bipolar sinusoid input signal application.  $V_{TRP}$  is the high threshold and  $V_{TRPL}$  is the low threshold. The PGAx output signal is compared with the two analog trip thresholds. If the PGAx output signal is either higher than  $V_{TRP}$  or lower than  $V_{TRPL}$ , the analog trip protection is triggered as shown in Figure 68.

Figure 68. Analog Trip Circuit

The analog trip thresholds are programmable with external resistors and can be calculated using the following equations:

$$V_{TRP}(V) = 0.01 \times R_{TRP}(k\Omega)$$

$$V_{TRPL}(V) = 0.01 \times R_{TRPL}(k\Omega)$$

where:

$V_{\mathit{TRP}}$  is the high analog trip threshold voltage.

$V_{TRPL}$  is the low analog trip threshold voltage.

$R_{TRP}$  is the resistance connected between the VTRP pin and ground.

$R_{TRPL}$  is the resistance connected between the VTRPL pin and ground.

Note that there are limitations when choosing the  $R_{\text{TRP}}$  and  $R_{\text{TRPL}}$  values to set the analog trip thresholds. The following requirements must be met.

For R<sub>TRP</sub> selection,

$$R_{TRP} < (V_{VREG} - 0.5) \times 100 (k\Omega)$$

and

$$R_{TRP} < (V_{AVDD} - 0.1) \times 100 (k\Omega)$$

For R<sub>TRP</sub> selection,

$$R_{TRPL} > 30 (k\Omega)$$

If the analog trip function is not used, connect both  $V_{\text{TRP}}$  and  $V_{\text{TRPL}}$  to VREG to disable the analog trip function.

In the CT current sense application where the input signal is half-sinusoid, only  $V_{TRP}$ , the high analog trip threshold, is needed. Connect  $V_{TRPL}$  to VREG to disable  $V_{TRPL}$ , the low analog trip threshold. Connect RCOM and VCOM to ground in this CT current sense application.

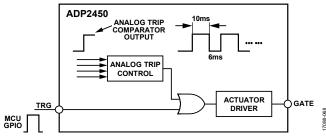

#### **ACTUATOR DRIVER**

The actuator driver receives the input signal either from the TRG pin or from the output of the analog trip control circuit. The driver also provides the gate drive voltage for the external thyristor through the GATE pin, as shown in Figure 69. When the analog trip protection is triggered, the analog trip control circuit outputs a 10 ms high, 6 ms low pulse signal. This pulse signal performs an OR logic with the signal on the TRG pin and inputs to the actuator driver circuit to provide the gate drive signal for the external thyristor or MOSFET. During this 16 ms period, the 10 ms high, 6 ms low pulse signal, any analog trip signal is ignored. If the analog trip signal is still active after the 16 ms period, another pulse that is 10 ms high, 6 ms low is generated. If the analog trip signal is cleared after the 16 ms period, the output of the analog trip control circuit latches to low. The GATE pin can be pulled up to VREG.

Figure 69. Actuator Driver Control Circuit

#### **THERMAL SHUTDOWN**

In the event that the ADP2450 junction temperature exceeds 150°C, the thermal shutdown circuit turns off most of the internal blocks but pulls the boost driver voltage (DRV pin) to high. A 15°C hysteresis is included so that the ADP2450 does not recover from thermal shutdown until the on-chip temperature drops below 135°C. Upon recovery, a soft start and power-up sequence is initiated prior to normal operation.

## APPLICATIONS INFORMATION OUTPUT CAPACITOR OF BOOST SHUNT CONTROLLER

The output capacitor stores the energy coming from the CT and provides the input voltage of the buck regulator as well as power to the actuator. Depending on the  $V_{\text{OUT1}}$  setting and actuator specification, the capacitance must be large enough so that it can provide sufficient power to trigger the actuator when the analog trip occurs and prevent the  $V_{\text{OUT1}}$  voltage from dropping.

The voltage rating of the boost shunt output capacitor must be higher than the output voltage of the boost shunt controller ( $V_{\text{OUT1}}$ ). A margin of at least 20% must be reserved. Polymer, tantalum, and aluminum electrolytic capacitors are recommended for the balance between capacitance, voltage rating, and size. It is recommended to use a ceramic capacitor in the range from 1  $\mu F$  to 10  $\mu F$  in parallel with the output capacitor to reduce the total effective series resistance (ESR), thus reducing the output voltage ripple. Table 9 lists several recommended output capacitors for the boost shunt controller.

**Table 9. Recommended Output Capacitors**

| Vendor    | Part Number        | Capacitance<br>(µF) | Voltage<br>(V) |

|-----------|--------------------|---------------------|----------------|

| KEMET     | T521X336M050ATE075 | 33                  | 50             |

|           | T521X476M035ATE070 | 47                  | 35             |

|           | T494E476M035AT7280 | 47                  | 35             |

|           | A767KN476M1HLAE029 | 47                  | 50             |

| Panasonic | EEFCX1V220R        | 22                  | 35             |

|           | 35SVPF39M          | 39                  | 35             |

|           | 50SVPF39M          | 39                  | 50             |

|           | EEHZA1H680P        | 68                  | 50             |

|           | EEHZA1H330XP       | 33                  | 50             |

#### **BRIDGE RECTIFIER**

The bridge rectifier converts the sinusoid current of the CT secondary side to a half sinusoid current to provide power to the ADP2450. The average forward rectified current of the bridge rectifier diode ( $I_F$ ) must be higher than the rms current of the CT secondary side during normal operation. The maximum dc blocking voltage of the bridge rectifier diode ( $V_{DC}$ ) must be higher than the boost shunt controller output voltage ( $V_{OUT1}$ ) of the ADP2450. Ensure that the peak forward surge current of the bridge rectifier diode ( $I_{FSM}$ ) can handle the peak current of the CT secondary side when a fault occurs, such as when an analog trip is triggered.

Bridge rectifier diodes with low forward voltage are recommended. A low forward voltage reduces the power loss on the bridge rectifier diodes. However, the package size of the bridge rectifier increases. Table 10 lists several recommended bridge rectifiers for general applications.

Table 10. Recommended Bridge Rectifiers

| Vendor    | Part Number     | I <sub>F</sub> (A) | V <sub>DC</sub> (V) | V <sub>F</sub> (V) | I <sub>FSM</sub> (A) |

|-----------|-----------------|--------------------|---------------------|--------------------|----------------------|

| Bourns    | CD2320-B1200    | 1                  | 200                 | 1                  | 30                   |

|           | CD2320-B1400    | 1                  | 400                 | 1                  | 30                   |

|           | CD2320-B1600    | 1                  | 600                 | 1                  | 30                   |

|           | CD2320-B1800    | 1                  | 800                 | 1                  | 30                   |

|           | CD2320-B11000   | 1                  | 1000                | 1                  | 30                   |

| Fairchild | Fairchild MDB6S |                    | 600                 | 1.1                | 30                   |