# Quad Channel, 256-Position, SPI, Nonvolatile Digital Potentiometer

### **Enhanced Product**

# AD5144-EP

### FEATURES

10 k $\Omega$  resistance option Resistor tolerance: 8% maximum Maximum continuous current: ±6 mA at R<sub>AB</sub> = 10 k $\Omega$ Low resistance temperature coefficient: 35 ppm/°C typical Wide bandwidth: 3 MHz at R<sub>AB</sub> = 10 k $\Omega$ Fast start-up time: 75 µs Linear gain setting mode Single- and dual-supply operation Independent V<sub>LOGIC</sub>: 1.8 V to 5.5 V

#### **ENHANCED PRODUCT FEATURES**

Supports defense and aerospace applications (AQEC standard) Military temperature range: -55°C to +125°C Controlled manufacturing baseline One assembly/test site One fabrication site Product change notification Qualification data available on request

### **APPLICATIONS**

Missiles and munitions Avionics and unmanned systems Programmable filters, delays, and time constants Programmable power supplies

### **GENERAL DESCRIPTION**

The AD5144-EP potentiometer provides a nonvolatile solution for 256-position adjustment applications, offering guaranteed low resistor tolerance errors of  $\pm 8\%$  and up to  $\pm 6$  mA current density in the Ax, Bx, and Wx pins.

The low resistor tolerance and low nominal temperature coefficient simplify open-loop applications as well as applications requiring tolerance matching.

The linear gain setting mode allows independent programming of the resistance between the digital potentiometer terminals, through the Terminal A to Terminal W ( $R_{AW}$ ) and the Terminal W to Terminal B ( $R_{WB}$ ) string resistors, allowing accurate resistor matching.

The high bandwidth and low total harmonic distortion (THD) ensure optimal performance for ac signals, making this device suitable for filter design.

The low wiper resistance of 40  $\Omega$  at the ends of the resistor array allow for pin-to-pin connection.

The wiper values can be set through a serial peripheral interface (SPI) digital interface that is also used to read back the wiper register and electronically erasable programmable read-only memory (EEPROM) contents.

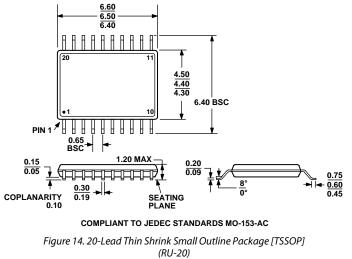

The AD5144-EP is available in a 20-lead TSSOP. The device is guaranteed to operate over the  $-55^{\circ}$ C to  $+125^{\circ}$ C temperature range.

Additional application and technical information can be found in the AD5144 data sheet.

Rev. A

#### Document Feedback

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 ©2019 Analog Devices, Inc. All rights reserved. Technical Support www.analog.com

## TABLE OF CONTENTS

| Features                        | 1 |

|---------------------------------|---|

| Enhanced Product Features       | 1 |

| Applications                    | 1 |

| General Description             | 1 |

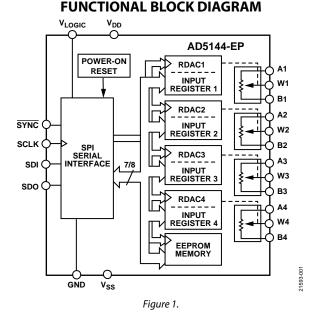

| Functional Block Diagram        | 1 |

| Revision History                | 2 |

| Specifications                  | 3 |

| Electrical Characteristics      | 3 |

| Interface Timing Specifications | 5 |

| Shift Register and Timing Diagrams          | 5  |

|---------------------------------------------|----|

| Absolute Maximum Ratings                    | 7  |

| Thermal Resistance                          | 7  |

| ESD Caution                                 | 7  |

| Pin Configuration and Function Descriptions | 8  |

| Typical Performance Characteristics         | 9  |

| Outline Dimensions                          | 11 |

| Ordering Guide                              | 11 |

### **REVISION HISTORY**

| 10/2019—Rev. 0 to Rev. A |  |

|--------------------------|--|

| Changes to Table 1 4     |  |

9/2019—Revision 0: Initial Version

### SPECIFICATIONS ELECTRICAL CHARACTERISTICS

$V_{DD}$  = 2.3 V to 5.5 V and  $V_{SS}$  = 0 V for the single-supply range,  $V_{DD}$  = 2.25 V to 2.75 V and  $V_{SS}$  = -2.25 V to -2.75 V for the dual-supply range,  $V_{LOGIC}$  = 1.8 V to 5.5 V, and -55°C < T<sub>A</sub> < +125°C, unless otherwise noted. See the AD5144 data sheet for the test circuits that define the test conditions used in the Specifications section.

| Table 1. |

|----------|

|----------|

| Parameter                                                                                    | Symbol Test Conditions/Comments                 |                                                                                                | Min                    | Typ¹ | Мах                           | Unit   |  |

|----------------------------------------------------------------------------------------------|-------------------------------------------------|------------------------------------------------------------------------------------------------|------------------------|------|-------------------------------|--------|--|

| DC CHARACTERISTICS—RHEOSTAT<br>MODE (ALL RESISTIVE DIGITAL-TO-<br>ANALOG CONVERTERS (RDACs)) |                                                 |                                                                                                |                        |      |                               |        |  |

| Resolution                                                                                   | Ν                                               |                                                                                                | 8                      |      |                               | Bits   |  |

| Resistor Integral Nonlinearity <sup>2</sup>                                                  | R-INL                                           | Terminal A and Terminal B resistor ( $R_{AB}$ ) = 10 k $\Omega$                                |                        |      |                               |        |  |

|                                                                                              |                                                 | $V_{DD} \ge 2.7 V$                                                                             | -2                     | ±0.2 | +2                            | LSB    |  |

|                                                                                              |                                                 | $V_{DD} < 2.7 V$                                                                               | -5                     | ±1.5 | +5                            | LSB    |  |

| Resistor Differential Nonlinearity <sup>2</sup>                                              | R-DNL                                           |                                                                                                | -0.5                   | ±0.2 | +0.5                          | LSB    |  |

| Nominal Resistor Tolerance                                                                   | $\Delta R_{AB}/R_{AB}$                          |                                                                                                | -8                     | ±1   | +8                            | %      |  |

| Resistance Temperature Coefficient <sup>3</sup>                                              | $(\Delta R_{AB}/R_{AB})/\Delta T \times 10^{6}$ | Code = full scale                                                                              |                        | 35   |                               | ppm/°C |  |

| Wiper Resistance <sup>3</sup>                                                                | Rw                                              | Code = zero scale, $R_{AB} = 10 \text{ k}\Omega$                                               |                        | 55   | 125                           | Ω      |  |

| Bottom Scale or Top Scale                                                                    | R <sub>BS</sub> or R <sub>TS</sub>              | $R_{AB} = 10 \ k\Omega$                                                                        |                        | 40   | 80                            | Ω      |  |

| Nominal Resistance Match                                                                     | $R_{AB1}/R_{AB2}$                               | Code = 0xFF                                                                                    | -1                     | ±0.2 | +1                            | %      |  |

| DC CHARACTERISTICS—POTENTIOMETER<br>DIVIDER MODE (ALL RDACs)                                 |                                                 |                                                                                                |                        |      |                               |        |  |

| Integral Nonlinearity <sup>4</sup>                                                           | INL                                             | $R_{AB} = 10 \ k\Omega$                                                                        | -1                     | ±0.2 | +1                            | LSB    |  |

| Differential Nonlinearity <sup>4</sup>                                                       | DNL                                             |                                                                                                | -0.5                   | ±0.2 | +0.5                          | LSB    |  |

| Full-Scale Error                                                                             | Vwfse                                           | $R_{AB} = 10 \ k\Omega$                                                                        | -2.5                   | -0.1 |                               | LSB    |  |

| Zero-Scale Error                                                                             | Vwzse                                           | $R_{AB} = 10 \ k\Omega$                                                                        |                        | 1.2  | 3                             | LSB    |  |

| Voltage Divider Temperature<br>Coefficient <sup>3</sup>                                      | $(\Delta V_W/V_W)/\Delta T 	imes 10^6$          | Code = half scale                                                                              |                        | ±5   |                               | ppm/°C |  |

| RESISTOR TERMINALS                                                                           |                                                 |                                                                                                |                        |      |                               |        |  |

| Maximum Continuous Current                                                                   | $I_A$ , $I_B$ , and $I_W$                       |                                                                                                |                        |      |                               |        |  |

|                                                                                              |                                                 | $R_{AB} = 10 \ k\Omega$                                                                        | -6                     |      | +6                            | mA     |  |

| Terminal Voltage Range⁵                                                                      |                                                 |                                                                                                | Vss                    |      | V <sub>DD</sub>               | V      |  |

| Capacitance A, Capacitance B <sup>3</sup>                                                    | С <sub>А</sub> , С <sub>В</sub>                 | f = 1 MHz, measured to GND,<br>code = half scale, $R_{AB} = 10 k\Omega$                        |                        | 25   |                               | pF     |  |

| Capacitance W <sup>3</sup>                                                                   | Cw                                              | f = 1 MHz, measured to GND,<br>code = half scale, $R_{AB} = 10 k\Omega$                        |                        | 12   |                               | pF     |  |

| Common-Mode Leakage Current <sup>3</sup>                                                     |                                                 | Terminal A voltage $(V_A) =$<br>wiper terminal voltage $(V_W) =$<br>Terminal B voltage $(V_B)$ | -500                   | ±15  | +500                          | nA     |  |

| DIGITAL INPUTS                                                                               |                                                 |                                                                                                |                        |      |                               |        |  |

| Input Logic <sup>3</sup>                                                                     |                                                 |                                                                                                |                        |      |                               |        |  |

| High                                                                                         | VINH                                            | $V_{LOGIC} = 1.8 V \text{ to } 2.3 V$                                                          | $0.8 \times V_{LOGIC}$ |      |                               | V      |  |

|                                                                                              |                                                 | $V_{LOGIC} = 2.3 V \text{ to } 5.5 V$                                                          | $0.7 \times V_{LOGIC}$ |      |                               | V      |  |

| Low                                                                                          | VINL                                            |                                                                                                |                        |      | $0.2 \times V_{\text{LOGIC}}$ | V      |  |

| Input Hysteresis <sup>3</sup>                                                                | V <sub>HYST</sub>                               |                                                                                                | $0.1 \times V_{LOGIC}$ |      |                               | V      |  |

| Input Current <sup>3</sup>                                                                   | l <sub>in</sub>                                 |                                                                                                |                        |      | ±1                            | μA     |  |

| Input Capacitance <sup>3</sup>                                                               | C <sub>IN</sub>                                 |                                                                                                |                        | 5    |                               | pF     |  |

### **Enhanced Product**

| Parameter                            | Symbol            | Test Conditions/Comments                                                                               | Min   | Typ <sup>1</sup> | Мах             | Unit    |

|--------------------------------------|-------------------|--------------------------------------------------------------------------------------------------------|-------|------------------|-----------------|---------|

| DIGITAL OUTPUTS                      |                   |                                                                                                        |       |                  |                 |         |

| Output High Voltage <sup>3</sup>     | V <sub>он</sub>   | Pull-up resistor ( $R_{PULL-UP}$ ) = 2.2 k $\Omega$ to V <sub>LOGIC</sub>                              |       | VLOGIC           |                 | V       |

| Output Low Voltage <sup>3</sup>      | Vol               | Sink current (I <sub>SINK</sub> ) = 3 mA                                                               |       |                  | 0.4             | V       |

|                                      |                   | $I_{SINK} = 6 \text{ mA}, V_{LOGIC} > 2.3 \text{ V}$                                                   |       |                  | 0.6             | V       |

| Three-State Leakage Current          |                   |                                                                                                        | -1    |                  | +1              | μA      |

| Three-State Output Capacitance       |                   |                                                                                                        |       | 2                |                 | pF      |

| POWER SUPPLIES                       |                   |                                                                                                        |       |                  |                 |         |

| Single-Supply Range                  |                   | $V_{ss} = GND$                                                                                         | 2.3   |                  | 5.5             | V       |

| Dual-Supply Range                    |                   |                                                                                                        | ±2.25 |                  | ±2.75           | V       |

| Logic Supply Range                   |                   | Single supply, $V_{ss} = GND$                                                                          | 1.8   |                  | V <sub>DD</sub> | V       |

|                                      |                   | Dual supply, Vss < GND                                                                                 | 2.25  |                  | V <sub>DD</sub> | V       |

| Positive Supply Current              | I <sub>DD</sub>   | $V_{INH} = V_{LOGIC}$ or $V_{INL} = GND$                                                               |       |                  |                 |         |

|                                      |                   | $V_{DD} = 5.5 V$                                                                                       |       | 0.7              | 5.5             | μA      |

|                                      |                   | $V_{DD} = 2.3 V$                                                                                       |       | 400              |                 | nA      |

| Negative Supply Current              | lss               | $V_{\text{INH}} = V_{\text{LOGIC}} \text{ or } V_{\text{INL}} = \text{GND}$                            | -5.5  | -0.7             |                 | μA      |

| EEPROM Store Current <sup>3, 6</sup> | IDD EEPROM STORE  | $V_{INH} = V_{LOGIC} \text{ or } V_{INL} = GND$                                                        |       | 2                |                 | mA      |

| EEPROM Read Current <sup>3, 7</sup>  | DD EEPROM READ    | $V_{\text{INH}} = V_{\text{LOGIC}} \text{ or } V_{\text{INL}} = \text{GND}$                            |       | 320              |                 | μA      |

| Logic Supply Current                 | ILOGIC            | $V_{INH} = V_{LOGIC} \text{ or } V_{INL} = GND$                                                        |       | 0.05             | 1.4             | μA      |

| Power Dissipation <sup>8</sup>       | P <sub>DISS</sub> | $V_{INH} = V_{LOGIC} \text{ or } V_{INL} = GND$                                                        |       | 3.5              |                 | μW      |

| Power Supply Rejection Ratio PSRR    |                   | $\Delta V_{DD}/\Delta V_{SS} = V_{DD} \pm 10\%$ ,<br>code = full scale                                 |       | -66              | -60             | dB      |

| DYNAMIC CHARACTERISTICS9             |                   |                                                                                                        |       |                  |                 |         |

| Bandwidth                            | BW                | $-3 \text{ dB}, \text{R}_{AB} = 10 \text{ k}\Omega$                                                    |       | 3                |                 | MHz     |

| Total Harmonic Distortion            | THD               | $V_{DD}/V_{SS} = \pm 2.5 V, V_A = 1 V rms,$<br>$V_B = 0 V, f = 1 kHz$                                  |       | -80              |                 | dB      |

| Resistor Noise Density               | ел_wв             | Code = half scale, $T_A = 25^{\circ}$ C,<br>f = 10 kHz, $R_{AB} = 10 \text{ k}\Omega$                  |       | 7                |                 | nV/√Hz  |

| V <sub>w</sub> Settling Time         | ts                | $V_{A} = 5 V, V_{B} = 0 V, from zero scale to full scale, \pm 0.5 LSB error band, R_{AB} = 10 k\Omega$ |       | 2                |                 | μs      |

| Crosstalk (Cw1/Cw2)                  | CT                | $R_{AB} = 10 \ k\Omega$                                                                                |       | 10               |                 | nV-sec  |

| Analog Crosstalk                     | Ста               |                                                                                                        |       | -90              |                 | dB      |

| Endurance <sup>10</sup>              |                   | $T_A = 25^{\circ}C$                                                                                    |       | 1                |                 | Mcycles |

|                                      |                   | $-40^{\circ}C < T_A < +125^{\circ}C$                                                                   | 100   |                  |                 | kcycles |

| Data Retention <sup>11, 12</sup>     |                   |                                                                                                        |       | 50               |                 | Years   |

$^{1}$  Typical values represent average readings at 25°C,  $V_{\text{DD}}$  = 5 V,  $V_{\text{SS}}$  = 0 V, and  $V_{\text{LOGIC}}$  = 5 V.

<sup>2</sup> Resistor integral nonlinearity error (R-INL) is the deviation from an ideal value measured between the maximum resistance and the minimum resistance wiper positions. R-DNL measures the relative step change from ideal between successive tap positions. The maximum wiper current is limited to (0.7 × V<sub>DD</sub>)/R<sub>AB</sub>.

<sup>3</sup> Guaranteed by design and characterization, not subject to production test.

<sup>4</sup> INL and DNL are measured across the Terminal W and Terminal B voltage (V<sub>WB</sub>) with the RDAC configured as a potentiometer divider similar to a voltage output DAC.  $V_A = V_{DD}$  and  $V_B = 0$  V. DNL specification limits of ±1 LSB maximum are guaranteed monotonic operating conditions.

<sup>5</sup> Resistor Terminal A, Resistor Terminal B, and Resistor Terminal W have no limitations on polarity with respect to each other. Dual-supply operation enables ground referenced bipolar signal adjustment.

<sup>6</sup> I<sub>DD\_EEPROM\_STORE</sub> is different from the operating current. Supply current for EEPROM program lasts approximately 30 ms.

<sup>7</sup> IDD\_EEPROM\_READ is different from the operating current. Supply current for EEPROM read lasts approximately 20 µs.

<sup>8</sup> P<sub>DISS</sub> is calculated from  $(I_{DD} \times V_{DD}) + (I_{LOGIC} \times V_{LOGIC})$ .

<sup>9</sup> All dynamic characteristics use  $V_{DD}/V_{SS} = \pm 2.5$  V, and  $V_{LOGIC} = 2.5$  V.

<sup>10</sup> Endurance is qualified per JEDEC Standard 22, Method A117 to 100,000 cycles measured at -40°C to +125°C.

<sup>11</sup> Retention lifetime equivalent at junction temperature (T.) = 125°C per JEDEC Standard 22, Method A117. Retention lifetime based on an activation energy of 1 eV, derates with junction temperature in the Flash/EE memory.

<sup>12</sup> 50 years apply to an endurance of 1000 cycles. An endurance of 100,000 cycles has an equivalent retention lifetime of 5 years.

### INTERFACE TIMING SPECIFICATIONS

$V_{\text{LOGIC}}$  = 1.8 V to 5.5 V, and all specifications  $T_{\text{MIN}}$  to  $T_{\text{MAX}}$ , unless otherwise noted.

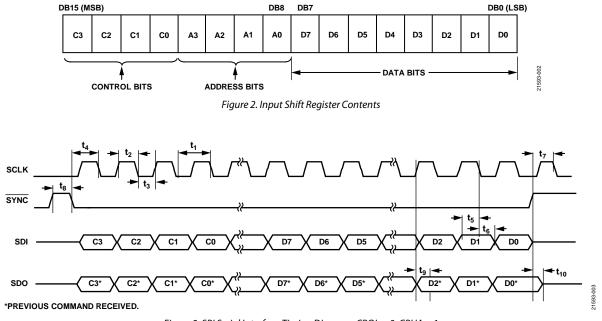

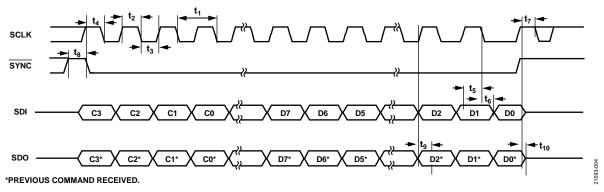

#### Table 2. SPI Interface

| Parameter <sup>1</sup>      | Test Conditions/Comments | Min | Тур | Max | Unit | Description                                        |

|-----------------------------|--------------------------|-----|-----|-----|------|----------------------------------------------------|

| t1                          | $V_{LOGIC} > 1.8 V$      | 20  |     |     | ns   | SCLK cycle time                                    |

|                             | $V_{LOGIC} = 1.8 V$      | 30  |     |     | ns   |                                                    |

| <b>t</b> <sub>2</sub>       | $V_{LOGIC} > 1.8 V$      | 10  |     |     | ns   | SCLK high time                                     |

|                             | $V_{LOGIC} = 1.8 V$      | 15  |     |     | ns   |                                                    |

| t <sub>3</sub>              | $V_{LOGIC} > 1.8 V$      | 10  |     |     | ns   | SCLK low time                                      |

|                             | $V_{LOGIC} = 1.8 V$      | 15  |     |     | ns   |                                                    |

| t4                          |                          | 10  |     |     | ns   | SYNC to SCLK falling edge setup time               |

| t <sub>5</sub>              |                          | 5   |     |     | ns   | Data setup time                                    |

| t <sub>6</sub>              |                          | 5   |     |     | ns   | Data hold time                                     |

| t <sub>7</sub>              |                          | 10  |     |     | ns   | SYNC rising edge to next SCLK fall ignored         |

| t <sub>8</sub> <sup>2</sup> |                          | 20  |     |     | ns   | Minimum SYNC high time                             |

| t <sub>9</sub> <sup>3</sup> |                          |     | 50  |     | ns   | SCLK rising edge to SDO valid                      |

| <b>t</b> 10                 |                          |     |     | 500 | ns   | SYNC rising edge to SDO pin disable                |

| tpower-up                   |                          |     |     | 75  | μs   | Start-up time (not shown in Figure 3 and Figure 4) |

<sup>1</sup> All input signals are specified with rising time ( $t_R$ ) = falling time ( $t_F$ ) = 1 ns/V (10% to 90% of  $V_{DD}$ ) and timed from a voltage level of ( $V_{LL} + V_{H}$ )/2.

<sup>2</sup> Refer to  $t_{EEPROM_PROGRAM}$  and  $t_{EEPROM_READBACK}$  for memory command operations (see the control pins table in the AD5144 data sheet for additional information). <sup>3</sup> The pull up registration (See the control pins table in the AD5144 data sheet for additional information).

$^3$  The pull-up resistance (R\_{PULL\_UP}) = 2.2 k\Omega to V\_DD with a capacitance load of 168 pF.

#### SHIFT REGISTER AND TIMING DIAGRAMS

Figure 3. SPI Serial Interface Timing Diagram, CPOL = 0, CPHA = 1

Figure 4. SPI Serial Interface Timing Diagram, CPOL = 1, CPHA = 0

### **ABSOLUTE MAXIMUM RATINGS**

$T_A = 25^{\circ}C$ , unless otherwise noted.

#### Table 3.

| Parameter                                                | Rating                                     |

|----------------------------------------------------------|--------------------------------------------|

|                                                          | 5                                          |

| V <sub>DD</sub> to GND                                   | –0.3 V to +7.0 V                           |

| V <sub>ss</sub> to GND                                   | +0.3 V to -7.0 V                           |

| V <sub>DD</sub> to V <sub>SS</sub>                       | 7 V                                        |

| V <sub>LOGIC</sub> to GND                                | -0.3 V to V <sub>DD</sub> + 0.3 V or       |

|                                                          | +7.0 V (whichever is less)                 |

| $V_A$ , $V_W$ , $V_B$ to GND                             | $V_{SS} - 0.3 V, V_{DD} + 0.3 V$           |

| I <sub>A</sub> , I <sub>W</sub> , I <sub>B</sub>         |                                            |

| Pulsed <sup>1</sup> , $R_{AW} = 10 k\Omega$              |                                            |

| Frequency > 10 kHz                                       | ±6 mA/d <sup>2</sup>                       |

| Frequency ≤ 10 kHz                                       | ±6 mA/√d²                                  |

| Digital Inputs                                           | -0.3 V to V <sub>LOGIC</sub> + 0.3 V or    |

|                                                          | +7 V (whichever is less)                   |

| Operating Temperature Range, T <sub>A</sub> <sup>3</sup> | –55°C to +125°C                            |

| Maximum Junction Temperature,                            | 150°C                                      |

| T <sub>J</sub> Maximum                                   |                                            |

| Storage Temperature Range                                | –65°C to +150°C                            |

| Reflow Soldering                                         |                                            |

| Peak Temperature                                         | 260°C                                      |

| Time at Peak Temperature                                 | 20 sec to 40 sec                           |

| Package Power Dissipation                                | (T」 max – T <sub>A</sub> )/θ <sub>JA</sub> |

| Field Induced Charged Device Model                       | 1.5 kV                                     |

| (FICDM)                                                  |                                            |

<sup>1</sup> The maximum terminal current is bounded by the maximum current handling of the switches, the maximum power dissipation of the package, and the maximum applied voltage across any two of the A, B, and W terminals at a given resistance.

$^{2}$  d = pulse duty factor.

<sup>3</sup> T<sub>A</sub> includes programming of EEPROM memory.

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

### THERMAL RESISTANCE

Thermal performance is directly linked to printed circuit board (PCB) design and operating environment. Careful attention to PCB thermal design is required.

$\theta_{JA}$  is the natural convection, junction to ambient thermal resistance measured in a one cubic foot sealed enclosure, and  $\theta_{JC}$  is the junction to case thermal resistance measured at package top.

#### Table 4. Thermal Resistance

| Package Type | $\mathbf{\Theta}_{JA}^{1}$ | οlo | Unit |

|--------------|----------------------------|-----|------|

| RU-20        | 143                        | 45  | °C/W |

<sup>1</sup> Thermal impedance simulated values are based on a JEDEC 2S2P thermal test board, still air (0 m/sec airflow). See JEDEC JESD-51.

### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

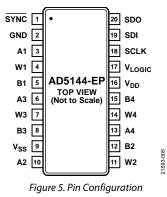

## **PIN CONFIGURATION AND FUNCTION DESCRIPTIONS**

#### **Table 5. Pin Function Descriptions**

| Pin No. | Mnemonic        | Description                                                                                                              |

|---------|-----------------|--------------------------------------------------------------------------------------------------------------------------|

| 1       | SYNC            | Synchronization Data Input, Active Low. When SYNC returns high, data is loaded into the input shift register.            |

| 2       | GND             | Ground Pin, Logic Ground Reference.                                                                                      |

| 3       | A1              | Terminal A of RDAC 1. $V_{SS} \le V_A \le V_{DD}$ .                                                                      |

| 4       | W1              | Wiper Terminal of RDAC 1. $V_{SS} \le V_W \le V_{DD}$ .                                                                  |

| 5       | B1              | Terminal B of RDAC 1. $V_{SS} \leq V_B \leq V_{DD}$ .                                                                    |

| 6       | A3              | Terminal A of RDAC 3. $V_{SS} \le V_A \le V_{DD}$ .                                                                      |

| 7       | W3              | Wiper Terminal of RDAC 3. $V_{SS} \le V_W \le V_{DD}$ .                                                                  |

| 8       | B3              | Terminal B of RDAC 3. $V_{SS} \leq V_B \leq V_{DD}$ .                                                                    |

| 9       | Vss             | Negative Power Supply. Decouple this pin with 0.1 $\mu$ F ceramic capacitors and 10 $\mu$ F capacitors.                  |

| 10      | A2              | Terminal A of RDAC 2. $V_{SS} \le V_A \le V_{DD}$ .                                                                      |

| 11      | W2              | Wiper Terminal of RDAC 2. $V_{SS} \le V_W \le V_{DD}$ .                                                                  |

| 12      | B2              | Terminal B of RDAC 2. $V_{SS} \leq V_B \leq V_{DD}$ .                                                                    |

| 13      | A4              | Terminal A of RDAC 4. $V_{SS} \le V_A \le V_{DD}$ .                                                                      |

| 14      | W4              | Wiper Terminal of RDAC 4. $V_{SS} \le V_W \le V_{DD}$ .                                                                  |

| 15      | B4              | Terminal B of RDAC 4. $V_{SS} \le V_B \le V_{DD}$ .                                                                      |

| 16      | V <sub>DD</sub> | Positive Power Supply. Decouple this pin with 0.1 $\mu$ F ceramic capacitors and 10 $\mu$ F capacitors.                  |

| 17      | VLOGIC          | Logic Power Supply, 1.8 V to $V_{DD}$ . Decouple this pin with 0.1 $\mu$ F ceramic capacitors and 10 $\mu$ F capacitors. |

| 18      | SCLK            | Serial Clock Line. Data is clocked in at the logic low transition.                                                       |

| 19      | SDI             | Serial Data Input.                                                                                                       |

| 20      | SDO             | Serial Data Output. SDO is an open-drain output pin that must have an external pull-up resistor.                         |

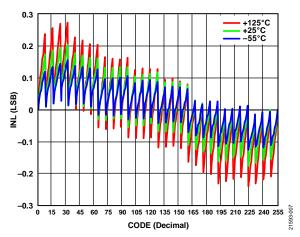

### **TYPICAL PERFORMANCE CHARACTERISTICS**

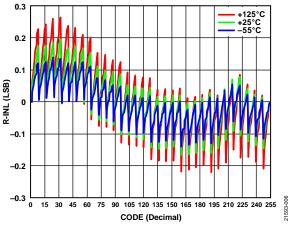

Figure 6. R-INL vs. Code for Various Temperatures

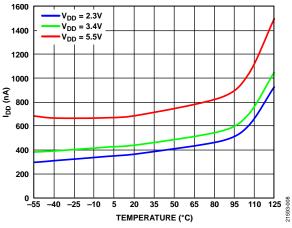

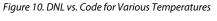

Figure 8. Supply Current (IDD) vs. Temperature for Various Power Supplies

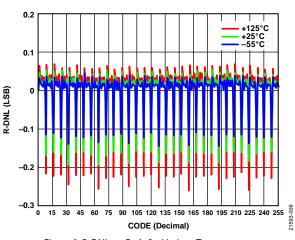

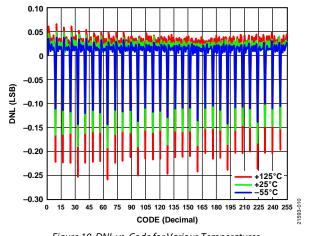

Figure 9. R-DNL vs. Code for Various Temperatures

## **Enhanced Product**

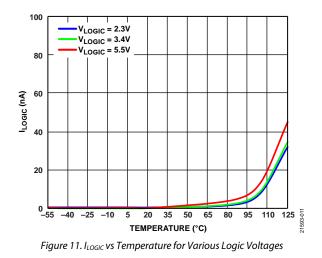

Figure 12. Potentiometer Mode Temperature Coefficient (( $\Delta V_w/V_w$ )/ $\Delta T \times 106$ ) vs. Code

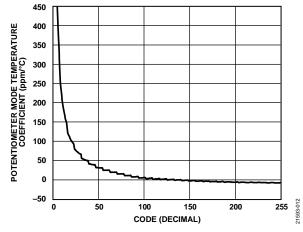

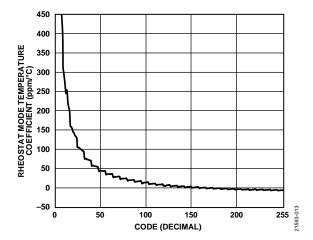

Figure 13. Rheostat Mode Temperature Coefficient (( $\Delta R_{WB}/R_{WB}$ )/ $\Delta T \times 106$ ) vs. Code

### **OUTLINE DIMENSIONS**

Dimensions shown in millimeters

### **ORDERING GUIDE**

| Model <sup>1</sup> | R <sub>AB</sub> (kΩ) | Resolution | Interface | Temperature Range | Package Description | Package Option |

|--------------------|----------------------|------------|-----------|-------------------|---------------------|----------------|

| AD5144TRUZ10-EP    | 10                   | 256        | SPI       | −55°C to +125°C   | 20-Lead TSSOP       | RU-20          |

| AD5144TRUZ10-EP-R7 | 10                   | 256        | SPI       | –55°C to +125°C   | 20-Lead TSSOP       | RU-20          |

$^{1}$  Z = RoHS Compliant Part.

©2019 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners. D21593-0-10/19(A)

www.analog.com

Rev. A | Page 11 of 11