# Please note that Cypress is an Infineon Technologies Company.

The document following this cover page is marked as "Cypress" document as this is the company that originally developed the product. Please note that Infineon will continue to offer the product to new and existing customers as part of the Infineon product portfolio.

## **Continuity of document content**

The fact that Infineon offers the following product as part of the Infineon product portfolio does not lead to any changes to this document. Future revisions will occur when appropriate, and any changes will be set out on the document history page.

# **Continuity of ordering part numbers**

Infineon continues to support existing part numbers. Please continue to use the ordering part numbers listed in the datasheet for ordering.

www.infineon.com

# Power Management IC for Automotive ADAS Platform

## Quad Buck 2.1 MHz DC/DC Converter and Dual LDO with Watchdog Timer

S6BP401A is a power management IC, consists of quad buck 2.1 MHz DC/DC converter with built-in switching FETs, dual Low Drop-out regulator (LDOs) and a digital windowed watchdog timer. Having the switching FETs built-in, S6BP401A realizes high power conversion efficiency and high switching frequency up to 2.4 MHz. The internal FETs are capable to handle up to 3 A load. As S6BP401A employs the current mode architecture, it has fast load transient response. Built-in output voltage setting resistors and compensation circuits reduce BOM cost and component area.

#### **Features**

- Quad Buck DC/DC Converter (DD1 to DD4)

- □ VIN Input Range: 4.5 V to 5.5 V

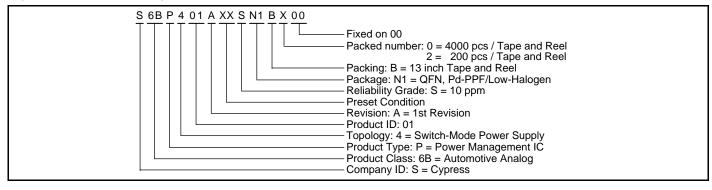

- □ Switching Frequency

- □ External clock mode: 1.8 MHz to 2.4 MHz

- □ Internal clock mode: 2.0 MHz to 2.2 MHz

- □ Built-in Switching FETs up to 3 A

- ☐ Built-in Output Voltage Setting Resistors

- □ Built-in Compensation Circuits

- ■Dual LDO (LD1, LD2)

- □ VIN Input Voltage Range: 2.97 V to 5.5 V □ Built-in Output Voltage Setting resistors

- Power Good Monitor Output for each DC/DC Converters, LDOs

- ■Built-in Windowed Watchdog Timer (WDT)

- ■Under Voltage Lockout (UVLO)

- ■Thermal Shutdown (TSD)

- Over Current Protection (OCP)

- Over Voltage Protection (OVP)

- ■Independent Enabling for each DC/DC Converters and LDOs

- ■Load-independent Soft-Start

- ■Built-in Discharge Resistors

- ■Small 6 mm × 6 mm QFN-40 Package

- ■AEC-Q100 compliant (Grade-1)

# **Applications**

- Automotive Applications

- Advanced Driver Assistance Systems (ADAS)

- ■Camera Systems such as Security Camera

- Industrial Applications

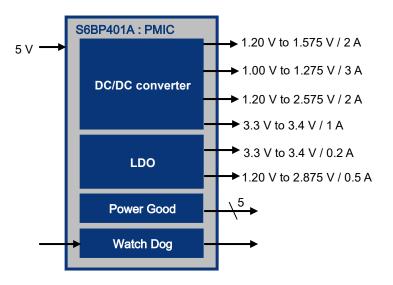

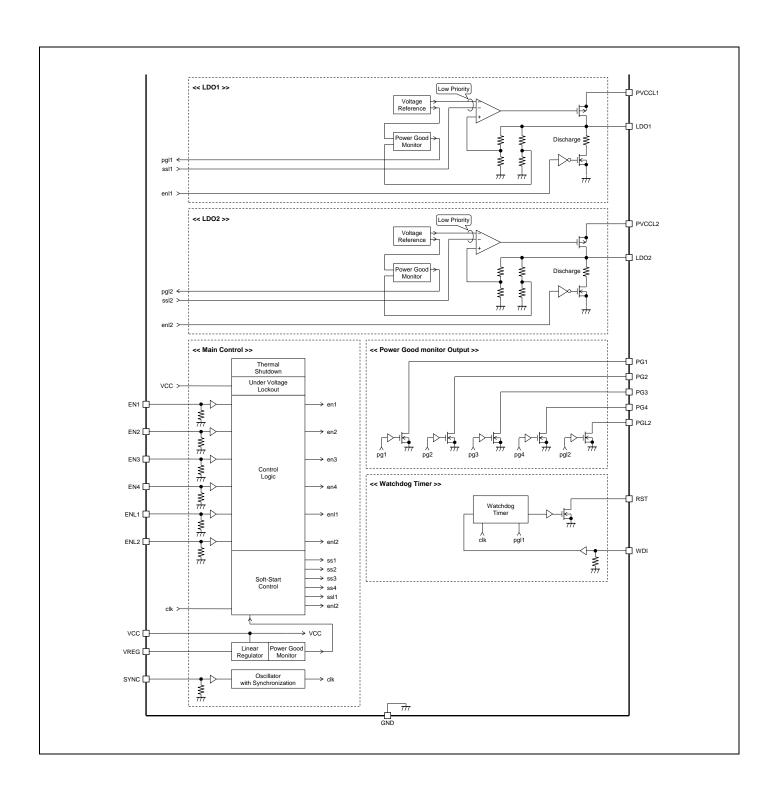

## **Block Diagram**

#### More Information

Cypress provides a wealth of data at <a href="https://www.cypress.com/pmic">www.cypress.com/pmic</a> to help you to select the right PMIC device for your design, and to help you to quickly and effectively integrate the device into your design. Following is an abbreviated list for S6BP401A:

- Overview: Automotive PMIC Portfolio, Automotive PMIC Roadmap

- Product Selector:

□ S6BP401A: 6 ch Automotive PMIC for ADAS

- Application Notes: Cypress offers S6BP401A application notes. Recommended application notes for getting started with S6BP401A are:

- □ AN98649: How to Design a Power Management System □ AN201006: Thermal Considerations and Parameters

- ■Evaluation Kit Operation Manual:

- □ S6SBP401AM2SA1001: Power block for automotive ADAS platform

- ■Related Products:

- □ S6BP201A, S6BP202A, S6BP203A:

- 1 ch Buck-Boost Automotive PMIC

- □ S6BP501A, S6BP502A:

- 3 ch Automotive PMIC for Instrument Cluster

Document Number: 002-03341 Rev.\*I Page 2 of 41

## **Contents**

| reat | tures                                      | 1  |

|------|--------------------------------------------|----|

| App  | olications                                 | 1  |

| Bloc | ck Diagram                                 | 1  |

| More | e Information                              | 2  |

| 1.   | Typical Application                        | 4  |

| 2.   | Pin Configuration                          | 5  |

| 3.   | Pin Functions                              | 6  |

| 4.   | Preset Output Voltage                      | 7  |

| 5.   | Architecture Block Diagram                 | 9  |

| 6.   | Absolute Maximum Ratings                   | 11 |

| 7.   | Recommended Operating Conditions           | 12 |

| 8.   | Electrical Characteristics                 | 13 |

| 9.   | Operating Mode List                        | 18 |

| 10.  | Function                                   | 19 |

| 10.1 | Turning ON and OFF Sequence                | 19 |

| 10.2 | 2 Over Current Protection                  | 21 |

| 10.3 | 3 Over Voltage Protection                  | 21 |

| 10.4 | 1 Thermal Shutdown (TSD)                   | 22 |

| 10.5 | 5 Under Voltage Lockout (UVLO)             | 22 |

| 10.6 | S Soft-Start Operation                     | 22 |

| 10.7 | 7 Discharge Operation                      | 23 |

| 10.8 | Power Good Monitor and Reset Function      | 24 |

| 10.9 | 9 Watchdog Timer                           | 26 |

| 10.1 | 10 Internal Linear Regulator Output (VREG) | 29 |

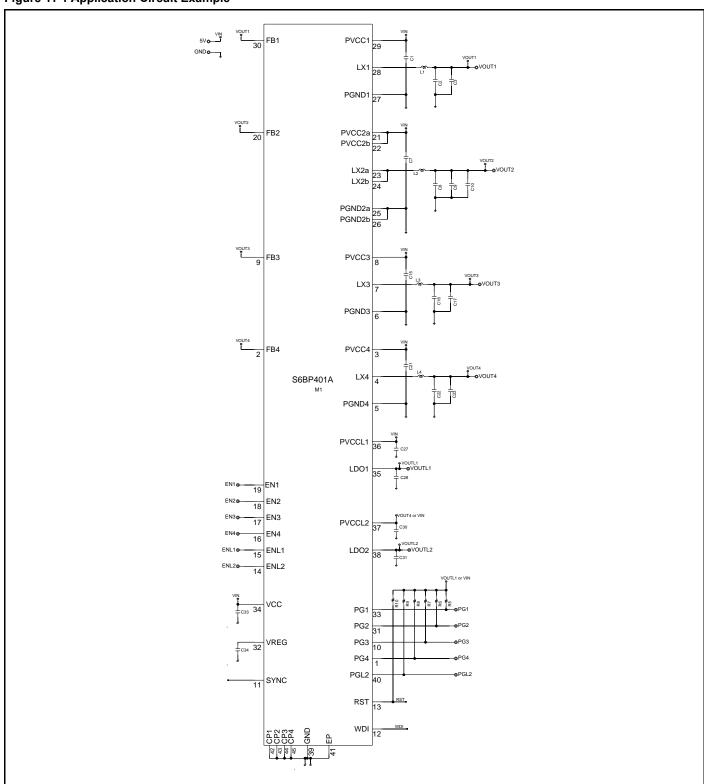

| 11.  | Application Circuit Example                | 30 |

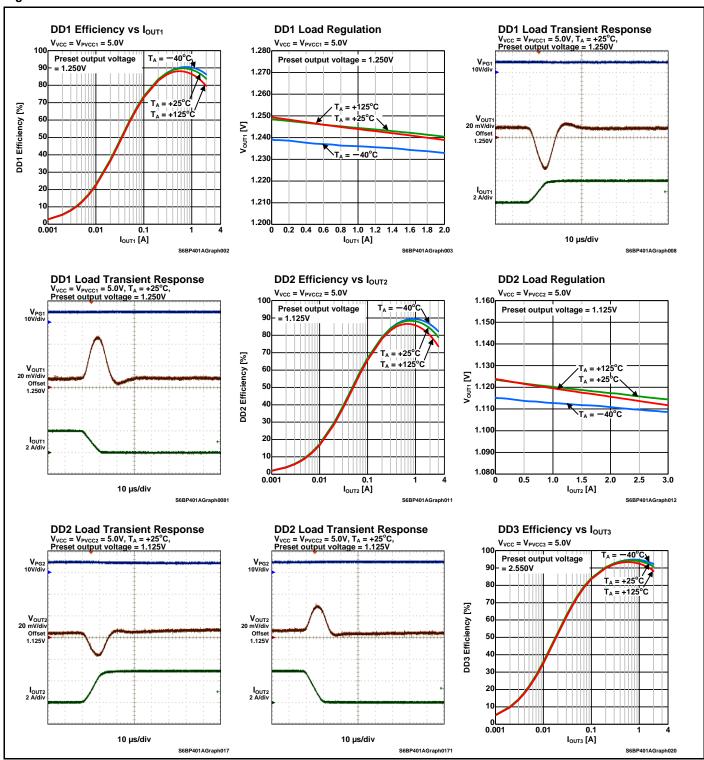

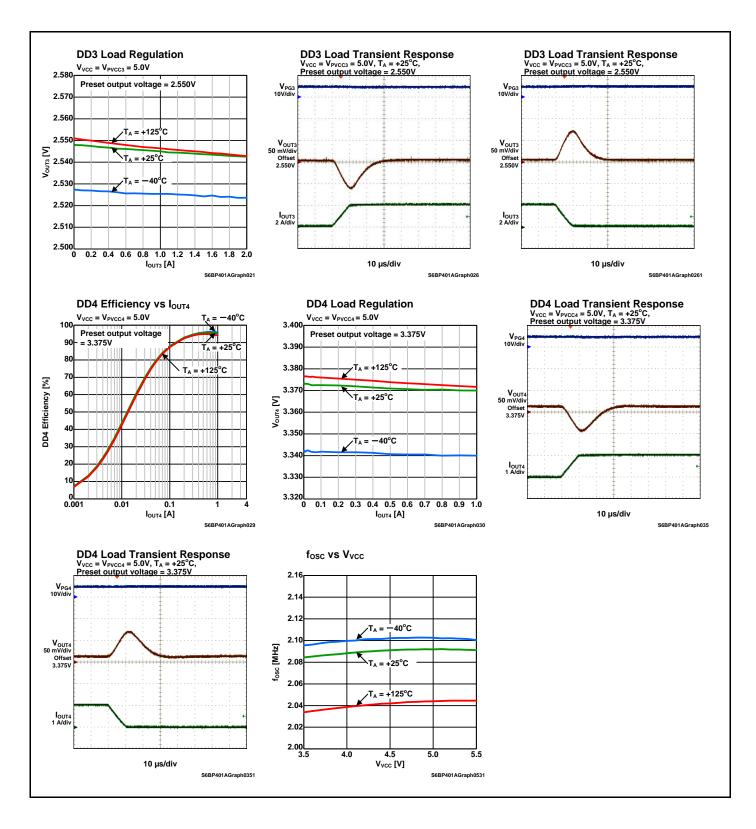

| 12.  | Reference Data                             | 32 |

| 13.  | Ordering Information                       | 35 |

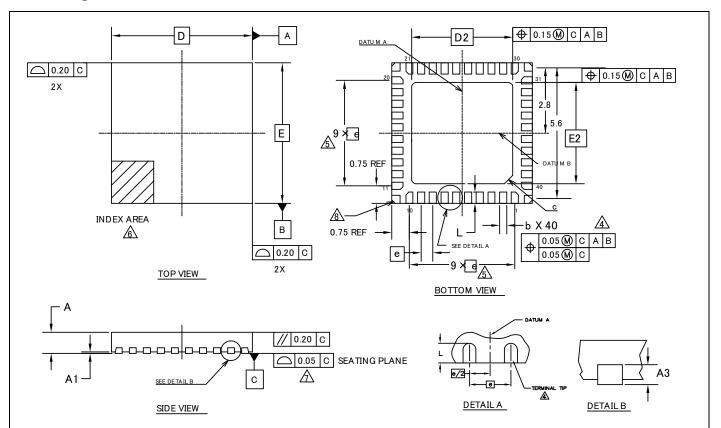

| 14.  | Package Dimensions                         | 36 |

| 15.  | Major Changes                              | 37 |

| Doc  | ument History                              | 38 |

# 1. Typical Application

Figure 1-1 Typical Application

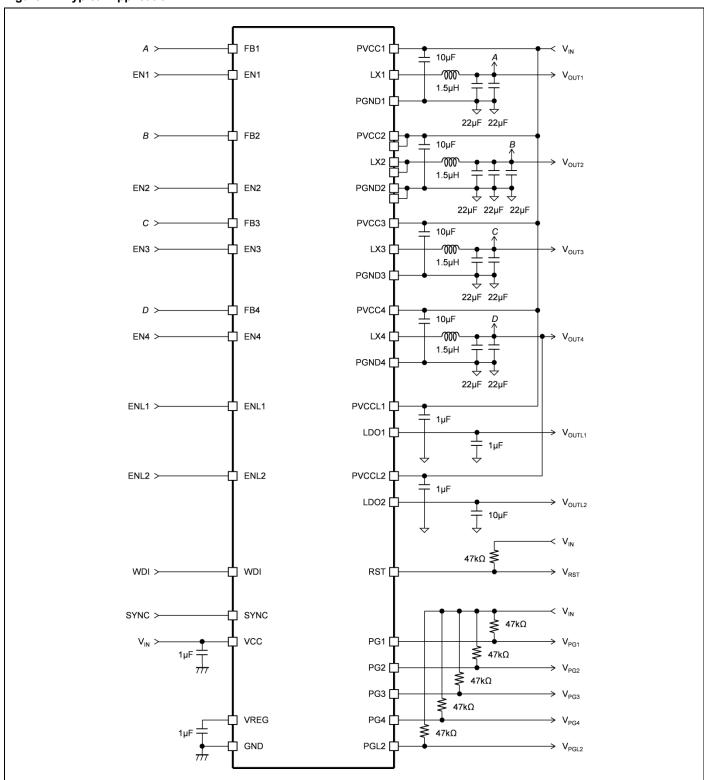

# 2. Pin Configuration

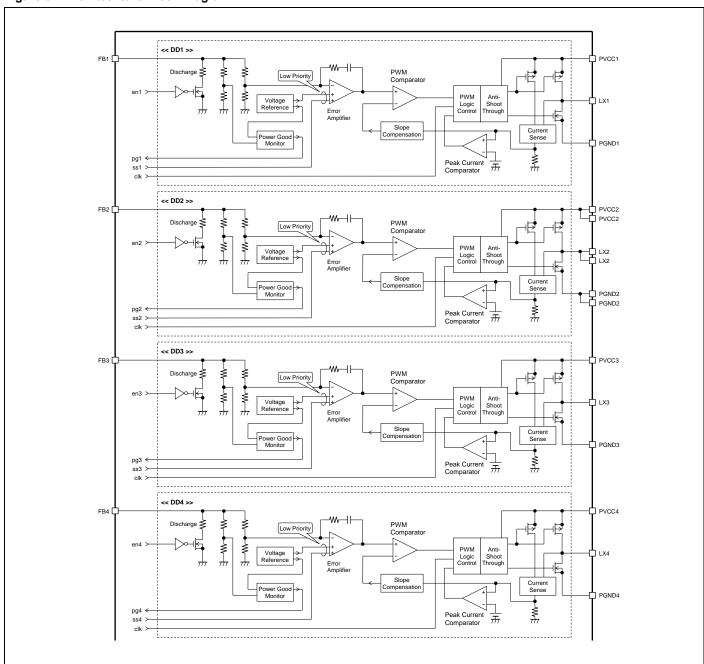

Figure 2-1 Pin Configuration

## 3. Pin Functions

**Table 3-1 Pin Functions**

| Functional Block | Pin Number            | Pin Name | I/O | Description                                                                                       | Pin Setting When Not Being Used |

|------------------|-----------------------|----------|-----|---------------------------------------------------------------------------------------------------|---------------------------------|

|                  | 19                    | EN1      | -   | Enable input terminal of DD1.                                                                     | Ground                          |

|                  | 30                    | FB1      | I   | Output voltage feedback terminal of DD1.                                                          | Ground                          |

| DD4              | 33                    | PG1      | 0   | Power good output terminal of DD1.                                                                | Ground                          |

| DD1              | 29                    | PVCC1    | -   | Power supply terminal of DD1.                                                                     | VCC                             |

|                  | 28                    | LX1      | 0   | Inductor connect terminal of DD1.                                                                 | Leave pin open                  |

|                  | 27                    | PGND1    | -   | Power ground terminal of DD1.                                                                     | Ground                          |

|                  | 18                    | EN2      | I   | Enable input terminal of DD2.                                                                     | Ground                          |

|                  | 20                    | FB2      | I   | Output voltage feedback terminal of DD2.                                                          | Ground                          |

| DDO              | 31                    | PG2      | 0   | Power good output terminal of DD2.                                                                | Ground                          |

| DD2              | 21, 22                | PVCC2    | -   | Power supply terminal of DD2.                                                                     | VCC                             |

|                  | 23, 24                | LX2      | 0   | Inductor connect terminal of DD2.                                                                 | Leave pin open                  |

|                  | 25, 26                | PGND2    | -   | Power ground terminal of DD2.                                                                     | Ground                          |

|                  | 17                    | EN3      | - 1 | Enable input terminal of DD3.                                                                     | Ground                          |

|                  | 9                     | FB3      | I   | Output voltage feedback terminal of DD3.                                                          | Ground                          |

| DDO              | 10                    | PG3      | 0   | Power good output terminal of DD3.                                                                | Ground                          |

| DD3              | 8                     | PVCC3    | -   | Power supply terminal of DD3.                                                                     | VCC                             |

|                  | 7                     | LX3      | 0   | Inductor connect terminal of DD3.                                                                 | Leave pin open                  |

|                  | 6                     | PGND3    | -   | Power ground terminal of DD3.                                                                     | Ground                          |

|                  | 16                    | EN4      | I   | Enable input terminal of DD4.                                                                     | Ground                          |

|                  | 2                     | FB4      | I   | Output voltage feedback terminal of DD4.                                                          | Ground                          |

| 554              | 1                     | PG4      | 0   | Power good output terminal of DD4.                                                                | Ground                          |

| DD4              | 3                     | PVCC4    | -   | Power supply terminal of DD4.                                                                     | VCC                             |

|                  | 4                     | LX4      | 0   | Inductor connect terminal of DD4.                                                                 | Leave pin open                  |

|                  | 5                     | PGND4    | -   | Power ground terminal of DD4.                                                                     | Ground                          |

|                  | 15                    | ENL1     | - 1 | Enable input terminal of LD1.                                                                     | Ground                          |

| LD1              | 36                    | PVCCL1   | -   | Power supply terminal of LD1.                                                                     | VCC                             |

|                  | 35                    | LDO1     | 0   | Output terminal of LD1.                                                                           | Leave pin open                  |

|                  | 14                    | ENL2     | I   | Enable input of LD2.                                                                              | Ground                          |

| 1.00             | 40                    | PGL2     | 0   | Power good output terminal of LD2.                                                                | Ground                          |

| LD2              | 37                    | PVCCL2   | -   | Power supply terminal of LD2.                                                                     | VCC                             |

|                  | 38                    | LDO2     | 0   | Output terminal of LD2.                                                                           | Leave pin open                  |

| WDT              | 12                    | WDI      | I   | Trigger input terminal of WDT.                                                                    | Ground                          |

| WDT              | 13                    | RST      | 0   | Reset input terminal of WDT.                                                                      | Ground                          |

| SYNC             | 11                    | SYNC     | I   | External clock input terminal.                                                                    | Ground                          |

| -                | 34                    | VCC      | -   | Power supply terminal for analog controller.                                                      | -                               |

| -                | 32                    | VREG     | 0   | Internal 1.8 V supply voltage capacitor terminal. Do NOT supply or load this terminal externally. | -                               |

| -                | 39                    | GND      | -   | Ground terminal for analog controller.                                                            | -                               |

| -                | EP                    | EP       | -   | Exposed pad. Connect to ground plane.                                                             | -                               |

| -                | CP1, CP2,<br>CP3, CP4 | СР       | -   | Corner pad for reinforcing attachment to a board. Connect to ground plane.                        |                                 |

# 4. Preset Output Voltage

Table 4-1 Preset Output Voltage (Buck DC/DC Converter)

| Channel | Preset Output<br>Voltage [V] | Soft-start Time [ms] | Maximum Output<br>Current [mA] | Under Voltage<br>Threshold [%] | Over Voltage<br>Threshold [%] |

|---------|------------------------------|----------------------|--------------------------------|--------------------------------|-------------------------------|

|         | 1.200                        | 1.200                |                                |                                |                               |

|         | 1.225                        | 1.225                |                                |                                |                               |

|         | 1.250                        | 1.250                |                                |                                |                               |

|         | 1.275                        | 1.275                |                                |                                |                               |

| DD1     | 1.300                        | 1.300                | 2000                           | 94.0                           | 106.0                         |

| וטט     | 1.325                        | 1.325                | 2000                           | 94.0                           | 100.0                         |

|         | 1.500                        | 1.500                |                                |                                |                               |

|         | 1.525                        | 1.525                |                                |                                |                               |

|         | 1.550                        | 1.550                |                                |                                |                               |

|         | 1.575                        | 1.575                | 1.575                          |                                |                               |

|         | 1.000                        | 1.000                |                                |                                |                               |

|         | 1.025                        | 1.025                |                                |                                |                               |

|         | 1.050                        | 1.050                |                                |                                |                               |

|         | 1.075                        | 1.075                |                                |                                |                               |

|         | 1.100                        | 1.100                |                                |                                |                               |

| DD2     | 1.125                        | 1.125                | 2000                           | 94.0                           | 106.0                         |

| DDZ     | 1.150                        | 1.150                | 3000                           |                                | 100.0                         |

|         | 1.175                        | 1.175                |                                |                                |                               |

|         | 1.200                        | 1.200                |                                |                                |                               |

|         | 1.225                        | 1.225                |                                |                                |                               |

|         | 1.250                        | 1.250                |                                |                                |                               |

|         | 1.275                        | 1.275                |                                |                                |                               |

|         | 1.200                        | 1.200                |                                |                                |                               |

|         | 1.225                        | 1.225                |                                |                                |                               |

|         | 1.250                        | 1.250                |                                |                                |                               |

|         | 1.275                        | 1.275                |                                |                                |                               |

|         | 1.500                        | 1.500                |                                |                                |                               |

|         | 1.525                        | 1.525                |                                |                                |                               |

|         | 1.550                        | 1.550                |                                |                                |                               |

| DD3     | 1.575                        | 1.575                | 2000                           | 95.2                           | 106.0                         |

| DD3     | 1.800                        | 1.800                | 2000                           | 95.2                           | 100.0                         |

|         | 1.825                        | 1.825                |                                |                                |                               |

|         | 1.850                        | 1.850                |                                |                                |                               |

|         | 1.875                        | 1.875                |                                |                                |                               |

|         | 2.500                        | 2.500                |                                |                                |                               |

|         | 2.525                        | 2.525                |                                |                                |                               |

|         | 2.550                        | 2.550                |                                |                                |                               |

|         | 2.575                        | 2.575                |                                |                                |                               |

|         | 3.300                        | 3.300                |                                |                                |                               |

|         | 3.325                        | 3.325                |                                |                                |                               |

| DD4     | 3.350                        | 3.350                | 1000                           | 95.5                           | 106.0                         |

|         | 3.375                        | 3.375                |                                |                                |                               |

|         | 3.400                        | 3.400                |                                |                                |                               |

#### Notes:

Document Number: 002-03341 Rev.\*I Page 7 of 41

Soft-start time values are at fosc = 2.1 MHz

See 8. Electrical Characteristics for the minimum or maximum values of output voltage, under voltage threshold and over voltage threshold.

Table 4-2 Preset Output Voltage (LDO)

| Channel | Preset Output<br>Voltage [V] | Soft-start Time<br>[ms] | Maximum Output<br>Current [mA] | Under Voltage<br>Threshold [%] | Over Voltage<br>Threshold [%] |  |

|---------|------------------------------|-------------------------|--------------------------------|--------------------------------|-------------------------------|--|

|         | 3.300                        | 3.300                   |                                |                                |                               |  |

|         | 3.325                        | 3.325                   |                                |                                |                               |  |

| LD1     | 3.350                        | 3.350                   | 200                            | 94.0                           | 106.0                         |  |

|         | 3.375                        | 3.375                   |                                |                                |                               |  |

|         | 3.400                        | 3.400                   |                                |                                |                               |  |

|         | 1.200                        | 1.200                   |                                |                                |                               |  |

|         | 1.225                        | 1.225                   |                                |                                |                               |  |

|         | 1.250                        | 1.250                   |                                |                                |                               |  |

|         | 1.275                        | 1.275                   |                                |                                |                               |  |

|         | 1.800                        | 1.800                   |                                |                                |                               |  |

| LD2     | 1.825                        | 1.825                   | 500                            | 04.0                           | 400.0                         |  |

| LD2     | 1.850                        | 1.850                   | 500                            | 94.0                           | 106.0                         |  |

|         | 1.875                        | 1.875                   |                                |                                |                               |  |

|         | 2.800                        | 2.800                   |                                |                                |                               |  |

|         | 2.825                        | 2.825                   |                                |                                |                               |  |

|         | 2.850                        | 2.850                   |                                |                                |                               |  |

|         | 2.875                        | 2.875                   |                                |                                |                               |  |

#### Notes:

<sup>-</sup> Soft-start time values are at fosc = 2.1 MHz

See 8. Electrical Characteristics for the minimum or maximum values of output voltage, under voltage threshold and over voltage threshold.

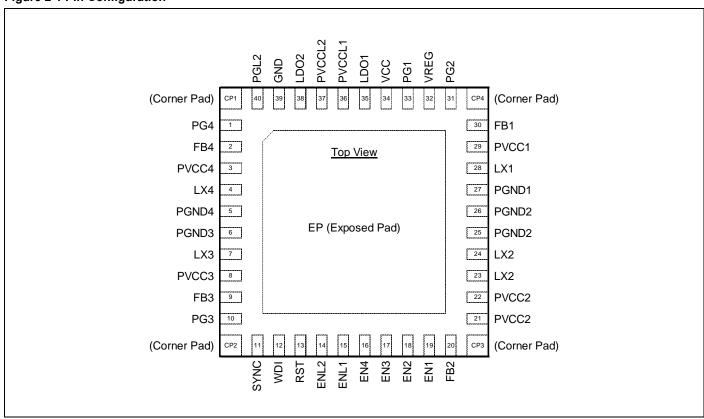

# 5. Architecture Block Diagram

Figure 5-1 Architechture Block Diagram

## 6. Absolute Maximum Ratings

**Table 6-1 Absolute Maximum Ratings**

| Parameter            | Symbol                | Condition                                                                                                              | Rat  | ting | Unit  |

|----------------------|-----------------------|------------------------------------------------------------------------------------------------------------------------|------|------|-------|

| Parameter            | Syllibol              | Condition                                                                                                              | Min  | Max  | Offic |

|                      | Vvcc                  | VCC                                                                                                                    | -0.3 | +6.9 | V     |

| Power supply voltage | V <sub>P</sub> VCC    | PVCC1, PVCC2, PVCC3, PVCC4                                                                                             | -0.3 | +6.9 | V     |

|                      | VPVCCL                | PVCCL1, PVCCL2                                                                                                         | -0.3 | +6.9 | V     |

|                      | V <sub>EN</sub>       | EN1, EN2, EN3, EN4, ENL1, ENL2                                                                                         | -0.3 | +6.9 | V     |

|                      | V <sub>WDI</sub>      | WDI                                                                                                                    | -0.3 | +6.9 | V     |

| lancit valtana       | Vsync                 | SYNC                                                                                                                   | -0.3 | +6.9 | V     |

| Input voltage        | V <sub>FB</sub>       | FB1, FB2, FB3, FB4                                                                                                     | -0.3 | +6.9 | V     |

|                      | V <sub>PG</sub>       | PG1, PG2, PG3, PG4, PGL2                                                                                               | -0.3 | +6.9 | V     |

|                      | V <sub>RST</sub>      | RST                                                                                                                    | -0.3 | +6.9 | V     |

| LX voltage           | V <sub>L</sub> X      | LX1, LX2, LX3, LX4                                                                                                     | -0.3 | +6.9 | V     |

|                      | V <sub>PVCC-VCC</sub> | PVCC1 -VCC, PVCC2-VCC,<br>PVCC3-VCC, PVCC4-VCC                                                                         | -0.3 | +0.3 | V     |

|                      | V <sub>PGND-GND</sub> | PGND1-GND, PGND2-GND,<br>PGND3-GND, PGND4-GND                                                                          | -0.3 | +0.3 | V     |

| Voltage difference   | V <sub>PVCC-LX</sub>  | PVCC1-LX1, PVCC2-LX2,<br>PVCC3-LX3, PVCC4-LX4                                                                          | -0.3 | +6.9 | V     |

|                      | Vvcc-INPUT            | VCC-EN1, VCC-EN2, VCC-EN3,<br>VCC-EN4, VCC-EN1L, VCC-EN2L,<br>VCC-WDI, VCC-SYNC, VCC-FB1,<br>VCC-FB2, VCC-FB3, VCC-FB4 | -0.3 | +6.9 | V     |

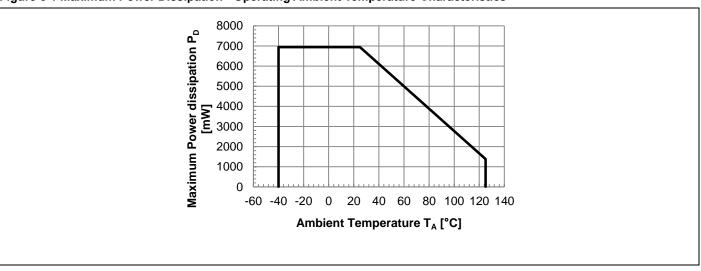

| Power dissipation    | P <sub>D</sub>        | $T_A \le +25$ °C,<br>Thermal resistance ( $\theta_{JA}$ ): 18 °C /W (*1)                                               |      | 6940 | mW    |

| Junction temperature | TJ                    | -                                                                                                                      | -40  | +150 | °C    |

| Storage temperature  | T <sub>STG</sub>      | -                                                                                                                      | -55  | +150 | °C    |

<sup>\*1:</sup> When the IC is mounted on 76.2 mm × 114.3 mm four-layer epoxy board. IC is mounted on a four-layer epoxy board, which terminal bias, and the IC's thermal pad is connected to the epoxy board.

#### **WARNING**

1. Semiconductor devices may be permanently damaged by application of stress (including, without limitation, voltage, current or temperature) in excess of absolute maximum ratings. Do not exceed any of these ratings.

Figure 6-1 Maximum Power Dissipation - Operating Ambient Temperature Characteristics

Document Number: 002-03341 Rev.\*I Page 11 of 41

## 7. Recommended Operating Conditions

**Table 7-1 Recommended Operating Conditions**

|                               |                     |                                |       | Value |      | 11. 14 |

|-------------------------------|---------------------|--------------------------------|-------|-------|------|--------|

| Parameter                     | Symbol              | Condition                      | Min   | Тур   | Max  | Unit   |

|                               | Vvcc                | VCC                            | +4.5  | +5.0  | +5.5 | V      |

| Power supply voltage          | V <sub>P</sub> VCC  | PVCC1, PVCC2, PVCC3, PVCC4     | -     | Vvcc  | -    | V      |

|                               | V <sub>P</sub> VCCL | PVCCL1, PVCCL2                 | +2.97 | +5.0  | Vvcc | V      |

|                               | V <sub>EN</sub>     | EN1, EN2, EN3, EN4, ENL1, ENL2 | 0     | -     | Vvcc | V      |

|                               | V <sub>WDI</sub>    | WDI                            | 0     | -     | Vvcc | V      |

| lanut valtaria                | Vsync               | SYNC                           | 0     | -     | Vvcc | V      |

| Input voltage                 | V <sub>FB</sub>     | FB1, FB2, FB3, FB4             | 0     | -     | Vvcc | V      |

|                               | V <sub>PG</sub>     | PG1, PG2, PG3, PG4, PGL2       | 0     | -     | +5.5 | V      |

|                               | V <sub>RST</sub>    | RST                            | 0     | -     | +5.5 | V      |

| Operating ambient temperature | TA                  | -                              | -40   | +25   | +125 | °C     |

#### **WARNING:**

- 1. The recommended operating conditions are required in order to ensure the normal operation of the semiconductor device. All of the device's electrical characteristics are warranted when the device is operated under these conditions.

- 2. Any use of semiconductor devices will be under their recommended operating condition.

- 3. Operation under any conditions other than these conditions may adversely affect reliability of device and could result in device failure

- 4. No warranty is made with respect to any use, operating conditions or combinations not represented on this data sheet. If you are considering application under any conditions other than listed herein, please contact sales representatives beforehand.

Document Number: 002-03341 Rev.\*I Page 12 of 41

## 8. Electrical Characteristics

$V_{VCC} = V_{PVCC} = 5.0 \text{ V}, V_{PVCCL} = 5.0 \text{ V}, T_A = T_J = -40 \text{ to } +125 \text{ °C}, \text{ unless otherwise noted.}$  Typical values are at  $T_A = +25 \text{ °C}.$

**Table 8-1 Electrical Characteristics**

| Davamatan               | Cumbal               | Condition                                                                                                                              |      | Value    |                  |      |  |

|-------------------------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------|------|----------|------------------|------|--|

| Parameter               | Symbol               | Condition                                                                                                                              | Min  | Тур      | Max              | Unit |  |

| Supply Current          |                      |                                                                                                                                        |      |          |                  |      |  |

| Shutdown current        | Ivccs                | VCC pin,<br>V <sub>EN1</sub> = V <sub>EN2</sub> = V <sub>EN3</sub> = V <sub>EN4</sub> = V <sub>ENL1</sub> =<br>V <sub>ENL2</sub> = 0 V | -    | 1        | 10               | μΑ   |  |

| UVLO: Under Voltage L   | ockout (VC           | CC)                                                                                                                                    |      |          |                  |      |  |

| Threshold voltage       | Vuvlof               | V <sub>VCC</sub> falling, UVLO stop voltage                                                                                            | 3.80 | 3.95     | 4.10             | V    |  |

| Hysteresis              | V <sub>UVHYS</sub>   | -                                                                                                                                      | 0.27 | 0.30     | 0.33             | V    |  |

| TSD: Thermal Shutdow    | /n                   |                                                                                                                                        | · L  |          |                  |      |  |

| Shutdown temperature    | T <sub>TSD</sub>     | Temperature rising                                                                                                                     | -    | 165 (*1) | -                | °C   |  |

| Hysteresis              | T <sub>TSDHYS</sub>  | -                                                                                                                                      | -    | 10 (*1)  | -                | °C   |  |

| Enable Inputs (EN1, EN  |                      | 4, ENL1, ENL2)                                                                                                                         | I    | \ /      |                  |      |  |

| Input high voltage      | V <sub>IHEN</sub>    | -                                                                                                                                      | 2.0  | -        | V <sub>VCC</sub> | V    |  |

| Input low voltage       | VILEN                | -                                                                                                                                      | 0    | -        | 0.4              | V    |  |

| Input current           | I <sub>IHEN</sub>    | V <sub>EN</sub> = 5.0 V                                                                                                                | 33   | 50       | 100              | μA   |  |

| Pull down resistance    | R <sub>PDEN</sub>    | -                                                                                                                                      | 50   | 100      | 150              | kΩ   |  |

| Internal Linear Regulat | or Output (          | VREG)                                                                                                                                  | II.  | -        |                  |      |  |

| Output voltage          | Vvreg                | V <sub>VCC</sub> = 5.0 V                                                                                                               | 1.74 | 1.80     | 1.86             | V    |  |

| Maximum output current  | Ivreg                | Vvcc = 5.0 V                                                                                                                           | 5    | -        | -                | mA   |  |

| Over voltage lockout    | Vvregovr             | V <sub>VREG</sub> rising, Power fail                                                                                                   | 1.86 | 1.92     | 1.98             | V    |  |

| threshold               | V <sub>VREGOVF</sub> | V <sub>VREG</sub> falling, Power good                                                                                                  | 1.81 | 1.87     | 1.93             | V    |  |

| Under voltage lockout   | V <sub>VREGUVR</sub> | V <sub>VREG</sub> rising, Power good                                                                                                   | 1.67 | 1.73     | 1.79             | V    |  |

| threshold               | V <sub>VREGUVF</sub> | V <sub>VREG</sub> falling, Power fail                                                                                                  | 1.62 | 1.68     | 1.74             | V    |  |

| Oscillator              |                      |                                                                                                                                        |      |          |                  |      |  |

| Switching frequency     | fosc                 | -                                                                                                                                      | 2.0  | 2.1      | 2.2              | MHz  |  |

| Synchronization Input   | (SYNC)               |                                                                                                                                        |      |          |                  |      |  |

| Input high voltage      | VIHSYNC              | -                                                                                                                                      | 2.0  | -        | Vvcc             | V    |  |

| Input Low voltage       | VILSYNC              | -                                                                                                                                      | 0    | -        | 0.4              | V    |  |

| Input current           | IIHSYNC              | V <sub>EN</sub> = 5.0 V                                                                                                                | 33   | 50       | 100              | μA   |  |

| Pull down resistance    | RPDSYNC              | -                                                                                                                                      | 50   | 100      | 150              | kΩ   |  |

| Input frequency         | fsync                | -                                                                                                                                      | 1.8  | 2.1      | 2.4              | MHz  |  |

| Switching frequency     | fosc                 | -                                                                                                                                      | -    | fsync    | -                | MHz  |  |

Document Number: 002-03341 Rev.\*I Page 13 of 41

| Borometer                            | Cumbal               | Condition                                                                                          |       | l Init         |                |          |

|--------------------------------------|----------------------|----------------------------------------------------------------------------------------------------|-------|----------------|----------------|----------|

| Parameter                            | Symbol Condition     |                                                                                                    | Min   | Тур            | Max            | Unit     |

| <b>Power Good Monitor (</b>          | PG1, PG2, F          | PGL2)                                                                                              |       |                |                |          |

| Over voltage                         | VPGOV                | Ratio of power fail threshold to Vout1, Vout2,                                                     | 104.5 | 106.0          | 107.5          | %        |

| threshold                            | V PGOV               | Voutl2 rising                                                                                      | 104.5 | 100.0          | 107.5          | 70       |

| Over voltage                         | V <sub>PGOVHYS</sub> | -                                                                                                  | 0.5   | 1.0            | 1.5            | %        |

| hysteresis                           |                      | Detic of new or fell through old to \/                                                             |       |                |                |          |

| Under voltage<br>threshold           | V <sub>PGUV</sub>    | Ratio of power fail threshold to V <sub>OUT1</sub> , V <sub>OUT2</sub> , V <sub>OUT3</sub> falling | 92.5  | 94.0           | 95.5           | %        |

| Under voltage hysteresis             | V <sub>PGUVHYS</sub> | -                                                                                                  | 0.5   | 1.0            | 1.5            | %        |

| Leakage current                      | I <sub>LEAKPG</sub>  | $V_{PG} = 5.0 \text{ V}$                                                                           | -     | -              | 1              | μΑ       |

| Output low voltage                   | Volpg                | I <sub>PG</sub> = 3 mA                                                                             | -     | 0.15           | 0.30           | V        |

| Propagation time                     | $T_{PPG}$            | 5 % outside of the threshold, Power fail                                                           | -     | 4 (*1)         | 8 (*1)         | μs       |

| Power-on reset time                  | $T_{RPG}$            | Power good                                                                                         | 8     | 10             | 12             | ms       |

| Power Good Monitor (                 | PG3)                 | -                                                                                                  |       |                |                |          |

| Over voltage threshold               | V <sub>PGOV</sub>    | Ratio of power fail threshold to V <sub>OUT3</sub> rising                                          | 104.5 | 106.0          | 107.5          | %        |

| Over voltage hysteresis              | Vpgovhys             | -                                                                                                  | 0.5   | 1.0            | 1.5            | %        |

| Under voltage<br>threshold           | V <sub>PGUV</sub>    | Ratio of power fail threshold to V <sub>OUT3</sub> falling                                         | 93.7  | 95.2           | 96.7           | %        |

| Under voltage<br>hysteresis          | VPGUVHYS             | -                                                                                                  | 0.5   | 1.0            | 1.5            | %        |

| Leakage current                      | ILEAKPG              | V <sub>PG</sub> = 5.0 V                                                                            | _     | _              | 1              | пΛ       |

| Output low voltage                   | VOLPG                | I <sub>PG</sub> = 3 mA                                                                             | -     | 0.15           | 0.30           | μA<br>V  |

| Propagation time                     | TPPG                 | 5 % outside of the threshold, Power fail                                                           |       | 4 (*1)         | 8 (*1)         | •        |

| Power-on reset time                  | TRPG                 | Power good                                                                                         | 8     | 10             | 12             | μs       |

| Power Good Monitor (                 |                      | Fower good                                                                                         | 0     | 10             | 12             | ms       |

| ,                                    | PG4)                 | T T                                                                                                |       | I              | 1              |          |

| Over voltage threshold               | V <sub>PGOV</sub>    | Ratio of power fail threshold to V <sub>OUT4</sub> rising                                          | 104.5 | 106.0          | 107.5          | %        |

| Over voltage hysteresis              | V <sub>PGOVHYS</sub> | -                                                                                                  | 0.5   | 1.0            | 1.5            | %        |

| Under voltage threshold              | V <sub>PGUV</sub>    | Ratio of power fail threshold to V <sub>OUT4</sub> falling                                         | 94.0  | 95.5           | 97.0           | %        |

| Under voltage hysteresis             | VPGUVHYS             | -                                                                                                  | 0.5   | 1.0            | 1.5            | %        |

| Leakage current                      | I <sub>LEAKPG</sub>  | V <sub>PG</sub> = 5.0 V                                                                            | -     | -              | 1              | μΑ       |

| Output low voltage                   | Volpg                | $I_{PG} = 3 \text{ mA}$                                                                            | -     | 0.15           | 0.30           | V        |

| Propagation time                     | $T_{PPG}$            | 5 % outside of the threshold, Power fail                                                           | -     | 4 (*1)         | 8 (*1)         | μs       |

| Power-on reset time                  | T <sub>RPG</sub>     | Power good                                                                                         | 8     | 10             | 12             | ms       |

| Reset (RST)                          |                      |                                                                                                    |       |                |                | _        |

| Over voltage threshold               | V <sub>RSOV</sub>    | Ratio of power fail threshold to V <sub>OUTL1</sub> rising                                         | 104.5 | 106.0          | 107.5          | %        |

| Over voltage hysteresis              | Vrsovhys             | -                                                                                                  | 0.5   | 1.0            | 1.5            | %        |

| Under voltage<br>threshold           | V <sub>RSUV</sub>    | Ratio of power fail threshold to V <sub>OUTL1</sub> falling                                        | 92.5  | 94.0           | 95.5           | %        |

| Under voltage<br>hysteresis          | VRSUVHYS             | -                                                                                                  | 0.5   | 1.0            | 1.5            | %        |

| Leakage current                      | LENGOT               | V <sub>RST</sub> = 5.0 V                                                                           |       |                | 1              | ι.Λ      |

| Output low voltage                   | LEAKRST              |                                                                                                    | -     | 0.15           |                | μA<br>V  |

|                                      | Volrst               | IPG = 3 mA                                                                                         | -     | 0.15           | 0.30           | •        |

| Propagation time Power-on reset time | T <sub>PRST</sub>    | 5 % outside of the threshold, Power fail Power good                                                | 25.6  | 4 (*1)<br>32.0 | 8 (*1)<br>38.4 | μs<br>ms |

| Parameter                              | Symbol               | Condition                                                                                      |          | Value |          | Unit |

|----------------------------------------|----------------------|------------------------------------------------------------------------------------------------|----------|-------|----------|------|

|                                        |                      | Condition                                                                                      | Min      | Тур   | Max      | Onit |

| Watchdog Timer (WDI) Watchdog sampling | 1                    | I                                                                                              |          |       | T        | 1    |

| time                                   | Тѕам                 | -                                                                                              | 0.40     | 0.50  | 0.60     | ms   |

| Ignore window time                     | Tıw                  | -                                                                                              | 25.6     | 32.0  | 38.4     | ms   |

| Open window time                       | Tow                  | -                                                                                              | 25.6     | 32.0  | 38.4     | ms   |

| Long open window time                  | T <sub>LOW</sub>     | -                                                                                              | 102.4    | 128.0 | 153.6    | ms   |

| Closed window time                     | T <sub>CW</sub>      | -                                                                                              | 25.6     | 32.0  | 38.4     | ms   |

| Window watchdog trigger time           | Two                  | -                                                                                              | 38.4     | 48    | 51.2     | ms   |

| Input high voltage                     | Vihwdi               | -                                                                                              | 2.0      | -     | Vvcc     | V    |

| Input low voltage                      | VILWDI               | -                                                                                              | 0        | 1     | 0.4      | V    |

| Input current                          | I <sub>IHWDI</sub>   | V <sub>WDI</sub> = 5.0 V                                                                       | 33       | 50    | 100      | μA   |

| Pull down resistance                   | R <sub>PDWDI</sub>   | -                                                                                              | 50       | 100   | 150      | kΩ   |

| DD1: Buck DC/DC Con                    | verter               |                                                                                                |          |       |          |      |

| Output voltage                         | V <sub>OUT1</sub>    | Vvcc = 5.0 V,                                                                                  | -1.8     | 0     | +1.8     | %    |

| accuracy DC regulation                 | V <sub>REG1</sub>    | $I_{OUT1} = 10 \text{ mA}$<br>$V_{VCC} = V_{PVCC1} = 4.5 \text{ to } 5.5 \text{ V},$           | -15 (*1) | 0     | +5 (*1)  | mV   |

| _                                      |                      | lout1 = 0 to 2.0 A                                                                             | 1 1      |       |          |      |

| FB1 input resistance                   | R <sub>FB1</sub>     | V <sub>FB1</sub> = 2.0 V                                                                       | 95       | 190   | 285      | kΩ   |

| Switching FET                          | Ronhs1               | $I_{LX1} = 20 \text{ mA} (PVCC1 \text{ to } LX1)$                                              | -        | 100   | 190      | mΩ   |

| ON resistance                          | Ronls1               | $I_{LX1} = -20 \text{ mA (LX1 to PGND1)}$                                                      | -        | 65    | 125      | mΩ   |

| Switching FET leakage current          | I <sub>LEAK1</sub>   | I <sub>PVCC1</sub> = 5.0 V                                                                     | -        | 1     | 10       | μA   |

| Maximum output current                 | I <sub>OUT1</sub>    | L = 1.5 µH                                                                                     | 2 (*1)   | 1     | -        | Α    |

| LX1 peak current limit                 | I <sub>LIMIT1</sub>  | L = 1.5 µH                                                                                     | 2.5 (*1) | 1     | -        | Α    |

| Over voltage protection threshold      | V <sub>OVP1</sub>    | V <sub>OUT1</sub> rising, Switching termination threshold                                      | 125.0    | 130.0 | 135.0    | %    |

| Over voltage protection hysteresis     | V <sub>OVPHYS1</sub> | -                                                                                              | 2.0      | 5.0   | 8.0      | %    |

| FB1 discharge resistance               | R <sub>DIS1</sub>    | -                                                                                              | 160      | 400   | 640      | Ω    |

| Soft-start time coefficient            | T <sub>COESS1</sub>  | Tss1 = Vout1 x Tcoess1                                                                         | 0.9      | 1.0   | 1.1      | ms/V |

| DD2: Buck DC/DC Con                    | verter               |                                                                                                |          |       | <u> </u> | I.   |

| Output voltage                         |                      | V <sub>VCC</sub> = 5.0 V,                                                                      |          |       |          |      |

| accuracy                               | V <sub>OUT2</sub>    | Ιουτ2 = 10 mA                                                                                  | -1.8     | 0     | +1.8     | %    |

| DC regulation                          | V <sub>REG2</sub>    | $V_{VCC} = V_{PVCC2} = 4.5 \text{ to } 5.5 \text{ V}$ $I_{OUT2} = 0 \text{ to } 3.0 \text{ A}$ | -15 (*1) | 0     | +5 (*1)  | mV   |

| FB2 input resistance                   | R <sub>FB2</sub>     | V <sub>FB2</sub> = 2.0 V                                                                       | 95       | 190   | 285      | kΩ   |

| Switching FET                          | R <sub>ONHS2</sub>   | $I_{LX2} = 20 \text{ mA (PVCC2 to LX2)}$                                                       | -        | 85    | 165      | mΩ   |

| ON resistance                          | R <sub>ONLS2</sub>   | $I_{LX2} = -20 \text{ mA (LX2 to PGND2)}$                                                      | -        | 55    | 105      | mΩ   |

| Switching FET leakage current          | I <sub>LEAK2</sub>   | I <sub>PVCC2</sub> = 5.0 V                                                                     | -        | 1     | 10       | μA   |

| Maximum output                         | Іоит2                | L = 1.5 µH                                                                                     | 3 (*1)   | -     | -        | А    |

| current LX2 peak current limit         | I <sub>LIMIT2</sub>  | L = 1.5 μH                                                                                     | 3.5 (*1) | _     | _        | Α    |

| Over voltage protection threshold      | V <sub>OVP2</sub>    | V <sub>OUT2</sub> rising, Switching termination                                                | 125.0    | 130.0 | 135.0    | %    |

| Over voltage                           | VovPHYS2             | threshold                                                                                      | 2.0      | 5.0   | 8.0      | %    |

| protection hysteresis                  | V OVPRISZ            | _                                                                                              | 2.0      | 0.0   | 0.0      | /0   |

| FB2 discharge resistance               | R <sub>DIS2</sub>    | -                                                                                              | 160      | 400   | 640      | Ω    |

| Soft-start time coefficient            | T <sub>COESS2</sub>  | Tss2 = Vout2 x Tcoess2                                                                         | 0.9      | 1.0   | 1.1      | ms/V |

| Dovementor                         | Complete              | Condition                                                                                       |          | Value |         |      |  |

|------------------------------------|-----------------------|-------------------------------------------------------------------------------------------------|----------|-------|---------|------|--|

| Parameter                          | Symbol                | Condition                                                                                       | Min      | Тур   | Max     | Unit |  |

| DD3: Buck DC/DC Con                | verter                |                                                                                                 |          |       |         |      |  |

| Output voltage accuracy            | V <sub>О</sub> Т3     | Vvcc = 5.0 V,<br>Iout3 = 10 mA                                                                  | -1.8     | 0     | +1.8    | %    |  |

| DC regulation                      | $V_{REG3}$            | Vvcc = V <sub>P</sub> vcc <sub>3</sub> = 4.5 to 5.5 V,<br>lout <sub>3</sub> = 0 to 2.0 A        | -15 (*1) | 0     | +5 (*1) | mV   |  |

| FB3 input resistance               | R <sub>FB3</sub>      | V <sub>FB3</sub> = 2.0 V                                                                        | 95       | 190   | 285     | kΩ   |  |

| Switching FET                      | Ronhs3                | $I_{LX3} = 20 \text{ mA (PVCC3 to LX3)}$                                                        | -        | 100   | 190     | mΩ   |  |

| ON resistance                      | Ronls3                | $I_{LX3} = -20 \text{ mA (LX3 to PGND3)}$                                                       | -        | 65    | 125     | mΩ   |  |

| Switching FET leakage current      | I <sub>LEAK3</sub>    | IPVCC3 = 5.0 V                                                                                  | -        | 1     | 10      | μΑ   |  |

| Maximum output current             | Іоитз                 | L = 1.5 μH                                                                                      | 2 (*1)   | -     | -       | А    |  |

| LX3 peak current limit             | I <sub>LIMIT3</sub>   | L = 1.5 µH                                                                                      | 2.5 (*1) | 1     | -       | Α    |  |

| Over voltage protection threshold  | V <sub>OVP3</sub>     | V <sub>OUT3</sub> rising, Switching termination threshold                                       | 125.0    | 130.0 | 135.0   | %    |  |

| Over voltage protection hysteresis | V <sub>O</sub> VPHYS3 | -                                                                                               | 2.0      | 5.0   | 8.0     | %    |  |

| FB3 discharge resistance           | R <sub>DIS3</sub>     | -                                                                                               | 160      | 400   | 640     | Ω    |  |

| Soft-start time coefficient        | T <sub>COESS3</sub>   | Tss3 = Vout3 × Tcoess3                                                                          | 0.9      | 1.0   | 1.1     | ms/V |  |

| DD4: Buck DC/DC Con                | verter                |                                                                                                 |          |       |         |      |  |

| Output voltage accuracy            | V <sub>OUT4</sub>     | Vvcc = 5.0 V,<br>I <sub>OUT4</sub> = 10 mA                                                      | -1.8     | 0     | +1.8    | %    |  |

| DC regulation                      | V <sub>REG4</sub>     | $V_{VCC} = V_{PVCC4} = 4.5 \text{ to } 5.5 \text{ V},$ $I_{OUT4} = 0 \text{ to } 1.0 \text{ A}$ | -15 (*1) | 0     | +5 (*1) | mV   |  |

| FB4 input resistance               | R <sub>FB4</sub>      | V <sub>FB4</sub> = 2.0 V                                                                        | 95       | 190   | 285     | kΩ   |  |

| Switching FET                      | Ronhs4                | $I_{LX4} = 20 \text{ mA} (PVCC4 \text{ to } LX4)$                                               | -        | 100   | 190     | mΩ   |  |

| ON resistance                      | Ronls4                | $I_{LX4} = -20 \text{ mA (LX4 to PGND4)}$                                                       | -        | 65    | 125     | mΩ   |  |

| Switching FET leakage current      | I <sub>LEAK4</sub>    | I <sub>PVCC4</sub> = 5.0 V                                                                      | -        | 1     | 10      | μA   |  |

| Maximum output current             | I <sub>OUT4</sub>     | L = 1.5 µH                                                                                      | 1 (*1)   | -     | -       | Α    |  |

| LX4 peak current limit             | I <sub>LIMIT4</sub>   | L = 1.5 µH                                                                                      | 1.5 (*1) | -     | -       | Α    |  |

| Over voltage protection threshold  | V <sub>OVP4</sub>     | V <sub>OUT4</sub> rising, Switching termination threshold                                       | 125.0    | 130.0 | 135.0   | %    |  |

| Over voltage protection hysteresis | V <sub>OVPHYS4</sub>  | -                                                                                               | 2.0      | 5.0   | 8.0     | %    |  |

| FB4 discharge resistance           | R <sub>DIS4</sub>     | -                                                                                               | 160      | 400   | 640     | Ω    |  |

| Soft-start time coefficient        | T <sub>COESS4</sub>   | Tss4 = Vout4 × Tcoess4                                                                          | 0.9      | 1.0   | 1.1     | ms/V |  |

|                             |                      | 0 1141                                                                                                                    |                      | 11.22 |         |          |

|-----------------------------|----------------------|---------------------------------------------------------------------------------------------------------------------------|----------------------|-------|---------|----------|

| Parameter                   | Symbol               | Condition                                                                                                                 | Min                  | Тур   | Max     | Unit     |

| LD1: LDO Regulator          |                      |                                                                                                                           |                      |       |         |          |

| Output voltage accuracy     | Voutl1               | Vvcc = 5.0 V,<br>Ioutl1 = 10 mA                                                                                           | -1.8                 | 0     | +1.8    | %        |

| DC regulation               | $V_{REGL1}$          | $V_{VCC} = 4.5 \text{ to } 5.5 \text{ V}, V_{PVCCL1} = 2.97 \text{ to } V_{VCC}$<br>$I_{OUTL1} = 0 \text{ to } I_{OUTL1}$ | -15 (*1)             | 0     | +5 (*1) | mV       |

| Output FET leakage current  | ILEAKL1              | IPVCCL1 = 5.0 V                                                                                                           | -                    | 1     | 10      | μΑ       |

| Maximum output current      | loutl1               | V <sub>PVCCL1</sub> - V <sub>OUTL1</sub> ≥ 1.6 V<br>  0.17 V ≤ V <sub>PVCCL1</sub> - V <sub>OUTL1</sub> < 1.6 V           | 200 (*1)<br>100 (*1) | -     | -       | mA<br>mA |

| Output current limit        | ILIMITL1             | V <sub>PVCCL1</sub> - V <sub>OUTL1</sub> ≥ 1.6 V<br>0.17 V ≤ V <sub>PVCCL1</sub> - V <sub>OUTL1</sub> < 1.6 V             | 210 (*1)<br>105 (*1) | -     | -       | mA<br>mA |

| LDO1 discharge resistance   | R <sub>DISL1</sub>   | -                                                                                                                         | 160                  | 400   | 640     | Ω        |

| Soft-start time coefficient | T <sub>COESSL1</sub> | Tssl1 = Voutl1 × Tcoessl1                                                                                                 | 0.9                  | 1.0   | 1.1     | ms/V     |

| LD2: LDO Regulator          |                      |                                                                                                                           |                      |       |         |          |

| Output voltage accuracy     | V <sub>OUTL2</sub>   | Vvcc = 5.0 V,<br>Ioutl2 = 10 mA                                                                                           | -1.8                 | 0     | +1.8    | %        |

| DC regulation               | V <sub>REGL2</sub>   | $V_{VCC}$ = 4.5 to 5.5 V, $V_{PVCCL2}$ = 2.97 to $V_{VCC}$ $I_{OUTL2}$ = 0 to $I_{OUTL2}$                                 | -15 (*1)             | 0     | +5 (*1) | mV       |

| Output FET leakage current  | I <sub>LEAKL2</sub>  | I <sub>PVCCL2</sub> = 5.0 V                                                                                               | -                    | 1     | 10      | μA       |

| Maximum output current      | loutl2               | V <sub>PVCCL2</sub> - V <sub>OUTL2</sub> ≥ 1.6 V<br>0.17 V ≤ V <sub>PVCCL2</sub> - V <sub>OUTL2</sub> < 1.6 V             | 500 (*1)<br>400 (*1) | -     | -       | mA<br>mA |

| Output current limit        | ILIMITL2             | V <sub>PVCCL2</sub> - V <sub>OUTL2</sub> ≥ 1.6 V<br>0.17 V ≤ V <sub>PVCCL2</sub> - V <sub>OUTL2</sub> < 1.6 V             | 525 (*1)<br>420 (*1) |       | -       | mA<br>mA |

| LDO2 discharge resistance   | R <sub>DISL2</sub>   | -                                                                                                                         | 160                  | 400   | 640     | Ω        |

| Soft-start time coefficient | T <sub>COESSL2</sub> | T <sub>SSL2</sub> = V <sub>OUTL2</sub> × T <sub>COESSL2</sub>                                                             | 0.9                  | 1.0   | 1.1     | ms/V     |

<sup>\*1:</sup> The electrical characteristic is ensured by statistical characterization and indirect tests.

# 9. Operating Mode List

Table 9-1 shows the operation list of S6BP401A.

**Table 9-1 Operation Mode List**

|                    |        | Condition |                                      | Operating Block |          |                                  |                |     |                                     |

|--------------------|--------|-----------|--------------------------------------|-----------------|----------|----------------------------------|----------------|-----|-------------------------------------|

| Тл                 | SYNC   | ENL1      | EN1/<br>EN2/<br>EN3/<br>EN4/<br>ENL2 | Chip<br>Control | VREG LDO | Watch-<br>dog Trigger<br>Monitor | Freq.<br>Sync. | LD1 | DD1/<br>DD2/<br>DD3/<br>DD4/<br>LD2 |

| < T <sub>TSD</sub> | L or H | L         | L                                    | OFF             | OFF      | OFF                              | OFF            | OFF | OFF                                 |

| < T <sub>TSD</sub> | L or H | L         | Н                                    | ON              | ON       | OFF                              | OFF            | OFF | ON                                  |

| < T <sub>TSD</sub> | L or H | Н         | L                                    | ON              | ON       | ON                               | OFF            | ON  | OFF                                 |

| < T <sub>TSD</sub> | L or H | Н         | Н                                    | ON              | ON       | ON                               | OFF            | ON  | ON                                  |

| < T <sub>TSD</sub> | clock  | L         | L                                    | OFF             | OFF      | OFF                              | OFF            | OFF | OFF                                 |

| < T <sub>TSD</sub> | clock  | L         | Н                                    | ON              | ON       | OFF                              | ON             | OFF | ON                                  |

| < T <sub>TSD</sub> | clock  | Н         | L                                    | ON              | ON       | ON                               | ON             | ON  | OFF                                 |

| < T <sub>TSD</sub> | clock  | Н         | Н                                    | ON              | ON       | ON                               | ON             | ON  | ON                                  |

| ≥ T <sub>TSD</sub> | L or H | L         | L                                    | OFF             | OFF      | OFF                              | OFF            | OFF | OFF                                 |

| ≥ T <sub>TSD</sub> | L or H | L         | Н                                    | ON              | ON       | OFF                              | OFF            | OFF | OFF                                 |

| ≥ T <sub>TSD</sub> | L or H | Н         | L                                    | ON              | ON       | OFF                              | OFF            | OFF | OFF                                 |

| ≥ T <sub>TSD</sub> | L or H | Н         | Н                                    | ON              | ON       | OFF                              | OFF            | OFF | OFF                                 |

| ≥ T <sub>TSD</sub> | clock  | L         | L                                    | OFF             | OFF      | OFF                              | OFF            | OFF | OFF                                 |

| ≥ T <sub>TSD</sub> | clock  | L         | Н                                    | ON              | ON       | OFF                              | OFF            | OFF | OFF                                 |

| ≥ T <sub>TSD</sub> | clock  | Н         | L                                    | ON              | ON       | OFF                              | OFF            | OFF | OFF                                 |

| ≥ T <sub>TSD</sub> | clock  | Н         | Н                                    | ON              | ON       | OFF                              | OFF            | OFF | OFF                                 |

Document Number: 002-03341 Rev.\*I Page 18 of 41

#### 10. Function

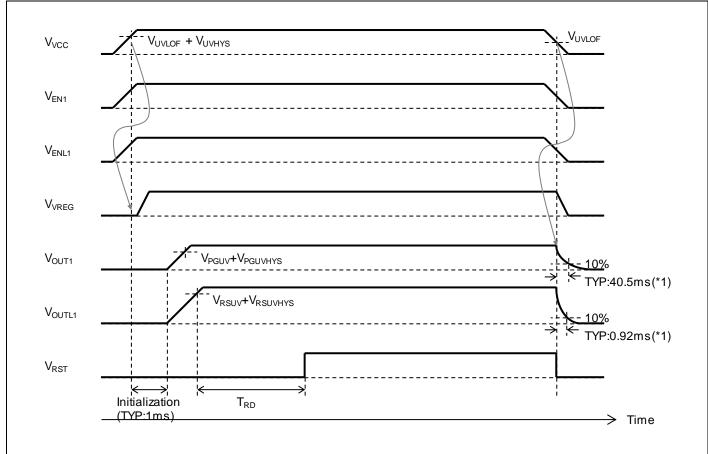

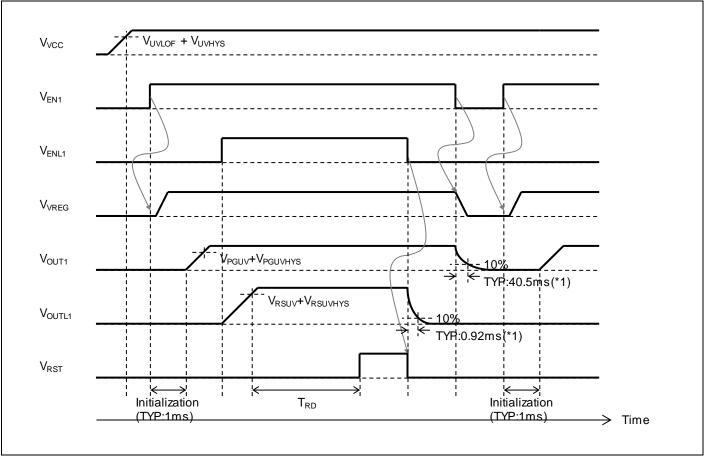

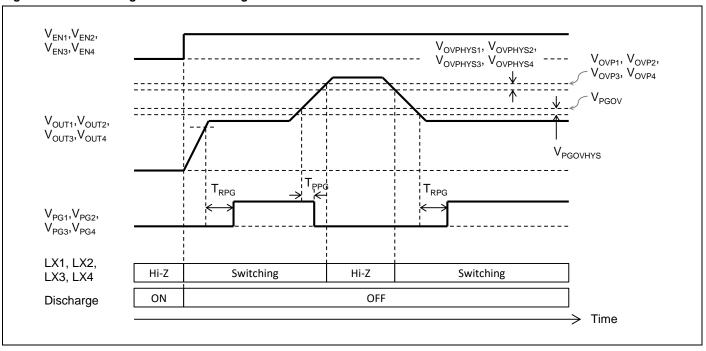

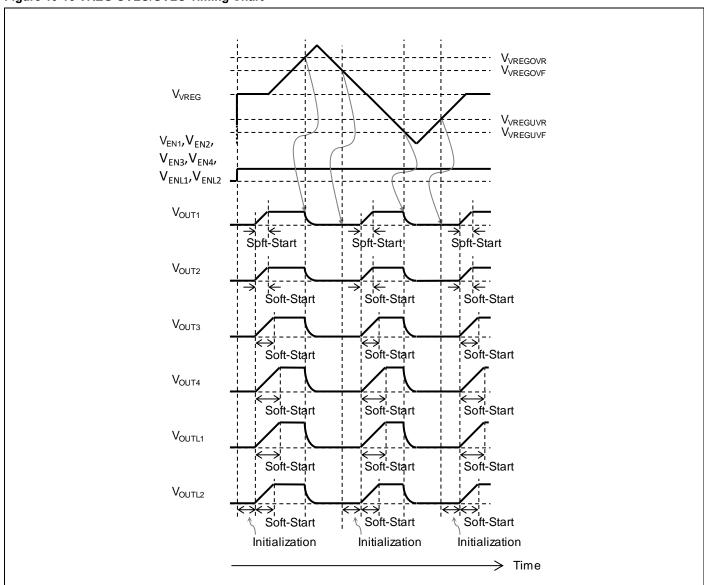

#### 10.1 Turning ON and OFF Sequence

When all of the enable input terminals (EN1, EN2, EN3, EN4, ENL1 and ENL2) are "Low", the device is in shutdown state. When any one or more than one of them go "High," the device is initialized, then the internal linear regulator (VREG) starts generating 1.8 V internal supply voltage. After that, each DC/DC converters and LDOs state is transitioned to the state which can be started.

In order for the device to start, the VCC terminal voltage must be higher than the under-voltage lockout threshold (VuvLoF + VuvHYs).

Figure 10-1 depicts the turning-on and off sequence where the enable signals are connected to VCC. Figure 10-2 depicts that where the enable signals are respectively controlled after the IC is powered.

Figure 10-1 Turning ON and OFF Sequence (where EN1 and ENL1 are Connected to VCC)

<sup>\*1:</sup> Given that the system employs the same external parts with those specified in "11. Application Circuit Example".

Figure 10-2 Turning ON and OFF Sequence (where EN1 and ENL1 are Respectively Controlled)

<sup>\*1:</sup> Given that the system employs the same external parts with those specified in "11. Application Circuit Example".

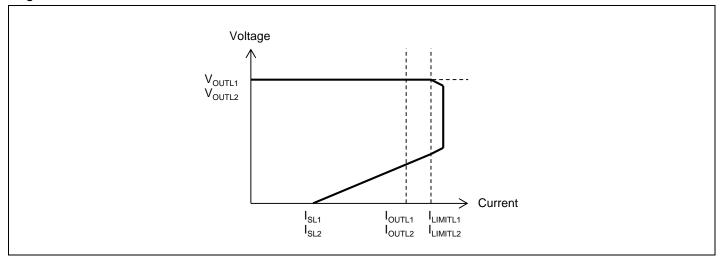

#### 10.2 Over Current Protection

The over current protection of the DC/DC converters detects the inductor peak current with on-resistance of Internal high side switching FET. If the DC/DC converter is over current state, the corresponding output voltage is decreased. If the device returns from over current state, the output voltage is target voltage.

Each LDOs equips foldback current limiter in order to prevent the IC itself from being damaged or destroyed. The curve of output current and output voltage in over current state is shown in the Figure 10-3.

Figure 10-3 LDO Foldback Over Current Protection Characteristic

#### 10.3 Over Voltage Protection

The over voltage protection of the DC/DC converters detects the output voltage. If the DC/DC converter is over voltage state, the corresponding channel stops switching and inductor connecting terminal (LX1, LX2, LX3, LX4) is held at high impedance. If the device returns from over voltage state, the channel returns switching automatically.

Figure 10-4 Over Voltage Protection Timing Chart

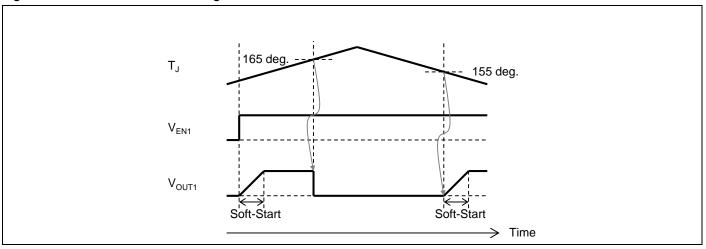

#### 10.4 Thermal Shutdown (TSD)

If the junction temperature reaches +165 °C, all DC/DC converters and LDOs stop outputting voltage. Then the discharge operation is carried out to discharge the output capacitor (The discharge operation continues until the state of the thermal shutdown released.) When the junction temperature drops below +155 °C, the soft-starters activate regulators and start generating voltage gradually if the enable is "High."

Figure 10-5 Thermal Shutdown Timing Chart

#### 10.5 Under Voltage Lockout (UVLO)

If the VCC terminal voltage ( $V_{VCC}$ ) drops below the lower UVLO threshold ( $V_{UVLOF}$ ), all DC/DC converters (DD1, DD2, DD3, DD4), LDOs (LD1, LD2), windowed watchdog timer (WDT) and the internal linear regulator (VREG) stop working. When the VCC terminal voltage ( $V_{VCC}$ ) is raised higher than the higher UVLO threshold ( $V_{UVLOF} + V_{UVHYS}$ ), the device returns automatically.

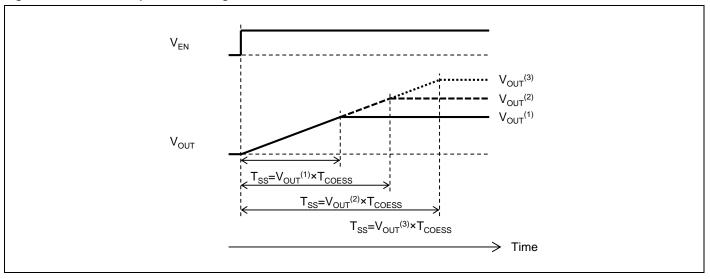

#### 10.6 Soft-Start Operation

S6BP401A equips load-independent soft-start function in order to prevent the DC/DC converters and LDOs from having rush current at the start-up. The soft-start timing is shown in the Figure 10-6, and is given by the following equation;

$$T_{SS} = V_{OUT} \times T_{COESS}$$

, where

Tss [ms]: Soft-start time

Vout [V]: Output voltage (Vout1, Vout2, Vout3, Vout4, Vout11, Vout12)

Tcoess [ms/V]: Soft-start time coefficient (Tcoess1, Tcoess2, Tcoess3, Tcoess4, TcoessL1, TcoessL2)

Figure 10-6 Soft-Start Operation Timing Chart

#### 10.7 Discharge Operation

When an enable signal goes "Low", the corresponding output capacitor is discharged by the internal discharge resistor and the output voltage is decreased gradually. Note that the discharge time is not consistent: it depends on the output load current.

As for a DC/DC converter, the output capacitor is discharged from FB1, FB2, FB3 and FB4 terminal to PGND1, PGND2, PGND3 and PGND4 terminal respectively. As for a LDO, the output capacitor is dis-charged from LDO1, LDO2 terminal to GND terminal.

The discharge time required to decrease the output voltage by 90 % without any explicit load given by the following equation;

$$T_{DIS} = 2.3 \times R_{DIS} \times C_{OUT}$$

, where

T<sub>DIS</sub> [ms]: Discharge time

$R_{\text{DIS}}\left[k\Omega\right]: \qquad \qquad \text{Discharge resistance}\left(R_{\text{DIS1}},\,R_{\text{DIS2}},\,R_{\text{DIS3}},\,R_{\text{DIS4}},\,R_{\text{DISL1}},\,R_{\text{DISL2}}\right)$

Cout [µF]: Output capacitor

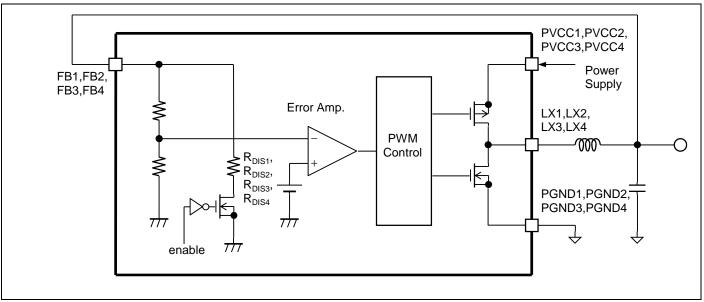

Figure 10-7 Discharge Diagram (DC/DC Converter)

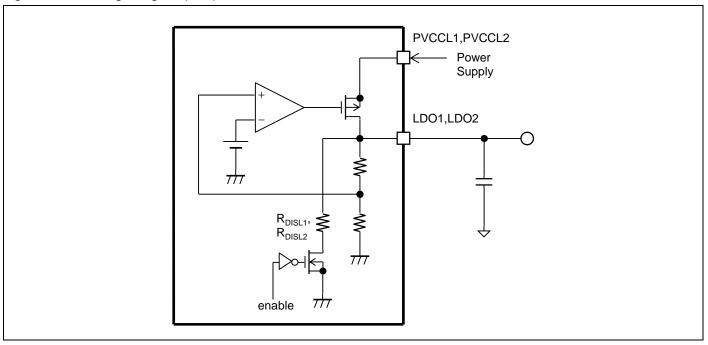

Figure 10-8 Discharge Diagram (LDO)

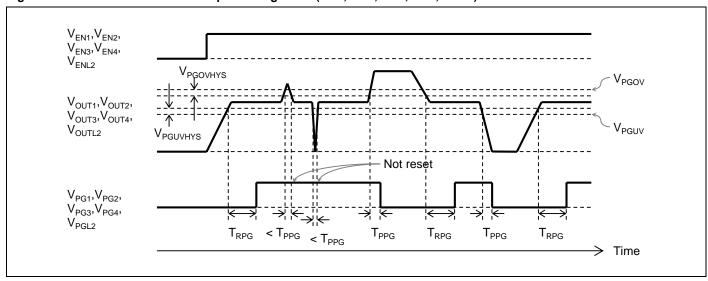

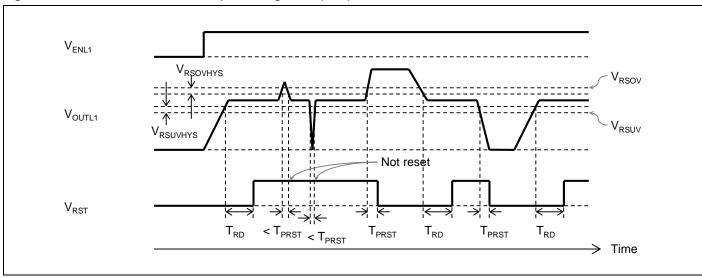

#### 10.8 Power Good Monitor and Reset Function

Each DC/DC converters and LDOs has power good function to indicate whether the output voltage is in the expected range. The Table 10-1 describes the power good pin names and their functions of each DC/DC converters and LDOs. The Figure 10-9 and Figure 10-10 depict power-good timing chart.

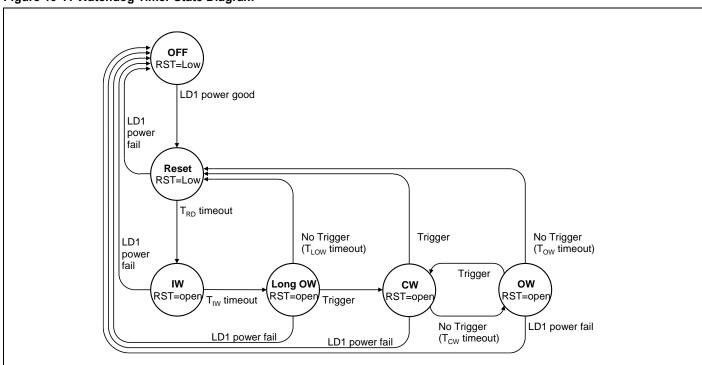

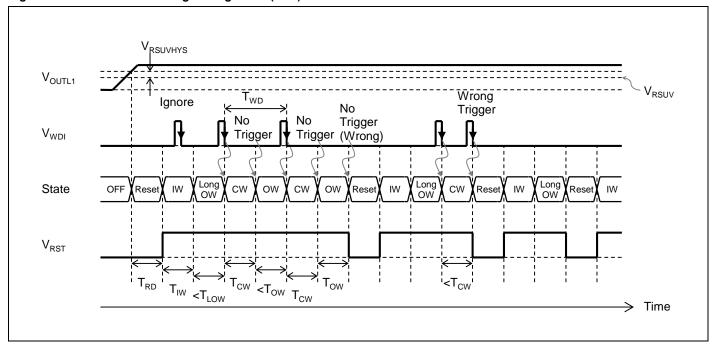

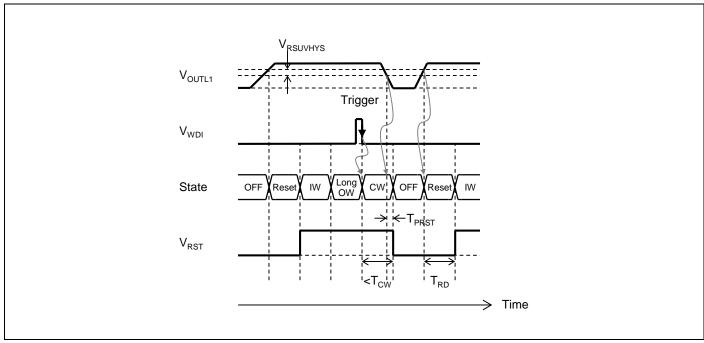

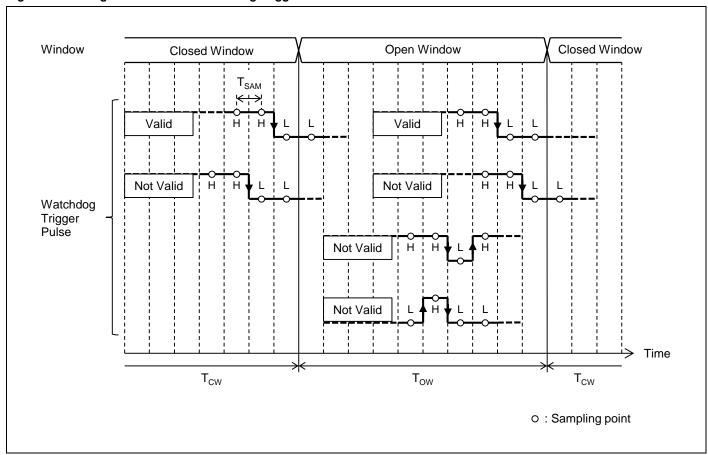

**Table 10-1 Power Good Monitor and Reset Function Pin List**