# Please note that Cypress is an Infineon Technologies Company.

The document following this cover page is marked as "Cypress" document as this is the company that originally developed the product. Please note that Infineon will continue to offer the product to new and existing customers as part of the Infineon product portfolio.

## **Continuity of document content**

The fact that Infineon offers the following product as part of the Infineon product portfolio does not lead to any changes to this document. Future revisions will occur when appropriate, and any changes will be set out on the document history page.

# **Continuity of ordering part numbers**

Infineon continues to support existing part numbers. Please continue to use the ordering part numbers listed in the datasheet for ordering.

www.infineon.com

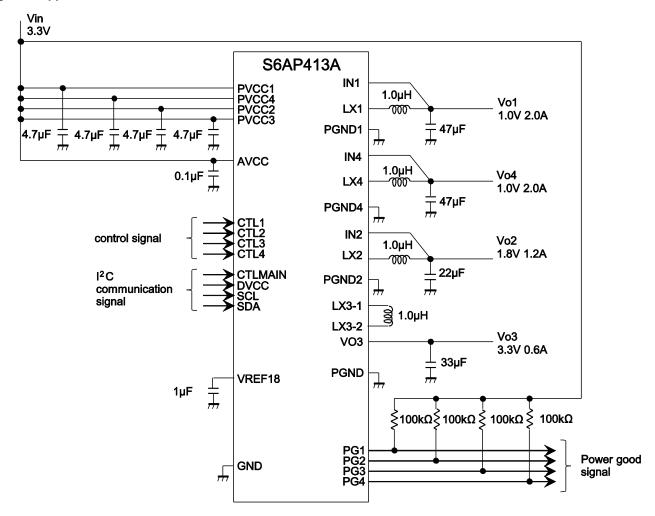

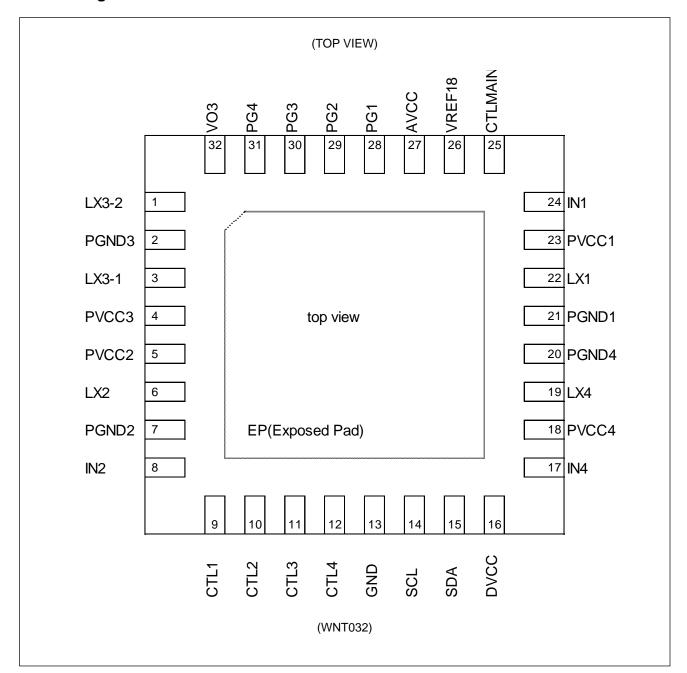

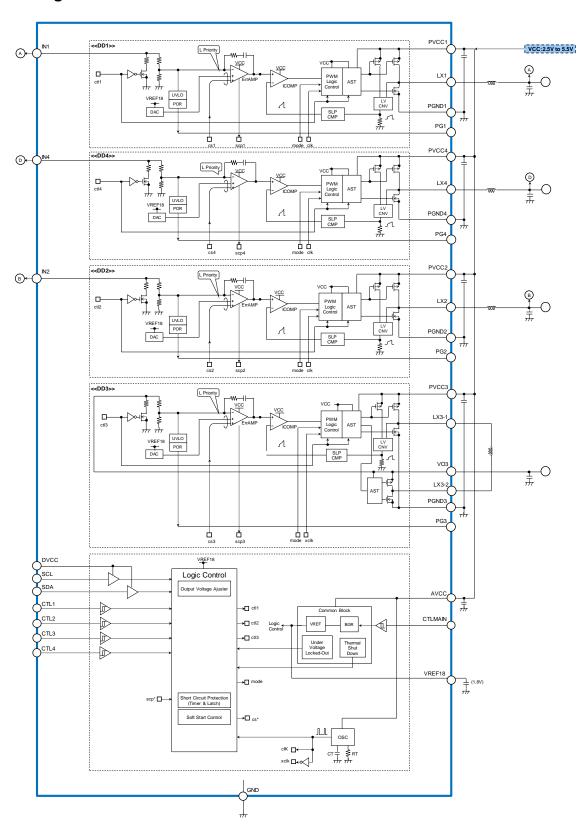

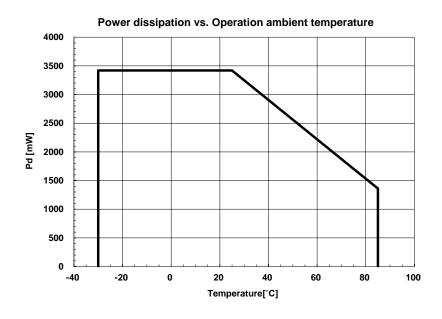

# 4ch DC/DC Converter with I<sup>2</sup>C Interface and Internal SW FETs

S6AP413A contains 3ch buck DC/DC converter and 1ch buck-boost DC/DC converter. S6AP413A can supply the main power line in several systems by using only its chip. The current mode control is adopted for the DC/DC converter, and it is possible to use the small chip inductor with the high switching frequency operation which contains internal switching FETs. S6AP413A contains the output setting resistor and the phase compensation circuit, and contributes to reduce the number of external components and its mount area. Also it contains the CTL input pin which can control the ON/OFF for each DC/DC converter, the Power Good signal output pin and I<sup>2</sup>C communication interface, therefore it is easy to design the power supply sequence. It is possible to tune in the output voltage exactly using the I<sup>2</sup>C communication.

#### **Features**

■Operating input voltage range: 2.5V to 5.5V (Maximum rating: 6.5V)

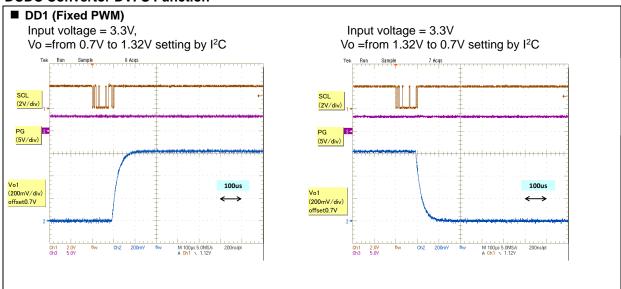

■Output voltage setting range: DD1\*:0.7V to 1.32V (20mV/step)

DD2\*:1.2V to 1.95V (50mV/step) DD3\*:2.8Vto 3.5V (100mV/step) DD4\*:0.7V to 1.32V (20mV/step)

- ■Maximum output current: DD1:2A, DD2:1.2A, DD3:0.6A, DD4:2A

- ■Internal switching FETs, output voltage setting resistor, phase compensation circuit and output discharge resistor (all DC/DC converters)

- ■Buck-boost DC/DC converter is seamless to change operation mode

- Soft start time setting range: 1 ms to 16 ms (approximately 1ms/step)

- Switching frequency for the DC/DC converter: 3 MHz

- Communication interface: I<sup>2</sup>C (ON/OFF, Output voltage, Soft start time)

- ■Internal PFM/PWM auto switching mode

- Each DC/DC converter Power Good function (open drain)

- Several protection functions: Under voltage lockout (UVLO), Over current protection (OCP), Thermal shut down (TSD)

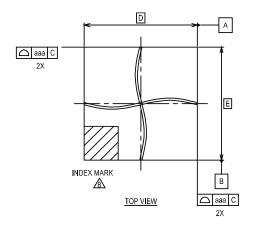

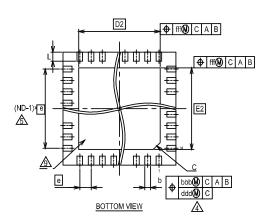

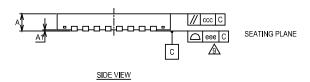

- ■Small package: QFN32 (5mm x 5mm x 0.71mm, 0.5mm pitch)

- \*: DD1, DD2, DD3, and DD4: DC/DC converter blocks 1,2,3,4

## **Applications**

Network equipment, Factory automation, Security system, Surveillance camera, Electrical music instrument, Multi-function printer, Scanner, Printer, Copy machine, Home appliances, Data storage (HDD, SSD), Mobile equipment for Li+ battery (1 cell)

## Contents

| 2. Recommended Application Specification 4. Pin Descriptions. 5. Block Diagram 6. Absolute Maximum Ratings 7. Recommended Operating Conditions 8. Electrical Characteristics 8. Electrical Characteristics 8. Electrical Characteristics 8. Preference Control Block 8. Di Reference Control Block 8. DD1 8. DD2 8. DD3 8. Dightal Block 9. Operation Mode List 10. State Transition Diagram 11. Turning ON and OFF Sequence (AVCC=CTLMAIN, CTL1, CTL2, CTL3, CTL4) 12. Turning ON and OFF Sequence (AVCC=CTLMAIN, CTL1, CTL2, CTL3, CTL4) 13. Turning ON and OFF Sequence (AVCC=CTLMAIN, CTL1, CTL2, CTL3, CTL4) 14. CTL Pin Threshold Voltage 15. Protection Operation Sequence (AVCC=CTLMAIN, CTL1, CTL2, CTL3, CTL4) 17. ID Soft Stat Operation Sequence (AVCC=CTLMAIN, CTL1, CTL2, CTL3, CTL4) 18. Discharge Operation 19. PG Function 20. FCInterface 21. Structure of PCInterface 22. Definition of Signal Lines 23. Validity of Data 24. Definition of Signal Lines 25. ACK Signal 26. FC Interface Input Timing 27. Slave Address 28. Bit Structure of PC Interface and Data 29. FC Interface 20. PG Interface 20. PG Interface 21. Structure of PC Interface and Data 21. Structure of PC Interface and Data 22. LO Plan Data 23. Validity of Data 24. About DD1, DD4-Output Voltage Setting 25. About DD3 Output Voltage Setting 26. About DD3 Output Voltage Setting 27. About Power Good Monitor 28. PG Interface 29. PG Interface 20. PG Interface 20. PG Interface 21. About DD7 (DP4 Output Voltage Setting 22. About DD7 (DP4 Output Voltage Setting 23. About Power Good Monitor 24. Reference Data 25. Ordering Information 26. Preset Code List                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1    | Application Circuit Example                                                    | 4  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------------------------------------------------------------------------------|----|

| 3. Pin Configuration. 4. Pin Descriptions. 5. Block Diagram. 6. Absolute Maximum Ratings. 7. Recommended Operating Conditions. 8. Electrical Characteristics. 8.1 Reference Control Block. 8.2 DD1. 8.3 DD2. 8.4 DD3. 8.6 Digital Block. 9. Operation Mode List. 10. State Transition Diagram. 11. Turning ON and OFF Sequence (AVCC=CTLMAIN, CTL1, CTL2, CTL3, CTL4). 12. Turning ON and OFF Sequence (AVCC=CTLMAIN,—TCL1,—CTL2,—CTL3,—CTL4). 13. Turning ON and OFF Sequence (AVCC—CTLMAIN,—PC). 14. CTLP, in Threshold Voltage. 15. Protection Operation Sequence. 16. Operation Condition, Stop Circuit and Release Condition for Protection Circuit. 17. DD Soft Start Operation. 18. Discharge Operation. 19. PG Function. 19. PG Function. 20. PCInterface. 20.1 Structure of PCInterface. 20.2 Definition of Signal Lines. 20.3 Validity of Data. 20.4 Definition of Signal Lines. 20.5 ACK Signal. 20.6 PC Interface Interface and Data. 21.1 About DD1, DD4 Output Voltage Setting. 21.2 About DD2 Output Voltage Setting. 21.3 About DD2 Output Voltage Setting. 21.4 About DD2 Output Voltage Setting. 21.5 Nover Consumer Consu |      | ··                                                                             |    |

| 4. Pin Descriptions. 5. Block Diagram. 6. Absolute Maximum Ratings. 7. Recommended Operating Conditions. 8. Electrical Characteristics. 8.1 Reference Control Block. 8.2 DD1. 8.3 DD2. 8.4 DD3. 8.5 DD4. 8.5 DD4. 8.6 Digital Block. 9. Operation Mode List. 10. State Transition Diagram. 11. Turning ON and OFF Sequence (AVCC=CTLMAIN, CTL1, CTL2, CTL3, CTL4). 12. Turning ON and OFF Sequence (AVCC—CTLMAIN—TL1, CTL2, CTL3, CTL4). 13. Turning ON and OFF Sequence (AVCC—CTLMAIN—TL1, CTL2, CTL3, CTL4). 14. CTL Pin Threshold Voltage. 15. Protection Operation Sequence (AVCC—CTLMAIN—PC). 16. Operation Condition, Stop Circuit and Release Condition for Protection Circuit. 17. DD Soft Start Operation. 18. Discharge Operation. 19. PG Function. 20. PCInterface. 20.1 Structure of PCInterface. 20.2 Definition of Signal Lines. 20.3 Validity of Data. 20.4 Definition of Signal Lines. 20.5 ACK Signal. 20.6 PC Interface Input Tirning. 20.7 Slave Address. 20.8 Bit Structure of Data on PC Interface. 21.1 About DD1, DD4Cuput Voltage Setting. 21.2 About DD2 Output Voltage Setting. 21.3 About DD3 Output Voltage Setting. 21.4 About D3 Output Voltage Setting. 21.5 DC/C Operation Mode. 22.1 OP Interface Input Voltage Setting. 23.4 Reference Data. 24. Reference Data. 25. Ordering Information.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |      |                                                                                |    |

| 5. Block Diagram. 6. Absolute Maximum Ratings. 7. Recommended Operating Conditions. 8. Electrical Characteristics. 8.1 Reference Control Block. 8.2 DD1. 8.3 DD2. 8.4 DD3. 8.5 DD4. 8.6 Digital Block. 9. Operation Mode List. 10. State Transition Diagram. 11. Turning ON and OFF Sequence (AVCC=CTLMAIN, CTL1, CTL2, CTL3, CTL4). 12. Turning ON and OFF Sequence (AVCC—CTLMAIN, CTL1, CTL2, CTL3, CTL4). 13. Turning ON and OFF Sequence (AVCC—CTLMAIN—IPC). 14. CTL Pin Threshold Voltage. 15. Protection Operation Sequence 16. Operation Condition, Stop Circuit and Release Condition for Protection Circuit. 17. DD Soft Start Operation. 18. Discharge Operation. 19. PG Function. 20.1 Structure of PCInterface. 20.2 Definition of Signal Lines. 20.3 Validity of Data. 20.4 Definition of Signal Lines. 20.5 ACK Signal. 20.6 PC Interface Input Timing. 20.7 Slave Address. 20.8 Bit Structure of PC Interface and Data. 21.1 About DD1, DD4Output Voltage Setting. 21.2 About DD2 Output Voltage Setting. 21.3 About DD3 Output Voltage Setting. 21.4 About Soft Start Time. 21.5 DC/DC Operation Mode. 22. WO Pin Equivalent Circuit Diagram. 23. Measurement Circuit for Characteristics of General Operation. 24. Reference Data. 25. Ordering Information.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |      | •                                                                              |    |

| 6. Absolute Maximum Ratings. 7. Recommended Operating Conditions. 8. Electrical Characteristics. 8.1 Reference Control Block. 8.2 DD1. 8.3 DD2. 8.4 DD3. 8.5 DD4. 8.6 Digital Block. 9. Operation Mode List. 10. State Transition Diagram. 11. Turning ON and OFF Sequence (AVCC-CTLMAIN, CTL1, CTL2, CTL3, CTL4). 12. Turning ON and OFF Sequence (AVCC-CTLMAIN-CTL1-CTL2-CTL3, CTL4). 12. Turning ON and OFF Sequence (AVCC-CTLMAIN-TCL1-CTL2-CTL3, CTL4). 13. Turning ON and OFF Sequence (AVCC-CTLMAIN-PC). 14. CTL Pin Threshold Voltage. 15. Protection Operation Sequence (AVCC-CTLMAIN-PC). 16. Operation Condition, Stop Circuit and Release Condition for Protection Circuit. 17. DD Soft Start Operation. 18. Discharge Operation. 19. PG Function. 20. PCInterface. 20.1 Structure of PCInterface. 20.2 Definition of Signal Lines. 20.3 Validity of Data. 20.4 Definition of Start and Stop Condition. 20.5 ACK Signal. 20.6 PC Interface Input Timing. 20.7 Slave Address. 20.8 Bit Structure of Data on PC Interface. 21.1 About DD D, DD4Outpt Voltage Setting. 21.2 About DD2 Output Voltage Setting. 21.3 About DD3 Output Voltage Setting. 21.4 About Soft Start Time. 21.5 DCDC Operation Mode. 21.6 Robust Power Good Monitor. 22. I/O Pin Equivalent Circuit Diagram. 23. Measurement Circuit Diagram. 23. Measurement Circuit Diagram. 23. Measurement Circuit Diagram. 24. Reference Data. 25. Ordering Information.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |      | ·                                                                              |    |

| 8. Electrical Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |      |                                                                                |    |

| 8. Electrical Characteristics 8.1 Reference Control Block 8.2 DD1 8.3 DD2 8.4 DD3 8.5 DD4 8.6 Digital Block 9. Operation Mode List 1. Turning ON and OFF Sequence (AVCC=CTLMAIN, CTL1, CTL2, CTL3, CTL4) 1.1 Turning ON and OFF Sequence (AVCC=CTLMAIN, CTL1, CTL2, CTL3, CTL4) 1.2 Turning ON and OFF Sequence (AVCC=CTLMAIN, CTL1, CTL2, CTL3, CTL4) 1.3 Turning ON and OFF Sequence (AVCC=CTLMAIN, CTL1, CTL2, CTL3, CTL4) 1.4. CTL Pin Threshold Voltage 1.5. Protection Operation Sequence 1.6. Operation Condition, Stop Circuit and Release Condition for Protection Circuit 1.7. DD Soft Start Operation. 1.9. PG Function 20. PCInterface 20.1 Structure of l'Clinterface. 20.2 Definition of Signal Lines 20.3 Validity of Data 20.4 Definition of Signal Lines 20.5 ACK Signal. 20.6 I'C Interface Input Timing 20.7 Slave Address 20.8 Bit Structure of Data on I'C Interface 21. Structure of I'C Interface and Data 21. About DD1, DD4Output Voltage Setting 21. About DD3 Output Voltage Setting 21. About DD4 Output Voltage Setting 21. About DD5 Output Voltage Setting 21. About DD7 Operation Mode 21. ON/OFF for DC/DC 21. About Drower Good Monitor 22. VO Pin Equivalent Circuit Tor Characteristics of General Operation 22. Voltage Information                                                                                                                                                                                                                                      |      |                                                                                |    |

| 8.1 Reference Control Block. 8.2 DD1 8.3 DD2 8.4 DD3 8.5 DD4 8.6 Digital Block 9. Operation Mode List 10. State Transition Diagram. 11. Turning ON and OFF Sequence (AVCC=CTLMAIN, CTL1, CTL2, CTL3, CTL4). 12. Turning ON and OFF Sequence (AVCC—CTLMAIN—CTL1—CTL2—CTL3—CTL4). 13. Turning ON and OFF Sequence (AVCC—CTLMAIN—CTL1—CTL2—CTL3—CTL4). 14. CTL Pin Threshold Voltage 15. Protection Operation Sequence 16. Operation Condition, Stop Circuit and Release Condition for Protection Circuit 17. DD Soft Start Operation. 18. Discharge Operation. 19. PG Function. 20. PCInterface 20.1 Structure of PCInterface. 20.2 Definition of Signal Lines 20.3 Validity of Data 20.4 Definition of Signal Lines 20.5 ACK Signal. 20.6 PC Interface Input Timing 20.7 Slave Address 20.8 Bit Structure of PC Interface and Data. 21.1 About DD1, DD4Output Voltage Setting 21.2 About DD2 Output Voltage Setting 21.3 About DD3 Output Voltage Setting 21.4 About DD3 Output Voltage Setting 21.5 DC/DC Operation Mode 21.6 ON/OFF for DC/DC 21.7 About Error Monitor 22. Wo Pie Reverse Data. 23. Measurement Circuit for Characteristics of General Operation. 24. Reference Data. 25. Ordering Information.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |      | ·                                                                              |    |

| 8.2 DD1 8.3 DD2 8.4 DD3 8.5 DD4 8.5 DD4 8.6 Digital Block. 9. Operation Mode List 10. State Transition Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |                                                                                |    |

| 8.3 DD2 8.4 DD3 8.5 DD4 8.6 Digital Block. 9. Operation Mode List 10. State Transition Diagram. 11. Turning ON and OFF Sequence (AVCC=CTLMAIN, CTL1, CTL2, CTL3, CTL4) 12. Turning ON and OFF Sequence (AVCC—CTLMAIN—CTL1—CTL2—CTL3—CTL4) 13. Turning ON and OFF Sequence (AVCC—CTLMAIN—IPC) 14. CTL Pin Threshold Voltage. 15. Protection Operation Sequence 16. Operation Condition, Stop Circuit and Release Condition for Protection Circuit. 17. DD Soft Start Operation 19. PG Function. 20. PCInterface 20.1 Structure of PCInterface. 20.2 Definition of Signal Lines. 20.3 Validity of Data 20.4 Definition of Start and Stop Condition. 20.5 ACK Signal 20.6 PC Interface Input Timing. 20.7 Slave Address 20.8 Bit Structure of Data on IPC Interface. 20.9 Structure of PC Interface and Data 21.1 About DD1, DD4 Output Voltage Setting. 21.2 About DD2 Output Voltage Setting. 21.3 About DD3 Output Voltage Setting. 21.4 About DD3 Output Voltage Setting. 21.5 About DD3 Output Voltage Setting. 21.6 NOVOFF for DC/DC. 21.7 About Power Good Monitor. 22. V/O Pin Equivalent Circuit for Characteristics of General Operation. 22. Reference Data. 23. Measurement Circuit for Characteristics of General Operation. 24. Reference Data. 25. Ordering Information.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |      |                                                                                |    |

| 8.4 DD3 8.5 DD4 8.6 Digital Block 9. Operation Mode List 11. Turning ON and OFF Sequence (AVCC=CTLMAIN, CTL1, CTL2, CTL3, CTL4) 12. Turning ON and OFF Sequence (AVCC → CTLMAIN → CTL1 → CTL2 → CTL3 → CTL4) 13. Turning ON and OFF Sequence (AVCC → CTLMAIN → CTL1 → CTL2 → CTL3 → CTL4) 14. CTL Pin Threshold Voltage 15. Protection Operation Sequence 16. Operation Condition, Stop Circuit and Release Condition for Protection Circuit 17. DD Soft Start Operation 18. Discharge Operation 19. PG Function 20. PCInterface 20.1 Structure of PCInterface 20.2 Definition of Signal Lines 20.3 Validity of Data 20.4 Definition of Signal Lines 20.5 ACK Signal 20.6 PC Interface Input Timing 20.7 Slave Address 20.8 Bit Structure of PC Interface and Data 21.1 About DD1, DD4Output Voltage Setting 21.2 About DD2 Output Voltage Setting 21.3 About DD3 Output Voltage Setting 21.4 About Structure of Mode 21.5 DC/DC Operation Mode 22.6 NOVOFF for DC/DC 21.8 About Power Good Monitor 22.10 Power Good Monitor 22.10 Power Good Monitor 22.10 Power Good Monitor 22.11 About Error Monitor 22.12 Reference Data 23. Meassurement Circuit for Characteristics of General Operation 24. Reference Data 25. Ordering Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      |                                                                                |    |

| 8.5 DD4  8.6 Digital Block.  9. Operation Mode List  10. State Transition Diagram.  11. Turning ON and OFF Sequence (AVCC=CTLMAIN, CTL1, CTL2, CTL3, CTL4).  12. Turning ON and OFF Sequence (AVCC → CTLMAIN, — CTL1 → CTL2 → CTL4).  13. Turning ON and OFF Sequence (AVCC → CTLMAIN → I²C).  14. CTL Pin Threshold Voltage.  15. Protection Operation Sequence.  16. Operation Condition, Stop Circuit and Release Condition for Protection Circuit.  17. DD Soft Start Operation.  18. Discharge Operation.  19. PG Function.  20. PCInterface.  20.1 Structure of I?CInterface.  20.2 Definition of Signal Lines.  20.3 Validity of Data.  20.4 Definition of Start and Stop Condition.  20.5 ACK Signal  20.6 I?C Interface Input Timing.  20.7 Slave Address.  20.8 Bit Structure of Data on I?C Interface.  21.1 About DD1, DD4Output Voltage Setting.  21.2 About DD2 Output Voltage Setting.  21.3 About DD3 Output Voltage Setting.  21.4 About Soft Start Time.  21.5 DC/DC Operation Mode.  21.6 Nov PF for DC/DC  21.7 About Porn Or/DC  22. VO Pin Equivalent Circuit Diagram.  23. Measurement Circuit for Characteristics of General Operation.  24. Reference Data.  25. Ordering Information.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      |                                                                                | _  |

| 8.6 Digital Block                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |      |                                                                                |    |

| 9. Operation Mode List 10. State Transition Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |      |                                                                                |    |

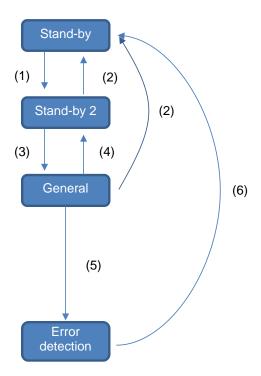

| 10. State Transition Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |      |                                                                                |    |

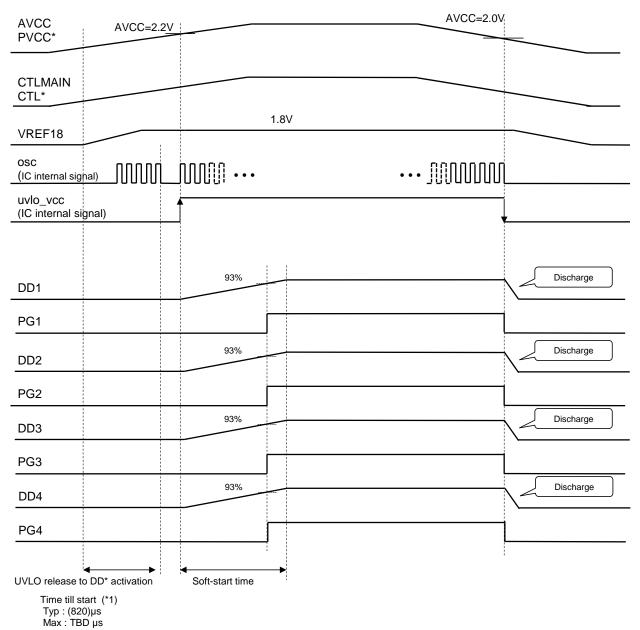

| 11. Turning ON and OFF Sequence (AVCC=CTLMAIN, CTL1, CTL2, CTL3, CTL4)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      | ·                                                                              |    |

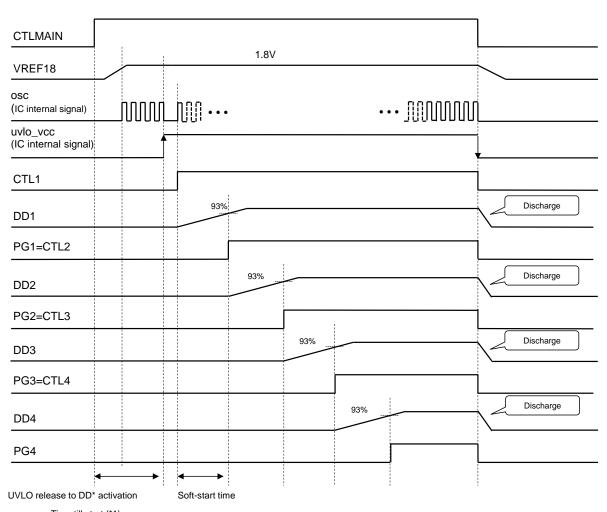

| 12. Turning ON and OFF Sequence (AVCC →CTLMAIN→CTL1→CTL2→ CTL3→ CTL4)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |      | <del>-</del>                                                                   |    |

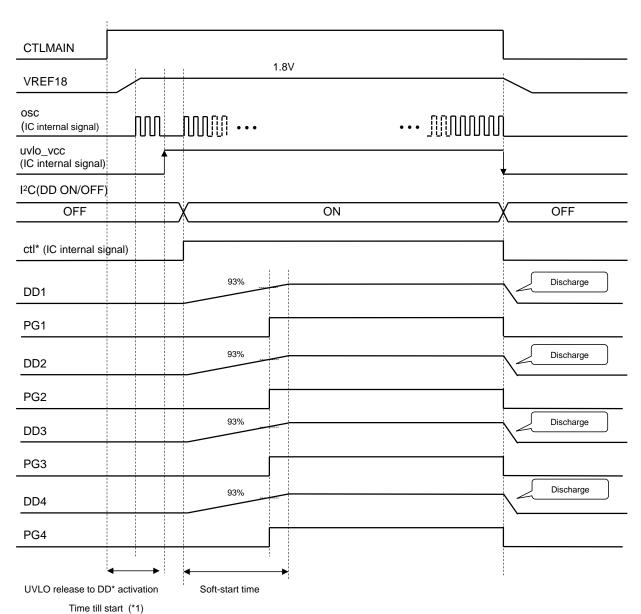

| 13. Turning ON and OFF Sequence (AVCC→CTLMAIN→I²C)  14. CTL Pin Threshold Voltage  15. Protection Operation Sequence  16. Operation Condition, Stop Circuit and Release Condition for Protection Circuit  17. DD Soft Start Operation  18. Discharge Operation  19. PG Function  20. I²CInterface  20. I²CInterface  20. Definition of Signal Lines  20.3 Validity of Data  20.4 Definition of Start and Stop Condition.  20.5 ACK Signal  20.6 I²C Interface Input Timing  20.7 Slave Address  20.8 Bit Structure of Data on I²C Interface  21. Structure of I²C Interface and Data  21.1 About DD1, DD4Output Voltage Setting  21.2 About DD2 Output Voltage Setting  21.3 About DD3 Output Voltage Setting  21.4 About Soft Start Time  21.5 DC/DC Operation Mode  21.6 ON/OFF for DC/DC  21.7 About Error Monitor  21.8 Nesurement Circuit Diagram  22.1 Mesurement Circuit for Characteristics of General Operation  23. Measurement Circuit for Characteristics of General Operation  24. Reference Data  25. Ordering Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |      |                                                                                |    |

| 14. CTL Pin Threshold Voltage 15. Protection Operation Sequence 16. Operation Condition, Stop Circuit and Release Condition for Protection Circuit 17. DD Soft Start Operation 18. Discharge Operation 19. PG Function 20. PG Function 20. PGInterface 20.1 Structure of I <sup>2</sup> Cinterface 20.2 Definition of Signal Lines 20.3 Validity of Data 20.4 Definition of Start and Stop Condition 20.5 ACK Signal 20.6 I <sup>2</sup> C Interface Input Timing 20.7 Slave Address 20.8 Bit Structure of Data on I <sup>2</sup> C Interface 21. Structure of I <sup>2</sup> C Interface and Data 21.1 About DD1, DD4Output Voltage Setting 21.2 About DD2 Output Voltage Setting 21.3 About DD3 Output Voltage Setting 21.4 About Soft Start Time 21.5 DC/DC Operation Mode 21.6 ON/OFF for DC/DC 21.7 About Error Monitor 21.8 About Power Good Monitor 22. I/O Pin Equivalent Circuit for Characteristics of General Operation 22. Measurement Circuit for Characteristics of General Operation 24. Reference Data 25. Ordering Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      | • • • • • • • • • • • • • • • • • • • •                                        |    |

| 15. Protection Operation Sequence 16. Operation Condition, Stop Circuit and Release Condition for Protection Circuit 17. DD Soft Start Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 13.  | Turning ON and OFF Sequence (AVCC→CTLMAIN→I²C)                                 | 23 |

| 16. Operation Condition, Stop Circuit and Release Condition for Protection Circuit  17. DD Soft Start Operation  18. Discharge Operation  19. PG Function  20. l²CInterface  20.1 Structure of l²CInterface  20.2 Definition of Signal Lines  20.3 Validity of Data  20.4 Definition of Start and Stop Condition  20.5 ACK Signal  20.6 l²C Interface Input Timing  20.7 Slave Address  20.8 Bit Structure of l²C Interface and Data  21.1 About DD1, DD4Output Voltage Setting  21.2 About DD2 Output Voltage Setting  21.3 About DD3 Output Voltage Setting  21.4 About Soft Start Time  21.5 DC/DC Operation Mode  21.6 ON/OFF for DC/DC  21.7 About Error Monitor  22.8 Measurement Circuit for Characteristics of General Operation  24. Reference Data  25. Ordering Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      | •                                                                              |    |

| 17. DD Soft Start Operation 18. Discharge Operation 19. PG Function 20. l'CInterface 20. l'CInterface 20. 2 Definition of Signal Lines 20. 3 Validity of Data 20. 4 Definition of Start and Stop Condition 20. 5 ACK Signal 20. 6 L'C Interface Input Timing 20. 7 Slave Address 20. 8 Bit Structure of l'C Interface and Data 20. 8 Bit Structure of Data on l'C Interface 21. Structure of l'C Interface and Data 21. 1 About DD1 DD2 Output Voltage Setting 21. 2 About DD3 Output Voltage Setting 21. 3 About DD3 Output Voltage Setting 21. 4 About Soft Start Time 21. 5 DC/DC Operation Mode 21. 6 ON/OFF for DC/DC 21. 7 About Error Monitor 21. 8 About Power Good Monitor 22. VO Pin Equivalent Circuit Diagram 23. Measurement Circuit for Characteristics of General Operation 24. Reference Data 25. Ordering Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      |                                                                                |    |

| 18. Discharge Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 16.  | Operation Condition, Stop Circuit and Release Condition for Protection Circuit | 26 |

| 19. PG Function 20.   **CInterface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 17.  | DD Soft Start Operation                                                        | 27 |

| 20.1 Structure of I²CInterface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 18.  | Discharge Operation                                                            | 28 |

| 20.1 Structure of I²CInterface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 19.  | PG Function                                                                    | 29 |

| 20.2 Definition of Signal Lines 20.3 Validity of Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 20.  | I <sup>2</sup> CInterface                                                      | 30 |

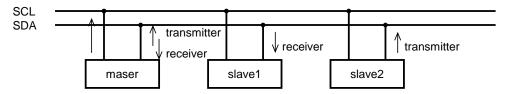

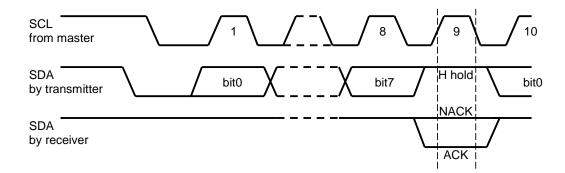

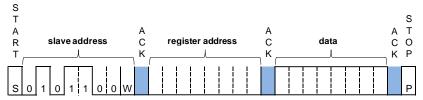

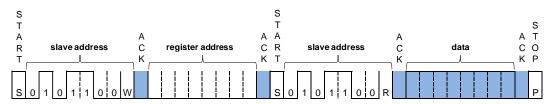

| 20.3 Validity of Data 20.4 Definition of Start and Stop Condition 20.5 ACK Signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 20.1 | 1 Structure of I <sup>2</sup> CInterface                                       | 30 |

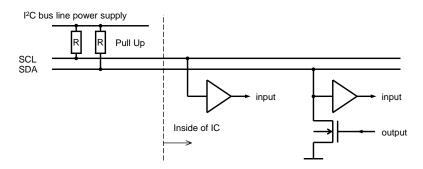

| 20.3 Validity of Data 20.4 Definition of Start and Stop Condition 20.5 ACK Signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 20.2 | 2 Definition of Signal Lines                                                   | 30 |

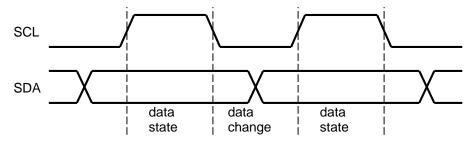

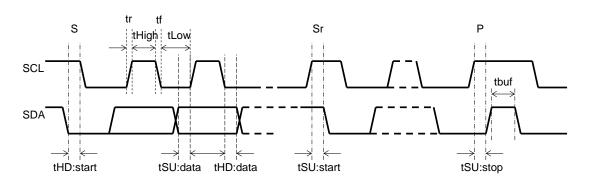

| 20.4 Definition of Start and Stop Condition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      | · ·                                                                            |    |

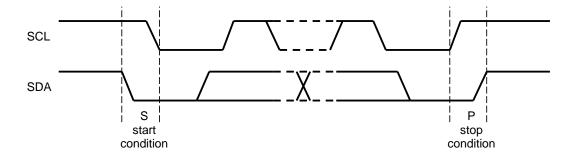

| 20.5 ACK Signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      | ·                                                                              |    |

| 20.6 I²C Interface Input Timing.  20.7 Slave Address.  20.8 Bit Structure of Data on I²C Interface.  21. Structure of I²C Interface and Data.  21.1 About DD1, DD4Output Voltage Setting.  21.2 About DD2 Output Voltage Setting.  21.3 About DD3 Output Voltage Setting.  21.4 About Soft Start Time.  21.5 DC/DC Operation Mode.  21.6 ON/OFF for DC/DC.  21.7 About Error Monitor.  21.8 About Power Good Monitor.  22. I/O Pin Equivalent Circuit Diagram.  23. Measurement Circuit for Characteristics of General Operation.  24. Reference Data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      | ·                                                                              |    |

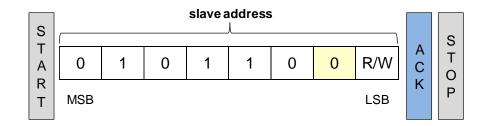

| 20.7 Slave Address  20.8 Bit Structure of Data on I <sup>2</sup> C Interface  21. Structure of I <sup>2</sup> C Interface and Data  21.1 About DD1, DD4Output Voltage Setting  21.2 About DD2 Output Voltage Setting  21.3 About DD3 Output Voltage Setting  21.4 About Soft Start Time  21.5 DC/DC Operation Mode  21.6 ON/OFF for DC/DC  21.7 About Error Monitor  21.8 About Power Good Monitor  21.8 About Power Good Monitor  22. I/O Pin Equivalent Circuit Diagram  23. Measurement Circuit for Characteristics of General Operation  24. Reference Data  25. Ordering Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      | ·                                                                              |    |

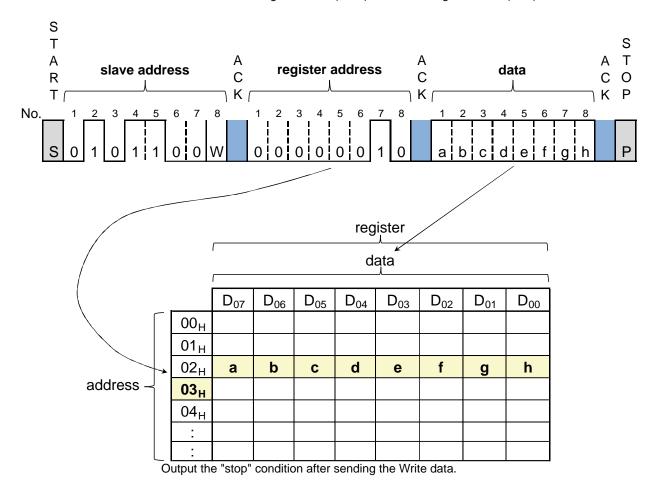

| 20.8 Bit Structure of Data on I <sup>2</sup> C Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |      | · · · · · · · · · · · · · · · · · · ·                                          |    |

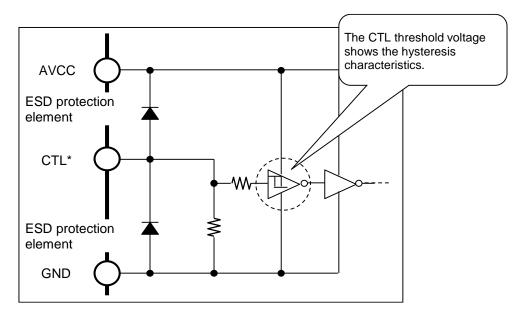

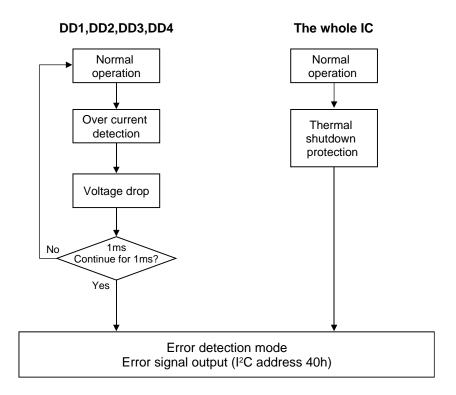

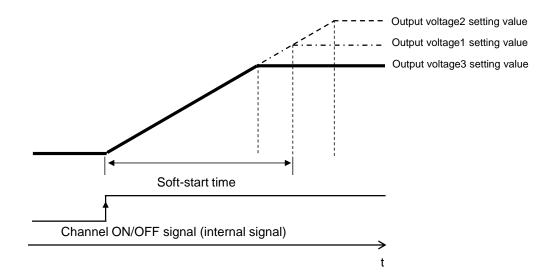

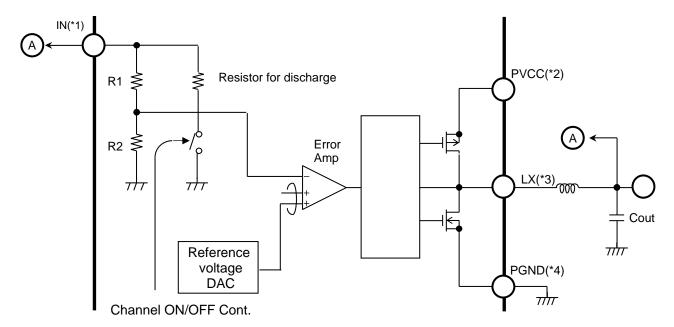

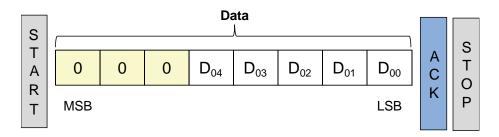

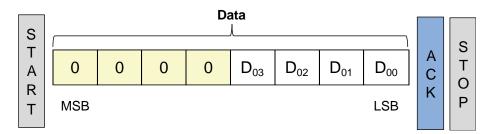

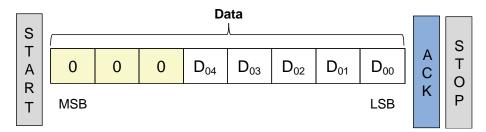

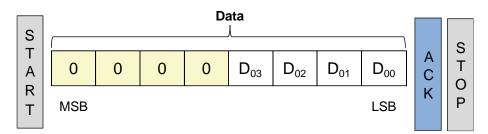

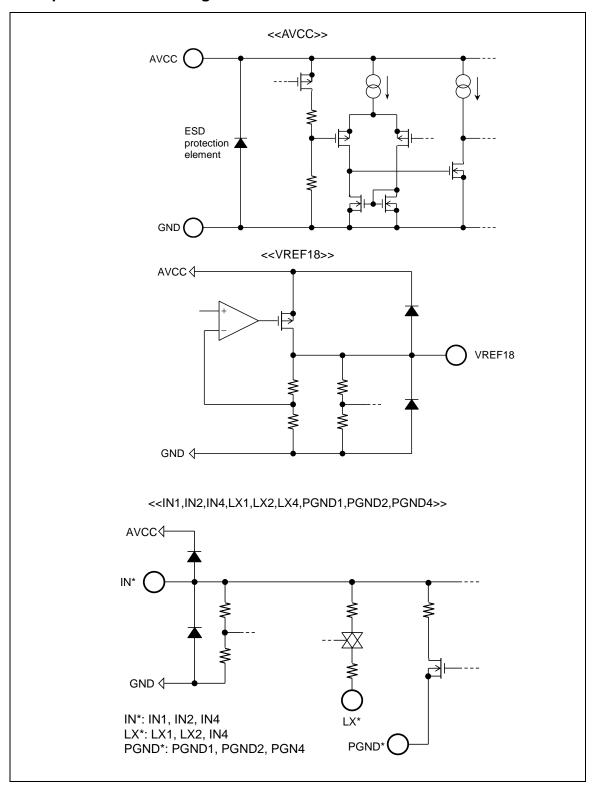

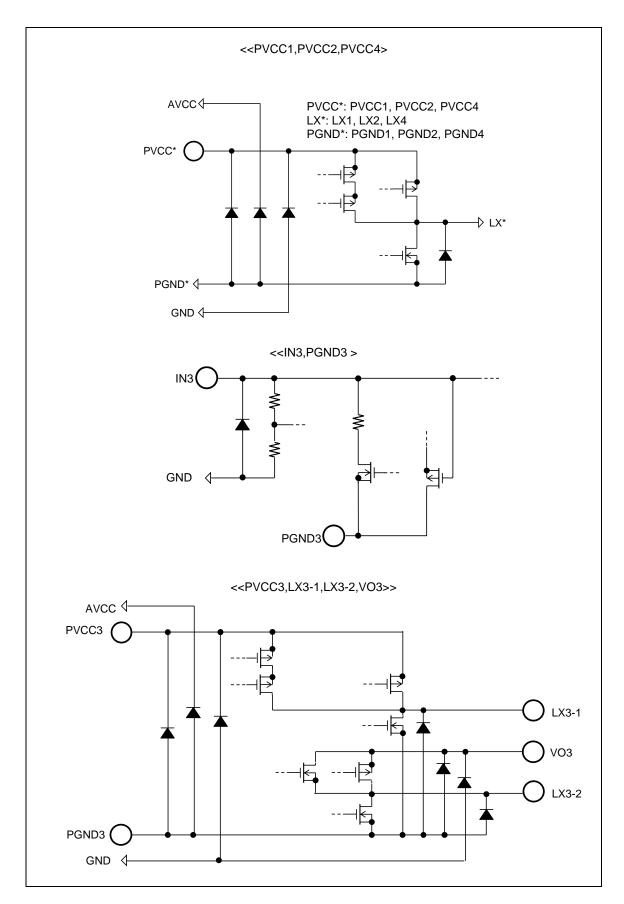

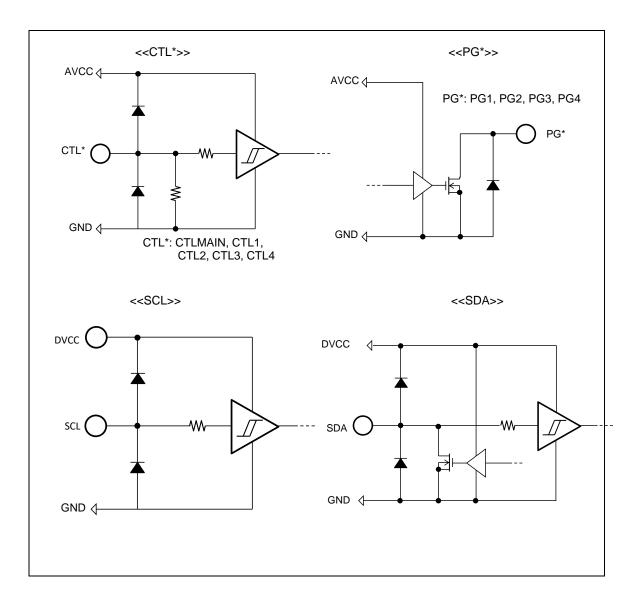

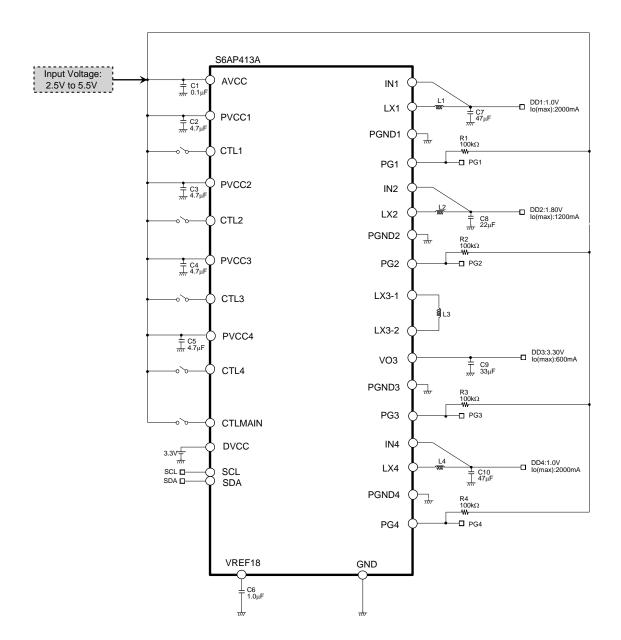

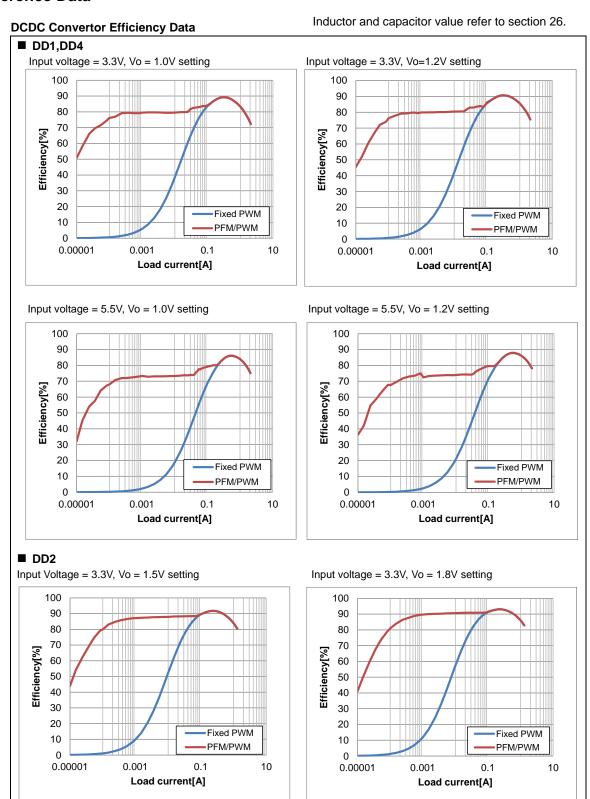

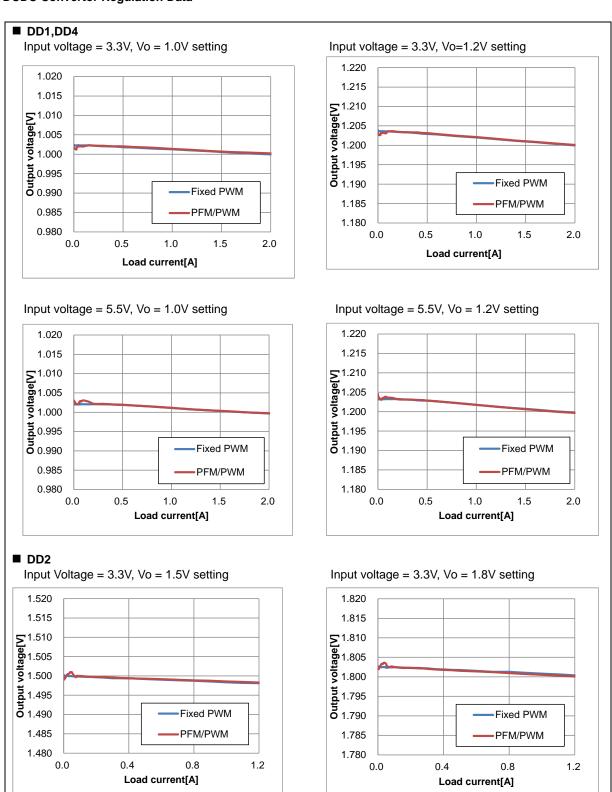

| 21. Structure of I²C Interface and Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      |                                                                                |    |