# RF tuner IC For DVB-H,DVB-T and DMB-TH

# **ADMTV102**

#### FEATURES

Single chip synthesized tuner for dual-band mobile-TV applications Zero-IF single-conversion architecture which eliminates all **SAW filters** Covers whole VHF (174 ~ 245 MHz) and UHF (470 MHz ~ 862 MHz) Typical AGC dynamic range: -102 ~ 0 dBm Ultra low power consumption VHF: 180 mW UHF: 200 mW **On-chip fast switching fractional-N PLL** On-chip low phase noise and wide frequency range VCO On-chip bandwidth-adjustable low pass filter Integrated baseband variable gain amplifier for direct connection to digital demodulators Noise/Linearity optimization through internal RFAGC loop Adjustable take-over point I<sup>2</sup>C serial bus interface Small 32-QFN package (5 × 5 mm<sup>2</sup>) **Minimal external components**

#### **GENERAL DESCRIPTION**

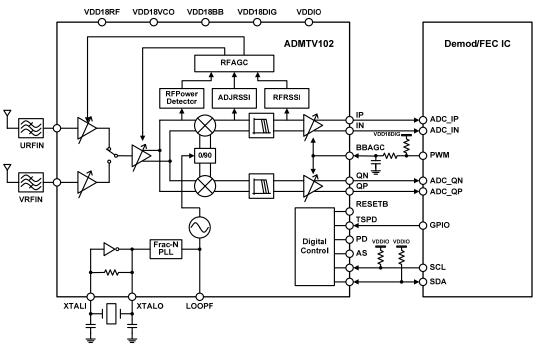

The ADMTV102 is a highly integrated CMOS single chip zero-IF conversion tuner IC for mobile-TV standards, such as DVB-H, DVB-T and DMB-TH. It includes dual RF input bands, which are VHF and UHF. The building blocks of ADMTV102 are LNAs, RFPGAs, I/Q down-conversion mixers, bandwidth adjustable low pass filters, baseband variable gain amplifiers, VCOs and a fractional-N PLL, etc. On-chip low phase noise VCO along with high resolution fractional-N frequency synthesizer make in-band phase noise low enough for mobile-TV applications.

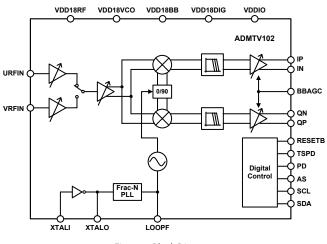

### FUNCTIONAL BLOCK DIAGRAM

Figure 1. Block Diagram

#### **APPLICATIONS**

DVB-H/DVB-T/DMB-TH mobile and portable TV receivers VHF and UHF mobile and portable TV receivers

The ADMTV102 supports dual-band mobile TV standards with ultra low power consumption such as 200 mW for DVB-H. Using small leadless 5 mm  $\times$  5 mm 32-LD QFN package, the ADMTV102 is the best solution for highly integrated dual-band mobile and portable applications where low power consumption is critical. It has an industry standard I<sup>2</sup>C serial bus interface. Applications of the ADMTV102 are DVB-H, DVB-T and DMB-TH.

#### Rev. 0

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

www.analog.com

Fax: 781.461.3113

©2007 Analog Devices, Inc. All rights reserved.

# TABLE OF CONTENTS

| Features                                    |

|---------------------------------------------|

| Functional Block Diagram                    |

| Applications                                |

| General Description1                        |

| Table of Contents                           |

| Revision History                            |

| Specifications                              |

| Absolute Maximum Ratings5                   |

| ESD Caution5                                |

| Pin Configuration and Function Descriptions |

| Terminology                                 |

| Typical Performance Characteristics9        |

| Functional Descriptions                     |

| I <sup>2</sup> C Operation13                |

| I <sup>2</sup> C Read/Write Address         |

| I <sup>2</sup> C Bus Format                 |

| Timing Characteristics14                    |

| I <sup>2</sup> C Register Map16             |

| Detailed Register Description18             |

| RFAGC Setting                               |

| BBAGC Setting23                             |

| Theory of Operation                         |

| RF LNA, PGA and I/Q Down-Converter24        |

|                                             |

| Local Oscillator                           | 24 |

|--------------------------------------------|----|

| PLL                                        | 24 |

| Baseband LPF and VGA                       | 24 |

| Automatic Gain Control                     | 25 |

| RFRSSI                                     | 25 |

| Hardware/Software/Time-Slicing Power Down  | 26 |

| Applications                               | 27 |

| RF Input Stage                             |    |

| VCO Bias/Bypass Capacitors                 |    |

| Digital Interface - I <sup>2</sup> C/Reset |    |

| Isolation from Digital Part                |    |

| BBVGA Interconnections                     |    |

| Reference Clock Selection                  | 29 |

| PLL Setting                                | 29 |

| Three Power Down Modes                     |    |

| Evaluation Board                           | 31 |

| Evaluation Board Bill of Materials (BOM)   | 31 |

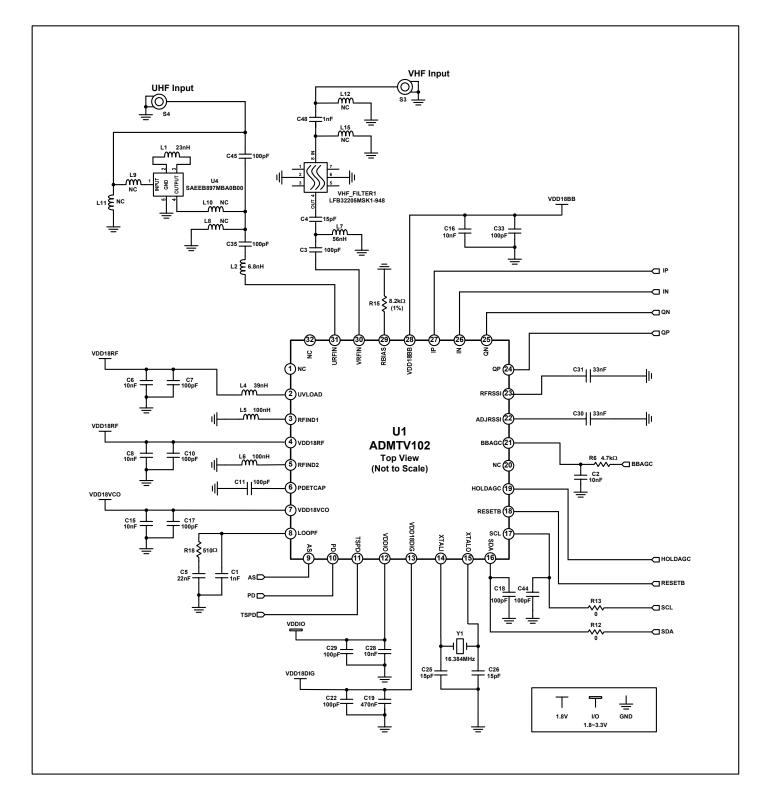

| Evaluation Board Schematics                | 32 |

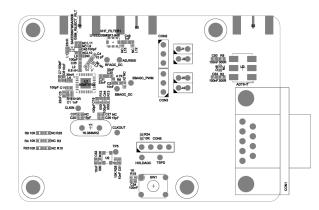

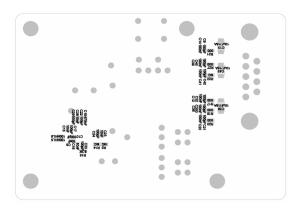

| PCB Layers                                 |    |

| Thermal Considerations                     | 34 |

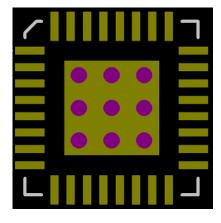

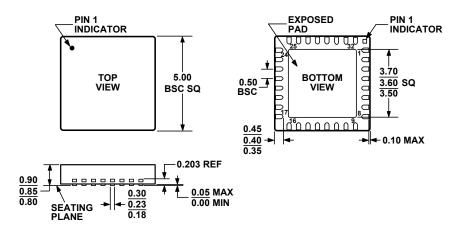

| Outline Dimensions                         | 35 |

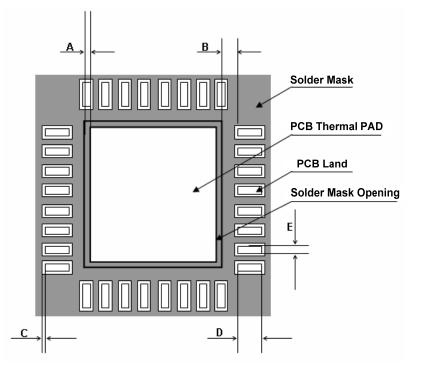

| Recommended PCB Land Pattern               |    |

| Ordering Guide                             |    |

## **REVISION HISTORY**

08/31—Revision 0: Initial Version

# **SPECIFICATIONS**

#### Table 1. DC Electrical Characteristics

| Parameter                                                       | Symbol            | Min                   | Тур | Max                   | Unit |

|-----------------------------------------------------------------|-------------------|-----------------------|-----|-----------------------|------|

| OPERATING CONDITIONS                                            |                   |                       |     |                       |      |

| 1.8 V Supply Voltage (VDD18RF, VDD18VCO, VDD18BB, VDD18DIG)     | V <sub>DD18</sub> | 1.7                   | 1.8 | 1.9                   | V    |

| IO Supply Voltage                                               | VDDIO             | 1.7                   | 3.3 | 3.6                   | V    |

| BBAGC Input Voltage                                             | VBBAGC            | 0                     |     | 1.8                   | V    |

| BBAGC Input Current                                             | <b>I</b> BBAGC    | -10                   |     | 10                    | μA   |

| DIGITAL IN/OUTPUT PINS (RESETB, TSPD, PD, AS, SCL,SDA, HOLDAGC) |                   |                       |     |                       |      |

| Maximum Low Input Voltage                                       | VIL               |                       |     | 0.3×V <sub>DDIO</sub> | V    |

| Minimum High Input Voltage                                      | VIH               | 0.7×V <sub>DDIO</sub> |     |                       | V    |

| Maximum Low Output Voltage                                      | Vol               |                       |     | 0.3×V <sub>DDIO</sub> | V    |

| Minimum High Output Voltage                                     | VOH               | 0.7×V <sub>DDIO</sub> |     |                       | V    |

| High Level Input Current (VIN=V <sub>DDIO</sub> )               | I <sub>IH</sub>   | -10                   |     | 10                    | μΑ   |

| Low Level Input Current (VIN=GND)                               | I⊫                | -10                   |     | 10                    | μA   |

| VHF POWER CONSUMPTION                                           |                   |                       |     |                       |      |

| 1.8 V Analog Current Consumption                                | IDD18AVHF         |                       | 98  |                       | mA   |

| 1.8 V Digital Current Consumption                               | IDD18DVHF         |                       | 1   |                       | mA   |

| IO Digital Current Consumption                                  |                   |                       | 1   |                       | mA   |

| Power Down Current Consumption                                  |                   |                       | 1   | 200                   | μΑ   |

| Total Power Consumption                                         | PVHF              |                       | 180 |                       | mW   |

| UHF POWER CONSUMPTION                                           |                   |                       |     |                       |      |

| 1.8 V Analog Current Consumption                                | IDD18AUHF         |                       | 110 |                       | mA   |

| 1.8 V Digital Current Consumption                               | IDD18DUHF         |                       | 1   |                       | mA   |

| IO Digital Current Consumption                                  |                   |                       | 1   |                       | mA   |

| Power Down Current Consumption                                  |                   |                       | 1   | 200                   | μA   |

| Total Power Consumption                                         | PUHF              |                       | 200 |                       | mW   |

#### Table 2. AC Electrical Characteristics

$T_{\rm A}$  = 25°C,  $V_{\rm DD18}$  = 1.8 V,  $V_{\rm DDIO}$  = 3.3 V, unless otherwise noted.

| Parameter                                            | Symbol                  | Min  | Тур | Max | Unit   |

|------------------------------------------------------|-------------------------|------|-----|-----|--------|

| Reference Crystal or Clock Input Frequency           | f <sub>CLK</sub>        | 13   |     | 40  | MHz    |

| VHF CHARACTERISTICS <sup>1</sup>                     |                         |      |     |     |        |

| RF Frequency Range                                   | f <sub>VHF</sub>        | 174  |     | 245 | MHz    |

| RF Input Impedance                                   | Zin                     |      | 50  |     | Ω      |

| Input VSWR                                           | VSWR                    |      |     | 2:1 |        |

| Typical AGC Dynamic Range                            | P <sub>IN</sub>         | -102 |     | 0   | dBm    |

| Noise Figure @ Max Gain                              | NF                      |      | 3   | TBD | dB     |

| In-Band Two Tone IMD <sub>3</sub> <sup>2</sup> (U/D) | IMD <sub>3</sub>        |      | -45 | TBD | dBc    |

| Out-band IIP <sub>3</sub> <sup>3</sup>               | IIP <sub>3</sub>        | TBD  | -4  |     | dBm    |

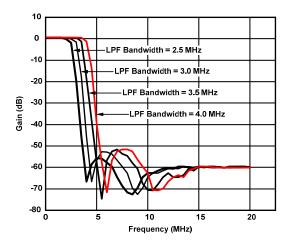

| 3 dB Cut-off Frequency <sup>4</sup>                  | <b>f</b> <sub>3dB</sub> | 2.5  |     | 4   | MHz    |

| Stop Band Attenuation <sup>5</sup>                   | SBA                     |      | 55  |     | dBc    |

| LO Phase Noise (SSB @ 10 kHz Offset)                 | PN                      |      | -90 | TBD | dBc/Hz |

| Baseband Output Amplitude Vpp, Single                | VOUTAC                  | 300  | 500 | 700 | mV     |

| Maximum Load @ PP Output Ding Differential           | 7                       | 2    |     |     | kΩ     |

| Maximum Load @ BB Output Pins, Differential          | Z <sub>MAX</sub>        |      |     | 20  | pF     |

| Output DC Voltage @ BB Output Pins                   | Voutdc                  |      | 0.9 |     | V      |

| Parameter                                   | Symbol           | Min  | Тур | Max | Unit   |

|---------------------------------------------|------------------|------|-----|-----|--------|

| UHF CHARACTERISTICS                         |                  |      |     |     |        |

| RF Frequency Range                          | f <sub>UHF</sub> | 470  |     | 862 | MHz    |

| RF Input Impedance                          | Z <sub>IN</sub>  |      | 50  |     | Ω      |

| Input VSWR                                  | VSWR             |      |     | 2:1 |        |

| Typical AGC Dynamic Range                   | P <sub>IN</sub>  | -102 |     | 0   | dBm    |

| Noise figure @ Max Gain                     | NF               |      | 4.5 | TBD | dB     |

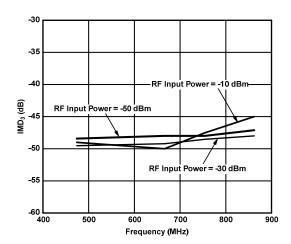

| In-band Two Tone IMD₃²(U/D)                 | IMD <sub>3</sub> |      | -48 | TBD | dBc    |

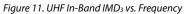

| Out-band IIP <sub>3</sub> <sup>3</sup>      | IIP <sub>3</sub> | TBD  | -5  |     | dBm    |

| 3 dB Cut-off Frequency⁴                     | f <sub>3dB</sub> | 2.5  |     | 4   | MHz    |

| Stop Band Attenuation <sup>5</sup>          | SBA              |      | 55  |     | dBc    |

| LO Phase Noise (SSB @ 10 kHz Offset)        | PN               |      | -90 | TBD | dBc/Hz |

| Baseband Output Amplitude Vpp, Single       | VOUTAC           | 300  | 500 | 700 | mV     |

| Maximum Load @ PP Quitaut Ding Differential | 7                | 2    |     |     | kΩ     |

| Maximum Load @ BB Output Pins, Differential | Z <sub>MAX</sub> |      |     | 20  | pF     |

| Output DC Voltage @ BB Output Pins          | VOUTDC           |      | 0.9 |     | V      |

#### NOTES

<sup>1</sup>VHF band is supported by ADMTV102BCPZRL. See Ordering Guide.

<sup>2</sup>For RF input power  $P_{IN} < -30$  dBm, f1, f2 = 200 kHz Frequency offset. <sup>3</sup>For RF input power  $P_{IN} = -80$  dBm, two-tone interferer power is -35 dBm, Frequency offset f1 = 13.25 MHz, f2 = 29.25 MHz. RFAGC: closed loop gain control, BBAGC: external gain control. <sup>4</sup>Programmable.

<sup>5</sup> For 6 MHz offset @ LPF cut-off 4 MHz

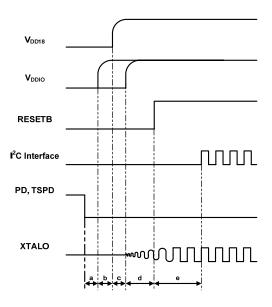

#### Table 3. Digital Timing Diagram

| Characteristic                               | Symbol | Min        | Unit |

|----------------------------------------------|--------|------------|------|

| PD Set-up Margin                             | a      | Don't Care | μs   |

| Power up Set-up Margin for V <sub>DD18</sub> | b      | Don't Care | μs   |

| Power up Set-up Margin for VDDIO             | c      | Don't Care | μs   |

| RESETB Set-up Time for RESETB                | d      | 100        | μs   |

| Set-up Time for I <sup>2</sup> C Interface   | e      | 100        | μs   |

Figure 2. Digital Timing Diagram

## **ABSOLUTE MAXIMUM RATINGS**

| Table 4. ( | $T_{\rm A}=25^{\circ}{\rm C},$ | unless otherwise | noted.) |

|------------|--------------------------------|------------------|---------|

|------------|--------------------------------|------------------|---------|

| Parameter                                                      | Rating                               |

|----------------------------------------------------------------|--------------------------------------|

| 1.8 V Supply Voltage (VDD18RF,<br>VDD18VCO, VDD18BB, VDD18DIG) | –0.3 V to +3.5 V                     |

| IO Supply Voltage (VDDIO)                                      | -0.3 V to +5.5 V                     |

| Analog Input Voltage                                           | –0.3 V to V <sub>DD18</sub> +0.3 V   |

| Digital Input Voltage                                          | -0.3 V to V <sub>DDIO</sub> $+0.3$ V |

| Analog Output Voltage                                          | -0.3 V to V <sub>DD18</sub> +0.3 V   |

| Digital Output Voltage                                         | –0.3 V to V <sub>DDIO</sub> +0.3 V   |

| Operating Temperature                                          | –45°C to +85°C                       |

| Storage Temperature Range                                      | –65°C to +150°C                      |

NOTES

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those listed in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. Only one absolute maximum rating may be applied at any one time.

## **ESD CAUTION**

ESD (electrostatic discharge) sensitive device. Although this product features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

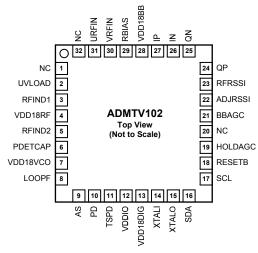

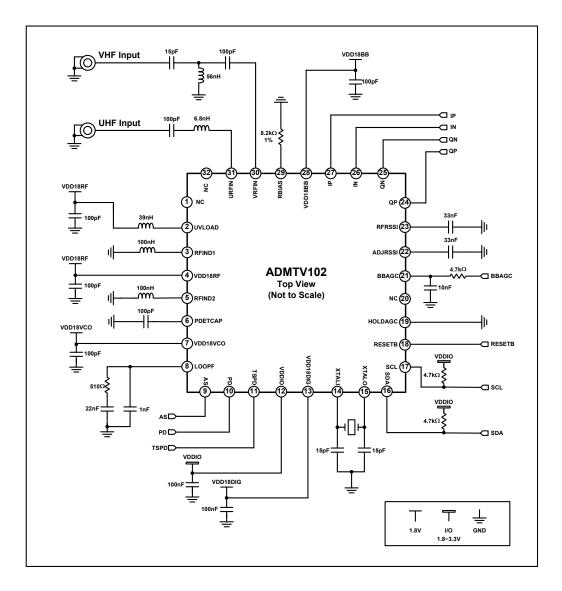

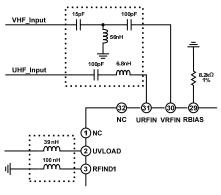

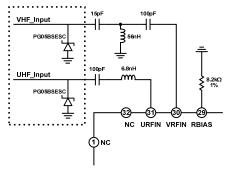

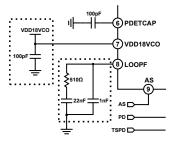

# **PIN CONFIGURATION AND FUNCTION DESCRIPTIONS**

Figure 3. 32-Lead QFN Pin Configuration

| Table 5. Pi | n Function Desc | riptions |                                                                                                                                                                          |

|-------------|-----------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin No.     | Mnemonic        | l/O Type | Description                                                                                                                                                              |

| 1           | NC              |          | No connection.                                                                                                                                                           |

| 2           | UVLOAD          | AO       | VHF/UHF LNA load inductor. Connect a 39 nH from this pin to VDD18RF as close as possible.                                                                                |

| 3           | RFIND1          | AI       | RFPGA inductor for bias. Connect a 100 nH from this pin to GND as close as possible.                                                                                     |

| 4           | VDD18RF         | Power    | RF power 1.8 V. Power decoupling capacitor is required. See application schematic.                                                                                       |

| 5           | RFIND2          | AI       | RFPGA inductor for bias. Connect a 100 nH from this pin to GND as close as possible.                                                                                     |

| 6           | PDETCAP         | AO       | External capacitor for RF power detector. Connect a 100 pF to GND.                                                                                                       |

| 7           | VDD18VCO        | Power    | VCO power 1.8 V. Power decoupling capacitor is required. See application schematic                                                                                       |

| 8           | LOOPF           | AI       | External loop filter components. Connect from this pin as close as possible.                                                                                             |

| 9           | AS              | DI       | Address select input. I <sup>2</sup> C address can be determined by AS pin.                                                                                              |

|             |                 |          | If AS is GND, read mode: $0 \times c3$ , write mode: $0 \times c2$ .                                                                                                     |

|             |                 |          | If AS is VDDIO, read mode: 0×c5, write mode: 0×c4.                                                                                                                       |

| 10          | PD              | DI       | Hardware power down. 0 V for operation and VDDIO for power down.                                                                                                         |

|             |                 |          | To recover from the hardware PD state, PD control signal level from the controller should be low first. So the clock oscillator is powered up and the tuner can operate. |

| 11          | TSPD            | DI       | Time-slicing hardware power down. 0 V for operation and VDDIO for power down.                                                                                            |

| 12          | VDDIO           | Power    | IO power. 1.8 V ~ 3.3 V wide range IO.                                                                                                                                   |

|             |                 |          | Power decoupling capacitor is required. See application schematic.                                                                                                       |

| 13          | VDD18DIG        | Power    | Digital power 1.8 V. Power decoupling capacitor is required. See application schematic.                                                                                  |

| 14          | XTALI           | DI       | Crystal oscillator input. Inverter buffer input. PD should be 'low' state to oscillate.                                                                                  |

| 15          | XTALO           | DO       | Crystal oscillator output. Inverter buffer output. PD should be 'low' state to oscillate.                                                                                |

| 16          | SDA             | DB       | I <sup>2</sup> C data. Bi-directional pin. Open drain output. Requires a pull-up resistor to VDDIO.                                                                      |

| 17          | SCL             | DI       | I <sup>2</sup> C clock. Requires a pull-up resistor to VDDIO.                                                                                                            |

| 18          | RESETB          | DI       | Reset input. 0 V for reset, VDDIO for normal operation.                                                                                                                  |

| 19          | HOLDAGC         | DI       | Test pin for holding AGC operation. Connect to GND for operation.                                                                                                        |

| 20          | NC              |          | No connection.                                                                                                                                                           |

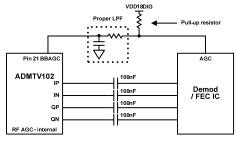

| 21          | BBAGC           | AI       | External BBAGC input. 0 V ~ 1.8 V analog input.                                                                                                                          |

| 22          | ADJRSSI         | AO       | RSSI output voltage for adjacent channels. Connect a 33 nF to GND.                                                                                                       |

| 23          | RFRSSI          | AO       | RSSI output voltage for wanted channel. Connect a 33 nF to GND.                                                                                                          |

| 24          | QP              | AO       | Quadrature-phase positive output.                                                                                                                                        |

#### Table 5. Pin Function Descriptions

| Pin No. | Mnemonic | l/O Type | Description                                                                                             |

|---------|----------|----------|---------------------------------------------------------------------------------------------------------|

| 25      | QN       | AO       | Quadrature-phase negative output.                                                                       |

| 26      | IN       | AO       | In-phase negative output.                                                                               |

| 27      | IP       | AO       | In-phase positive output.                                                                               |

| 28      | VDD18BB  | Power    | Baseband block power 1.8 V. Power decoupling capacitor is required. See application schematic.          |

| 29      | RBIAS    | AI       | Bias reference input. Connect a 8.2 k $\Omega$ (1% tolerance) from this pin to GND as close as possible |

| 30      | VRFIN    | AI       | VHF RF input.                                                                                           |

| 31      | URFIN    | AI       | UHF RF input.                                                                                           |

| 32      | NC       |          | No connection.                                                                                          |

NOTES

Al = Analog Input, AO = Analog Output, DI = Digital Input, DO = Digital Output, DB = Digital Bi-directional

# TERMINOLOGY

## Table 6. Terminology

| Parameter | Description                         |

|-----------|-------------------------------------|

| AGC       | Automatic gain control.             |

| IMD       | Intermodulation distortion.         |

| RSSI      | Received signal strength indicator. |

| LNA       | Low noise amplifier.                |

| LPF       | Low pass filter.                    |

| PGA       | Programmable gain amplifier.        |

| PLL       | Phase locked loop.                  |

| QFN       | Quad flat no-lead package.          |

| SCL       | Serial clock.                       |

| SDA       | Serial data.                        |

| SNR       | Signal to noise ratio.              |

| TA        | Ambient temperature.                |

| VCO       | Voltage controlled oscillator.      |

| VGA       | Variable gain amplifier.            |

| VSWR      | Voltage standing wave ratio.        |

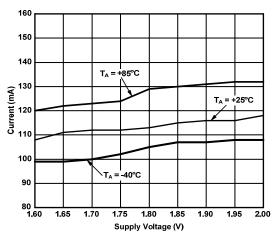

## **TYPICAL PERFORMANCE CHARACTERISTICS**

$T_A = 25^{\circ}$ C,  $V_{DD18} = 1.8$  V,  $V_{DDIO} = 3.3$  V, unless otherwise noted.

Figure 4. UHF Receiver Mode Current vs. Supply Voltage

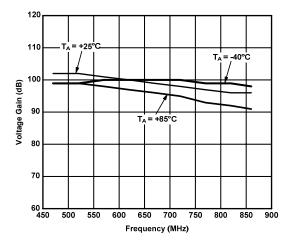

Figure 5. UHF Voltage Gain vs. Frequency

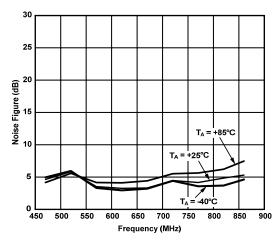

Figure 6 . UHF Noise Figure vs. Frequency

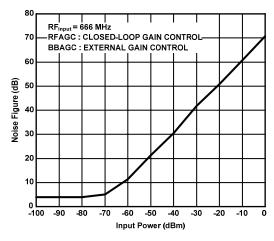

Figure 7. UHF Noise Figure vs. Input Power

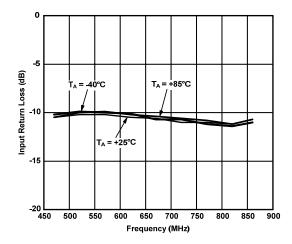

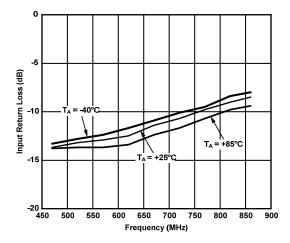

Figure 8. UHF Input Return Loss vs. Frequency [LNA Gain Mode: High]

Figure 9. UHF Input Return Loss vs. Frequency [LNA Gain Mode: Low]

Figure 10. UHF In-Band IIP3 vs. Input Power

Figure 12. UHF Out-Band IIP<sub>3</sub> vs. Frequency

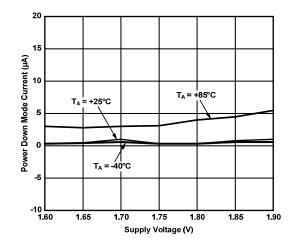

Figure 13.UHF Power Down Mode Current vs. Supply Voltage

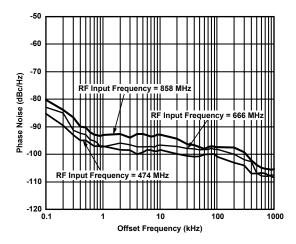

Figure 14. UHF Phase Noise vs. Offset Frequency

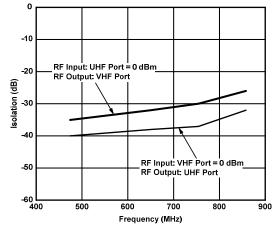

Figure 15. Port-to-Port Isolation

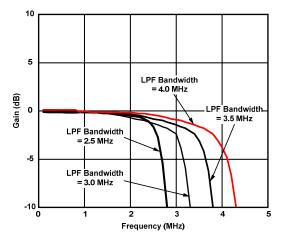

Figure 16. UHF Tunable Low Pass Filter Response

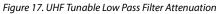

Figure 18. S<sub>11</sub> of UHF RFIN vs. Frequency [High Gain Mode]

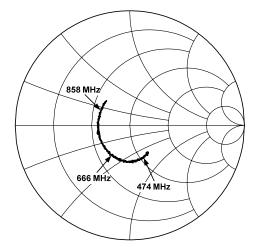

Figure 19. S<sub>11</sub> of UHF RFIN vs. Frequency [Low Gain Mode]

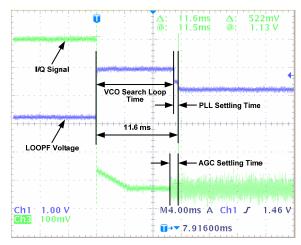

Figure 20. Software Power ON Timing

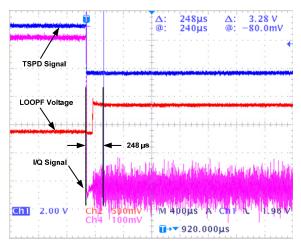

Figure 21. Time-slicing Power ON Timing

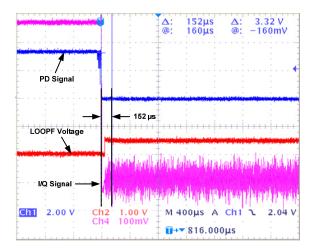

Figure 22. Hardware Power ON Timing

## **FUNCTIONAL DESCRIPTIONS**

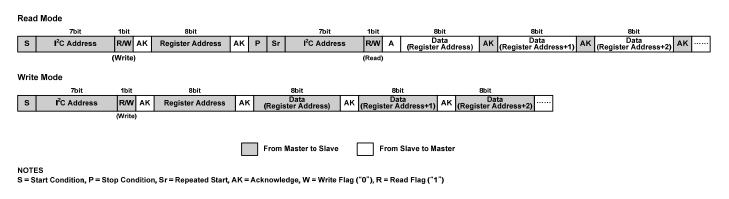

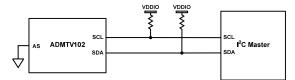

## **I<sup>2</sup>C OPERATION**

The ADMTV102 is controlled by an  $I^2C$  data bus and is compatible with industry standard supporting fast mode format. Data and clock are fed on the SDA and SCL lines, respectively, as defined by the  $I^2C$  bus format. The device can either accept data in the write-mode, or send data in the read-mode. The LSB of the address byte sets the device into write mode if it is low and read mode if it is high.

## I<sup>2</sup>C READ/WRITE ADDRESS

| Address Select Pin |     | Address |   |           |   |   |   |     |     |

|--------------------|-----|---------|---|-----------|---|---|---|-----|-----|

|                    | ·   |         | F | READ MODE |   |   |   |     |     |

| AS                 | MSB |         |   |           |   |   |   | LSB | Hex |

| Low                | 1   | 1       | 0 | 0         | 0 | 0 | 1 | 1   | C3  |

| High               | 1   | 1       | 0 | 0         | 0 | 1 | 0 | 1   | C5  |

|                    |     |         | V | RITE MODE |   |   |   |     |     |

| AS                 | MSB |         |   |           |   |   |   | LSB | Hex |

| Low                | 1   | 1       | 0 | 0         | 0 | 0 | 1 | 0   | C2  |

| High               | 1   | 1       | 0 | 0         | 0 | 1 | 0 | 0   | C4  |

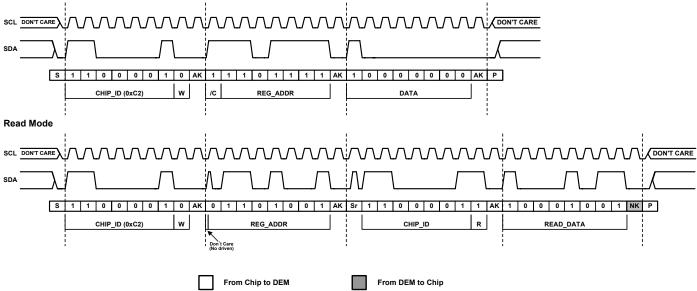

## I<sup>2</sup>C BUS FORMAT

Figure 23. I<sup>2</sup>C Bus Format

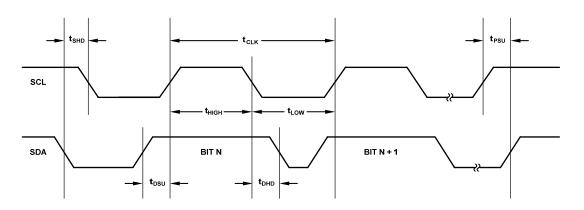

## TIMING CHARACTERISTICS

#### $(T_A = 25^{\circ}C, V_{DDIO} = 3.3 V, GND = 0 V, unless otherwise noted.)$

According to standard I<sup>2</sup>C specification, the CLK frequency reaches maximum 400 kHz in fast-mode and 100 kHz in standard-mode. To communicate with RF tuner, you need to comply as the following timing diagrams.

NOTES

S = Start Condition, P = Stop Condition, Sr = Repeated Start (Stop + Start, fast transition) condition, AK = Acknowledge : Active low, NK = Not Acknowledge : Active high, W = Write mode, R = Read mode, C = Automatic Address Increase mode, /C = Single Input Address mode ADMTV102 meets the demanding performance specification of I<sup>2</sup>C combined mode. Therefore, upper access condition is able to be modified on standard I<sup>2</sup>C.

Figure 24. Serial Control Port Write/ Read Mode

Figure 25. Serial Control Port Timing

#### **Table 8. Serial Control Port Timing**

|                                                 |                  | Sta | ndard-mode | F   | ast-mode |      |

|-------------------------------------------------|------------------|-----|------------|-----|----------|------|

| Parameter                                       | Symbol           | Min | Max        | Min | Max      | Unit |

| Hold Time (Repeat) Start Condition <sup>1</sup> | t <sub>shD</sub> | 4.0 |            | 0.6 |          | μs   |

| SCL Clock Period                                | t <sub>CLK</sub> | 0   | 100        | 0   | 400      | kHz  |

| HIGH Period of the SCL Clock                    | thigh            | 4.0 |            | 0.6 |          | μs   |

| LOW Period of the SCL Clock                     | t <sub>LOW</sub> | 4.7 |            | 1.3 |          | μs   |

|                                                  |                  | Sta            | Standard-mode     |                  | Fast-mode |      |

|--------------------------------------------------|------------------|----------------|-------------------|------------------|-----------|------|

| Parameter                                        | Symbol           | Min            | Max               | Min              | Max       | Unit |

| Set-up Time for STOP Condition                   | t <sub>PSU</sub> | 4.0            |                   | 0.6              |           | μs   |

| Data Set-up Time                                 | t <sub>DSU</sub> | 250            |                   | 100 <sup>2</sup> |           | μs   |

| Data Hold Time for I <sup>2</sup> C Bus Devices. | <b>t</b> DHD     | 5.0            |                   |                  |           | μs   |

|                                                  |                  | 0 <sup>3</sup> | 3.45 <sup>4</sup> | 0 <sup>3</sup>   | 0.94      | μs   |

NOTES

<sup>1</sup>Afer this period, the first clock pulse is generated. <sup>2</sup>A fast-mode l<sup>2</sup>C-bus device can be used in a standard-mode l<sup>2</sup>C-bus system, but the requirement  $t_{DSU} \ge 250$  ns must then be met. This will automatically be the case if the device does not stretch the LOW period of the SCL signal.

<sup>3</sup>A device must internally provide a hold time of at least 300 ns for the SDA signal to bridge the undefined region of the falling edge of SCL. <sup>4</sup>The maximum  $t_{DHD}$  has only to be met if the device does not stretch the LOW period ( $t_{LOW}$ ) of the SCL signal.

## I<sup>2</sup>C REGISTER MAP

## Table 9. I<sup>2</sup>C Register Map.

| Addr<br>(Hex) | Туре       | Parameter             | (MSB)<br>Bit 7 | Bit 6              | Bit 5               | Bit 4    | Bit 3         | Bit 2        | Bit 1       | (LSB)<br>Bit 0 | Reset<br>Value<br>(Hex) | Initiali<br>zation<br>Value<br>(Hex) |

|---------------|------------|-----------------------|----------------|--------------------|---------------------|----------|---------------|--------------|-------------|----------------|-------------------------|--------------------------------------|

| 00            | R          | SPLITID               |                |                    | •                   | SPLI     | TID<7:0>      | •            |             | •              | 0e                      |                                      |

| 01            | R          | CHIPID 0              |                |                    |                     | CHIP     | 'ID<15:8>     |              |             |                | 02                      |                                      |

| 02            | R          | CHIPID 1              |                |                    |                     | CHI      | PID<7:0>      |              |             |                | 00                      |                                      |

| 03            | R          |                       |                |                    |                     |          | Reserved      |              |             |                |                         |                                      |

| 04            | R          | BBAGC 0<br>and        |                | GVBE               | 3<3:0>              |          |               | ADCOU        | JT<3:0>     |                |                         |                                      |

|               |            | Loop Filter           |                |                    |                     |          |               |              |             |                |                         |                                      |

| 05            | R          | RFAGC 0               |                |                    |                     | RFA      | GC<7:0>       |              |             |                |                         |                                      |

| 06            | R          | RFAGC 1               |                |                    | Rese                | erved    |               |              | LOCK<0>     | RFAGC<8>       |                         |                                      |

| 07 to<br>09   | R          |                       |                |                    |                     |          | Reserved      |              |             |                |                         |                                      |

| 0a            | R          | I/Q OFFSET 0          |                | IOFFSE             | T<11:8>             |          |               | QOFFSE       | T<11:8>     |                |                         |                                      |

| 0b            | R          | IOFFSET 1             |                |                    |                     | IOFF     | SET<7:0>      |              |             |                |                         |                                      |

| 0c            | R          | QOFFSET 1             |                |                    |                     | QOF      | -SET<7:0>     |              |             |                |                         |                                      |

| 0d            | R          | LNA 0<br>and<br>VCO 0 | Blank          |                    |                     |          |               |              |             |                |                         |                                      |

| 0e            | R          | Low Pass<br>Filter 0  | Blank          |                    | Blank CTUNEI2C<4:0> |          | CTUNEI2C<4:0> |              |             |                |                         |                                      |

| Of            | R          | Low Pass<br>Filter 1  |                | Blank CTUNE<4:0>   |                     |          |               |              |             |                |                         |                                      |

| 10            | R/W        | RF Band<br>Select     | BAND           | BAND<1:0> Reserved |                     | 49       | 4c            |              |             |                |                         |                                      |

| 11 to<br>14   | R/W        |                       |                | Reserved           |                     |          |               | ·            | •           |                |                         |                                      |

| 15            | R/W        | Low Pass<br>Filter 2  | Bla            | ink                |                     | Reserved |               |              | LPFBW<2:0>  | •              | 25                      | 3d                                   |

| 16            | R/W        |                       |                |                    |                     |          | Reserved      |              |             |                |                         |                                      |

| 17            | R/W        | RSSI                  | Reserved       |                    | ADJ<2:0>            |          |               | TOP          | <3:0>       |                | c8                      | 9a                                   |

| 18            | R/W        |                       |                |                    |                     |          | Reserved      |              |             |                |                         |                                      |

| 19            | R/W        | PLL 0                 |                | Rese               | erved               |          |               | PLLR         | <3:0>       |                | 01                      |                                      |

| 1a            | R/W        | PLL 1                 |                | ICP<5              |                     | <5:0>    |               | PLLN<9:8>    |             | 28             |                         |                                      |

| 1b            | R/W        | PLL 2                 |                |                    |                     | PLI      | N<7:0>        |              |             |                | 20                      |                                      |

| 1c            | R/W        | VCO 1<br>And PLL 3    | VCOSEL<0>      |                    | DIVSEL<2:0>         | >        |               | PLLF<        | :19:16>     |                | 30                      |                                      |

| 1d            | R/W        | PLL 4                 |                |                    |                     | PLL      | F<15:8>       |              |             |                | 00                      |                                      |

| 1e            | R/W        | PLL 5                 |                |                    |                     | PLI      | _F<7:0>       |              |             |                | 80                      |                                      |

| 1f to         | R/W        |                       | I.             |                    |                     |          | Reserved      |              |             |                | 1                       | 1                                    |

| 23            |            |                       |                |                    |                     |          |               |              |             |                |                         |                                      |

| 24            | R/W        | Low Pass<br>Filter 3  | Reserved       | (                  | CLKSELI2C<2:0       | 0>       |               | Rese         | erved       |                | ad                      | 1a                                   |

| 25            | R/W        | Low Pass<br>Filter 4  |                | (                  | TUNEOFS<4:          | 0>       |               | EXTUNE<0>    | TUNEEN<0>   | Reserved       | 02                      | 6e                                   |

| 26 to<br>2e   | R/W        |                       |                |                    |                     |          | Reserved      |              |             |                |                         |                                      |

| 2f            | R/W<br>R/W | PLL 6                 | RST_PLL<0>     | PC4<0>             | PC8_16<0>           | •        | Poconvod      | VCORG_I2C<4: | 0>          |                | 10                      |                                      |

| 30            |            | DDACC 1               |                |                    | Descrived           |          | Reserved      | -            |             | n.             | 44                      | 04                                   |

| 31            | R/W        | BBAGC 1               |                |                    | Reserved            |          |               | L            | DIVAGOCK<2: | 02             | 44                      | 04                                   |

| Addr<br>(Hex) | Туре | Parameter                 | (MSB)<br>Bit 7      | Bit 6           | Bit 5          | Bit 4            | Bit 3                    | Bit 2             | Bit 1              | (LSB)<br>Bit 0   | Reset<br>Value<br>(Hex) | Initiali<br>zation<br>Value<br>(Hex) |

|---------------|------|---------------------------|---------------------|-----------------|----------------|------------------|--------------------------|-------------------|--------------------|------------------|-------------------------|--------------------------------------|

| 32 to<br>38   | R/W  |                           |                     |                 |                | Re               | eserved                  |                   |                    |                  |                         |                                      |

| 39            | R/W  | VCO 2                     | Reserved            | EXTVCORG<br><0> |                |                  | Rese                     | erved             |                    |                  | 80                      |                                      |

| 3a to<br>42   | R/W  |                           |                     |                 | L              | Re               | eserved                  |                   |                    |                  | 1                       | 1                                    |

| 43            | R/W  | TSPD 0                    | Blank               | TSPD<br>ALL<0>  | TSPD<br>PLL<0> | TSPD<br>VCO<0>   | TSPD<br>RSSIRTUNE<br><0> | TSPD<br>RFRSSI<0> | TSPD<br>ADJRSSI<0> | TSPD<br>PWDET<0> | 7f                      |                                      |

| 44            | R/W  | TSPD 1                    | TSPD<br>OSC<0>      | TSPD<br>LPF<0>  | TSPD<br>MIX<0> | TSPD<br>RFPGA<0> | TSPD<br>LNA<0>           | TSPD<br>BGR<0>    | TSPD<br>TPSNS<0>   | TSPD<br>BBPGA<0> | ff                      | f8                                   |

| 45            | R/W  | SWPD 0                    | Blank               | SWPD<br>ALL<0>  | SWPD<br>PLL<0> | SWPD<br>VCO<0>   | SWPD<br>RSSIRTUNE<br><0> | SWPD<br>RFRSSI<0> | SWPD<br>ADJRSSI<0> | SWPD<br>PWDET<0> | 00                      |                                      |

| 46            | R/W  | SWPD 1                    | Blank               | SWPD<br>LPF<0>  | SWPD<br>MIX<0> | SWPD<br>RFPGA<0> | SWPD<br>LNA<0>           | SWPD<br>BGR<0>    | SWPD<br>TPSNS<0>   | SWPD<br>BBPGA<0> | 00                      |                                      |

| 47            | R/W  | RF Gain<br>And<br>BBAGC 2 | LNAGAINI2C<br><1:0> |                 |                | Rese             | erved                    |                   |                    | EXTGVBB<br><0>   | c2                      |                                      |

| 48            | R/W  | BBAGC 3                   |                     | GVBBI2          | C<3:0>         |                  |                          | Rese              | erved              |                  | 82                      | 21                                   |

| 49 to<br>50   | R/W  |                           |                     | Reserved        |                |                  |                          |                   |                    |                  |                         |                                      |

| 51            | R/W  | RFAGC 2                   |                     |                 | Blank          |                  |                          | RFAGCMAX<br><8>   | RFAGCMIN<br><8>    | RFAGCI2C<br><8>  | 05                      |                                      |

| 52            | R/W  | RFAGC3                    |                     |                 |                | RFAGCN           | IAX<7:0>                 |                   |                    |                  | 7f                      |                                      |

| 53            | R/W  | RFAGC 4                   |                     |                 |                | RFAGCN           | 1IN<7:0>                 |                   |                    |                  | 01                      |                                      |

| 54            | R/W  | RFAGC 5                   |                     |                 |                | RFAGCI           | 2C<7:0>                  |                   |                    |                  | 7f                      |                                      |

| 55            | R/W  | TSPD<br>Polarity          |                     |                 |                | Reserved         |                          |                   |                    | TSPDPOL<br><0>   | f0                      |                                      |

NOTES

This table has reserved bits in order to guarantee performance. Contact Analog Devices to get the latest initialization file. Reset value is factory value.

R: Read Only.

R/W: Read and Write.

## **DETAILED REGISTER DESCRIPTION**

## Table 10. Read-only Register

| Reg.<br>Addr<br>(Hex) | Bit(s) | Name          | Description                                                                                                                                                                                                                                                                                                                            |

|-----------------------|--------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 00                    | <7:0>  | SPLITID<7:0>  | Chip split ID.                                                                                                                                                                                                                                                                                                                         |

| 01                    | <7:0>  | CHIPID<15:8>  | Chip ID.                                                                                                                                                                                                                                                                                                                               |

| 02                    | <7:0>  | CHIPID<7:0>   | Chip ID.                                                                                                                                                                                                                                                                                                                               |

| 04                    | <3:0>  | ADCOUT<3:0>   | VLFO( PLL loop filter output voltage) = 0.2 + ADCOUT × 0.1 ~ 0.3 + ADCOUT × 0.1<br>If ADCOUT is 0×C2.<br><3:0> = 0×2: VLFO = 0.2 + 2 × 0.1 = 0.4 V<br><3:0> = 0×C: VLFO = 0.2 + 12 × 0.1 = 1.3 V                                                                                                                                       |

| 04                    | <7:4>  | GVBB<3:0>     | Baseband PGA gain control. Step: 3 dB.<br><3:0> = 0×00: Minimum gain.<br><3:0> = 0×0e: Maximum gain.                                                                                                                                                                                                                                   |

| 05                    | <7:0>  | RFAGC<7:0>    | Gain code value of RFPGA.                                                                                                                                                                                                                                                                                                              |

| 06                    | <0>    | RFAGC<8>      | $\langle 8:0 \rangle = 0 \times 000$ : RFAGC minimum gain.<br>$\langle 8:0 \rangle = 0 \times 17$ f: RFAGC maximum gain.                                                                                                                                                                                                               |

| 06                    | <1>    | LOCK<0>       | PLL lock indicator.<br><0> = 0×1: PLL is locked.<br><0> = 0×0: PLL is unlocked.                                                                                                                                                                                                                                                        |

| 0a                    | <3:0>  | QOFFSET<11:8> | I/Q path DC offset digital code value.                                                                                                                                                                                                                                                                                                 |

| 0a                    | <7:4>  | IOFFSET<11:8> | <11:0> = 0×000: Minimum value.                                                                                                                                                                                                                                                                                                         |

| 0b                    | <7:0>  | IOFFSET<7:0>  | $<11:0> = 0\times800$ : Norminal center value when there is no DC offset.                                                                                                                                                                                                                                                              |

| 0c                    | <7:0>  | QOFFSET<7:0>  | <11:0> = 0×fff: Maximum value.                                                                                                                                                                                                                                                                                                         |

| 0d                    | <4:0>  | VCORG<4:0>    | VCO varactor diode operation range (varactor switch).<br>$<4:0> = 0\times00$ : Lowest frequency of VCO oscillation.<br>$<4:0> = 0\times1f$ : Highest frequency of VCO oscillation.                                                                                                                                                     |

| 0d                    | <6:5>  | LNAGAIN<1:0>  | LNAGAIN status.<br><1:0> = 0×0: Low gain.<br><1:0> = 0×3: High gain.                                                                                                                                                                                                                                                                   |

| 0e                    | <4:0>  | CTUNEI2C<4:0> | Cap bank value after auto tuning without offset value.                                                                                                                                                                                                                                                                                 |

| Of                    | <4:0>  | CTUNE<4:0>    | CTUNE is a low pass filter's cap bank value plus offset. CTUNE value is calculated as below condition.<br>CTUNE value.<br>1) If EXTUNE = 0,<br>CTUNE<4:0> = CTUNEI2C<4:0> + CTUNEOFS<3:0> when CTUNEOFS<4> = 0,<br>CTUNE<4:0> = CTUNEI2C<4:0> - CTUNEOFS<3:0> when CTUNEOFS<4> = 1,<br>2) If EXTUNE = 1,<br>CTUNE<4:0> = CTUNEOFS<4:0> |

NOTES

## Table 11. Signal Path Register Setting

| Reg.<br>Addr |       |                |                                                                                                 |

|--------------|-------|----------------|-------------------------------------------------------------------------------------------------|

|              | . ,   | Name           | Description                                                                                     |

| 10           | <7:6> | BAND<1:0>      | RF input band selection.                                                                        |

|              |       |                | <1:0> = 0×0: VHF                                                                                |

|              |       |                | <1:0> = 0×1: UHF                                                                                |

|              |       |                | <1:0> = 0×2: UHF                                                                                |

| 5            | <2:0> | LPFBW<2:0>     | Low pass filter cut-off frequency selection.                                                    |

|              |       |                | $\langle 2:0 \rangle = 0 \times 5:4$ MHz (For 8 MHz channel bandwidth)                          |

|              |       |                | $\langle 2:0 \rangle = 0 \times 4: 3.5$ MHz (For 7 MHz channel bandwidth)                       |

|              |       |                | $\langle 2:0 \rangle = 0 \times 3:3$ MHz (For 6 MHz channel bandwidth)                          |

|              |       |                | $\langle 2:0 \rangle = 0 \times 2:2.5$ MHz (For 5 MHz channel bandwidth)                        |

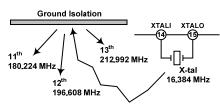

| 4            | <6:4> | CLKSELI2C<2:0> | Reference clock selection.                                                                      |

|              |       |                | $<2:0> = 0\times0: 13 \text{ MHz}$                                                              |

|              |       |                | $<2:0> = 0\times1:16.384$ MHz                                                                   |

|              |       |                | $<2:0> = 0\times2: 19.2 \text{ MHz}$                                                            |

|              |       |                | $<2:0> = 0\times3: 20.48 \text{ MHz}$                                                           |

|              |       |                | <2:0> = 0×4: 24.576 MHz                                                                         |

|              |       |                | $<2:0> = 0\times5:26$ MHz                                                                       |

|              |       |                | $<2:0> = 0\times6:36$ MHz                                                                       |

|              |       |                | $<2:0> = 0\times7:38.4$ MHz                                                                     |

| 5            | <1>   | TUNEEN<0>      | Cut-off frequency auto tuning enable of low pass filter.                                        |

|              |       |                | $<0> = 0\times0$ : Disable.                                                                     |

|              |       |                | $\langle 0 \rangle = 0 \times 1$ : Enable.                                                      |

| 5            | <2>   | EXTUNE<0>      | External setting enable of low pass filter cap bank. See CTUNE<4:0> description (0×0f address). |

|              |       |                | $<0> = 0\times0$ : Disable.                                                                     |

|              |       |                | $\langle 0 \rangle = 0 \times 1$ : Enable.                                                      |

| 5            | <7:3> | CTUNEOFS<4:0>  | Cap bank offset value. It needs to change the CTUNE value after cut-off frequency auto tuning.  |

|              |       |                | See CTUNE<4:0> description (0×0f address).                                                      |

| OTES         | 1     | 1              |                                                                                                 |

NOTES

## Table 12. VCO/PLL Register Setting

| Reg.<br>Addr<br>(Hex) | Bit(s) | Name           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

|-----------------------|--------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 19                    | <3:0>  | PLLR<3:0>      | PLL reference divider: Fref (Reference frequency) = Fck (Reference clock) $\div$ PLLR (Reference divider). <3:0> = 0×1: Default value.                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| а                     | <7:2>  | ICP<5:0>       | Charge pump current control.<br>Current = {ICP (decimal) + 1} × 10 $\mu$ A                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| a                     | <1:0>  | PLLN<9:8>      | PLLN is integral part of feedback divider. PLLF is fractional part of feedback divider.                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| b                     | <7:0>  | PLLN<7:0>      | LO frequency = {Clock frequency $\times$ (PLLN + PLLF $\div$ 2^20)} $\div$ PLLR                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

| lc                    | <6:4>  | DIVSEL<2:0>    | Divider value selection register.<br><2:0> = 0×0: Generate divider 32 value of VCO frequency. (LO output frequency: 58.75 ~ 117.5 MHz)<br><2:0> = 0×1: Generate divider 16 value of VCO frequency. (LO output frequency: 117.5 ~ 235 MHz)<br><2:0> = 0×2: Generate divide 8 value of VCO frequency. (LO output frequency: 235 ~ 470 MHz)<br><2:0> = 0×3: Generate divide 4 value of VCO frequency (LO output frequency: 470 ~ 940 MHz)<br><2:0> = 0×4: Generate divide 2 value of VCO frequency. (LO output frequency: 940 ~ 1880 MHz) |  |  |  |  |  |

| c                     | <7>    | VCOSEL<0>      | VCO selection register.<br>$<0> = 0\times0$ : Enable low band VCO. Low band VCO frequency range: 1880 ~ 2630 MHz.<br>$<0> = 0\times1$ : Enable high band VCO. High band VCO frequency: 2630 ~ 3760 MHz.                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| с                     | <3:0>  | PLLF<19:16>    | PLLF is fractional part of feedback divider.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

| d                     | <7:0>  | PLLF<15:8>     | LO frequency = {Clock frequency $\times$ (PLLN + PLLF $\div$ 2^20)} $\div$ PLLR                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

| e                     | <7:0>  | PLLF<7:0>      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

| ?f                    | <4:0>  | VCORG_I2C<4:0> | External registers setting for capacitor bank in VCO core.<br>Write mode: When EXTVCORG<0> is enable.<br><4:0> = 0×00: Mimimum oscillation frequency.<br><4:0> = 0×1f: Maximum oscillation frequency.                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

| f                     | <5>    | PC8_16<0>      | Prescaler divider ratio setting value:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| f                     | <6>    | PC4<0>         | PC4<0>       PC8_16<0>       Prescaler divider         0       0       8/9 ratio         0       1       16/17 ratio         1       0       4/5 ratio         1       1       4/5 ratio                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| 2f                    | <7>    | RST_PLL<0>     | PLL Reset.<br><0> = 0×1: Reset.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

| 39<br>NOTES           | <6>    | EXTVCORG<0>    | Manual control of VCO search loop.<br><0> = 0×1: When EXTVCORG<0> is enabled, VCORG_12C register operates.                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| Reg.<br>Addr |        |                 |                                                                                                                                                                                                                        |

|--------------|--------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|              | Bit(s) | Name            | Description                                                                                                                                                                                                            |

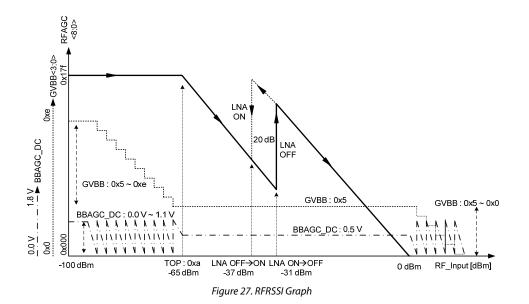

| 7            |        | TOP<3:0>        | TOP is RF gain control register. When close to 0×0, linearity is improved, but tuner output SNR and NF are degraded. When close to 0×b, linearity is degraded, but tuner output SNR and NF are improved. Step is 3 dB. |

|              |        |                 | $<3:0> = 0 \times 0:33 \text{ dB}$                                                                                                                                                                                     |

|              |        |                 | $<3:0> = 0 \times 1:30 \text{ dB}$                                                                                                                                                                                     |

|              |        |                 | $<3:0> = 0\times2:27 \text{ dB}$                                                                                                                                                                                       |

|              |        |                 | $<3:0> = 0\times3:24 \text{ dB}$                                                                                                                                                                                       |

|              |        |                 | $<3:0> = 0\times4:21 \text{ dB}$                                                                                                                                                                                       |

|              |        |                 | <3:0> = 0×5: 18 dB                                                                                                                                                                                                     |

|              |        |                 | <3:0> = 0×6: 15 dB                                                                                                                                                                                                     |

|              |        |                 | $<3:0> = 0\times7: 12 \text{ dB}$                                                                                                                                                                                      |

|              |        |                 | $<3:0> = 0 \times 8:9 \text{ dB}$                                                                                                                                                                                      |

|              |        |                 | $<3:0> = 0 \times 9:6 \text{ dB}$                                                                                                                                                                                      |

|              |        |                 | $<3:0> = 0 \times a: 3 dB$                                                                                                                                                                                             |

|              |        |                 | $<3:0> = 0 \times b: 0  dB$                                                                                                                                                                                            |

| 7            | <6:4>  | ADJ<2:0>        | ADJ is gain control register of adjacent channel power detector. Gain step is 3 dB.                                                                                                                                    |

|              |        |                 | $<2:0> = 0 \times 0:6 \text{ dB}$                                                                                                                                                                                      |

|              |        |                 | $<2:0> = 0 \times 1:3 \text{ dB}$                                                                                                                                                                                      |

|              |        |                 | $<2:0> = 0\times2:0 \text{ dB}$                                                                                                                                                                                        |

|              |        |                 | $<2:0> = 0\times3: -3 \text{ dB}$                                                                                                                                                                                      |

|              |        |                 | $<2:0> = 0\times4:-6$ dB                                                                                                                                                                                               |

|              |        |                 | $<2:0> = 0\times5: -9 \text{ dB}$                                                                                                                                                                                      |

|              |        |                 | $<2:0> = 0\times6: -2 \text{ dB}$                                                                                                                                                                                      |

|              |        |                 | <2:0> = 0×7: -5 dB                                                                                                                                                                                                     |

| 1            | <2:0>  | DIVAGOCK<2:0>   | DIVAGOCK is digital gain switching speed of BBPGA. Fck is a reference clock.                                                                                                                                           |

|              |        |                 | Baseband digital gain switching speed = Fck/2^(DIVAGOCK+8)                                                                                                                                                             |

| 7            | <0>    | EXTGVBB<0>      | Enternal GVBB setting when EXTGVBB is 0x1.                                                                                                                                                                             |

|              |        |                 | $\langle 0 \rangle = 0 \times 0$ : Disable.                                                                                                                                                                            |

|              |        |                 | <0> = 0×1: Enable.                                                                                                                                                                                                     |

| 7            | <7:6>  | LNAGAINI2C<1:0> | LNA Gain mode manual setting when TOP is 0×f.                                                                                                                                                                          |

|              |        |                 | If UHF mode,<br>$<1:0> = 0\times0:$ Low gain.                                                                                                                                                                          |

|              |        |                 | $<1:0> = 0\times3:$ High gain.                                                                                                                                                                                         |

|              |        |                 | If VHF mode,                                                                                                                                                                                                           |

|              |        |                 | <1:0> = 0×0: Low gain.                                                                                                                                                                                                 |

|              |        |                 | $<1:0> = 0 \times 1, 0 \times 2, 0 \times 3$ : High gain.                                                                                                                                                              |

| 8            | <7:4>  | GVBBI2C<3:0>    | GVBBI2C is external baseabnd PGA gain control when EXTGVBB< $0 > = 0 \times 1$ .                                                                                                                                       |

|              |        |                 | $\langle 3:0 \rangle = 0 \times 00$ : Minimum gain.                                                                                                                                                                    |

|              |        |                 | <3:0> = 0×0e: Maximum gain.                                                                                                                                                                                            |

| 1            | <0>    | RFAGCI2C<8>     | RFAGC manual gain setting when TOP = $0 \times f$ .                                                                                                                                                                    |

| 1            | <7:0>  | RFAGCI2C<7:0>   |                                                                                                                                                                                                                        |

| 3            |        | RFAGCMIN<7:0>   | RFAGC minimum limit value.                                                                                                                                                                                             |

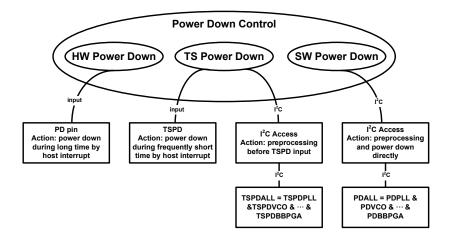

| 1            | <1>    | RFAGCMIN<8>     | 1                                                                                                                                                                                                                      |