# Low Noise, Matched Dual Monolithic Transistor

**MAT02**

**FEATURES**

Low Offset Voltage: 50 µV max

Low Noise Voltage at 100 Hz, 1 mA: 1.0 nV/√Hz max

High Gain (h<sub>FE</sub>):

500 min at  $I_C = 1$  mA 300 min at  $I_C = 1$   $\mu$ A

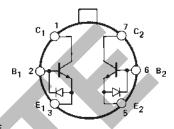

Excellent Log Conformance:  $r_{BE} \simeq 0.3~\Omega$ Low Offset Voltage Drift: 0.1  $\mu$ V/°C max Improved Direct Replacement for LM194/394 PIN CONNECTION

TO-78 (H Suffix)

Substrate is connected to case on TO-78 package. Substrate is normally connected to the most negative circuit potential, but can be floated.

#### PRODUCT DESCRIPTION

The design of the MAT02 series of NPN dual monolithic transistors is optimized for very low noise, low drift and low  $r_{BE}$ . Precision Monolithics' exclusive Silicon Nitride "Triple-Passivation" process stabilizes the critical device parameters over wide ranges of temperature and elapsed time. Also, the high current gain ( $h_{FE}$ ) of the MAT02 is maintained over a wide range of collector current. Exceptional characteristics of the MAT02 include offset voltage of 50  $\mu V$  max (A/E grades) and 150  $\mu V$  max F grade. Device performance is specified over the full military temperature range as well as at 25°C.

Input protection diodes are provided across the emitter-base junctions to prevent degradation of the device characteristics due to reverse-biased emitter current. The substrate is clamped to the most negative emitter by the parasitic isolation junction created by the protection diodes. This results in complete isolation between the transistors.

The MAT02 should be used in any application where low noise is a priority. The MAT02 can be used as an input stage to make an amplifier with noise voltage of less than 1.0 nV/ $\sqrt{\text{Hz}}$  at 100 Hz. Other applications, such as log/antilog circuits, may use the excellent logging conformity of the MAT02. Typical bulk resistance is only 0.3  $\Omega$  to 0.4  $\Omega$ . The MAT02 electrical characteristics approach those of an ideal transistor when operated over a collector current range of 1  $\mu$ A to 10 mA. For applications requiring multiple devices see MAT04 Quad Matched Transistor data sheet.

REV. E

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 www.analog.com

Fax: 781/326-8703 © Analog Devices, Inc., 2002

# MATO2-SPECIFICATIONS

# **ELECTRICAL CHARACTERISTICS** (@ $V_{CB} = 15$ V, $I_C = 10$ $\mu A$ , $T_A = 25^{\circ}C$ , unless otherwise noted.)

|                            |                               |                                                         | MAT02E |      | MAT02F |     |      |     |                |

|----------------------------|-------------------------------|---------------------------------------------------------|--------|------|--------|-----|------|-----|----------------|

| Parameter                  | Symbol                        | Conditions                                              | Min    | Typ  | Max    | Min | Typ  | Max | Unit           |

| Current Gain               | $h_{\mathrm{FE}}$             | $I_C = 1 \text{ mA}^1$                                  | 500    | 605  |        | 400 | 605  |     |                |

|                            | 12                            | $I_{\rm C} = 100  \mu A$                                | 500    | 590  |        | 400 | 590  |     |                |

|                            |                               | $I_C = 10 \mu\text{A}$                                  | 400    | 550  |        | 300 | 550  |     |                |

|                            |                               | $I_C = 1 \mu A$                                         | 300    | 485  |        | 200 | 485  |     |                |

| Current Gain Match         | $\Delta h_{\mathrm{FE}}$      | $10 \mu\text{A} \leq I_{\text{C}} \leq 1 \text{mA}^2$   |        | 0.5  | 2      |     | 0.5  | 4   | %              |

| Offset Voltage             | Vos                           | $V_{CB} = 0, 1 \mu A \le I_C \le 1 \text{ mA}^3$        |        | 10   | 50     |     | 80   | 150 | μV             |

| Offset Voltage             | $\Delta V_{OS}/\Delta V_{CB}$ | $0 \le V_{CB} \le V_{MAX}^4$                            |        | 10   | 25     |     | 10   | 50  | μV             |

| Change vs. V <sub>CB</sub> |                               | $1 \mu A \le I_C \le 1 mA^3$                            |        | 10   | 25     |     | 10   | 50  | μV             |

| Offset Voltage Change      | $\Delta V_{OS}/\Delta I_{C}$  | $V_{CB} = 0 V$                                          |        | 5    | 25     |     | 5    | 50  | μV             |

| vs. Collector Current      |                               | $1 \mu A \le I_C \le 1 mA^3$                            |        | 5    | 25     |     | 5    | 50  | μV             |

| Offset Current             |                               |                                                         |        |      |        |     |      |     |                |

| Change vs. V <sub>CB</sub> | $\Delta I_{OS}/\Delta V_{CB}$ | $0 \le V_{CB} \le V_{MAX}$                              |        | 30   | 70     |     | 30   | 70  | pA/V           |

| Bulk Resistance            | $r_{ m BE}$                   | $10 \ \mu A \le I_C \le 10 \ mA^5$                      |        | 0.3  | 0.5    |     | 0.3  | 0.5 | Ω              |

| Collector-Base             |                               |                                                         |        |      |        |     |      |     |                |

| Leakage Current            | $I_{CBO}$                     | $V_{CB} = V_{MAX}$                                      |        | 25   | 200    |     | 25   | 400 | pA             |

| Collector-Collector        |                               |                                                         |        | A `  |        |     |      |     |                |

| Leakage Current            | $I_{CC}$                      | $V_{CC} = V_{MAX}^{5, 6}$                               |        | 35   | 200    |     | 35   | 400 | pA             |

| Collector-Emitter          |                               | $V_{CE} = V_{MAX}^{5, 6}$                               |        |      |        |     |      |     |                |

| Leakage Current            | $I_{CES}$                     | $V_{BE} = 0$                                            |        | 35   | 200    |     | 35   | 400 | pA             |

| Noise Voltage Density      | e <sub>n</sub>                | $I_C = 1 \text{ mA}, V_{CB} = 0^7$                      |        |      |        |     |      |     |                |

|                            |                               | $f_O = 10 \text{ Hz}$                                   |        | 1.6  | 2      |     | 1.6  | 3   | $nV/\sqrt{Hz}$ |

|                            |                               | $f_O = 100 \text{ Hz}$                                  |        | 0.9  | 1      |     | 0.9  | 2   | $nV/\sqrt{Hz}$ |

|                            |                               | $f_O = 1 \text{ kHz}$                                   |        | 0.85 | 1      |     | 0.85 | 2   | $nV/\sqrt{Hz}$ |

|                            |                               | $f_O = 10 \text{ kHz}$                                  |        | 0.85 | 1      |     | 0.85 | 2   | $nV/\sqrt{Hz}$ |

| Collector Saturation       |                               |                                                         |        |      |        |     |      |     |                |

| Voltage                    | V <sub>CE(SAT)</sub>          | $I_{\rm C} = 1 \text{ mA}, I_{\rm B} = 100 \mu\text{A}$ |        | 0.05 | 0.1    |     | 0.05 | 0.2 | V              |

| Input Bias Current         | $I_{\mathrm{B}}$              | $I_C = 10 \mu A$                                        |        |      | 25     |     |      | 34  | nA             |

| Input Offset Current       | I <sub>OS</sub>               | $I_C = 10 \mu\text{A}$                                  |        |      | 0.6    |     |      | 1.3 | nA             |

| Breakdown Voltage          | $BV_{CEO}$                    |                                                         | 40     |      |        | 40  |      |     | V              |

| Gain-Bandwidth Product     | $f_{\rm T}$                   | $I_C = 10 \text{ mA}, V_{CE} = 10 \text{ V}$            |        | 200  |        |     | 200  |     | MHz            |

| Output Capacitance         | $C_{OB}$                      | $V_{CB} = 15 \text{ V}, I_{E} = 0$                      |        | 23   |        |     | 23   |     | pF             |

| Collector-Collector        |                               |                                                         |        | 2 =  |        |     | 2 =  |     |                |

| Capacitance                | C <sub>CC</sub>               | $V_{CC} = 0$                                            |        | 35   |        |     | 35   |     | pF             |

Specifications subject to change without notice.

-2-REV. E

$<sup>^{1}</sup>$ Current gain is guaranteed with Collector-Base Voltage ( $V_{CB}$ ) swept from 0 to  $V_{MAX}$  at the indicated collector currents.

$<sup>^2</sup>Current$  gain match ( $\Delta h_{FE}$ ) is defined as:  $\Delta h_{FE} = 100~(\Delta I_B)~(h_{FE}~min)$

$<sup>^3</sup>$ Measured at  $I_C$  = 10 μA and guaranteed by design over the specified range of  $I_C$ .  $^4$ This is the maximum change in  $V_{OS}$  as  $V_{CB}$  is swept from 0 V to 40 V.  $^6$ Guaranteed by design.

$<sup>^6\</sup>mathrm{I}_{\mathrm{CC}}$  and  $\mathrm{I}_{\mathrm{CES}}$  are verified by measurement of  $\mathrm{I}_{\mathrm{CBO}}$ .

<sup>&</sup>lt;sup>7</sup>Sample tested.

### **ELECTRICAL CHARACTERISTICS** ( $V_{CB} = 15 \text{ V}, -25^{\circ}\text{C} \le T_{A} \le +85^{\circ}\text{C}$ , unless otherwise noted.)

|                                      |                   |                                                                                                                                                             | MAT02E |              | MAT02F     |     |              |     |       |

|--------------------------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------------|------------|-----|--------------|-----|-------|

| Parameter                            | Symbol            | Conditions                                                                                                                                                  | Min    | Typ          | Max        | Min | Typ          | Max | Unit  |

| Offset Voltage                       | V <sub>OS</sub>   | $V_{CB} = 0$ $1 \mu A \le I_C \le 1 \text{ mA}^1$                                                                                                           |        |              | 70         |     |              | 220 | μV    |

| Average Offset                       |                   |                                                                                                                                                             |        |              |            |     |              |     |       |

| Voltage Drift                        | TCV <sub>OS</sub> | 10 $\mu$ A $\leq$ I <sub>C</sub> $\leq$ 1 mA, 0 $\leq$ V <sub>CB</sub> $\leq$ V <sub>MAX</sub> <sup>2</sup><br>V <sub>OS</sub> Trimmed to Zero <sup>3</sup> |        | 0.08<br>0.03 | 0.3<br>0.1 |     | 0.08<br>0.03 |     | μV/°C |

| Input Offset Current<br>Input Offset | I <sub>OS</sub>   | $I_C = 10 \mu A$                                                                                                                                            |        |              | 8          |     |              | 13  | nA    |

| Current Drift                        | TCI <sub>OS</sub> | $I_{\rm C} = 10  \mu A^4$                                                                                                                                   |        | 40           | 90         | •   | 40           | 150 | pA/°C |

| Input Bias Current                   | $I_{B}$           | $I_C = 10 \mu\text{A}$                                                                                                                                      |        |              | 45         |     |              | 50  | nA    |

| Current Gain                         | $h_{ m FE}$       | $I_C = 1 \text{ mA}^5$                                                                                                                                      | 325    |              |            | 300 |              |     |       |

|                                      |                   | $I_C = 100 \mu\text{A}$                                                                                                                                     | 275    |              |            | 250 |              |     |       |

|                                      |                   | $I_C = 10 \mu A$                                                                                                                                            | 225    |              |            | 200 |              |     |       |

|                                      |                   | $I_C = 1 \mu A$                                                                                                                                             | 200    |              |            | 150 |              |     |       |

| Collector-Base                       | $I_{CBO}$         | $V_{CB} = V_{MAX}$                                                                                                                                          |        | 2            |            |     | 3            |     | nA    |

| Leakage Current                      |                   |                                                                                                                                                             |        |              |            |     |              |     |       |

| Collector-Emitter                    | $I_{CES}$         | $V_{CE} = V_{MAX}, V_{BE} = 0$                                                                                                                              | 1      | 3            |            |     | 4            |     | nA    |

| Leakage Current                      |                   |                                                                                                                                                             |        |              |            |     |              |     |       |

| Collector-Collector Leakage Current  | $I_{CC}$          | $V_{CC} = V_{MAX}$                                                                                                                                          |        | 3            |            |     | 4            |     | nA    |

| Leakage Current                      |                   |                                                                                                                                                             |        |              |            |     |              |     |       |

#### NOTES

<sup>2</sup>Guaranteed by V<sub>OS</sub> test

$$(TCV_{OS} \cong \frac{V_{OS}}{T}$$

for  $V_{OS} \ll V_{BE})$   $T = 298K$  for T<sub>A</sub> = 25°C.

Specifications subject to change without notice.

#### ABSOLUTE MAXIMUM RATINGS<sup>1</sup>

| Collector-Base Voltage (BV <sub>CBO</sub> )                           |

|-----------------------------------------------------------------------|

| Collector-Emitter Voltage (BV <sub>CEO</sub> )                        |

| Collector-Collector Voltage (BV <sub>CC</sub> ) 40 V                  |

| Emitter-Emitter Voltage (BV <sub>EE</sub> )                           |

| Collector Current (I <sub>C</sub> ) 20 mA                             |

| Emitter Current (I <sub>E</sub> ) 20 mA                               |

| Total Power Dissipation                                               |

| Case Temperature $\leq 40^{\circ} \text{C}^2 \dots 1.8 \text{ W}$     |

| Ambient Temperature $\leq 70^{\circ} \text{C}^3 \dots 500 \text{ mW}$ |

| Operating Temperature Range                                           |

| MAT02E, F25°C to +85°C                                                |

| Operating Junction Temperature       | 55°C to +150°C  |

|--------------------------------------|-----------------|

| Storage Temperature                  | −65°C to +150°C |

| Lead Temperature (Soldering, 60 sec) | 300°C           |

| Junction Temperature                 | −65°C to +150°C |

#### NOTES

<sup>1</sup>Absolute maximum ratings apply to both DICE and packaged devices.

#### **ORDERING GUIDE**

| Model $V_{OS}$ max $(T_A = 25^{\circ}C)$ |        | Temperature<br>Range | Package<br>Option |  |  |

|------------------------------------------|--------|----------------------|-------------------|--|--|

| MAT02EH                                  | 50 μV  | -25°C to +85°C       | TO-78             |  |  |

| MAT02FH                                  | 150 μV | -25°C to +85°C       | TO-78             |  |  |

#### CAUTION\_

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although the MAT02 features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

$<sup>^{1}</sup>$ Measured at  $I_{C}$  = 10  $\mu$ A and guaranteed by design over the specified range of  $I_{C}$ .

$<sup>^3</sup>$ The initial zero offset voltage is established by adjusting the ratio of  $I_C 1$  to  $I_C 2$  at  $T_A = 25^{\circ}C$ . This ratio must be held to 0.003% over the entire temperature range. Measurements are taken at the temperature extremes and 25  $^{\circ}C$ .

<sup>&</sup>lt;sup>4</sup>Guaranteed by design.

<sup>&</sup>lt;sup>5</sup>Current gain is guaranteed with Collector-Base Voltage (V<sub>CB</sub>) swept from 0 V to V<sub>MAX</sub> at the indicated collector current.

<sup>&</sup>lt;sup>2</sup>Rating applies to applications using heat sinking to control case temperature. Derate linearly at 16.4 mW/°C for case temperature above 40°C.

<sup>&</sup>lt;sup>3</sup>Rating applies to applications not using a heat sinking; devices in free air only. Derate linearly at 6.3 mW/°C for ambient temperature above 70°C.

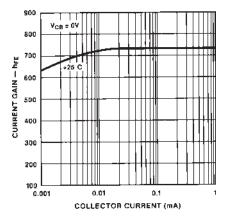

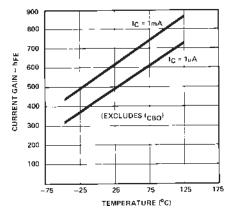

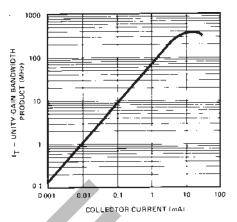

# **MAT02**—Typical Performance Characteristics

TPC 1. Current Gain vs. Collector Current

TPC 2. Current Gain vs. Temperature

TPC 3. Gain Bandwidth vs. Collector Current

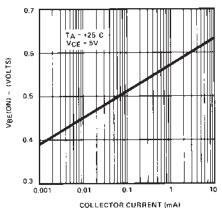

TPC 4. Base-Emitter-On Voltage vs. Collector Current

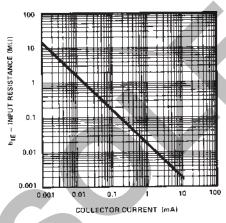

TPC 5. Small Signal Input Resistance vs. Collector Current

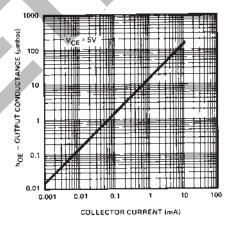

TPC 6. Small-Signal Output Conductance vs. Collector Current

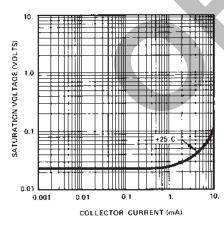

TPC 7. Saturation Voltage vs. Collector Current

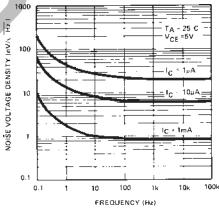

TPC 8. Noise Voltage Density vs. Frequency

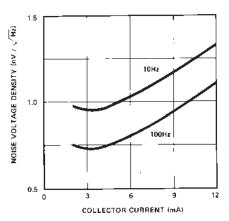

TPC 9. Noise Voltage Density vs. Collector Current

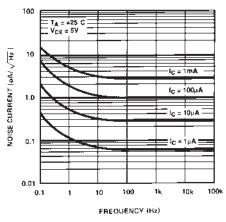

TPC 10. Noise Current Density vs. Frequency

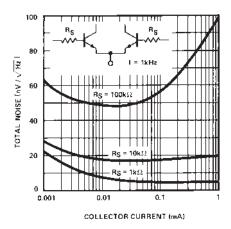

TPC 11. Total Noise vs. Collective Current

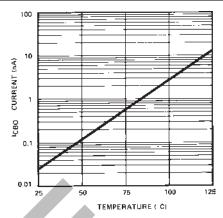

TPC 12. Collector-to-Base Leakage vs. Temperature

TPC 13. Collector-to-Collector Leakage vs. Temperature

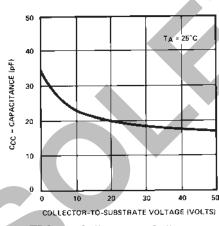

TPC 14. Collector-to-Collector Capacitance vs. Collector-to Substrate Voltage

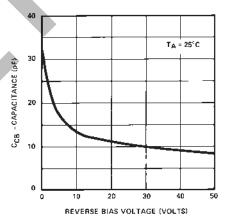

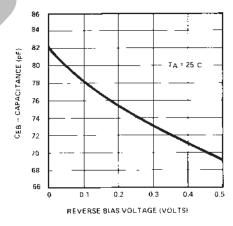

TPC 15. Collector-Base Capacitance vs. Reverse Bias Voltage

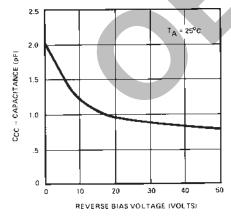

TPC 16. Collector-to-Collector Capacitance vs. Reverse Bias Voltage

TPC 17. Emitter-Base Capacitance vs. Reverse Bias Voltage

REV. E \_5\_

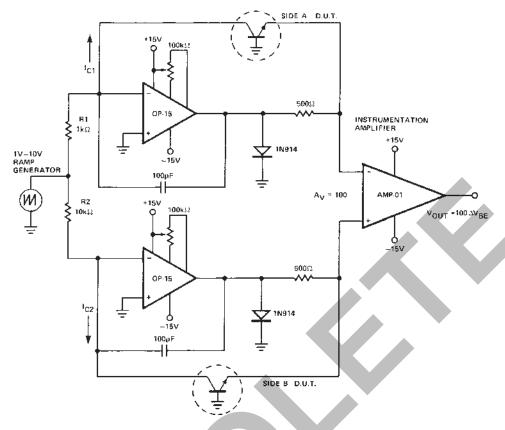

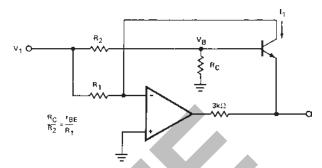

Figure 1. Log Conformance Test Circuit

#### LOG CONFORMANCE TESTING

The log conformance of the MAT02 is tested using the circuit shown above. The circuit employs a dual transdiode logarithmic converter operating at a fixed ratio of collector currents that are swept over a 10:1 range. The output of each transdiode converter is the  $V_{BE}$  of the transistor plus an error term which is the product of the collector current and  $r_{BE}$ , the bulk emitter resistance. The difference of the  $V_{BE}$  is amplified at a gain of  $\times 100$  by the AMP01 instrumentation amplifier. The differential emitter-base voltage  $(\Delta V_{BE})$  consists of a temperature-dependent dc level plus an ac error voltage, which is the deviation from true log conformity as the collector currents vary.

The output of the transdiode logarithmic converter comes from the idealized intrinsic transistor equation (for silicon):

$$V_{BE} = \frac{kT}{a} \ln \frac{I_C}{I_S} \tag{1}$$

where

$k = \text{Boltzmann's Constant} (1.38062 \times 10^{-23} \text{ J/K})$

$q = \text{Unit Electron Charge } (1.60219 \times 10^{-19} \, ^{\circ}\text{C})$

T =Absolute Temperature, K (=  $^{\circ}$ C + 273.2)

$I_S$  = Extrapolated Current for  $V_{BE} \rightarrow 0$

$I_C$  = Collector Current

An error term must be added to this equation to allow for the bulk resistance ( $r_{BE}$ ) of the transistor. Error due to the op amp input current is limited by use of the OP15 BiFET-input op amp. The resulting AMP01 input is:

$$\Delta V_{BE} = \frac{kT}{q} \ln \frac{I_{C1}}{I_{C2}} + I_{C1} r_{BE1} - I_{C2} r_{BE2}$$

(2)

A ramp function that sweeps from 1 V to 10 V is converted by the op amps to a collector current ramp through each transistor. Because  $I_{C1}$  is made equal to 10  $I_{C2}$ , and assuming  $T_A = 25$ °C, the previous equation becomes:

$$\Delta V_{BE} = 59 \ mV + 0.9 \ I_{C1} \ r_{BE} \ (\Delta r_{BE} \sim 0)$$

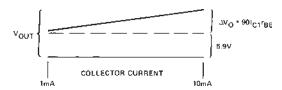

As viewed on an oscilloscope, the change in  $\Delta V_{BE}$  for a 10:1 change in  $I_C$  is then displayed as shown in Figure 2 below:

Figure 2.

With the oscilloscope ac coupled, the temperature dependent term becomes a dc offset and the trace represents the deviation from true log conformity. The bulk resistance can be calculated from the voltage deviation  $\Delta V_{\rm O}$  and the change in collector current (9 mA):

$$r_{BE} = \frac{\Delta V_O}{9\,\text{mA}} \times \frac{1}{100} \tag{3}$$

This procedure finds  $r_{BE}$  for Side A. Switching  $R_1$  and  $R_2$  will provide the  $r_{BE}$  for Side B. Differential  $r_{BE}$  is found by making  $R_1 = R_2$ .

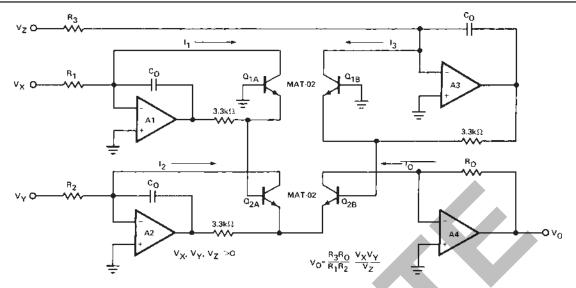

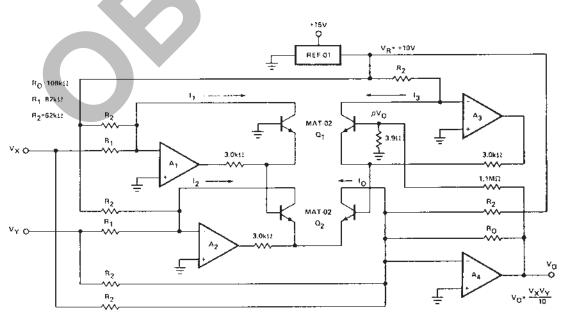

Figure 3. One-Quadrant Multiplier/Divider

# APPLICATIONS: NONLINEAR FUNCTIONS MULTIPLIER/DIVIDER CIRCUIT

The excellent log conformity of the MAT02 over a very wide range of collector current makes it ideal for use in log-antilog circuits. Such nonlinear functions as multiplying, dividing, squaring and square-rooting are accurately and easily implemented with a log antilog circuit using two MAT02 pairs (see Figure 3). The transistor circuit accepts three input currents ( $I_1$ ,  $I_2$  and  $I_3$ ) and provides an output current  $I_0$  according to  $I_0 = I_1I_2/I_3$ . All four currents must be positive in the log antilog circuit, but negative input voltages can be easily accommodated by various offsetting techniques. Protective diodes across each base-to-emitter junction would normally be needed, but these diodes are built into the MAT02. External protection diodes are, therefore, not needed.

For the circuit shown in Figure 3, the operational amplifiers make  $I_1 = V_X/R_1$ ,  $I_2 = V_Y/R_2$ ,  $I_3 = V_Z/R_3$ , and  $I_O = V_O/R_O$ . The output voltage for this one-quadrant, log-antilog multiplier/divider is ideally:

$$V_{O} = \frac{R_{3}R_{O}}{R_{1}R_{2}} \frac{V_{X}V_{Y}}{V_{Z}} (V_{X}, V_{Y}, V_{Z} > 0)$$

(4)

If all the resistors  $(R_0, R_1, R_2, R_3)$  are made equal, then

$$V_O = V_X V_Y / V_Z$$

Resistor values of 50 k $\Omega$  to 100 k $\Omega$  are recommended assuming an input range of 0.1 V to +10 V.

#### **ERROR ANALYSIS**

The base-to-emitter voltage of the MAT02 in its forward active operation is:

$$V_{BE} = \frac{kT}{a} In \frac{I_C}{I_S} + r_{BE} I_C, \ V_{CB} \sim 0$$

(5)

The first term comes from the idealized intrinsic transistor equation previously discussed (see equation (1)).

Extrinsic resistive terms and the early effect cause departure from the ideal logarithmic relationship. For small  $V_{CB}$ , all of

these effects can be lumped together as a total effective bulk resistance  $r_{BE}.$  The  $r_{BE}I_{C}$  term causes departure from the desired logarithmic relationship. The  $r_{BE}$  term for the MAT02 is less than 0.5  $\Omega$  and  $\Delta r_{BE}$  between the two sides is negligible.

Returning to the multiplier/divider circuit of Figure 1 and using Equation (4):

$$V_{BE1A} + V_{BE2A} - V_{BE2B} - V_{BE1B} + (I_1 + I_2 - I_0 - I_3) r_{BE} = 0$$

If the transistor pairs are held to the same temperature, then:

$$\frac{kT}{q} In \frac{I_1 I_2}{I_3 I_O} = \frac{kT}{q} In \frac{I_{S1A} I_{S2A}}{I_{S1B} I_{S2B}} + (I_1 + I_2 - I_O - I_3) r_{BE}$$

(6)

If all the terms on the right-hand side were zero, then In  $(I_1 \ I_2/I_3 \ I_O)$  would equal zero, which would lead directly to the desired result:

$$I_O = \frac{I_1 I_2}{I_3}$$

, where  $I_1$ ,  $I_2$ ,  $I_3$ ,  $I_O > 0$  (7)

Note that this relationship is temperature independent. The right-hand side of Equation (6) is near zero and the output current  $I_O$  will be approximately  $I_1$   $I_2/I_3$ . To estimate error, define  $\emptyset$  as the right-hand side terms of Equation (6):

$$\emptyset = In \frac{I_{S1A}I_{S2A}}{I_{S1B}I_{S2B}} + \frac{q}{kT} (I_1 + I_2 - I_O - I_3) r_{BE}$$

(8)

For the MAT02, In  $(I_{SA}/I_{SB})$  and  $I_Cr_{BE}$  are very small. For small ø,  $\epsilon^0\sim 1$  + ø and therefore:

$$\frac{I_1 I_2}{I_3 I_O} = 1 + \emptyset \tag{9}$$

$$I_O \sim \frac{I_1 I_2}{I_3} \ (1 - \emptyset)$$

The In  $(I_{SA}/I_{SB})$  terms in ø cause a fixed gain error of less than  $\pm 0.6\%$  from each pair when using the MAT02, and this gain error is easily trimmed out by varying  $R_O$ . The  $I_{OUT}$  terms are

more troublesome because they vary with signal levels and are multiplied by absolute temperature. At 25°C, kT/q is approximately 26 mV and the error due to an  $r_{BE}I_{C}$  term will be  $r_{BE}I_{C}/26$  mV. Using an  $r_{BE}$  of 0.4  $\Omega$  for the MAT02 and assuming a collector current range of up to 200  $\mu A$ , then a peak error of 0.3% could be expected for an  $r_{BE}I_{C}$  error term when using the MAT02. Total error is dependent on the specific application configuration (multiply, divide, square, etc.) and the required dynamic range. An obvious way to reduce  $I_{C}r_{BE}$  error is to reduce the maximum collector current, but then op amp offsets and leakage currents become a limiting factor at low input levels. A design range of no greater than 10  $\mu A$  to 1 mA is generally recommended for most nonlinear function circuits.

A powerful technique for reducing error due to  $I_{C}r_{BE}$  is shown in Figure 4. A small voltage equal to  $I_{C}r_{BE}$  is applied to the transistor base. For this circuit:

$$V_B = \frac{R_C}{R_2} V_1 \text{ and } I_C r_{BE} = \frac{r_{BE}}{R_1} V_1$$

(10)

The error from  $r_{BE}I_C$  is cancelled if  $R_C/R_2$  is made equal to  $r_{OUT}$   $R_I$ . Since the MAT02 bulk resistance is approximately 0.39  $\Omega$ , an  $R_C$  of 3.9  $\Omega$  and  $R_2$  of 10  $R_1$  will give good error cancellation.

In more complex circuits, such as the circuit in Figure 3, it may be inconvenient to apply a compensation voltage to each individual base. A better approach is to sum all compensation to the bases of Q1. The "A" side needs a base voltage of  $(V_{\rm O}/R_{\rm O} + V_{\rm Z}/R_{\rm 3})$   $r_{\rm BE}$ , and the "B" side needs a base voltage of  $(V_{\rm X}/R_{\rm 1}+V_{\rm Y}/R_{\rm 2})$   $r_{\rm BE}$ . Linearity of better than  $\pm 0.1\%$  is readily achievable with this compensation technique.

Operational amplifier offsets are another source of error. In Figure 4, the input offset voltage and input bias current will cause an error in collector current of  $(V_{OS}/R_1) + I_B$ . A low offset op amp, such as the OP07 with less than 75  $\mu V$  of  $V_{OS}$  and  $I_B$  of less than  $\pm 3$  nA, is recommended. The OP193, micropower op amp, should be considered if low power con-

sumption or single-supply operation is needed. The value of frequency-compensating capacitor ( $C_0$ ) is dependent on the op amp frequency response and peak collector current. Typical values for  $C_0$  range from 30 pF to 300 pF.

Figure 4. Compensation of Bulk Resistance Error

#### FOUR-QUADRANT MULTIPLIER

A simplified schematic for a four-quadrant log-antilog multiplier is shown in Figure 5. Similar to the previously discussed one-quadrant multiplier, the circuit makes  $I_0 = I_1 \ I_2/I_3$ . The two input currents,  $I_1$  and  $I_2$ , are each offset in the positive direction. This positive offset is then subtracted out at the output stage. Assuming ideal op amps, the currents are:

$$I_{1} = \frac{V_{X}}{R_{1}} + \frac{V_{R}}{R_{2}}, I_{2} = \frac{V_{Y}}{R_{1}} + \frac{V_{R}}{R_{2}}$$

$$V_{Y} = V_{Y} - V_{D} - V_{D} - V_{D}$$

(11)

$$I_O = \frac{V_X}{R_1} + \frac{V_Y}{R_1} + \frac{V_R}{R_2} + \frac{V_O}{R_O}, I_3 = \frac{V_R}{R_2}$$

From  $I_O = I_1 I_2/I_3$ , the output voltage will be:

$$V_{O} = \frac{R_{O}R_{2}}{R_{1}^{2}} \frac{V_{X}V_{Y}}{V_{R}}$$

(12)

Figure 5. Four-Quadrant Multiplier

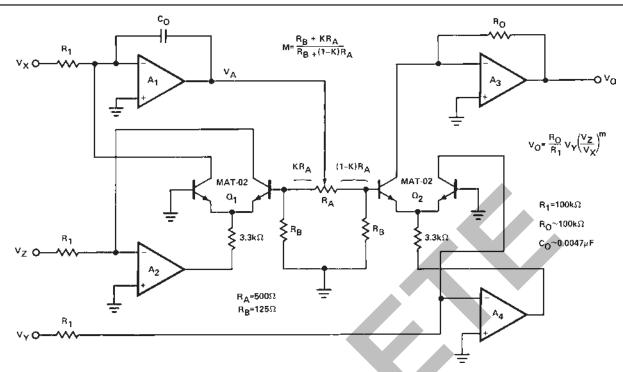

Figure 6. Multifunction Converter

-9-

Collector current range is the key design decision. The inherently low  $r_{BE}$  of the MAT02 allows the use of a relatively high collector current. For input scaling of  $\pm 10$  V full-scale and using a 10 V reference, we have a collector-current range for  $I_1$  and  $I_2$  of:

$$\left(\frac{-10}{R_1} + \frac{10}{R_2}\right) \le I_C \le \left(\frac{10}{R_1} + \frac{10}{R_2}\right) \tag{13}$$

Practical values for  $R_1$  and  $R_2$  would range from 50  $k\Omega$  to 100  $k\Omega.$  Choosing an  $R_1$  of 82  $k\Omega$  and  $R_2$  of 62  $k\Omega$  provides a collector current range of approximately 39  $\mu A$  to 283  $\mu A.$  An  $R_O$  of 108  $k\Omega$  will then make the output scale factor 1/10 and  $V_O=V_XV_Y/10.$  The output, as well as both inputs, are scaled for  $\pm 10$  V full scale.

Linear error for this circuit is substantially improved by the small correction voltage applied to the base of Q1 as shown in Figure 5. Assuming an equal bulk emitter resistance for each MAT02 transistor, then the error is nulled if:

$$(I_1 + I_2 - I_3 - I_O) r_{BE} + \rho V_O = 0$$

The currents are known from the previous discussion, and the relationship needed is simply:

$$V_O = \frac{r_{BE}}{R_O} \ V_O \tag{14}$$

The output voltage is attenuated by a factor of  $r_{BE}/R_O$  and applied to the base of Q1 to cancel the summation of voltage drops due to  $r_{BE}I_C$  terms. This will make In  $(I_1\ I_2/I_3\ I_O)$  more nearly zero which will thereby make  $I_O=I_1\ I_2/I_3$  a more accurate relationship. Linearity of better than 0.1% is readily achievable with this circuit if the MAT02 pairs are carefully kept at the same temperature.

#### **MULTIFUNCTION CONVERTER**

The multifunction converter circuit provides an accurate means of squaring, square rooting, and raising ratios to arbitrary powers. The excellent log conformity of the MAT02 allows a wide range of exponents. The general transfer function is:

$$V_O = V_Y \left(\frac{V_Z}{V_X}\right)^m \tag{15}$$

$V_{\rm X}, V_{\rm Y}$ , and  $V_{\rm Z}$  are input voltages and the exponent "m" has a practical range of approximately 0.2 to 5. Inputs  $V_{\rm X}$  and  $V_{\rm Y}$  are often taken from a fixed reference voltage. With a REF01 providing a precision 10 V to both  $V_{\rm X}$  and  $V_{\rm Y}$ , the transfer function would simplify to:

$$V_O = 10 \left(\frac{V_Z}{10}\right)^m \tag{16}$$

As with the multiplier/divider circuits, assume that the transistor pairs have excellent matching and are at the same temperature. The In  $I_{SA}/I_{SB}$  will then be zero. In the circuit of Figure 6, the voltage drops across the base-emitter junctions of Q1 provide:

$$\frac{R_B}{R_B + KR_A} V_A = \frac{kT}{q} \ln \frac{I_Z}{I_X}$$

(17)

$I_Z$  is  $V_Z/R_1$  and  $I_X$  is  $V_X/R_1$ . Similarly, the relationship for Q2 is:

$$\frac{R_B}{R_B + (1 - K)R_A} V_A = \frac{kT}{q} \ln \frac{I_O}{I_Y}$$

(18)

$I_O$  is  $V_O/R_O$  and  $I_Y$  is  $V_Y/R_1$ . These equations for Q1 and Q2 can then be combined.

$$\frac{R_B + KR_A}{R_B + (1 - K)R_A} \ln \frac{I_Z}{I_X} = \ln \frac{I_O}{I_Y}$$

(19)

REV. E

Substituting in the voltage relationships and simplifying leads to:

$$V_O = \frac{R_O}{R_1} V_Y \left(\frac{V_Z}{V_X}\right)^m, \text{ where}$$

$$m = \frac{R_B + KR_A}{R_B + (1 - K)R_A}$$

(20)

The factor "K" is a potentiometer position and varies from zero to 1.0, so "m" ranges from  $R_B/(R_A+R_B)$  to  $(R_B+R_A)/R_B$ . Practical values are 125  $\Omega$  for  $R_B$  and 500  $\Omega$  for  $R_A$ ; these values will provide an adjustment range of 0.2 to 5.0. A value of 100 k $\Omega$  is recommended for the  $R_1$  resistors assuming a full-scale input range of 10 V. As with the one-quadrant multiplier/divider circuit previously discussed, the  $V_X$ ,  $V_Y$ , and  $V_Z$  inputs must all be positive.

The op amps should have the lowest possible input offsets. The OP07 is recommended for most applications, although such programmable micropower op amps as the OP193/OP293 offer advantages in low-power or single-supply circuits. The micropower op amps also have very low input bias-current drift, an important advantage in log/antilog circuits. External offset nulling may be needed, particularly for applications requiring a wide dynamic range. Frequency compensating capacitors, on the order of 50 pF, may be required for  $A_2$  and  $A_3$ . Amplifier  $A_1$  is likely to need a larger capacitor, typically  $0.0047\,\mu\text{F}$ , to assure stability.

Accuracy is limited at the higher input levels by bulk emitter resistance, but this is much lower for the MAT02 than for other transistor pairs. Accuracy at the lower signal levels primarily depends on the op amp offsets. Accuracies of better than 1% are readily achievable with this circuit configuration and can be better than  $\pm 0.1\%$  over a limited operating range.

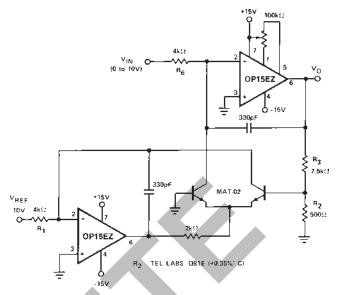

#### **FAST LOGARITHMIC AMPLIFIER**

The circuit of Figure 7 is a modification of a standard logarithmic amplifier configuration. Running the MAT02 at 2.5 mA per side (full-scale) allows a fast response with wide dynamic range. The circuit has a 7 decade current range, a 5 decade voltage range, and is capable of 2.5  $\mu s$  settling time to 1% with a 1 V to 10 V step.

The output follows the equation:

$$V_{O} = \frac{R_{3} + R_{2}}{R_{2}} \frac{kT}{q} In \frac{V_{REF}}{V_{IN}}$$

(21)

The output is inverted with respect to the input, and is nominally –1 V/decade using the component values indicated.

Figure 7. Fast Logarithmic Amplifier

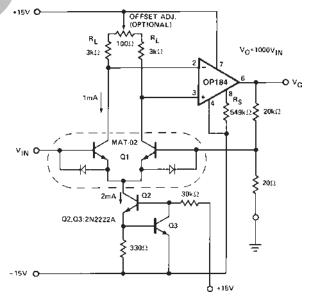

#### **LOW-NOISE** ×1000 AMPLIFIER

The MAT02 noise voltage is exceptionally low, only 1 nV/ $\overline{\text{Hz}}$  at 10 Hz when operated over a collector current range of 1 mA to 4 mA. A single-ended ×1000 amplifier that takes advantage of this low MAT02 noise level is shown in Figure 8. In addition to low noise, the amplifier has very low drift and high CMRR. An OP184 is used for the second stage to obtain good speed with minimal power consumption. Small-signal bandwidth is 4.0 MHz, slew rate is 2.4 V/ $\mu$ s, and total supply current is approximately 2.25 mA.

Figure 8. Low-Noise, Single-Ended × 1000 Amplifier

Transistors Q2 and Q3 form a 2 mA current source (0.65 V/330  $\Omega \sim 2$  mA). Each collector of Q1 operates at 1 mA. The OP184 inputs are 3 V below the positive supply voltage ( $R_L I_C \sim 3$  V). Input stage gain is  $g_m R_L$ , which is approximately 100 when operating at  $I_C$  of 1 mA with  $R_L$  of 3 k $\Omega$ . Since the OP184 has a minimum open-loop gain of 500,000, total open-loop gain for the composite amplifier is over 50 million. Even at closed-loop gain of 1000, the gain error due to finite open-loop gain will be negligible. The OP184 features excellent symmetry of slew-rate and very linear gain. Signal distortion is minimal.

Dynamic range of this amplifier is excellent; the OP184 has an output voltage swing of  $\pm 14.8$  V with a  $\pm 15$  V supply.

Input characteristics are outstanding. The MAT02F has offset voltage of less than 150  $\mu V$  at 25°C and a maximum offset drift of 1  $\mu V/^{\circ}C$ . Nulling the offset will further reduce offset drift. This can be accomplished by slightly unbalancing the collector load resistors. This adjustment will reduce the drift to less than 0.1  $\mu V/^{\circ}C$ .

Input bias current is relatively low due to the high current gain of the MAT02. The minimum  $\beta$  of 400 at 1 mA for the MAT02F implies an input bias current of approximately 2.5  $\mu A$ . This circuit should be used with signals having relatively low source impedance. A high source impedance will degrade offset and noise performance.

This circuit configuration provides exceptionally low input noise voltage and low drift. Noise can be reduced even further by raising the collector currents from 1 mA to 3 mA, but power consumption is then increased.

REV. E -11-

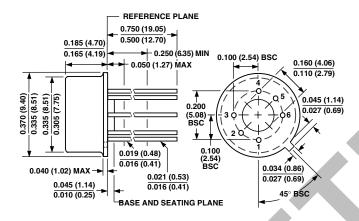

#### **OUTLINE DIMENSION**

Dimensions shown in inches and (mm).

#### 6-Lead Metal Can (TO-78)

# **Revision History**

| Location                                       |      | Page |

|------------------------------------------------|------|------|

| 4/02—Data Sheet changed from REV. D to REV. E. |      |      |

| Changes to ORDERING GUIDE                      | <br> |      |

| 1/02—Data Sheet changed from REV. C to REV. D. |      |      |

| Edits to FEATURES                              | <br> |      |

| Edits to ABSOLUTE MAXIMUM RATINGS              |      |      |

| Edits to ORDERING GUIDE                        |      |      |

| Deleted ELECTRICAL CHARACTERISTICS             | <br> |      |

| Deleted WAFER TEST LIMITS                      | <br> |      |

| Deleted TYPICAL ELECTRICAL CHARACTERISTICS     |      |      |

| Deleted DICE CHARACTERISTICS                   | <br> |      |

| Edits to ABSOLUTE MAXIMUM RATINGS              |      |      |

| Edits to text                                  | <br> |      |

| Updated Figures                                | <br> |      |