The following document contains information on Cypress products. The document has the series name, product name, and ordering part numbering with the prefix "MB". However, Cypress will offer these products to new and existing customers with the series name, product name, and ordering part number with the prefix "CY".

### **How to Check the Ordering Part Number**

- 1. Go to <a href="https://www.cypress.com/pcn">www.cypress.com/pcn</a>.

- 2. Enter the keyword (for example, ordering part number) in the **SEARCH PCNS** field and click **Apply**.

- 3. Click the corresponding title from the search results.

- 4. Download the Affected Parts List file, which has details of all changes

#### For More Information

Please contact your local sales office for additional information about Cypress products and solutions.

#### **About Cypress**

Cypress is the leader in advanced embedded system solutions for the world's most innovative automotive, industrial, smart home appliances, consumer electronics and medical products. Cypress' microcontrollers, analog ICs, wireless and USB-based connectivity solutions and reliable, high-performance memories help engineers design differentiated products and get them to market first. Cypress is committed to providing customers with the best support and development resources on the planet enabling them to disrupt markets by creating new product categories in record time. To learn more, go to www.cypress.com.

# 2ch Buck DC/DC Converter + 1ch LDO with I2C Interface and SW FET

#### **Description**

The MB39C031 contains 2ch buck DC/DC converter and 1ch LDO. It is possible to supply the main power supply line in a system by using only one chip. The current mode system is adopted for the DC/DC converter, and it is possible to use the chip inductor with the high switching frequency operation which contains internal SW FET. The MB39C031 contains the output setting resistor and the phase compensation circuit, and contributes to reduce the number of external components and the mounting area. Also, it contains the CTL input pin which can control the ON/OFF for each CH, the Power Good signal output pin and the I<sup>2</sup>C communication interface, therefore it is easy to design the power supply sequence.

It is possible to tune in the output voltage exactly using the I<sup>2</sup>C communication and possible to correspond to the DVS/ASV system.

#### **Features**

- Operating input voltage range:2.5 V to 5.5 V (Maximum rating: 7 V)

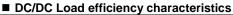

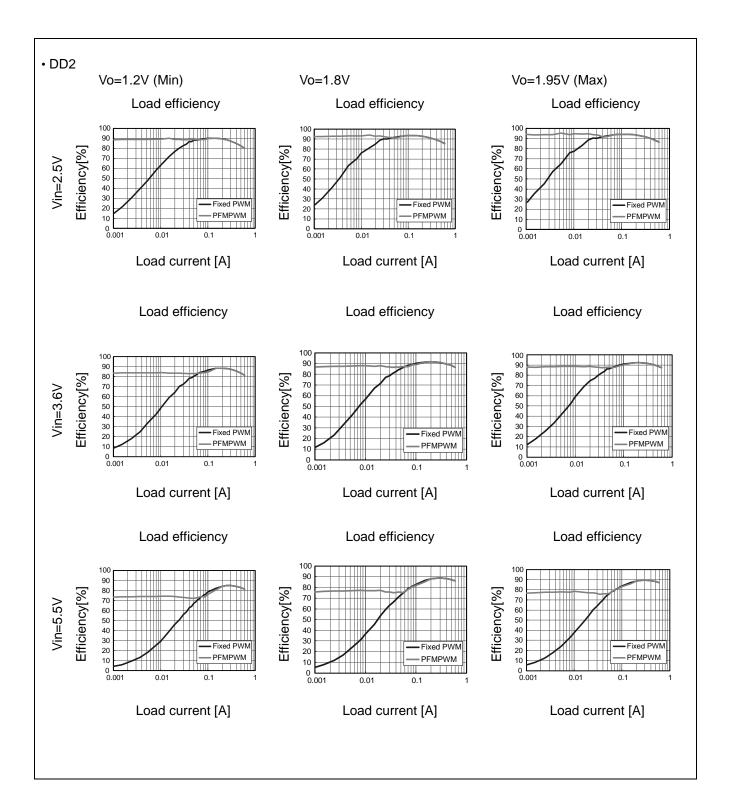

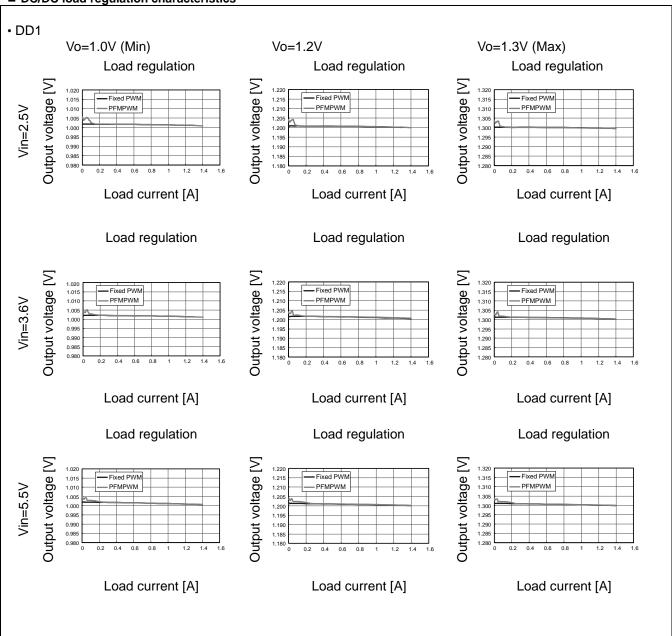

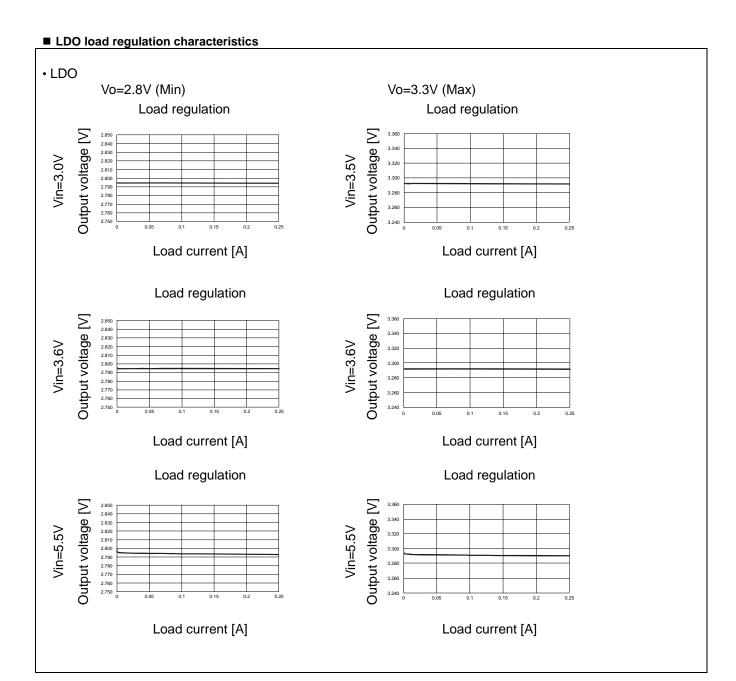

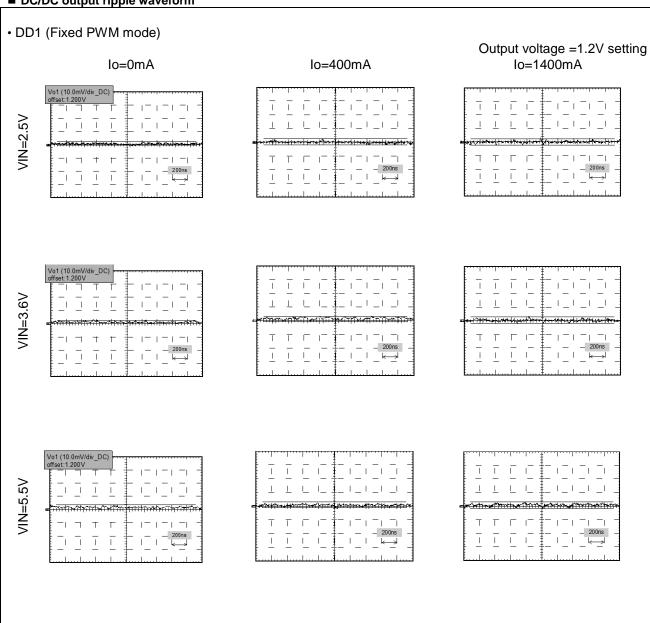

- Output voltage setting range, Maximum output current: DD1\*:1.0 V to 1.3 V (20 mV/step), 1.4 A (DC)

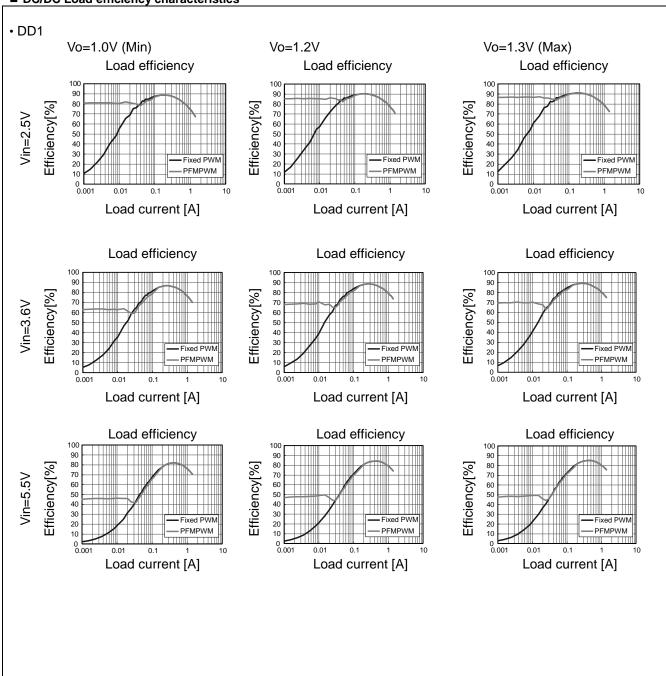

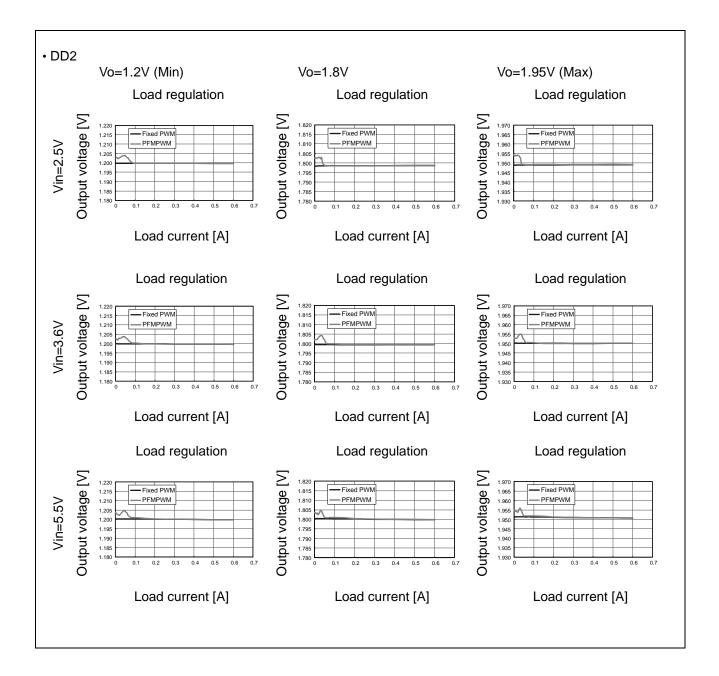

DD2\*:1.2 V to 1.95 V (50 mV/step), 0.6 A (DC) LDO:2.8 V/2.85 V/3.0 V/3.3 V, 0.25 A (DC)

Note: Each channel has selective preset voltage (Lineup for a total of 32 kinds) .

- Soft-start time setting range: 0.9 ms to 14.3 ms (approximately 0.9 ms/step)

- Switching frequency for the DC/DC block:3 MHz (fixed)

- Communication interface: I<sup>2</sup>C (ON/OFF, Output voltage, Soft-start time setting)

- Built-in PFM/PWM auto switching mode

- Built-in function: Output setting resistor, Phase compensation circuit, Discharge resistor, Soft-start

- Each Channel Power Good output function (Open-drain)

- Protection function: Under voltage lockout protection circuit (UVLO), Over current protection circuit (OCP), Thermal shutdown protection circuit (TSD)

- Error signal output pin installed (Open-drain)

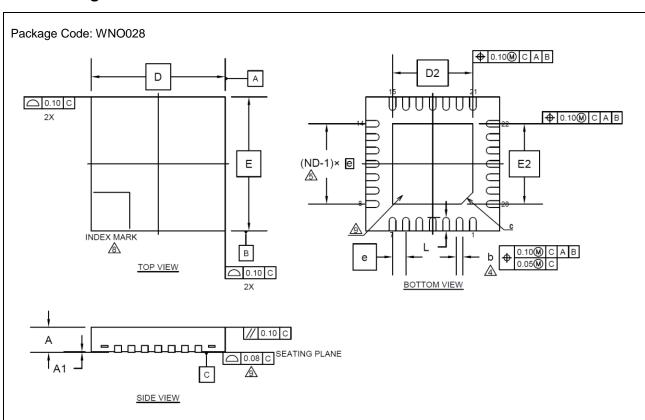

- Small package: QFN28 (4 mm × 4 mm × 0.8 mm, 0.4 mm pitch)

\*: DD1,DD2: DC/DC converter block 1, 2

#### **Applications**

Network equipment: Wifi-tuner, Surveillance camera

Data-storage device: HDD, SSD, Picture recording equipment

Image and voice output equipment: MFP, Printer, Scanner, Projector, Electrophone, STB

Various terminals: POS, FA, HEMS etc.

### **Contents**

| Des  | scription                                                                      | 1  |

|------|--------------------------------------------------------------------------------|----|

| Fea  | atures                                                                         | 1  |

| App  | lications                                                                      | 1  |

| 1.   | Application Circuit Example                                                    | 3  |

| 2.   | Recommended Application Specifications                                         | 4  |

| 3.   | Pin Assignment                                                                 | 6  |

| 4.   | Pin Descriptions (PKG)                                                         | 7  |

| 5.   | Block Diagram                                                                  |    |

| 6.   | Absolute Maximum Ratings                                                       | 10 |

| 7.   | Recommended Operating Conditions                                               |    |

| 8.   | Electrical Characteristics                                                     | 12 |

| 9.   | Operation Mode List                                                            |    |

| 10.  |                                                                                | 18 |

| 11.  |                                                                                |    |

|      | CTL* Turning On and Off Sequence 1 (VCC → CTL*: CTL1, CTL2, CTLMAIN)           |    |

|      | CTL* Turning On and Off Sequence 2(VCC→CTLMAIN→CTL1→CTL2)                      |    |

|      | CTL* Pin Threshold Voltage                                                     |    |

|      | Protection Operation Sequence                                                  |    |

|      | Operation Condition, Stop Circuit and Release Condition for Protection Circuit |    |

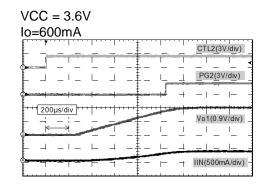

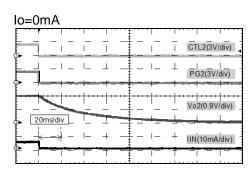

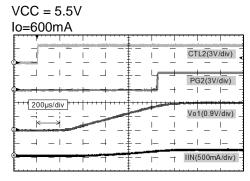

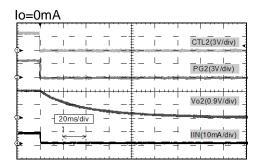

|      | DD Soft-Start Operation                                                        |    |

|      | Discharge Operation                                                            |    |

|      | PG1/PG2/PGL PIN and ERR PIN                                                    |    |

|      | I <sup>2</sup> C Interface                                                     |    |

|      | Structure of I <sup>2</sup> C Interface and Data                               |    |

|      | I/O Pin Equivalent Circuit Diagram                                             |    |

|      | I/O Circuit Type                                                               |    |

|      | Typical Operation Characteristic Measurement Circuit                           |    |

|      | Reference Data                                                                 |    |

|      | Usage Precaution                                                               |    |

|      | Ordering Information                                                           |    |

|      | Preset Code (MB39C031)                                                         |    |

|      | Package Dimensions                                                             |    |

|      | cument History                                                                 |    |

| Sale | es. Solutions, and Legal Information                                           | 69 |

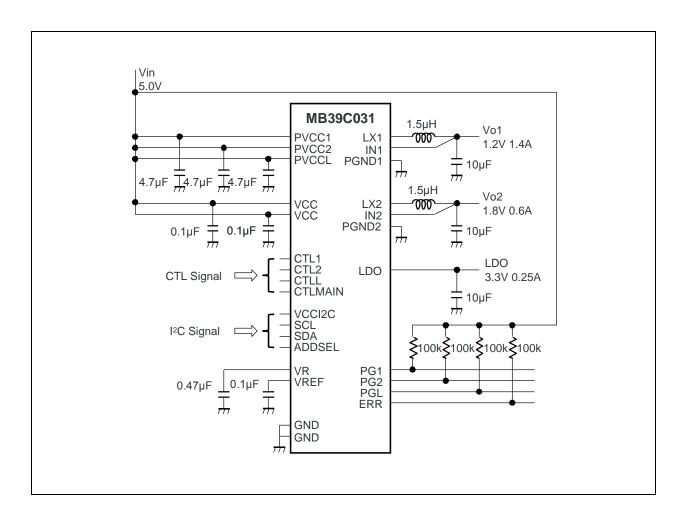

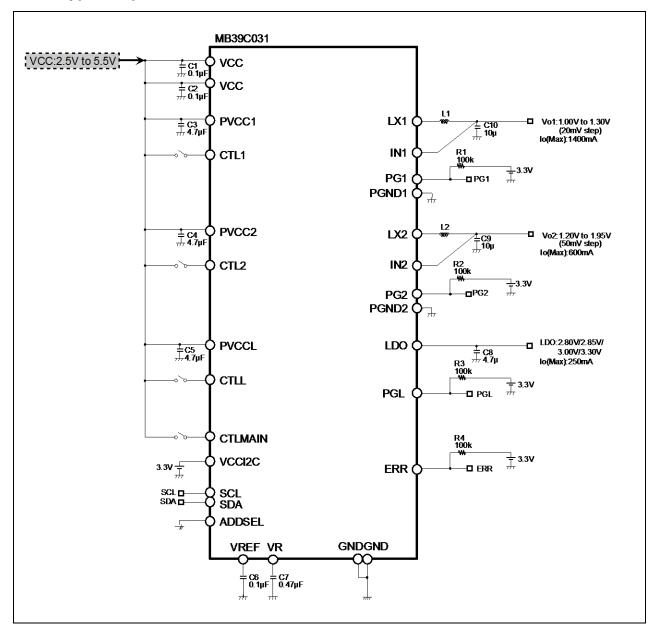

### 1. Application Circuit Example

### 2. Recommended Application Specifications

### [Input Voltage Range]

| Input | voltage VC | CC (V) |

|-------|------------|--------|

| Min   | Тур        | Max    |

| 2.5   | 3.6        | 5.5    |

#### [Output Specification]

(Ta=+25°C)

| Channel | Symbol | Accuracy | Outp  | ut vo<br>(V)  | Itage | Output<br>current<br>(mA) | Limit<br>Current<br>(mA) | Mode                     | Switching frequency | •••  | Output capacitance | time | Discharge resistance | Remarks                    |

|---------|--------|----------|-------|---------------|-------|---------------------------|--------------------------|--------------------------|---------------------|------|--------------------|------|----------------------|----------------------------|

| ပ်      | Sy     | Aco      | Min   | Тур           | Max   | Max                       | Min                      |                          | (MHz)               | (µH) | (μF)               | (ms) | (kΩ)                 |                            |

|         |        |          | 0.99* | 1.00*         | 1.01* |                           |                          |                          |                     |      |                    | 14.3 |                      |                            |

|         |        |          | 1.01  | 1.02          | 1.03  |                           |                          |                          |                     |      |                    | 0.9* |                      |                            |

|         |        |          | 1.03  | 1.04          | 1.05  |                           |                          |                          |                     |      |                    | 1.8  |                      | Duilt in CM                |

|         |        |          |       | 1.06          |       |                           |                          |                          |                     |      |                    | 2.7  |                      |                            |

|         |        |          |       | 1.08          |       |                           |                          |                          |                     |      |                    | 3.6  |                      | Built-in SW<br>FET         |

|         |        |          |       | 1.10*         |       |                           |                          |                          |                     |      |                    | 4.5  |                      | Built-in<br>output         |

|         |        |          |       | 1.12          |       |                           |                          | Buck                     |                     |      |                    | 5.4  |                      | setting                    |

| DD1     | Vo1    | ±1.2%    |       | 1.14          |       | 1400                      | 2000                     | (synchronous             | 3.0                 | 1.5  | 10                 | 6.3  | 5                    | resistors                  |

|         |        |          |       | 1.16          |       |                           |                          | rectification)<br>C-mode |                     |      |                    | 7.2  |                      | Operation mode             |

|         |        |          |       | 1.18          |       |                           |                          |                          |                     |      |                    | 8.1  |                      | switching                  |

|         |        |          | 1.19  | 1.20*<br>1.22 | 1.23  |                           |                          |                          |                     |      |                    | 9.0  |                      | (Fixed<br>PWM,<br>PFM/PWM) |

|         |        |          |       | 1.24          |       |                           |                          |                          |                     |      |                    | 10.8 |                      |                            |

|         |        |          |       | 1.26          |       |                           |                          |                          |                     |      |                    | 11.6 |                      |                            |

|         |        |          |       | 1.28          |       |                           |                          |                          |                     |      |                    | 12.5 |                      |                            |

|         |        |          |       | 1.30*         |       |                           |                          |                          |                     |      |                    | 13.4 |                      |                            |

|         |        |          | 1.19* |               |       |                           |                          |                          |                     |      |                    | 14.3 |                      |                            |

|         |        |          | 1.24  | 1.25          | 1.27  |                           |                          |                          |                     |      |                    | 0.9* |                      |                            |

|         |        |          | 1.28  | 1.30          | 1.32  |                           |                          |                          |                     |      |                    | 1.8  |                      |                            |

|         |        |          | 1.33* | 1.35*         | 1.37* |                           |                          |                          |                     |      |                    | 2.7  |                      |                            |

|         |        |          | 1.38  | 1.40          | 1.42  |                           |                          |                          |                     |      |                    | 3.6  |                      | Built-in SW<br>FET         |

|         |        |          | 1.43  | 1.45          | 1.47  |                           |                          |                          |                     |      |                    | 4.5  |                      | Built-in                   |

|         |        |          | 1.48* |               |       |                           |                          | Buck                     |                     |      |                    | 5.4  |                      | output<br>setting          |

| DD2     | Vo2    | ±1.2%    | _     | 1.55          |       | 600                       | 900                      | (synchronous             | 3.0                 | 1.5  | 10                 | 6.3  | 5                    | resistors                  |

|         |        | /0       | 1.58  | 1.60          | 1.62  |                           |                          | rectification)<br>C-mode | 0.0                 |      |                    | 7.2  | Ů                    | Operation mode             |

|         |        |          |       |               |       |                           |                          | C-IIIoue                 |                     |      |                    | 8.1  |                      | switching                  |

|         |        |          |       | 1.70          | 1.72  |                           |                          |                          |                     |      |                    | 9.0  |                      | (Fixed<br>PWM,             |

|         |        |          |       | 1.75          | 1.77  |                           |                          |                          |                     |      |                    | 9.9  |                      | PFM/PWM)                   |

|         |        |          | 1.78* |               |       |                           |                          |                          |                     |      |                    | 10.8 |                      |                            |

|         |        |          |       |               |       |                           |                          |                          |                     |      |                    | 11.6 |                      |                            |

|         |        |          |       |               |       |                           |                          |                          |                     |      |                    | 12.5 |                      |                            |

|         |        |          | 1.93  | 1.95          | 1.97  |                           |                          |                          |                     |      |                    | 13.4 |                      |                            |

| Channel | Symbol | Accuracy | Outp  | ut vo<br>(V) |       | Output<br>current<br>(mA) | Limit<br>Current<br>(mA) | Mode | Switching frequency | Coil<br>(µH) | capacitance   | time | Discharge resistance | Remarks |

|---------|--------|----------|-------|--------------|-------|---------------------------|--------------------------|------|---------------------|--------------|---------------|------|----------------------|---------|

| ភ       | S      | Acc      | Min   | Тур          | Max   | Max                       | Min                      |      | (MHz)               | (μπ)         | (μ <b>F</b> ) | (ms) | (kΩ)                 |         |

|         |        |          | 2.75  | 2.80         | 2.85  |                           |                          |      |                     |              |               | 14.3 |                      |         |

|         |        |          | 2.80* | 2.85*        | 2.90* |                           |                          |      |                     |              |               | 0.9  |                      |         |

|         |        |          | 2.95  | 3.00         | 3.05  |                           |                          |      |                     |              |               | 1.8  |                      |         |

|         |        |          | 3.24* | 3.30*        | 3.36* |                           |                          |      |                     |              |               | 2.7* |                      |         |

|         |        |          | -     | -            | -     |                           |                          |      |                     |              |               | 3.6  |                      |         |

|         |        |          | -     | -            | -     |                           |                          |      |                     |              |               | 4.5  |                      |         |

|         |        |          | -     | -            | -     |                           |                          |      |                     |              |               | 5.4  |                      |         |

| LDO     | I DO   | ±1.8%    | -     | -            | -     | 250                       | 300                      | LDO  | _                   | _            | 4.7           | 6.3  | 5                    |         |

|         | LDO    | ±1.070   | -     | -            | -     | 200                       | 300                      | LDO  |                     |              | 4.7           | 7.2  | 3                    |         |

|         |        |          | -     | -            | -     |                           |                          |      |                     |              |               | 8.1  |                      |         |

|         |        |          | -     | -            | -     |                           |                          |      |                     |              |               | 9.0  |                      |         |

|         |        |          | -     | -            | -     |                           |                          |      |                     |              |               | 9.9  |                      |         |

|         |        |          | -     | -            | -     |                           |                          |      |                     |              |               | 10.8 |                      |         |

|         |        |          | -     | -            | -     |                           |                          |      |                     |              |               | 11.6 |                      |         |

|         |        |          | -     | -            | -     |                           |                          |      |                     |              |               | 12.5 |                      |         |

|         |        |          | -     | -            | -     |                           |                          |      |                     |              |               | 13.4 |                      |         |

\*: Preset value

Note: It is possible to set the output voltage and to change the soft-start time using  $I^2C$ .

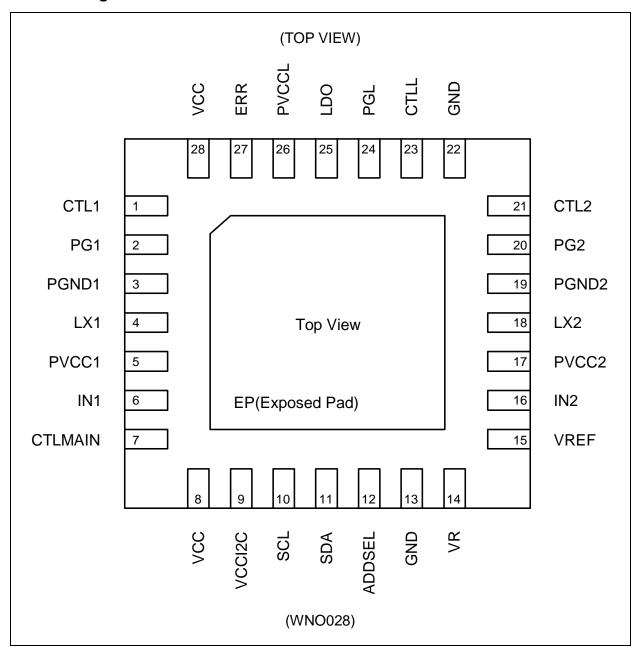

### 3. Pin Assignment

### 4. Pin Descriptions (PKG)

| Circuit<br>block | Pin name | Numb<br>er of<br>pin for<br>PKG | Pin<br>No | I/O | Description<br>(PKG)                             | Pull-<br>down<br>resist<br>ance | PAD<br>treatment<br>when not<br>using<br>DD1 | PAD<br>treatment<br>when not<br>using<br>DD2 | PAD<br>treatment<br>when not<br>using LDO | PAD<br>treatment<br>when not<br>using I <sup>2</sup> C<br>communi<br>cation |

|------------------|----------|---------------------------------|-----------|-----|--------------------------------------------------|---------------------------------|----------------------------------------------|----------------------------------------------|-------------------------------------------|-----------------------------------------------------------------------------|

|                  | IN1      | 1                               | 6         | I   | DD1-Output<br>voltage feedback<br>pin.           | -                               | GND<br>connection                            | -                                            | -                                         | -                                                                           |

|                  | PVCC1    | 1                               | 5         | -   | DD1-Output block power supply pin                | -                               | VCC connection                               | -                                            | -                                         | -                                                                           |

| DD1              | LX1      | 1                               | 4         | 0   | DD1-Pin for inductance connection.               | -                               | Open                                         | -                                            | -                                         | -                                                                           |

|                  | PG1      | 1                               | 2         | 0   | DD1-POWERGOO<br>D output pin                     | -                               | Open                                         | -                                            | -                                         | -                                                                           |

|                  | PGND1    | 1                               | 3         | -   | DD1-Output block ground pin                      | -                               | GND connection                               | -                                            | -                                         | -                                                                           |

|                  | IN2      | 1                               | 16        | I   | DD2-Output<br>voltage feedback<br>pin.           | -                               | -                                            | GND<br>connection                            | -                                         | -                                                                           |

|                  | PVCC2    | 1                               | 17        | -   | DD2-Output block power supply pin                | -                               | -                                            | VCC<br>connection                            | =                                         | -                                                                           |

| DD2              | LX2      | 1                               | 18        | 0   | DD2-Pin for inductance connection.               | Open                            |                                              | Open                                         | -                                         | -                                                                           |

|                  | PG2      | 1                               | 20        | 0   | DD2-POWERGOO<br>D output pin                     | -                               | -                                            | Open                                         | -                                         | -                                                                           |

|                  | PGND2    | 1                               | 19        | -   | DD2-Output block ground pin                      | -                               | -                                            | GND connection                               | -                                         | -                                                                           |

|                  | PVCCL    | 1                               | 26        | -   | LDO-Power supply pin                             | -                               | -                                            | -                                            | VCC<br>connection                         | -                                                                           |

| LDO              | LDO      | 1                               | 25        | 0   | LDO-Output pin                                   | -                               | -                                            | -                                            | Open                                      | -                                                                           |

|                  | PGL      | 1                               | 24        | 0   | LDO-POWERGOO<br>D output pin                     | -                               | -                                            | -                                            | Open                                      | -                                                                           |

|                  | CTL1     | 1                               | 1         | I   | DD1 Control pin                                  | O                               | Open                                         | -                                            | -                                         | -                                                                           |

|                  | CTL2     | 1                               | 21        | I   | DD2 Control pin                                  | •                               | -                                            | Open                                         | -                                         | -                                                                           |

| CTL              | CTLL     | 1                               | 23        | I   | LDO Control pin                                  | •                               | -                                            | -                                            | Open                                      | -                                                                           |

|                  | CTLMAIN  | 1                               | 7         | I   | Control pin for common block and digital block * | O                               | -                                            | -                                            | -                                         | -                                                                           |

| ERR              | ERR      | 1                               | 27        | 0   | ERR signal output pin                            | -                               | -                                            | -                                            | -                                         | -                                                                           |

| Circuit<br>block | Pin name | Numb<br>er of<br>pin for<br>PKG | Pin<br>No | I/O | Description<br>(PKG)                   | Pull-<br>down<br>resist<br>ance | whon not | PAD<br>treatment<br>when not<br>using<br>DD2 | PAD<br>treatment<br>when not<br>using LDO | PAD<br>treatment<br>when not<br>using I <sup>2</sup> C<br>communi<br>cation |

|------------------|----------|---------------------------------|-----------|-----|----------------------------------------|---------------------------------|----------|----------------------------------------------|-------------------------------------------|-----------------------------------------------------------------------------|

|                  | VCCI2C   | 1                               | 9         | -   | Power supply pin for I <sup>2</sup> C. | -                               | -        | -                                            | _                                         | GND connection                                                              |

| I <sup>2</sup> C | SCL      | 1                               | 10        | I   | I <sup>2</sup> C clock pin             | ×                               | -        | -                                            | -                                         | Open                                                                        |

|                  | SDA      | 1                               | 11        | I/O | I <sup>2</sup> C data I/O pin          | ×                               | -        | -                                            | -                                         | Open                                                                        |

|                  | ADDSEL   | 1                               | 12        | I   | Switch pin for slave address           | O                               | -        | -                                            | -                                         | Open                                                                        |

|                  | VCC      | 2                               | 8,<br>28  | -   | Control circuit block power supply pin | -                               | -        | -                                            | -                                         | -                                                                           |

| Commo            | VREF     | 1                               | 15        | 0   | Reference voltage (2.4V) output pin    | -                               | -        | -                                            | =                                         | -                                                                           |

| n                | VR       | 1                               | 14        | 0   | Reference voltage (0.6V) output pin    | -                               | -        | -                                            | -                                         | -                                                                           |

|                  | GND      | 2                               | 13,<br>22 | -   | Control circuit block ground pin       | =                               | -        | -                                            | -                                         | -                                                                           |

| -                | GND      | 1                               | EP        | -   | Ground pin                             | -                               | -        | -                                            | -                                         | -                                                                           |

<sup>\*:</sup> When turning on DD1, DD2 and LDO, it is also necessary to set CTLMAIN to "H". See 9. Operation Mode List for the details.

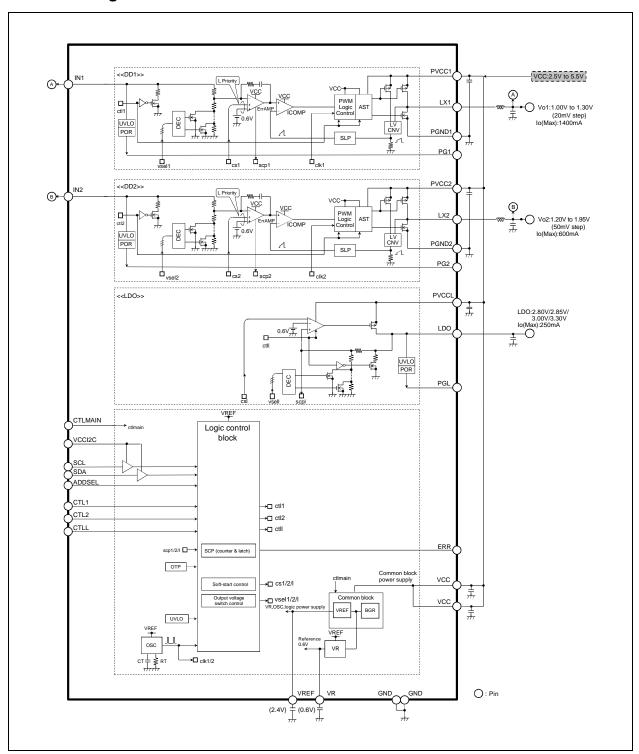

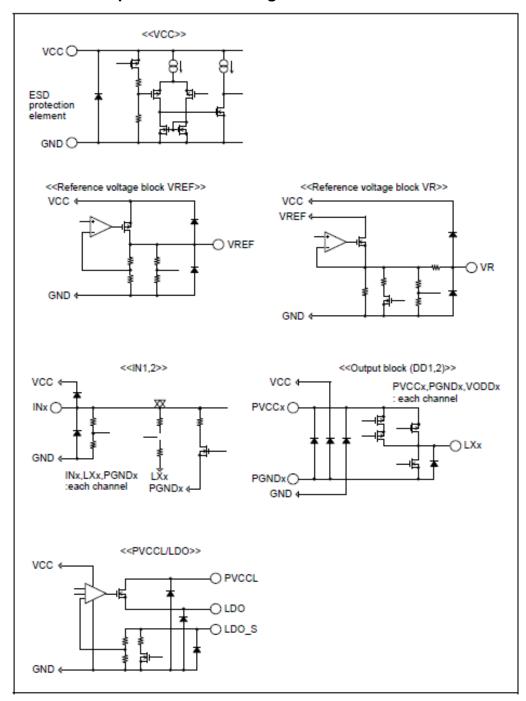

### 5. Block Diagram

### 6. Absolute Maximum Ratings

| Parameter                    | Cumbal            | Condition                             | Rat  | ting | Unit  |  |

|------------------------------|-------------------|---------------------------------------|------|------|-------|--|

| Parameter                    | Symbol            | Condition                             | Min  | Max  | Oilit |  |

| Power supply voltage         | V <sub>cc</sub>   | VCC, PVCC1, PVCC2, PVCCL, VCCI2C pins | -    | 7    | V     |  |

|                              | V <sub>CTL</sub>  | CTLMAIN, 1, 2, L pins                 | -    | 7    | V     |  |

| Input voltage                | V <sub>OUT</sub>  | IN1, IN2 pins                         | -    | 7    | V     |  |

|                              | Vlogic            | SDA, SCL pins                         | -    | 7    | V     |  |

| LX voltage                   | V <sub>LX</sub>   | LX1, LX2 pins                         | -0.3 | +7   | V     |  |

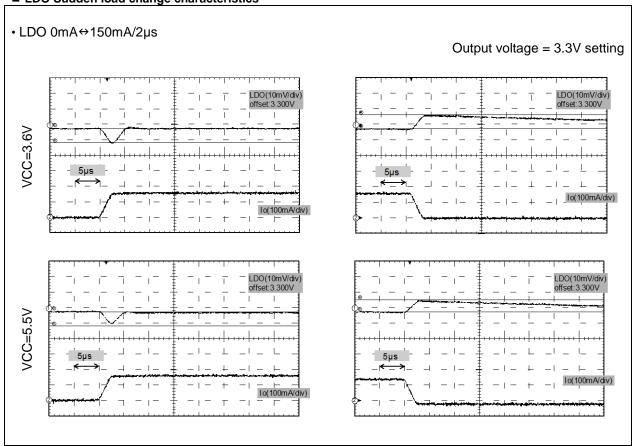

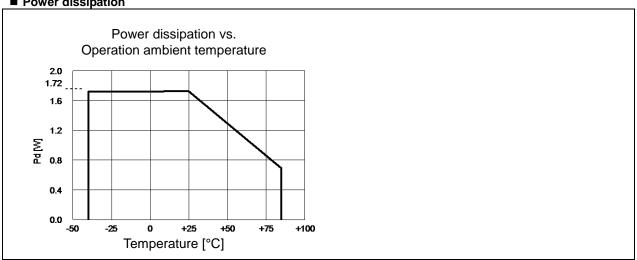

| Power dissipation            | P <sub>D</sub>    | Ta ≤ +25°C Thermal resistor value     | -    | 1720 | mW    |  |

| ·                            |                   | (θj-a):(50°C/W*)                      |      |      |       |  |

| Maximum junction temperature | T <sub>jmax</sub> | -                                     | -    | +125 | °C    |  |

| Storage temperature          | T <sub>STG</sub>  | -                                     | -55  | +125 | °C    |  |

<sup>\*:</sup> When mounted on a QFN28 (WNO028) PKG, 4layers 0.8 mm thickness 117 mm × 84 mm

WARNING: Semiconductor devices can be permanently damaged by application of stress (voltage, current, temperature, etc.) in excess of absolute maximum ratings. Do not exceed these ratings.

### 7. Recommended Operating Conditions

| Do                 | rameter               | Cumbal           | Condition                                              |      | Value |        | Unit |

|--------------------|-----------------------|------------------|--------------------------------------------------------|------|-------|--------|------|

| Pa                 | rameter               | Symbol           | Condition                                              | Min  | Тур   | Max    | Unit |

|                    | Power supply voltage  | V <sub>CC</sub>  | VCC pin                                                | 2.5  | 3.6   | 5.5    | V    |

| General            | Reference voltage     | I <sub>REF</sub> | VREF pin                                               | -1   | -     | 0      | mA   |

| General            | output<br>current     | I <sub>R</sub>   | VR pin                                                 | -1   | -     | 0      | μΑ   |

|                    | Operating temperature | Та               | -                                                      | -30  | +25   | +85    | °C   |

| DC/DC<br>CH        | Power supply voltage  | V <sub>CC</sub>  | VCC, PVCC1, PVCC2 pins                                 | 2.5  | 3.6   | 5.5    | V    |

| СП                 | Input voltage         | V <sub>OUT</sub> | IN1, IN2 pins                                          | 0    | -     | VCC    | V    |

| LDO CH             | Power supply voltage  | V <sub>CC</sub>  | VCC, PVCCL pins Output voltage setting: default (3.3V) | 3.5  | 3.6   | 5.5    | V    |

| CTL<br>block       | Input voltage         | V <sub>CTL</sub> | CTL* pin                                               | 0    | -     | VCC    | V    |

| Digital<br>block   | Power supply voltage  | V <sub>CC</sub>  | VCCI2C pin                                             | 1.76 | -     | 3.37   | V    |

| (I <sup>2</sup> C) | Logic input voltage   | Vlogic           | SDA, SCL pin                                           | 0    | -     | VCCI2C | V    |

<sup>\*:</sup> CTLMAIN, CTL1, CTL2, CTLL

WARNING: The recommended operating conditions are required in order to ensure the normal operation of the semiconductor device. All of the device's electrical characteristics are warranted when the device is operated within these ranges. Always use semiconductor devices within their recommended operating condition ranges. Operation outside these ranges may adversely affect reliability and could result in device failure.

No warranty is made with respect to uses, operating conditions, or combinations not represented on the data sheet. Users considering application outside the listed conditions are advised to contact their representatives beforehand.

### 8. Electrical Characteristics

#### **Common Block**

| Danam                                                 |                          | Comple ed           | Comdition                                                                   |              | Value |       | Unit |

|-------------------------------------------------------|--------------------------|---------------------|-----------------------------------------------------------------------------|--------------|-------|-------|------|

| Param                                                 | ieter                    | Symbol              | Condition                                                                   | Min          | Тур   | Max   | Unit |

|                                                       |                          | $V_R$               | VR pin =0mA                                                                 | 0.594        | 0.600 | 0.606 | V    |

| Reference Voltage                                     | Output valtage           | V <sub>REF1</sub>   | VREF pin =0mA                                                               | 2.376        | 2.400 | 2.424 | V    |

| Block<br>[VR, VREF]                                   | Output voltage           | V <sub>REF2</sub>   | VCC pin =2.5V to 5.5V                                                       | 2.370        | 2.400 | 2.430 | V    |

|                                                       |                          | V <sub>REF3</sub>   | VREF pin =0mA to -1mA                                                       | 2.370        | 2.400 | 2.430 | V    |

| Under Voltage<br>Lockout Protection                   | Threshold voltage        | V <sub>TH</sub>     | VCC pin = _                                                                 | 2.156        | 2.20  | 2.244 | V    |

| Circuit Block<br>[VCC UVLO]                           | Hysteresis width         | V <sub>H</sub>      | -                                                                           | -            | 0.20  | -     | V    |

| Over Current Protection Circuit Block [OCP]           | Timer time               | t <sub>OCP1</sub>   | DD1, DD2, LDO Default value                                                 | 0.5          | 1     | 1.5   | ms   |

| Thermal shutdown<br>Protection Circuit<br>Block [TSD] | Stop temperature         | T <sub>TSDH</sub>   | -                                                                           | -            | 150*  | -     | °C   |

|                                                       | Input voltage            | V <sub>IH</sub>     | CTL* pin                                                                    | VCC<br>× 0.7 | -     | VCC   | V    |

|                                                       |                          | V <sub>IL</sub>     | CTL* pin                                                                    | 0            | -     | 0.4   | V    |

| Control Block (CTL) [CTL]                             | Input current            | I <sub>CTLH</sub>   | CTL* pin =3.6V                                                              | 2.7          | 3.6   | 5.1   | μΑ   |

| [0.2]                                                 | input current            | I <sub>CTLL</sub>   | CTL* pin =0V                                                                | -            | -     | 1     | μA   |

|                                                       | Input pull-down resistor | R <sub>P</sub>      | CTL* pin                                                                    | -            | 1     | -     | МΩ   |

|                                                       |                          | I <sub>VCCS1</sub>  | CTL* pin =0V                                                                | -            | 0     | 1.0   | μA   |

|                                                       |                          | I <sub>VCCS2</sub>  | CTLMAIN=3.6V<br>CTL1, CTL2.L pins =0V                                       | -            | 80    | 120   | μΑ   |

|                                                       |                          | I <sub>vcc</sub>    | CTLMAIN, L pins =3.6V Only LDO operation No load                            | -            | 200   | 300   | μΑ   |

| General<br>(DC/DC block)                              | Power supply current     | lvcc                | CTL* pin = 3.6V<br>all CH No load<br>(DD operation mode:<br>PFM/PWM mode)   | -            | 450   | 680   | μΑ   |

|                                                       |                          | Ivec                | CTL* pin = 3.6V<br>all CH No load<br>(DD operation mode:<br>Fixed PWM mode) | -            | 10.8  | 16.2  | mA   |

|                                                       |                          | I <sub>VCCI2C</sub> | CTLMAIN, L pin=3.6V<br>VCCI2C pin = 1.8V                                    | -            | 7.2   | 12.0  | μА   |

<sup>\*:</sup> These are not the rated values. Use these values as reference when planning.

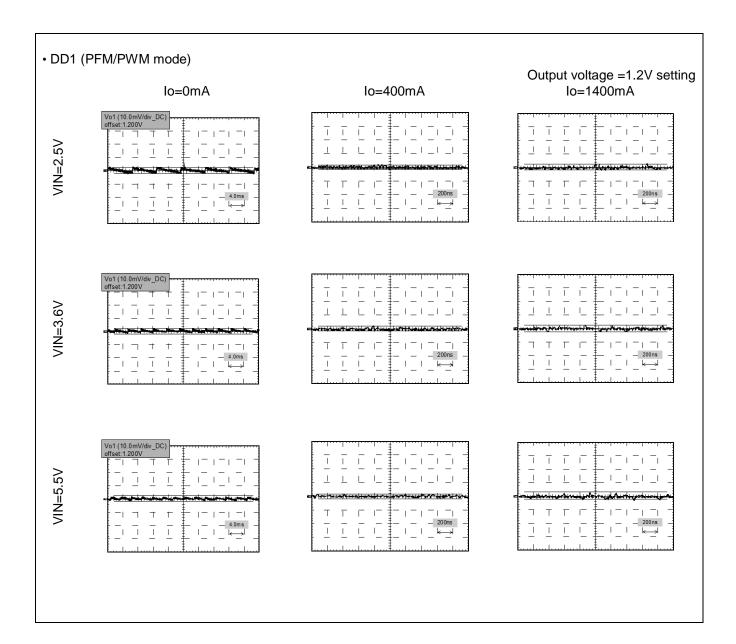

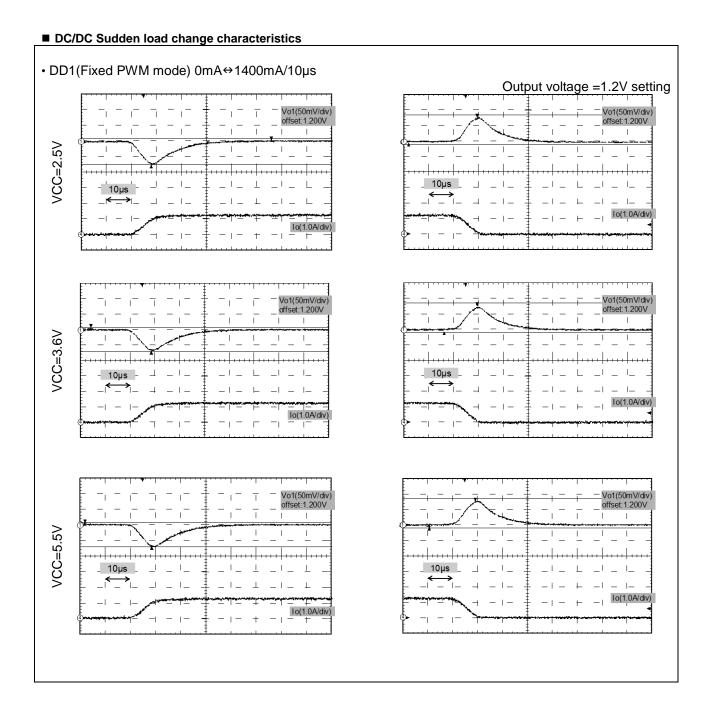

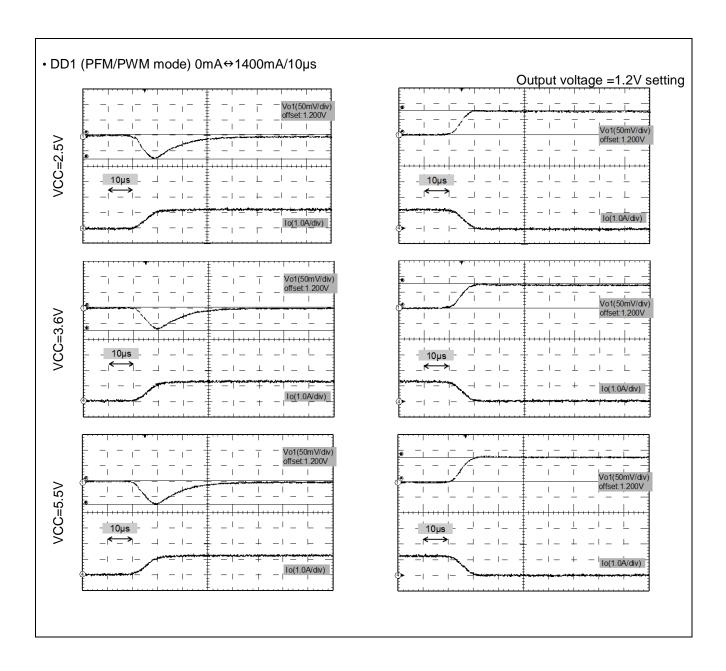

#### DD1, DD2

|                          | Namana 4 a n                         | Complete           | Condition                                        |       | Value |       | Unit |

|--------------------------|--------------------------------------|--------------------|--------------------------------------------------|-------|-------|-------|------|

| <u>'</u>                 | Parameter                            | Symbol             | Condition                                        | Min   | Тур   | Max   | Unit |

|                          | Output voltage                       | V <sub>OUT</sub>   | Output voltage setting: 1.2V IOUT=-10mA          | 1.186 | 1.20  | 1.214 | ٧    |

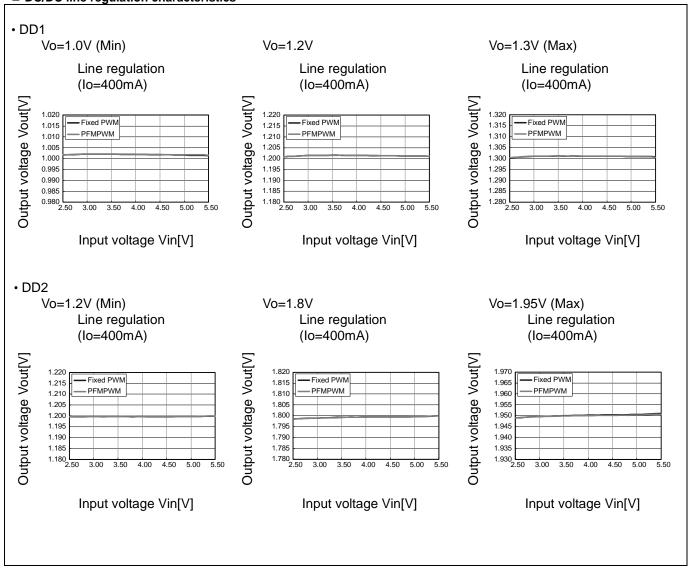

|                          | Input stability                      | V <sub>LINE</sub>  | IOUT=-10mA, VCC=2.5V to 5.5V                     | -5    | -     | +5    | mV   |

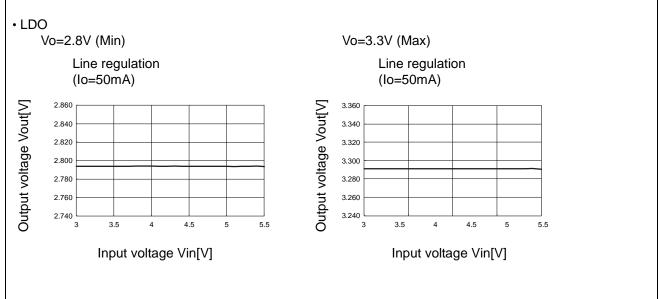

|                          | Load stability                       | $V_{LOAD}$         | IOUT=-1mA to -1400mA<br>(when in Fixed PWM mode) | -10   | -     | -     | mV   |

|                          | Load Stability                       | <b>V</b> LOAD      | IOUT=-1mA to -1400mA<br>(when in PFM/PWM mode)   | -10   | -     | +15   | mV   |

|                          |                                      |                    | IN1 pin=1.5V                                     |       |       |       |      |

|                          | IN1 pin input impedance              | R <sub>IN</sub>    | output voltage setting: 1.2V                     | -     | 400   | -     | kΩ   |

| DC/DC<br>Converter Block | SW PMOS-Tr ON resistance             | R <sub>PMOS</sub>  | LX1 pin=-30mA                                    | -     | 0.12* | -     | Ω    |

| [DD1]                    | SW NMOS-Tr ON resistance             | R <sub>NMOS</sub>  | LX1 pin= 30mA                                    | -     | 0.09* | -     | Ω    |

|                          | SW PMOS-Tr leak current              | I <sub>LEAK</sub>  | LX1 pin=0V                                       | -1    | -     | -     | μА   |

|                          | SW NMOS-Tr leak current              | I <sub>LEAK</sub>  | LX1 pin=3.6V                                     | -     | -     | 1     | μА   |

|                          | Overcurrent protection value         | I <sub>LIMIT</sub> | L=1.5µH                                          | 2000  | -     | -     | mA   |

|                          | PFM/PWM reshuffling electric current | I <sub>PFM</sub>   | L=1.5μH                                          | -     | 40*   | -     | mA   |

|                          | Discharge resistor                   | R <sub>DIS</sub>   | -                                                | -     | 5     | -     | kΩ   |

|                          | Soft-start time                      | t <sub>SS</sub>    | Preset value                                     | 0.8   | 0.9   | 1.0   | ms   |

|                          | Switching frequency                  | f <sub>osc</sub>   | -                                                | 2.7   | 3.0   | 3.3   | MHz  |

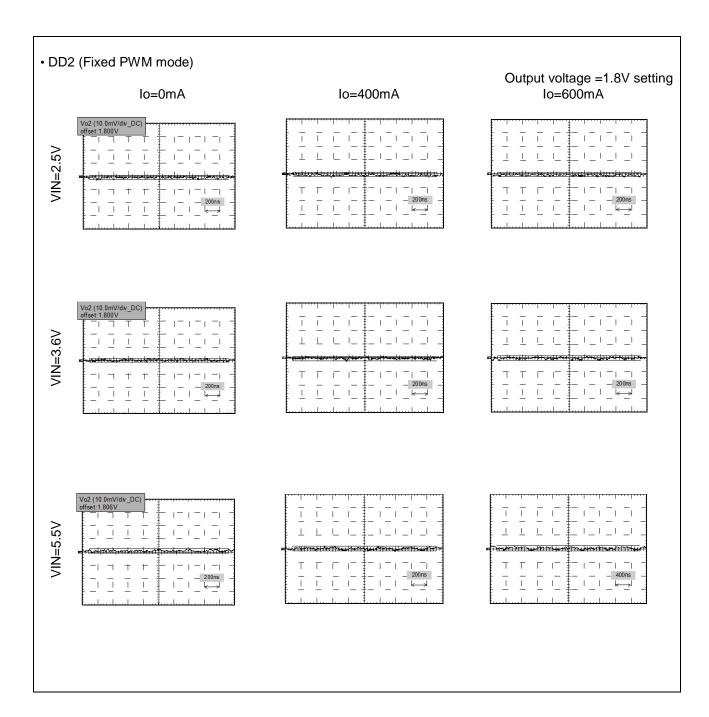

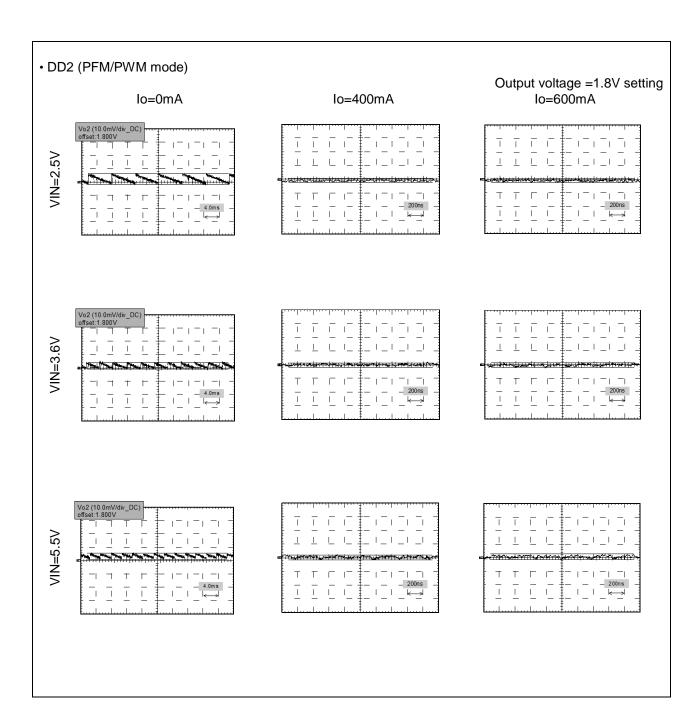

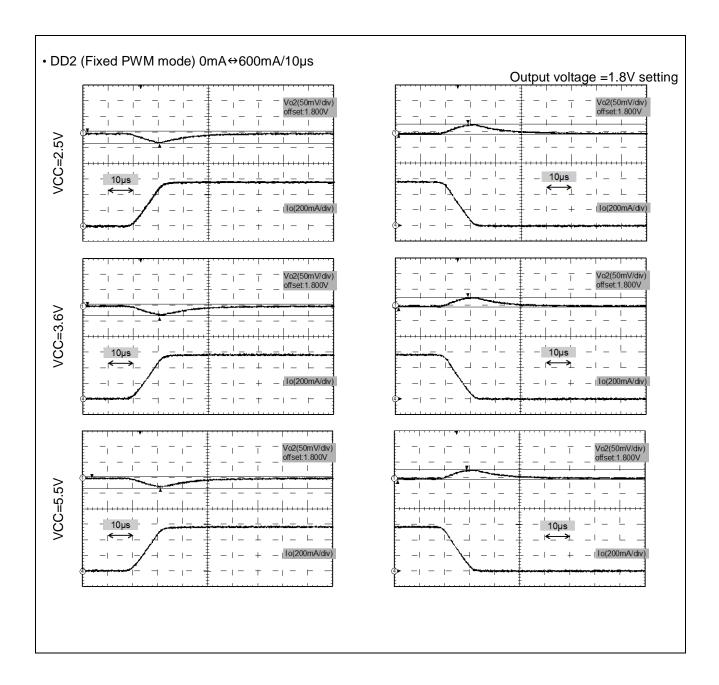

|                       | Davana atau                          | Cumala al          | Condition                                       |       | Value |       | Unit |

|-----------------------|--------------------------------------|--------------------|-------------------------------------------------|-------|-------|-------|------|

| ·                     | Parameter                            | Symbol             | Condition                                       | Min   | Тур   | Max   | Unit |

|                       | Output voltage                       | V <sub>OUT</sub>   | Output voltage setting: 1.8V IOUT=-10mA         | 1.778 | 1.80  | 1.822 | V    |

|                       | Input stability                      | V <sub>LINE</sub>  | IOUT=-10mA VCC=2.5V to 5.5V                     | -5    | -     | +5    | mV   |

|                       | Load stability                       | VLOAD              | IOUT=-1mA to -600mA<br>(when in Fixed PWM mode) | -10   | -     | -     | mV   |

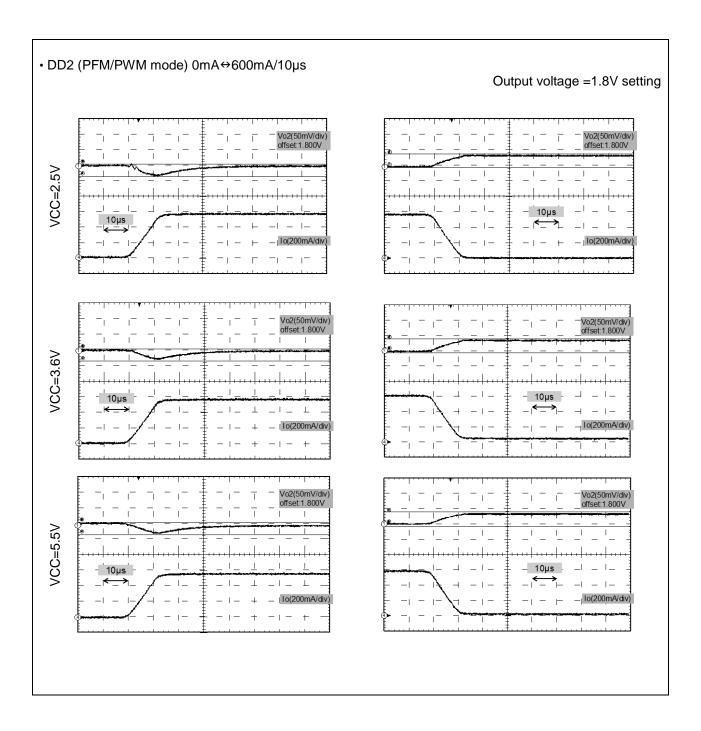

|                       | Load Stability                       | <b>V</b> LOAD      | IOUT=-1mA to -600mA<br>(when in PFM/PWM mode)   | -10   | -     | +20   | mV   |

|                       | IN2 pin input impedance              | R <sub>IN</sub>    | IN2 pin =2.0V<br>Output voltage setting: 1.8V   | 1     | 300   | -     | kΩ   |

| DC/DC                 | SW PMOS-Tr ON resistance             | R <sub>PMOS</sub>  | LX2 pin =-30mA                                  | -     | 0.16* | -     | Ω    |

| Converter Block [DD2] | SW NMOS-Tr ON resistance             | R <sub>NMOS</sub>  | LX2 pin = 30mA                                  | -     | 0.14* | -     | Ω    |

|                       | SW PMOS-Tr leak current              | I <sub>LEAK</sub>  | LX2 pin =0V                                     | -1    | -     | -     | μΑ   |

|                       | SW NMOS-Tr leak current              | I <sub>LEAK</sub>  | LX2 pin =3.6V                                   | -     | -     | 1     | μΑ   |

|                       | Overcurrent protection value         | I <sub>LIMIT</sub> | L=1.5μH                                         | 900   | -     | -     | mA   |

|                       | PFM/PWM reshuffling electric current | I <sub>PFM</sub>   | L=1.5μH                                         | -     | 70*   | -     | mA   |

|                       | Discharge resistor                   | R <sub>DIS</sub>   | -                                               | -     | 5     | -     | kΩ   |

|                       | Soft-start time                      | t <sub>SS</sub>    | Preset value                                    | 0.8   | 0.9   | 1.0   | ms   |

|                       | Switching frequency                  | fosc               | -                                               | 2.7   | 3.0   | 3.3   | MHz  |

<sup>\*:</sup> These are not the rated values. Use these values as reference when planning.

#### LDO

|           | Darameter                    | Cumbal              | Condition                                |       | Value |       | Unit |

|-----------|------------------------------|---------------------|------------------------------------------|-------|-------|-------|------|

|           | Parameter                    | Symbol              | Condition                                | Min   | Тур   | Max   | Unit |

|           | Output voltage               | V <sub>OUT</sub>    | Output voltage setting : 3.3V IOUT=-10mA | 3.241 | 3.300 | 3.359 | V    |

|           | I/O voltage difference       | $V_{DIF}$           | IOUT=-10mA                               | -     | -     | 0.20  | V    |

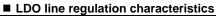

|           | Input stability              | V <sub>LINE</sub>   | IOUT=-10mA,<br>VCC=3.5V to 5.5V          | -5    | -     | +5    | mV   |

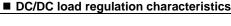

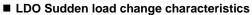

|           | Load stability               | $V_{LOAD}$          | IOUT=-1mA to -150mA                      | -30   | -20   | -     | mV   |

| LDO Block | <u> </u>                     |                     | PVCCL=0.2Vrms, f=10Hz,<br>IOUT=-150mA    | 35    | 75    | -     | dB   |

| [LDO]     | Ripple remove ratio          | RR                  | PVCCL=0.2Vrms, f=10kHz,<br>IOUT=-150mA   | 15    | 50    | -     | dB   |

|           | Overcurrent protection value | I <sub>LIMIT</sub>  | Vout×0.9                                 | 300   | -     | -     | mA   |

|           | Control macro                | I <sub>PVCCLS</sub> | At stand-by                              | -     | 0     | 1     | μA   |

|           | consumption current          | I <sub>PVCCL</sub>  | IOUT=0mA                                 | -     | 80    | 105   | μA   |

|           | Discharge resistor           | R <sub>DIS</sub>    | -                                        | -     | 5     | -     | kΩ   |

|           | Soft-start time              | t <sub>SS</sub>     | Preset value                             | 2.4   | 2.7   | 3.0   | ms   |

#### **Digital Block**

| Parameter                                    |                                  | Complete                         | Condition                                | Value           |               |              | Unit |

|----------------------------------------------|----------------------------------|----------------------------------|------------------------------------------|-----------------|---------------|--------------|------|

|                                              |                                  | Symbol                           | Condition                                | Min             | Тур           | Max          | Unit |

|                                              | Output voltage                   | V <sub>OL</sub>                  | PG1, PG2, L pins<br>I <sub>OL</sub> =1mA | -               | -             | 0.4          | V    |

| DOWED OOOD                                   | Output current                   | I <sub>OL</sub> PG1, PG2, L pins |                                          | 1               | -             | =            | mA   |

| POWER-GOOD<br>Block<br>[Power Good ]         | Low-voltage detection            | $V_{th}$                         | IN1, IN2, LDO pins                       | -               | Vo ×<br>0.75* | -            | V    |

|                                              | Power-on<br>detection<br>voltage | V <sub>th</sub>                  | IN1, IN2, LDO pins                       | -               | Vo ×<br>0.85* | -            | V    |

| Error Block                                  | Output voltage                   | V <sub>OL</sub>                  | $V_{OL}$ ERR pin $I_{OL} = 1$ mA         |                 | -             | 0.4          | V    |

| [ERR]                                        | Output current                   | I <sub>OL</sub>                  | ERR pin                                  | 1               | -             | =            | mA   |

|                                              | land to the same                 | V <sub>IH</sub>                  | SCL, SDA pins<br>VCCI2C=3.3V             | VCCI2C ×<br>0.7 | -             | VCCI2C       | V    |

|                                              | Input voltage                    | V <sub>IL</sub>                  | SCL, SDA pins<br>VCCI2C=3.3V             | 0               | -             | VCCI2C × 0.3 | V    |

| 120 Plants                                   | land somet                       | I <sub>IH</sub>                  | SCL, SDA pins<br>VCCI2C=3.3V             | -               | -             | 10           | μA   |

| I <sup>2</sup> C Block<br>[I <sup>2</sup> C] | Input current I <sub>IL</sub>    | I <sub>IL</sub>                  | SCL, SDA pins<br>VCCI2C=3.3V             | -10             | -             | -            | μA   |

|                                              | Output voltage                   | V <sub>OL</sub>                  | SDA pin I <sub>OL</sub> =3mA             | -               | -             | 0.4          | V    |

|                                              | Output current                   | I <sub>OL</sub>                  | SDA pin                                  | 3               | -             | -            | mA   |

|                                              | Input<br>pull-down<br>resistor   | R <sub>P</sub>                   | ADDSEL pin                               | -               | 1             | -            | МΩ   |

<sup>\*:</sup> These are not the rated values. Use these values as reference when planning.

### 9. Operation Mode List

|                                   | Mode                                 | Stand-by      | Stand-by 2    | General   | ERR detection |

|-----------------------------------|--------------------------------------|---------------|---------------|-----------|---------------|

|                                   | CTLMAIN (External)                   | L             | Н             | Н         | Н             |

| CTI Cianal                        | CTL1 (External / I <sup>2</sup> C)   | L             | L             | H/L       | Х             |

| CTL Signal                        | CTL2 (External / I <sup>2</sup> C)   | L             | L             | H/L       | Х             |

|                                   | CTLL (External / I <sup>2</sup> C)   | L             | L             | H/L       | Х             |

|                                   | General                              | OFF           | ON            | ON        | ON            |

|                                   | Digital Block                        | OFF           | ON            | ON        | ON            |

| Operation Block                   | OSC, VR Block                        | OFF           | OFF           | ON*2      | OFF           |

|                                   | DD1                                  | OFF           | OFF           | ON/OFF    | OFF           |

|                                   | DD2                                  | OFF           | OFF           | ON/OFF    | OFF           |

|                                   | LDO                                  | OFF           | OFF           | ON/OFF    | OFF           |

| I <sup>2</sup> C<br>Communication | I <sup>2</sup> C communication       | Disabled      | Enabled       | Enabled   | Enabled       |

| Protection<br>Operating           | Thermal shutdown<br>Protection (TSD) | Not available | Not available | Available | *1            |

|                                   | Over Current Protection (OCP)        | Not available | Not available | Available | *1            |

<sup>\*1:</sup>This is the state after detection of ERR. It is possible to release the ERR detection mode by turning the power supply on again or turning CTLMAIN on again.

■ Priority of the external pin/I<sup>2</sup>C communication for CTL1. CTL2 and L

| CTLMAIN<br>(External pin) | CTL*<br>(External pin) | CTL*<br>(I <sup>2</sup> C communication) | Relevant CH |  |

|---------------------------|------------------------|------------------------------------------|-------------|--|

| Н                         | Н                      | Н                                        | Unavailable |  |

| Н                         | Н                      | L                                        | ON          |  |

| Н                         | L                      | Н                                        | ON          |  |

| Н                         | L                      | L                                        | OFF         |  |

| L                         | Х                      | Communication disabled                   | OFF         |  |

- \*:The I<sup>2</sup>C communication is enabled after the common block and digital block activation setting the external CTLMAIN pin to "H".

- When executing the ON/OFF control for DD1, DD2 and LDO using the external pin, don't execute the ON/OFF control using I²C. Aside from the ON/OFF control, it is possible to control everything else using I²C.

- When executing the ON/OFF control for DD1, DD2 and LDO using I<sup>2</sup>C, input "L" to the CTL\* pin (the pin is open or in the GND connection condition).

Document Number: 002-08407 Rev. \*B

<sup>\*2:</sup>When only LDO is operating, the OSC block stops (OFF) after LDO activation. Also, the VR block keeps operating (ON) after LDO activation.

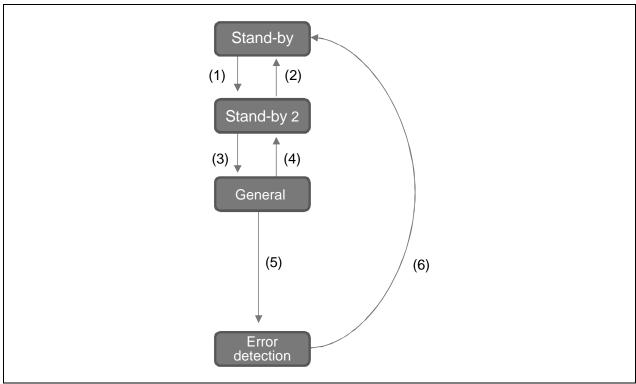

### 10. State Transition Diagram

- (1)External CTLMAIN pin "H"

- (2)External CTLMAIN pin "L"

- (3)External CTL pin "H" / I<sup>2</sup>C communication "relevant CH\_ON"

- (4)External CTL pin "L" / I2C communication "relevant CH\_OFF"

- (5)Error detection (OCP, OCP\_1ms continuation)

- (6)Turning on the power supply again (equal to or less than uvlo\_vcc reset voltage) or setting CTLMAIN to "L"

#### Notes:

- When executing the ON/OFF control for DD1, DD2 and LDO using the external pin, don't execute the ON/OFF control using I<sup>2</sup>C. Aside from the ON/OFF control, it is possible to control everything else using I<sup>2</sup>C.

- When executing the ON/OFF control for DD1, DD2 and LDO using I<sup>2</sup>C, input "L" to the CTL\* pin (the pin is open or in the GND connection condition).

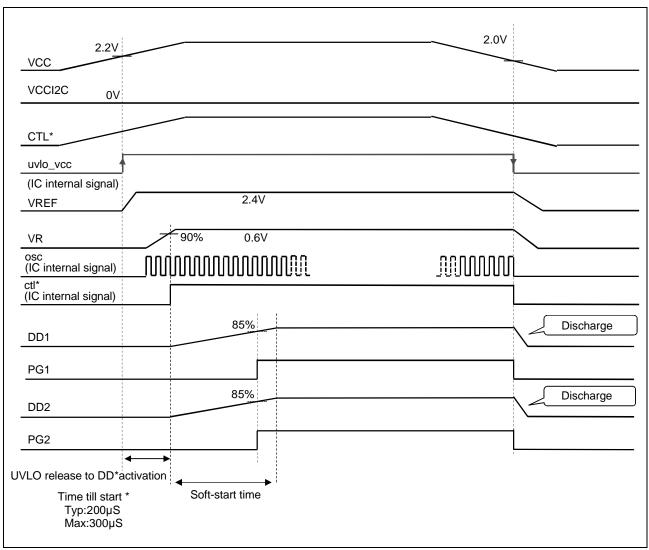

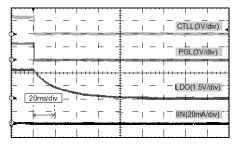

## 11. Turning On and Off Sequence (Turning On CTL\*:CTL1, CTL2, CTLMAIN=VCC Simultaneously)

\*: VREF and VR activations depend on the VREF pin capacitance and VR pin capacitance. Time in the sequence figure above is applied for the following condition.

■ VREF pin capacitance: 0.1 µF■ VR pin capacitance: 0.47 µF

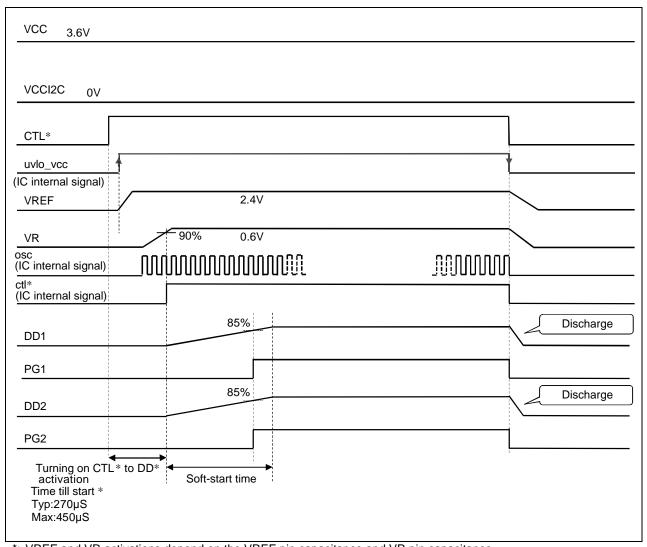

### 12. CTL\* Turning On and Off Sequence 1 (VCC → CTL\*: CTL1, CTL2, CTLMAIN)

\*: VREF and VR activations depend on the VREF pin capacitance and VR pin capacitance. Time in the sequence figure above is applied for the following condition.

■ VREF pin capacitance: 0.1 µF■ VR pin capacitance: 0.47 µF

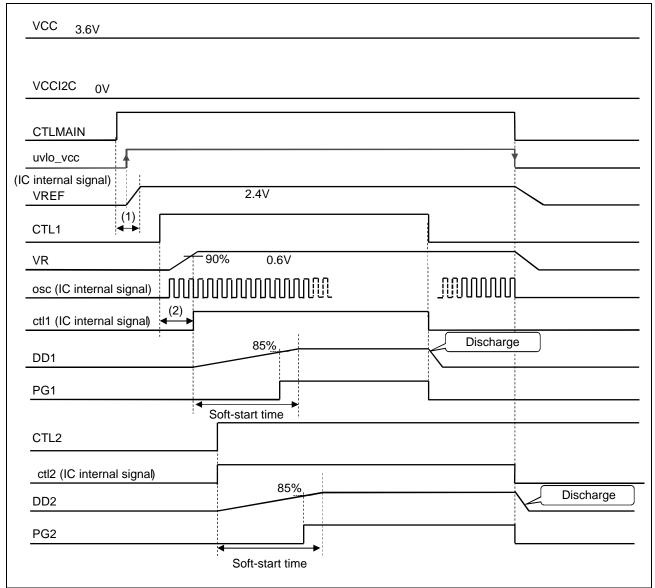

### 13. CTL\* Turning On and Off Sequence 2(VCC→CTLMAIN→CTL1→CTL2)

Time from turning on CTLMAIN to VREF activation completion (=communication enabled)\* Typ: 130 μs, Max: 200 μs

(2) Time from turning on CTL1 to ctll (IC internal signal) "H"

Typ: 150 μs, Max: 250 μs

\*: VREF and VR activations depend on the VREF pin capacitance and VR pin capacitance. Time in the sequence figure above is applied for the following condition.

■ VREF pin capacitance: 0.1 µF■ VR pin capacitance: 0.47 µF

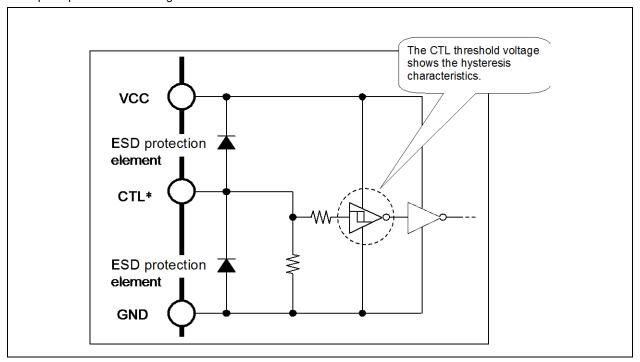

### 14. CTL\* Pin Threshold Voltage

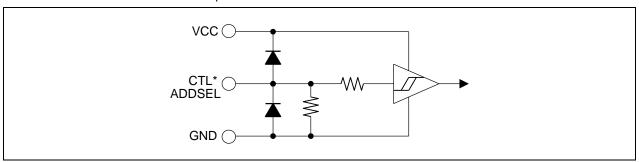

The input circuit structure for the CTL\* pin is the schmitt trigger style, and the threshold voltage shows the hysteresis characteristics when CTL\* OFF  $\rightarrow$  ON and ON  $\rightarrow$  OFF. (See "•CTL\* pin equivalent circuit diagram" below.)

Also, the threshold voltage level depends on the VCC pin voltage.

Moreover, make sure to input either the "H" level (>"VCCx0.7"V) or "L" level (<0.4 V) to the CTL\* pin when in use.

CTL\* pin equivalent circuit diagram

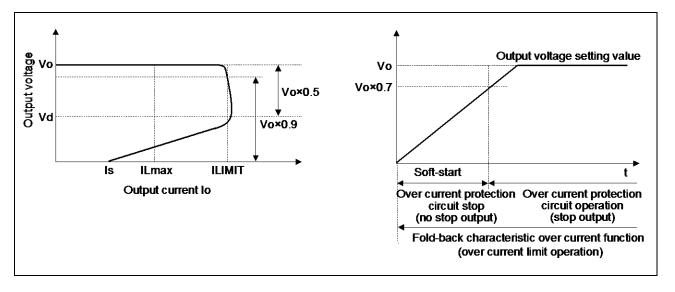

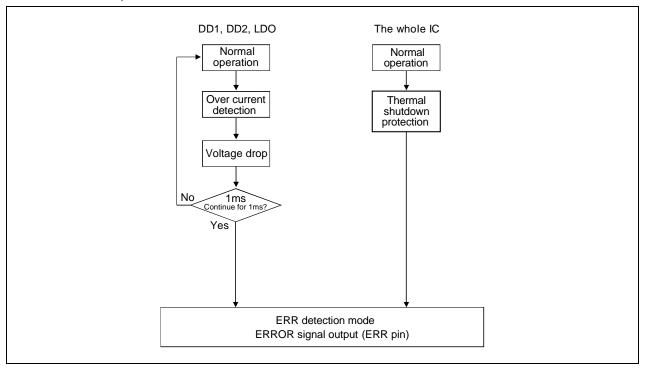

#### 15. Protection Operation Sequence

#### DD channel

The DD channel monitors the FET current peak value at any time during the operation. When the DD output becomes the over current state, the output voltage is decreased. Afterward, the timer operation is performed and the output stops after about 1ms progress.

#### LDO channel

It contains the fold-back type over current protection circuit in order to prevent destroy because of the over load and the output over current. It limits the output current and the output voltage from the peak around the over current protection value for LDO (ILIMIT) to the over current current (Is).

At this time, if the output voltage Vo gets lower than the detection voltage Vd (Vd: Vo×0.5), the timer operation starts and the output stops after about 1ms progress. Moreover, because the over current protection circuit does not operate at the soft-start (0V to Vo × 0.7), neither the output stops nor the error signal outputs. However, the fold-back type over current protection characteristic functions. The following shows the fold-back type over current protection characteristic.

#### Thermal shutdown protection

If the temperature at the junction part reaches +150 °C, the thermal shutdown protection circuit turns all channels off.

#### Error detection sequence

#### ERR detection mode release

It is necessary to turn the power supply on again, or to turn CTLMAIN on again to release the ERR detection mode.

### 16. Operation Condition, Stop Circuit and Release Condition for Protection Circuit

| Channel                | Operation whilst under protection | Over voltage protection (OCP)                                                                                                                                                                               | Under voltage lockout protection (UVLO)                                                            | Thermal shutdown protection (TSD)                                                                                                            |  |

|------------------------|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|--|

| DD1, DD2               | Discharge                         | Operating condition: After about 1ms progress in the over current condition Process during protection operation: DD1, DD2, LDO stop Recovery condition: (1) Power supply reasserted (2) CTLMAIN reasserted  | Operating condition: Input voltage drop Process during protection operation: DD1, DD2, LDO stop    | Operating condition: Chip temperature increment Process during protection operation: DD1, DD2, LDO stop Recovery condition: (1) Power supply |  |

| LDO                    | Discharge                         | Operating condition: After about 1ms progress in the over current condition Process during protection operation: DD1, DD2, LDO stop Recovery condition: (1) Power supply re-asserted (2) CTLMAIN reasserted | Recovery condition: Input voltage rise  UVLO operates only when CTLMAIN is "H" (normal operation). | control of the manner of CTL1, CTL2 or L is in the "H" state and one of CTL1, CTL2 or L is in the "H" state, TSD will operate.               |  |

| ERR output<br>(ERRpin) | -                                 | "L" output when detecting OCP at CH of DD1, DD2, or LDO                                                                                                                                                     | No change                                                                                          | "L" output when detecting TSD                                                                                                                |  |

Thermal shutdown protection (TSD) operation during over current protection timer operation

When the thermal shutdown protection (TSD) operated during the over current protection (OCP) timer operation, the thermal shutdown protection has priority.

Operation when releasing under voltage lockout protection (UVLO)

DD1, DD2 and LDO: Activation following the condition for CTL\* pin

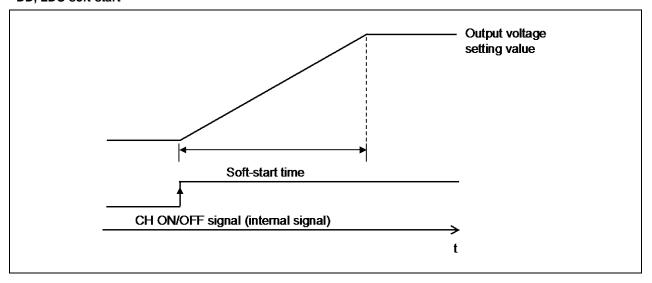

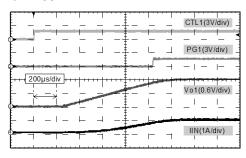

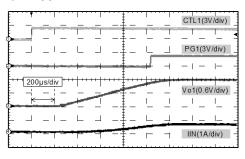

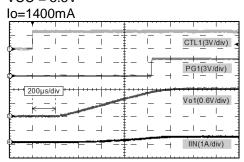

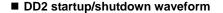

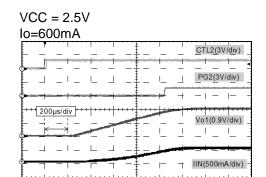

### 17. DD Soft-Start Operation

The soft-start operation for DD1, DD2 and LDO is enabled in order to prevent the rush current during the DD activation. The soft-start time can be controlled by  $l^2C$ .

Soft-start control: enabled to set at DD1, DD2 and LDO

#### DD, LDO soft-start

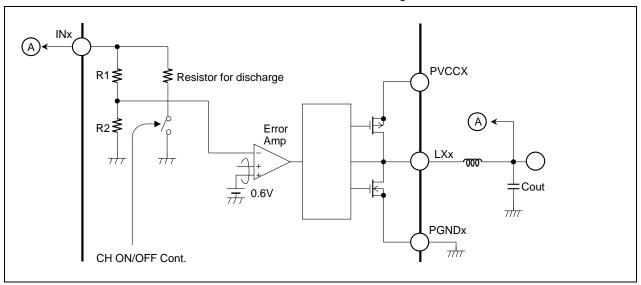

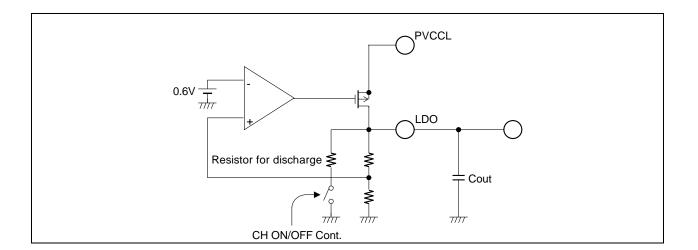

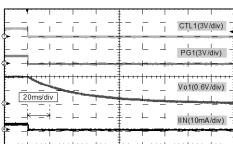

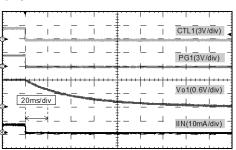

#### 18. Discharge Operation

#### **DD** channel

When executing the DD OFF operation at the CH ON/OFF signal, the DC/DC smooth capacitance charged for each output voltage is discharged using resistor for discharge which is set in the IC and the output voltage is decreased gradually. However, the discharge time changes depending on the DC/DC converter load current. The discharge time is calculated by the following equation.

Discharge time (time till the output becomes 10% without load)

$toff(s) \approx 2.3 \times R_{DIS} \times Cout(F)$

Note: See the table in ELECTRICAL CHARACTERISTICS for the discharge resistor value.

#### LDO channel

When executing the LD OFF operation at the CH ON/OFF signal, the output capacitance charged for the output voltage is discharged using resistor for discharge which is set in the IC and the output voltage is decreased gradually. However, the discharge time changes depending on the output load current. The discharge time is calculated by the following equation.

Discharge time (time till the output becomes 10 % without load).

$toff(s) \approx 2.3 \times R_{DIS} \times Cout(F)$

Note: See the table in ELECTRICAL CHARACTERISTICS for the discharge resistor value.

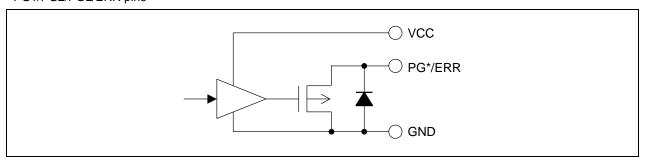

#### 19. PG1/PG2/PGL PIN and ERR PIN

The following pins for each CH POWER GOOD output are prepared.

#### PG<sub>1</sub>

It is the pin for DD1 POWER GOOD output.

When the output voltage exceeds 85 % of the setting value at the DD1 ON mode, "H" is output.

Also, when the output voltage becomes equal to or lower than 75 % of the setting value after the "H" output, "L" is output. "L" is output at the DD1 OFF mode.

#### PG<sub>2</sub>

It is the pin for DD2 POWER GOOD output.

When the output voltage exceeds 85% of the setting value at the DD2 ON mode, "H" is output.

Also, when the output voltage becomes equal to or lower than 75% of the setting value after the "H" output, "L" is output. "L" is output at the DD2 OFF mode.

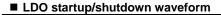

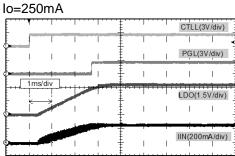

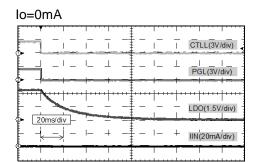

#### **PGL**

It is the pin for LDO POWER GOOD output.

When the output voltage exceeds 85 % of the setting value at the LDO ON mode, "H" is output.

Also, when the output voltage becomes equal to or lower than 75 % of the setting value after the "H" output, "L" is output. "L" is output at the LDO OFF mode.

The following pin for the error state output is prepared.

#### **ERR** pin

It is the pin for the error state output. "L" is output during the error detection mode.

The ERR detection mode is released by turning on the power supply or CTLMAIN again.

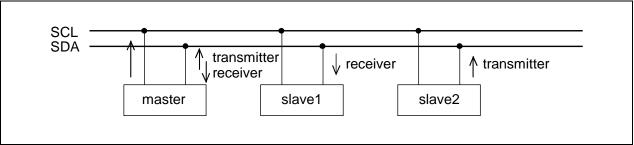

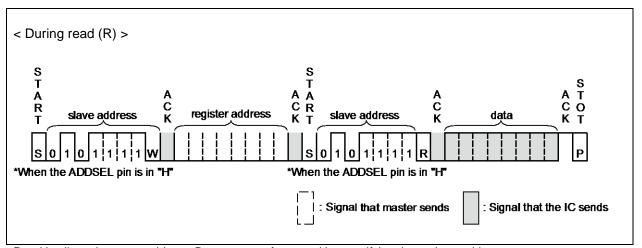

#### 20. I<sup>2</sup>C Interface

#### 1. Structure of I2C interface

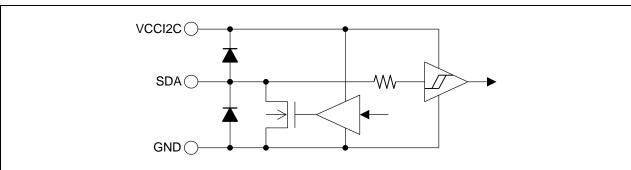

The I<sup>2</sup>C interface executes the data communication in 1 byte (8-bit) units using two signal lines (bus), a SCL (serial clock line) and a SDA (serial data line).

This bus is connected to multiple devices;

master: device to generate the clock signal and to control the data transfer (CPU and so on)

slave: device that an address is specified by a master.

This IC is set as the slave and has no function to be the master.

Each device is defined due to the communication direction as described below.

transmitter: device to send data to bus receiver: device to receive data from bus

The IC has the function both transmitter and receiver.

The IC defines the followings;

Write: data is transmitted from master and the IC receives data

Read: The IC transmits data and master receives data.

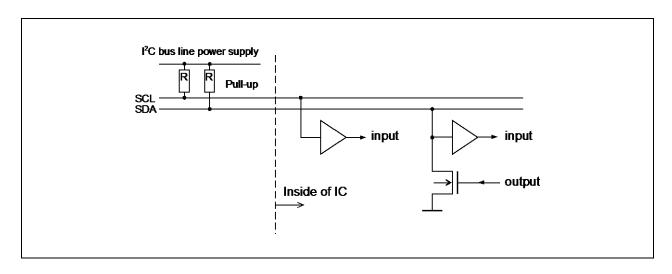

#### 2. Definition of signal lines

SCL and SDA are connected to the power supply by the pull-up resistor.

The output circuit is the open Drain output.

When a bus is not used (waiting state), the open "H" is set changing the open Drain to the OFF state.

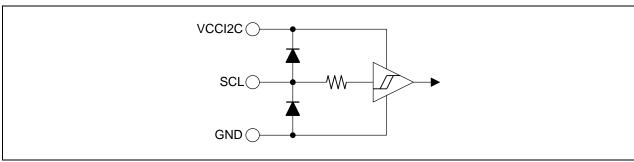

Note: SCL and SDA pins adopt a different ESD protection system from standard I<sup>2</sup>C specification because of ESD enhancement (see 2.3 I/O CIRCUIT TYPE).

When the power supply is in the bus line, don't shut off the power supply for an IC (VCCI2C).

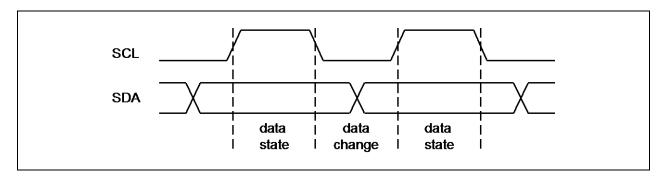

#### 3. Validity of data

Data has the following characteristics;

change when SCL is the "L" level

valid if the state is kept while SCL is the "H" level.

Moreover, the SDA signal change means the start or stop condition when SCL is the "H" level.

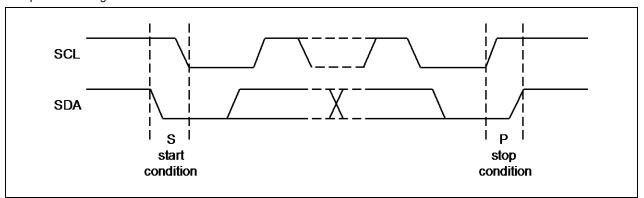

#### 4. Definition of start and stop condition

The start and stop conditions are output from the master and shows start and stop of communications to the slave.

Start : SDA changes from "H" to "L" when SCL is "H".

Stop: SDA changes from "L" to "H" when SCL is "H".

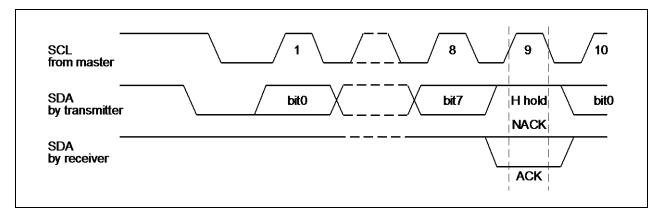

#### 5. ACK signal

This is a signal to confirm the data reception during communication.

The receiver replies the ACK signal to show the data reception to a transmitter every time 1 byte (8-bit) of data is received. The ACK signal is sent in 9clk after sending data 8-bit matching to the SCL signal that the master generates.

- A transmitter keeps SDA output "open H" in SCL9clk.

- A receiver informs the data reception situation to a transmitter outputting the followings in SCL 9 clk; when data was received: SDA output "L" (ACK) when no data was received: SDA output "open H" (NACK)

However, if the master is changed to the receiver, ACK is not replied after the last data reception because the bus keeps open stopping the data transmission to the slave transmitter. In this case, the slave transmitter opens the bus (open H) and is set to the stop condition reception waiting state from the master.

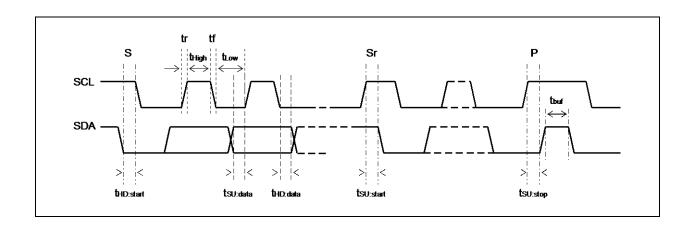

### 6. I<sup>2</sup>C Interface Input Timing

(within recommended operating conditions)

|                              |                       |            | Value |            |     |      |

|------------------------------|-----------------------|------------|-------|------------|-----|------|

| Parameter                    | Symbol                | SCL=100kHz |       | SCL=400kHz |     | Unit |

|                              |                       | Min        | Max   | Min        | Max | 1    |

| SCL clock frequency          | fSCL                  | -          | 100   | -          | 400 | kHz  |

| Start condition hold time    | t <sub>HD:start</sub> | 4.0        | -     | 0.6        | -   | μs   |

| Restart condition setup time | t <sub>SU:start</sub> | 4.7        | -     | 0.6        | -   | μs   |

| Stop condition setup time    | t <sub>SU:stop</sub>  | 4.0        | -     | 0.6        | -   | μs   |

| Stop to Start bus open time  | t <sub>buf</sub>      | 4.7        | -     | 1.3        | -   | μs   |

| SCL "L" time                 | t <sub>Low</sub>      | 4.7        | -     | 1.3        | -   | μs   |

| SCL "H" time                 | t <sub>High</sub>     | 4.0        | -     | 0.6        | -   | μs   |

| SCL/SDA rising time          | t <sub>r</sub>        | -          | 1.0   | -          | 0.3 | μs   |

| SCL/SDA falling time         | t <sub>f</sub>        | -          | 0.3   | -          | 0.3 | μs   |

| Data hold time               | t <sub>HD:data</sub>  | 0.0        | -     | 0.0        | -   | μs   |

| Data setup time              | t <sub>SU: data</sub> | 0.25       | -     | 0.10       | -   | μs   |

| SCL/SDA capacitor load       | Сь                    | -          | 400   | -          | 400 | pF   |

- VIH/VIL level reference

- Conform to I<sup>2</sup>C bus specifications

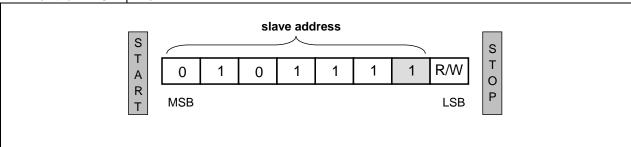

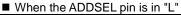

#### 7. Slave Address

This is a slave address when communicating with the I<sup>2</sup>C interface.

The slave address of this IC is set by the first seven bits as shown below.

The seventh bit follows the ADDSEL pin and "0"/"1" are variable.

The eighth bit is called the least significant bit (LSB) and determines the message direction. The bit "0" shows that information will be written from the master to the slave.

The bit "1" shows that the master reads information from the slave.

This does not support the general call address.

■ When the ADDSEL pin is in "H"

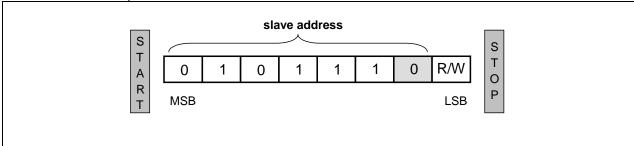

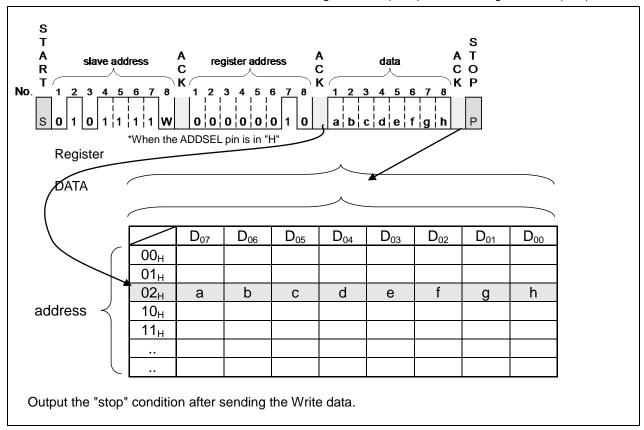

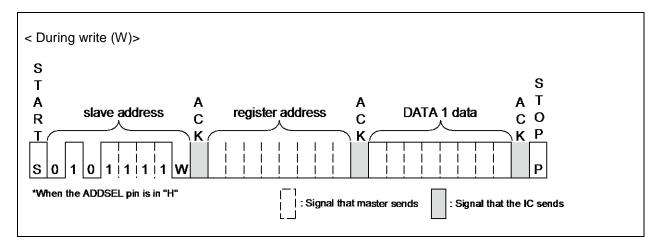

#### 8. Bit structure of data on I2C interface

(1) Writing data to register and reading data

The data line is sent/received in the order from the most significant bit (MSB) to the least significant bit (LSB).

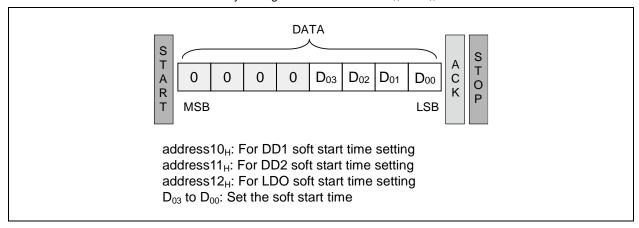

#### (2) I<sup>2</sup>C Interface Data Format

#### I<sup>2</sup>C communication

- 1. When a different slave address comes, non-matching ID is informed by not replying ACK after receiving the slave address.

- 2. All registers write to internal registers in the ACK signal after receiving the 8-bit data of each setting.

- 3. If a non-existing register address is specified, data is not written to a register.

- 4. Output the "stop" condition after sending the write data.

Write is allowed per one address. (sequential writing is not allowed.) Send register address and data as one unit.

Read is allowed per one address. Be sure to perform read by specifying the register addresses. (sequential reading is not allowed.)

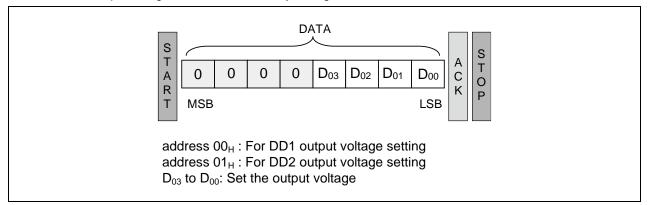

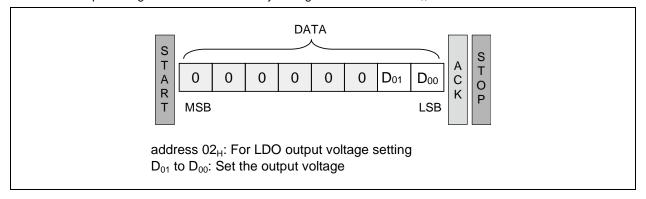

# 21. Structure of I<sup>2</sup>C Interface and Data

# Register map

|                         | address         |     | DATA |     |     |     |     |     |     | Writing                                 | Remarks |                                                                            |

|-------------------------|-----------------|-----|------|-----|-----|-----|-----|-----|-----|-----------------------------------------|---------|----------------------------------------------------------------------------|

|                         | auuress         | d07 | d06  | d05 | d04 | d03 | d02 | d01 | d00 | Default                                 | timing  | Remarks                                                                    |

|                         |                 |     |      |     |     |     |     |     |     | 00 <sub>H</sub> *                       |         |                                                                            |

|                         | 00н             | X   | X    | X   | X   | D03 | D02 | D01 | D00 | 05 <sub>H</sub> *                       | ACK     | DD1 output voltage setting                                                 |

|                         | ООН             | ^   | ^    | ^   | ^   | D03 | D02 | DOT | Doo | 0A <sub>H</sub> *                       | AOR     | DD1 output voitage setting                                                 |

| Outroot                 |                 |     |      |     |     |     |     |     |     | 0F <sub>H</sub> *                       |         |                                                                            |

| Output voltage          |                 |     |      |     |     |     |     |     |     | 00 <sub>H</sub> *                       |         |                                                                            |

| Ü                       | 01н             | Х   | X    | Х   | Х   | D03 | D02 | D01 | D00 | 03 <sub>H</sub> *                       | ACK     | DD2 output voltage setting                                                 |

|                         | 0.11            | ,,  |      | ^   |     |     |     |     |     | 06 <sub>H</sub> *                       | 7.01    | 222 carpar remage coming                                                   |

|                         |                 |     |      |     |     |     |     |     |     | 0C <sub>H</sub> *                       |         |                                                                            |

|                         | 02 <sub>H</sub> | Х   | Х    | Х   | Х   | Х   | Х   | D01 | D00 | 03 <sub>H</sub>                         | ACK     | LDO output voltage setting                                                 |

|                         | 10 <sub>H</sub> | Х   | Х    | Х   | Χ   | D03 | D02 | D01 | D00 | 01н                                     | ACK     | DD1 soft-start time setting                                                |

| Soft start              | 11 <sub>H</sub> | Х   | Х    | Х   | Х   | D03 | D02 | D01 | D00 | 01 <sub>H</sub> */<br>03 <sub>H</sub> * | ACK     | DD2 soft-start time setting                                                |

|                         | 12 <sub>H</sub> | Χ   | Х    | Χ   | Χ   | D03 | D02 | D01 | D00 | 03 <sub>H</sub>                         | ACK     | LDO soft-start time setting                                                |

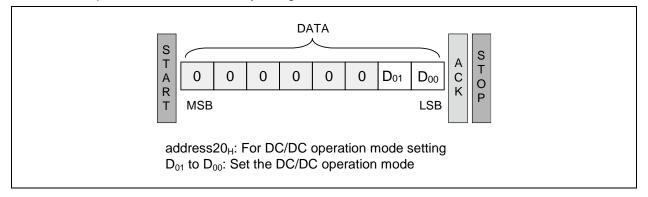

| DD<br>operation<br>mode | 20 <sub>H</sub> | Х   | Х    | Х   | Х   | Х   | X   | D01 | D00 | 00н                                     | ACK     | DD1, DD2 operation mode setting "0": Fixed PWM mode,                       |

| mode                    |                 |     |      |     |     |     |     |     |     |                                         |         | "1": PFM/PWM mode                                                          |

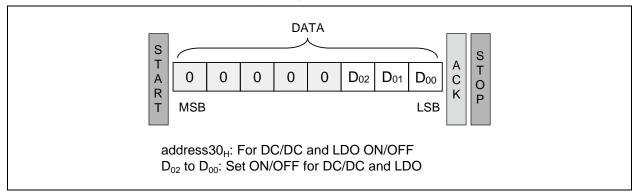

| ON/OFF                  | 30н             | X   | X    | X   | X   | Х   | D02 | D01 | D00 | 00н                                     | ACK     | DD1, DD2, LDO output<br>ON/OFF setting<br>"0":Output OFF/<br>"1":Output ON |

| For test                | FX <sub>H</sub> | -   | -    | -   | 1   | -   | -   | -   | -   | -                                       | -       | Disabled                                                                   |

<sup>\*:</sup> The value depends on the preset value.