# 2.5 V/3.3 V, 16-Bit, 2-Port Level Translating, Bus Switch

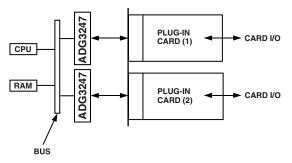

FUNCTIONAL BLOCK DIAGRAM

# ADG3247

RO

B7

**B**8

B15

### **FEATURES**

225 ps Propagation Delay through the Switch 4.5 Ω Switch Connection between Ports Data Rate 1.244 Gbps 2.5 V/3.3 V Supply Operation Selectable Level Shifting/Translation Small Signal Bandwidth 610 MHz Level Translation 3.3 V to 2.5 V 3.3 V to 1.8 V 2.5 V to 1.8 V 40-Lead 6 mm × 6 mm LFCSP and 38-Lead TSSOP Packages **APPLICATIONS** 3.3 V to 1.8 V Voltage Translation 3.3 V to 2.5 V Voltage Translation 2.5 V to 1.8 V Voltage Translation **Bus Switching Bus Isolation** Hot Plug Hot Swap

**Analog Switching Applications**

### **GENERAL DESCRIPTION**

The ADG3247 is a 2.5 V or 3.3 V 16-bit, 2-port digital switch. It is designed on Analog Devices' low voltage CMOS process, which provides low power dissipation yet gives high switching speed and very low on resistance, allowing inputs to be connected to outputs without additional propagation delay or generating additional ground bounce noise.

The ADG3247 is organized as dual 8-bit bus switches with separate bus enable  $(\overline{BEx})$  inputs. This allows the device to be used as two 8-bit digital switches or one 16-bit bus switch. These bus switches allow bidirectional signals to be switched when ON. In the OFF condition, signal levels up to the supplies are blocked.

This device is ideal for applications requiring level translation. When operated from a 3.3 V supply, level translation from 3.3 V inputs to 2.5 V outputs occurs. Similarly, if the device is operated from a 2.5 V supply and 2.5 V inputs are applied, the device will translate the outputs to 1.8 V. In addition to this, the ADG3247 has a level translating select pin ( $\overline{SEL}$ ). When  $\overline{SEL}$  is low,  $V_{CC}$  is reduced internally, allowing for level translation between 3.3 V inputs and 1.8 V outputs. This makes the device suited to applications requiring level translation between different supplies, such as converter to DSP/microcontroller interfacing.

### REV.0

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective companies.

### **PRODUCT HIGHLIGHTS**

1. 3.3 V or 2.5 V supply operation

Δ0

Δ7

BE1

Δ15

- 2. Extremely low propagation delay through switch

- 3. 4.5  $\Omega$  switches connect inputs to outputs

- 4. Level/voltage translation

- 5. 40-lead 6 mm  $\times$  6 mm LFCSP and 38-lead TSSOP packages

# ADG3247\* PRODUCT PAGE QUICK LINKS

Last Content Update: 02/23/2017

## COMPARABLE PARTS

View a parametric search of comparable parts.

### DOCUMENTATION

### Data Sheet

ADG3247: 2.5 V/3.3 V, 16 Bit, 2 Port Level Translator, Bus Switch Data Sheet

### REFERENCE MATERIALS

### **Product Selection Guide**

• Switches and Multiplexers Product Selection Guide

### **Technical Articles**

- CMOS Switches Offer High Performance in Low Power, Wideband Applications

- Data-acquisition system uses fault protection

- Enhanced Multiplexing for MEMS Optical Cross Connects

### DESIGN RESOURCES

- ADG3247 Material Declaration

- PCN-PDN Information

- Quality And Reliability

- Symbols and Footprints

## DISCUSSIONS

View all ADG3247 EngineerZone Discussions.

### SAMPLE AND BUY

Visit the product page to see pricing options.

## TECHNICAL SUPPORT

Submit a technical question or find your regional support number.

## DOCUMENT FEEDBACK

Submit feedback for this data sheet.

#

| Parameter                                                                                | Symbol                              | Conditions                                                                                                                                                                                                              | Min        | B Version<br>Typ <sup>2</sup> | Max        | Unit            |

|------------------------------------------------------------------------------------------|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-------------------------------|------------|-----------------|

| DC ELECTRICAL CHARACTERISTICS<br>Input High Voltage                                      | V <sub>INH</sub>                    | V <sub>CC</sub> = 2.7 V to 3.6 V                                                                                                                                                                                        | 2.0        |                               |            | v               |

| input Ingir ( onuge                                                                      | V <sub>INH</sub>                    | $V_{CC} = 2.3 \text{ V to } 2.7 \text{ V}$                                                                                                                                                                              | 1.7        |                               |            | v               |

| Input Low Voltage                                                                        | V <sub>INL</sub>                    | $V_{CC} = 2.7 \text{ V to } 3.6 \text{ V}$                                                                                                                                                                              |            |                               | 0.8        | V               |

|                                                                                          | V <sub>INL</sub>                    | $V_{CC} = 2.3 \text{ V}$ to 2.7 V                                                                                                                                                                                       |            |                               | 0.7        | V               |

| Input Leakage Current                                                                    | II                                  |                                                                                                                                                                                                                         |            | $\pm 0.01$                    | ±1         | μA              |

| OFF State Leakage Current                                                                | I <sub>OZ</sub>                     | $0 \le A, B \le V_{CC}$                                                                                                                                                                                                 |            | $\pm 0.01$                    | ±1         | μA              |

| ON State Leakage Current                                                                 | I <sub>OL</sub>                     | $0 \le A, B \le V_{CC}$                                                                                                                                                                                                 |            | ±0.01                         | ±1         | μA              |

| Maximum Pass Voltage                                                                     | $V_P$                               | $V_A/V_B = V_{CC} = \overline{SEL} = 3.3 \text{ V}, I_O = -5 \mu\text{A}$                                                                                                                                               | 2.0        | 2.5                           | 2.9        | V               |

|                                                                                          |                                     | $V_A/V_B = V_{CC} = \overline{SEL} = 2.5 V, I_O = -5 \mu A$<br>$V_A/V_B = V_{CC} = 3.3 V, \overline{SEL} = 0 V, I_O = -5 \mu A$                                                                                         | 1.5<br>1.5 | 1.8<br>1.8                    | 2.1<br>2.1 | V<br>V          |

| CAPACITANCE <sup>3</sup>                                                                 |                                     | · · · · · ·                                                                                                                                                                                                             |            |                               |            |                 |

| A Port Off Capacitance                                                                   | C <sub>A</sub> OFF                  | f = 1 MHz                                                                                                                                                                                                               |            | 5                             |            | pF              |

| B Port Off Capacitance                                                                   | C <sub>B</sub> OFF                  | f = 1 MHz                                                                                                                                                                                                               |            | 5                             |            | pF              |

| A, B Port On Capacitance                                                                 |                                     | f = 1 MHz                                                                                                                                                                                                               |            | 10                            |            | pF              |

| Control Input Capacitance                                                                | C <sub>IN</sub>                     | f = 1 MHz                                                                                                                                                                                                               |            | 6                             |            | pF              |

| SWITCHING CHARACTERISTICS <sup>3</sup><br>Propagation Delay A to B or B to A, $t_{PD}^4$ | t <sub>PHL</sub> , t <sub>PLH</sub> | $C_L = 50 \text{ pF}, V_{CC} = \overline{SEL} = 3 \text{ V}$                                                                                                                                                            |            |                               | 0.225      | ns              |

| Propagation Delay Matching <sup>5</sup>                                                  | PHL, PLH                            | $C_{L} = 50 \text{ pr}, V_{C} = 5LL = 5 \text{ V}$                                                                                                                                                                      |            |                               | 22.5       | ps              |

| Bus Enable Time $\overline{BEx}$ to A or $B^6$                                           | t <sub>PZH</sub> , t <sub>PZL</sub> | $V_{CC} = 3.0 \text{ V}$ to 3.6 V; $\overline{\text{SEL}} = V_{CC}$                                                                                                                                                     | 1          | 3.2                           | 4.8        | ns              |

| Bus Disable Time $\overline{BEx}$ to A or $B^6$                                          | $t_{\rm PHZ}$ , $t_{\rm PLZ}$       |                                                                                                                                                                                                                         | 1          | 3.2                           | 4.8        | ns              |

| Bus Enable Time $\overline{BEx}$ to A or $B^6$                                           | $t_{PZH}, t_{PZL}$                  | $V_{CC} = 3.0 \text{ V to } 3.6 \text{ V}; \overline{\text{SEL}} = 0 \text{ V}$                                                                                                                                         | 0.5        | 2.2                           | 3.3        | ns              |

| Bus Disable Time $\overline{\text{BEx}}$ to A or B <sup>6</sup>                          | $t_{PHZ}, t_{PLZ}$                  | $V_{CC} = 3.0 \text{ V}$ to 3.6 V; $\overline{SEL} = 0 \text{ V}$                                                                                                                                                       | 0.5        | 1.7                           | 2.9        | ns              |

| Bus Enable Time $\overline{\text{BEx}}$ to A or $B^6$                                    | t <sub>PZH</sub> , t <sub>PZL</sub> | $V_{CC} = 2.3 \text{ V to } 2.7 \text{ V}; \overline{\text{SEL}} = V_{CC}$                                                                                                                                              | 0.5        | 2.2                           | 3          | ns              |

| Bus Disable Time $\overline{\text{BEx}}$ to A or $B^6$                                   | t <sub>PHZ</sub> , t <sub>PLZ</sub> | $V_{CC}$ = 2.3 V to 2.7 V; $\overline{SEL}$ = $V_{CC}$                                                                                                                                                                  | 0.5        | 1.75                          | 2.6        | ns              |

| Maximum Data Rate                                                                        |                                     | $V_{CC} = \overline{SEL} = 3.3 \text{ V}; V_A/V_B = 2 \text{ V}$                                                                                                                                                        |            | 1.244                         |            | Gbps            |

| Channel Jitter                                                                           |                                     | $V_{CC} = \overline{SEL} = 3.3 \text{ V}; V_A/V_B = 2 \text{ V}$                                                                                                                                                        |            | 50                            |            | ps p-           |

| Operating Frequency—Bus Enable                                                           | f <sub>BEx</sub>                    |                                                                                                                                                                                                                         |            |                               | 10         | MHz             |

| DIGITAL SWITCH                                                                           |                                     |                                                                                                                                                                                                                         |            |                               | 0          | 0               |

| On Resistance                                                                            | R <sub>ON</sub>                     | $V_{CC} = 3 V, \overline{SEL} = V_{CC}, V_A = 0 V, I_{BA} = 8 mA$                                                                                                                                                       |            | 4.5                           | 8          | Ω               |

|                                                                                          |                                     | $V_{CC} = 3 V$ , $\overline{SEL} = V_{CC}$ , $V_A = 1.7 V$ , $I_{BA} = 8 mA$                                                                                                                                            |            | 15<br>5                       | 28<br>9    | $\Omega \Omega$ |

|                                                                                          |                                     | $V_{CC} = 2.3 \text{ V}, \overline{\text{SEL}} = V_{CC}, V_A = 0 \text{ V}, I_{BA} = 8 \text{ mA}$ $V_{CC} = 2.3 \text{ V}, \overline{\text{SEL}} = V_{CC}, V_A = 1 \text{ V}, I_{BA} = 8 \text{ mA}$                   |            | 11                            | 9<br>18    | $\Omega$        |

|                                                                                          |                                     | $V_{CC} = 2.5 \text{ V}, \text{ SEL} = V_{CC}, \text{ V}_A = 1 \text{ V}, \text{ I}_{BA} = 8 \text{ mA}$<br>$V_{CC} = 3 \text{ V}, \text{ SEL} = 0 \text{ V}, \text{ V}_A = 0 \text{ V}, \text{ I}_{BA} = 8 \text{ mA}$ |            | 5                             | 8          | $\Omega$        |

|                                                                                          |                                     | $V_{CC} = 3 V, SEL = 0 V, V_A = 0 V, I_{BA} = 8 mA$<br>$V_{CC} = 3 V, SEL = 0 V, V_A = 1 V, I_{BA} = 8 mA$                                                                                                              |            | 14                            | 0          | $\Omega$        |

| On Resistance Matching                                                                   | $\Delta R_{ON}$                     | $V_{CC} = 3 V, SEL = 0 V, V_A = 1 V, I_{BA} = 0 III V$<br>$V_{CC} = 3 V, SEL = V_{CC}, V_A = 0 V, I_{BA} = 8 mA$                                                                                                        |            | 0.45                          |            | Ω               |

|                                                                                          |                                     | $V_{CC} = 3 \text{ V}, \overline{\text{SEL}} = V_{CC}, V_A = 1 \text{ V}, I_{BA} = 8 \text{ mA}$                                                                                                                        |            | 0.65                          |            | Ω               |

| POWER REQUIREMENTS                                                                       |                                     |                                                                                                                                                                                                                         |            |                               |            |                 |

| V <sub>CC</sub>                                                                          |                                     |                                                                                                                                                                                                                         | 2.3        |                               | 3.6        | V               |

| Quiescent Power Supply Current                                                           | I <sub>CC</sub>                     | Digital Inputs = 0 V or $V_{CC}$ ; <u>SEL</u> = $V_{CC}$                                                                                                                                                                |            | 0.001                         | 1          | μA              |

| Increase in I <sub>CC</sub> per Input <sup>7</sup>                                       | $I_{CC} \Delta I_{CC}$              | Digital Inputs = 0 V or $V_{CC}$ ; $\overline{SEL} = 0 V$<br>$V_{CC} = 3.6 V$ , $\overline{BE}_1 = 3.0 V$ ;                                                                                                             |            | 0.65                          | 1.2        | mA              |

| merenee in the per input                                                                 |                                     | $\overline{BE}_2 = V_{CC}$ or GND; $\overline{SEL} = V_{CC}$                                                                                                                                                            |            |                               | 85         | μA              |

NOTES

<sup>1</sup>Temperature range is as follows: B Version: -40°C to +85°C.

<sup>2</sup>Typical values are at 25°C, unless otherwise stated.

<sup>3</sup>Guaranteed by design, not subject to production test.

<sup>4</sup>The digital switch contributes no propagation delay other than the RC delay of the typical R<sub>ON</sub> of the switch and the load capacitance when driven by an ideal voltage source. Since the time constant is much smaller than the rise/fall times of typical driving signals, it adds very little propagation delay to the system. Propagation delay of the digital switch when used in a system is determined by the driving circuit on the driving side of the switch and its interaction with the load on the driven side. <sup>5</sup>Propagation delay matching between channels is calculated from the on resistance matching and load capacitance of 50 pF.

<sup>6</sup>See Timing Measurement Information section.

<sup>7</sup>This current applies to the control pins ( $\overline{\text{BEx}}$ ) only. The A and B ports contribute no significant ac or dc currents as they transition.

Specifications subject to change without notice.

### **ABSOLUTE MAXIMUM RATINGS\***

$(T_A = 25^{\circ}C, \text{ unless otherwise noted.})$

| V <sub>CC</sub> to GND                  |

|-----------------------------------------|

| Digital Inputs to GND                   |

| DC Input Voltage                        |

| DC Output Current 25 mA per channel     |

| Operating Temperature Range             |

| Industrial (B Version)                  |

| Storage Temperature Range65°C to +150°C |

| Junction Temperature 150°C              |

|                                         |

| LFCSP Package                                   |

|-------------------------------------------------|

| $\theta_{IA}$ Thermal Impedance                 |

| TSSOP Package                                   |

| $\theta_{IA}$ Thermal Impedance                 |

| Lead Temperature, Soldering (10 seconds) 300°C  |

| IR Reflow, Peak Temperature (<20 seconds) 235°C |

| Lead Temperature, Soldering (10 seconds) 300°C  |

\*Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those listed in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. Only one absolute maximum rating may be applied at any one time.

### **ORDERING GUIDE**

| Model            | Temperature Range                  | Package Description                       | Package Option |

|------------------|------------------------------------|-------------------------------------------|----------------|

| ADG3247BCP       | -40°C to +85°C                     | Lead Frame Chip Scale Package (LFCSP)     | CP-40          |

| ADG3247BCP-REEL7 | $-40^{\circ}$ C to $+85^{\circ}$ C | Lead Frame Chip Scale Package (LFCSP)     | CP-40          |

| ADG3247BRU       | –40°C to +85°C                     | Thin Shrink Small Outline Package (TSSOP) | RU-38          |

| ADG3247BRU-REEL7 | -40°C to +85°C                     | Thin Shrink Small Outline Package (TSSOP) | RU-38          |

### Table I. Pin Description

| Mnemonic | Description                                         |

|----------|-----------------------------------------------------|

| BEx      | Bus Enable (Active Low)<br>Level Translation Select |

| SEL      | Level Translation Select                            |

| Ax       | Port A, Inputs or Outputs                           |

| Bx       | Port B, Inputs or Outputs                           |

### Table II. Truth Table

| BEx | <b>SEL</b> * | Function                                            |

|-----|--------------|-----------------------------------------------------|

| L   | L            | A = B, 3.3 V to 1.8 V Level Shifting                |

| L   | Η            | A = B, 3.3 V to 2.5 V/2.5 V to 1.8 V Level Shifting |

| Н   | Х            | Disconnect                                          |

|     |              |                                                     |

\* $\overline{\text{SEL}}$  = 0 only when V<sub>DD</sub> = 3.3 V ± 10%

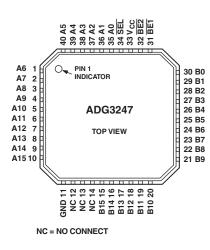

### PIN CONFIGURATION 40-Lead LFCSP and 38-Lead TSSOP

#### CAUTION .

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although the ADG3247 features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

### TERMINOLOGY

| V <sub>CC</sub>                     | Positive Power Supply Voltage.                                                                                                                                                                                                                                                                                                                                                   |

|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GND                                 | Ground (0 V) Reference.                                                                                                                                                                                                                                                                                                                                                          |

| V <sub>INH</sub>                    | Minimum Input Voltage for Logic 1.                                                                                                                                                                                                                                                                                                                                               |

| V <sub>INL</sub>                    | Maximum Input Voltage for Logic 0.                                                                                                                                                                                                                                                                                                                                               |

| $I_{I}$                             | Input Leakage Current at the Control Inputs.                                                                                                                                                                                                                                                                                                                                     |

| I <sub>OZ</sub>                     | OFF State Leakage Current. It is the maximum leakage current at the switch pin in the OFF state.                                                                                                                                                                                                                                                                                 |

| I <sub>OL</sub>                     | ON State Leakage Current. It is the maximum leakage current at the switch pin in the ON state.                                                                                                                                                                                                                                                                                   |

| $V_P$                               | Maximum Pass Voltage. The maximum pass voltage relates to the clamped output voltage of an NMOS device when the switch input voltage is equal to the supply voltage.                                                                                                                                                                                                             |

| R <sub>ON</sub>                     | Ohmic Resistance Offered by a Switch in the ON State. It is measured at a given voltage by forcing a specified amount of current through the switch.                                                                                                                                                                                                                             |

| $\Delta R_{ON}$                     | On Resistance Match between Any Two Channels, i.e., R <sub>ON</sub> Max – R <sub>ON</sub> Min.                                                                                                                                                                                                                                                                                   |

| C <sub>X</sub> OFF                  | OFF Switch Capacitance.                                                                                                                                                                                                                                                                                                                                                          |

| C <sub>X</sub> ON                   | ON Switch Capacitance.                                                                                                                                                                                                                                                                                                                                                           |

| C <sub>IN</sub>                     | Control Input Capacitance. This consists of BEx and SEL.                                                                                                                                                                                                                                                                                                                         |

| I <sub>CC</sub>                     | Quiescent Power Supply Current. It is measured when all control inputs are at a logic HIGH or LOW level and the switches are OFF.                                                                                                                                                                                                                                                |

| $\Delta I_{CC}$                     | Extra power supply current component per each $\overline{\text{BEx}}$ control input when the Input is not driven at the supplies.                                                                                                                                                                                                                                                |

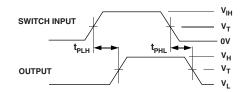

| t <sub>PLH</sub> , t <sub>PHL</sub> | Data Propagation Delay through the Switch in the ON State. Propagation delay is related to the RC time constant $R_{ON} \times C_L$ , where $C_L$ is the load capacitance.                                                                                                                                                                                                       |

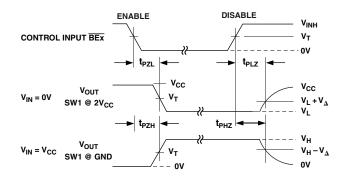

| t <sub>PZH</sub> , t <sub>PZL</sub> | Bus Enable Times. These are the times taken to cross the $V_T$ voltage at the switch output when the switch turns on in response to the control signal, $\overline{BEx}$ .                                                                                                                                                                                                       |

| t <sub>PHZ</sub> , t <sub>PLZ</sub> | Bus Disable Times. These are the times taken to place the switch in the high impedance OFF state in response to the control signal. They are measured as the time taken for the output voltage to change by $V_{\Delta}$ from the original quiescent level, with reference to the logic level transition at the control input. (Refer to Figure 3 for enable and disable times.) |

| Max Data Rate                       | Maximum Rate at which Data Can Be Passed through the Switch.                                                                                                                                                                                                                                                                                                                     |

| Channel Jitter                      | Peak-to-Peak Value of the Sum of the Deterministic and Random Jitter of the Switch Channel.                                                                                                                                                                                                                                                                                      |

| $f_{\overline{BEx}}$                | Operating Frequency of Bus Enable. This is the maximum frequency at which bus enable $(\overline{BEx})$ can be toggled.                                                                                                                                                                                                                                                          |

# **Typical Performance Characteristics–ADG3247**

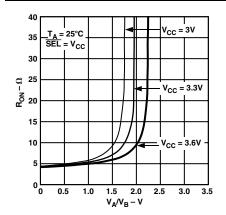

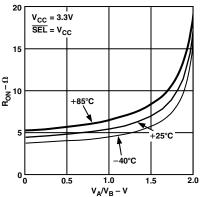

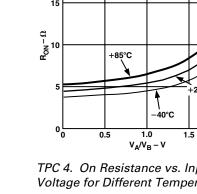

TPC 1. On Resistance vs. Input Voltage

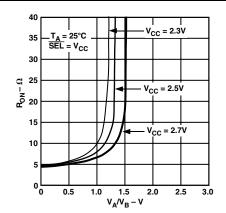

TPC 2. On Resistance vs. Input Voltage

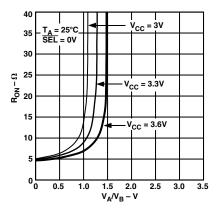

TPC 3. On Resistance vs. Input Voltage

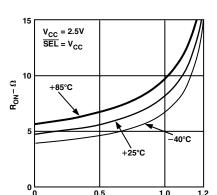

TPC 4. On Resistance vs. Input Voltage for Different Temperatures

TPC 5. On Resistance vs. Input Voltage for Different Temperatures

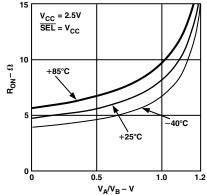

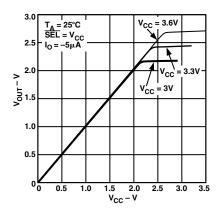

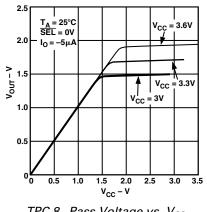

TPC 6. Pass Voltage vs. V<sub>CC</sub>

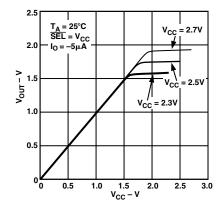

TPC 7. Pass Voltage vs. V<sub>CC</sub>

TPC 8. Pass Voltage vs. V<sub>CC</sub>

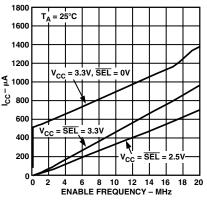

TPC 9. I<sub>CC</sub> vs. Enable Frequency

REV.0

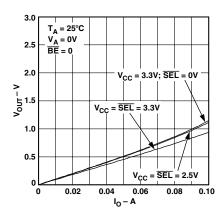

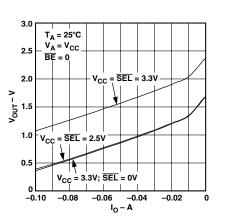

TPC 10. Output Low Characteristic

TPC 11. Output High Characteristic

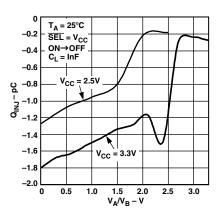

*TPC 12. Charge Injection vs. Source Voltage*

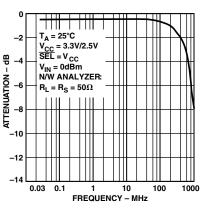

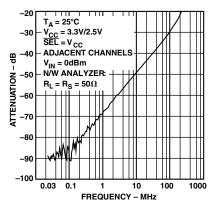

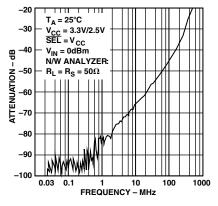

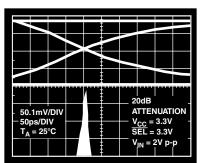

TPC 13. Bandwidth vs. Frequency

TPC 14. Crosstalk vs. Frequency

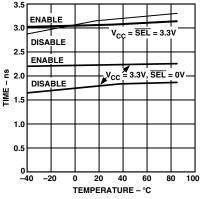

TPC 16. Enable/Disable Time vs. Temperature

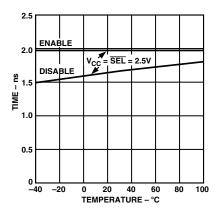

TPC 17. Enable/Disable Time vs. Temperature

TPC 15. Off Isolation vs. Frequency

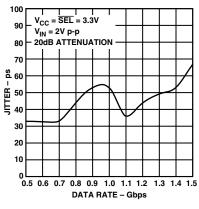

TPC 18. Jitter vs. Data Rate; PRBS 31

Downloaded from Arrow.com.

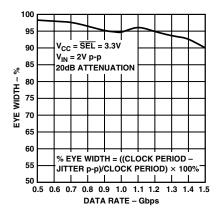

*TPC 19. Eye Width vs. Data Rate; PRBS 31*

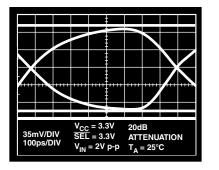

*TPC 20. Eye Pattern; 1.244 Gbps, V<sub>CC</sub> = 3.3 V, PRBS 31*

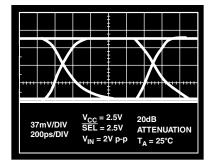

TPC 21. Eye Pattern; 1 Gbps, V<sub>CC</sub> = 2.5 V, PRBS 31

TPC 22. Jitter @ 1.244 Gbps, PRBS 31

### TIMING MEASUREMENT INFORMATION

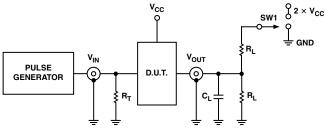

For the following load circuit and waveforms, the notation that is used is  $V_{IN}$  and  $V_{OUT}$  where

$V_{IN} = V_A$  and  $V_{OUT} = V_B$  or  $V_{IN} = V_B$  and  $V_{OUT} = V_A$

Figure 2. Propagation Delay

NOTES PULSE GENERATOR FOR ALL PULSES:  $t_R^{} \leq$  2.5ns,  $t_F^{} \leq$  2.5ns, ...  $\label{eq:FREQUENCY} \mathsf{FREQUENCY} \leq \mathsf{10MHz}.$

CL INCLUDES BOARD, STRAY, AND LOAD CAPACITANCES

RT IS THE TERMINATION RESISTOR, SHOULD BE EQUAL TO Z<sub>OUT</sub> OF THE PULSE GENERATOR.

Figure 1. Load Circuit

### **Test Conditions**

| Symbol         | $V_{CC} = 3.3 \text{ V} \pm 0.3 \text{ V} (\overline{\text{SEL}} = V_{CC})$ | $V_{CC} = 2.5 V \pm 0.2 V (\overline{SEL} = V_{CC})$ | $V_{\rm CC} = 3.3 \text{ V} \pm 0.3 \text{ V} (\overline{\text{SEL}} = 0 \text{ V})$ | Unit |

|----------------|-----------------------------------------------------------------------------|------------------------------------------------------|--------------------------------------------------------------------------------------|------|

| R <sub>L</sub> | 500                                                                         | 500                                                  | 500                                                                                  | Ω    |

| $V_{\Delta}$   | 300                                                                         | 150                                                  | 150                                                                                  | mV   |

| CL             | 50                                                                          | 30                                                   | 30                                                                                   | pF   |

| V <sub>T</sub> | 1.5                                                                         | 0.9                                                  | 0.9                                                                                  | V    |

Figure 3. Enable and Disable Times

### Table III. Switch Position

| TEST                                | <b>S</b> 1        |

|-------------------------------------|-------------------|

| t <sub>PLZ</sub> , t <sub>PZL</sub> | $2 \times V_{CC}$ |

| t <sub>PHZ</sub> , t <sub>PZH</sub> | GND               |

### **BUS SWITCH APPLICATIONS**

#### Mixed Voltage Operation, Level Translation

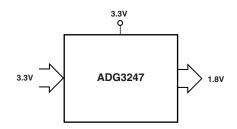

Bus switches can be used to provide an ideal solution for interfacing between mixed voltage systems. The ADG3247 is suitable for applications where voltage translation from 3.3 V technology to a lower voltage technology is needed. This device can translate from 3.3 V to 1.8 V, from 2.5 V to 1.8 V, or bidirectionally from 3.3 V directly to 2.5 V.

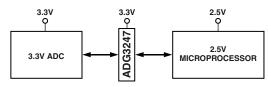

Figure 4 shows a block diagram of a typical application in which a user needs to interface between a 3.3 V ADC and a 2.5 V microprocessor. The microprocessor may not have 3.3 V tolerant inputs; therefore placing the ADG3247 between the two devices allows the devices to communicate easily. The bus switch directly connects the two blocks, thus introducing minimal propagation delay, timing skew, or noise.

Figure 4. Level Translation between a 3.3 V ADC and a 2.5 V Microprocessor

### 3.3 V to 2.5 V Translation

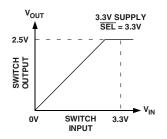

When  $V_{CC}$  is 3.3 V (SEL =  $V_{CC}$ ) and the input signal range is 0 V to  $V_{CC}$ , the maximum output signal will be clamped to within a voltage threshold below the  $V_{CC}$  supply.

Figure 5. 3.3 V to 2.5 V Voltage Translation,  $\overline{SEL} = V_{CC}$

In this case, the output will be limited to 2.5 V, as shown in Figure 6.

Figure 6. 3.3 V to 2.5 V Voltage Translation,  $\overline{SEL} = V_{CC}$

This device can be used for translation from 2.5 V to 3.3 V devices and also between two 3.3 V devices.

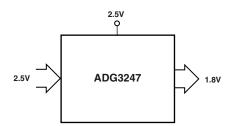

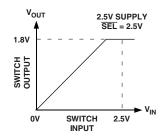

#### 2.5 V to 1.8 V Translation

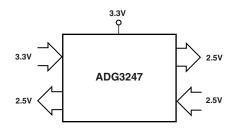

When  $V_{CC}$  is 2.5 V (SEL =  $V_{CC}$ ) and the input signal range is 0 V to  $V_{CC}$ , the maximum output signal will, as before, be clamped to within a voltage threshold below the  $V_{CC}$  supply.

Figure 7. 2.5 V to 1.8 V Voltage Translation,  $\overline{SEL} = V_{CC}$

In this case, the output will be limited to approximately 1.8 V, as shown in Figure 7.

Figure 8. 2.5 V to 1.8 V Voltage Translation,  $\overline{SEL} = V_{CC}$

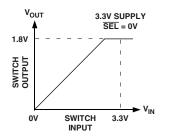

### 3.3 V to 1.8 V Translation

The ADG3247 offers the option of interfacing between a 3.3 V device and a 1.8 V device. This is possible through use of the SEL pin.

$\overline{\text{SEL}}$  pin: An active low control pin.  $\overline{\text{SEL}}$  activates internal circuitry in the ADG3247 that allows voltage translation between 3.3 V devices and 1.8 V devices.

Figure 9. 3.3 V to 1.8 V Voltage Translation,  $\overline{SEL} = 0$  V

When  $V_{CC}$  is 3.3 V and the input signal range is 0 V to  $V_{CC}$ , the maximum output signal will be clamped to 1.8 V, as shown in Figure 9. To do this, the SEL pin must be tied to Logic 0. If SEL is unused, it should be tied directly to  $V_{CC}$ .

Figure 10. 3.3 V to 1.8 V Voltage Translation, SEL = 0 V

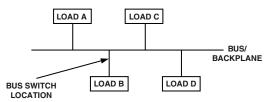

### **Bus Isolation**

A common requirement of bus architectures is low capacitance loading of the bus. Such systems require bus bridge devices that extend the number of loads on the bus without exceeding the specifications. Because the ADG3247 is designed specifically for applications that do not need drive yet require simple logic functions, it solves this requirement. The device isolates access to the bus, thus minimizing capacitance loading.

Figure 11. Location of Bus Switched in a Bus Isolation Application

### Hot Plug and Hot Swap Isolation

The ADG3247 is suitable for hot swap and hot plug applications. The output signal of the ADG3247 is limited to a voltage that is below the  $V_{CC}$  supply, as shown in Figures 6, 8, and 10. Therefore the switch acts like a buffer to take the impact from hot insertion, protecting vital and expensive chipsets from damage.

In hot-plug applications, the system cannot be shutdown when new hardware is being added. To overcome this, a bus switch can be positioned on the backplane between the bus devices and the hot plug connectors. The bus switch is turned off during hot plug. Figure 12 shows a typical example of this type of application.

Figure 12. ADG3247 in a Hot Plug Application

There are many systems that require the ability to handle hot swapping, such as docking stations, PCI boards for servers, and line cards for telecommunications switches. If the bus can be isolated prior to insertion or removal, then there is more control over the hot swap event. This isolation can be achieved using a bus switch. The bus switches are positioned on the hot swap card between the connector and the devices. During hot swap, the ground pin of the hot swap card must connect to the ground pin of the back plane before any other signal or power pins.

### Analog Switching

Bus switches can be used in many analog switching applications; for example, video graphics. Bus switches can have lower on resistance, smaller ON and OFF channel capacitance and thus improved frequency performance than their analog counterparts. The bus switch channel itself consisting solely of an NMOS switch limits the operating voltage (see TPC 1 for a typical plot), but in many cases, this does not present an issue.

### High Impedance during Power-Up/Power-Down

To ensure the high impedance state during power-up or powerdown, BEx should be tied to  $V_{CC}$  through a pull-up resistor; the minimum value of the resistor is determined by the currentsinking capability of the driver.

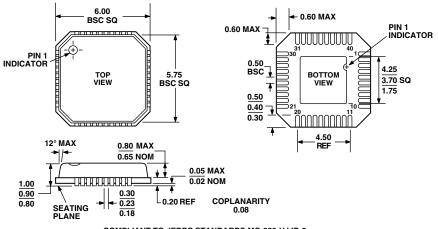

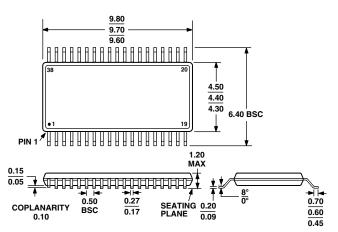

### PACKAGE AND PINOUT

The ADG3247 is packaged in both a small 38-lead TSSOP or a tiny 40-lead LFCSP package. The area of the TSSOP option is 62.7 mm<sup>2</sup>, while the area of the LFCSP option is 36 mm<sup>2</sup>. This leads to a 43% savings in board space when using the LFCSP package compared with the TSSOP package. This makes the LFCSP option an excellent choice for space-constrained applications.

The ADG3247 in the TSSOP package offers a flowthrough pinout. The term flowthrough signifies that all the inputs are on opposite sides from the outputs. A flowthrough pinout simplifies the PCB layout.

### **OUTLINE DIMENSIONS**

### 40-Lead Lead Frame Chip Scale Package [LFCSP] (CP-40)

Dimensions shown in millimeters

### 38-Lead Thin Shrink Small Outline Package [TSSOP] (RU-38)

Dimensions shown in millimeters

COMPLIANT TO JEDEC STANDARDS MS-153BD-1

C03013-0-5/03(0)