# Dual Low Power Operational Amplifier, Single or Dual Supply

# **OP221**

#### **FEATURES**

Excellent TCV<sub>OS</sub> Match, 2  $\mu$ V/°C Max Low Input Offset Voltage, 150  $\mu$ V Max Low Supply Current, 550  $\mu$ A Max Single Supply Operation, 5 V to 30 V Low Input Offset Voltage Drift, 0.75  $\mu$ V/°C High Open-Loop Gain, 1500 V/mV Min High PSRR, 3  $\mu$ V/V Wide Common-Mode Voltage Range, V- to within 1.5 V of V+ Pin Compatible with 1458, LM158, LM2904 Available in Die Form

#### **GENERAL DESCRIPTION**

The OP221 is a monolithic dual operational amplifier that can be used either in single or dual supply operation. The wide supply voltage range, wide input voltage range, and low supply current drain of the OP221 make it well-suited for operation from batteries or unregulated power supplies.

The excellent specifications of the individual amplifiers combined with the tight matching and temperature tracking between channels

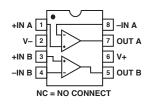

### **PIN CONNECTIONS**

#### 8-Lead SOIC (S-Suffix)

provide high performance in instrumentation amplifier designs. The individual amplifiers feature very low input offset voltage, low offset voltage drift, low noise voltage, and low bias current. They are fully compensated and protected.

Matching between channels is provided on all critical parameters including input offset voltage, tracking of offset voltage vs. temperature, non-inverting bias currents, and common-mode rejection.

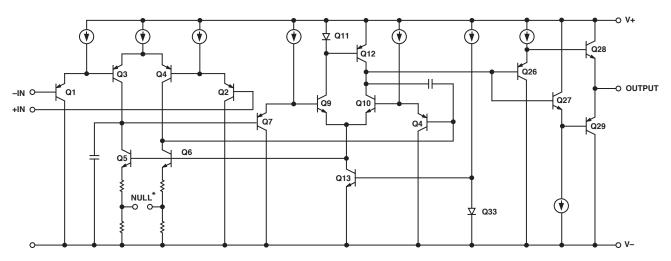

#### SIMPLIFIED SCHEMATIC

\*ACCESSIBLE IN CHIP FORM ONLY

### REV. C

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781/329-4700 www.analog.com Fax: 781/326-8703 © Analog Devices, Inc., 2002

# **OP221\* PRODUCT PAGE QUICK LINKS**

Last Content Update: 12/18/2017

## COMPARABLE PARTS

View a parametric search of comparable parts.

### EVALUATION KITS

• EVAL-OPAMP-2 Evaluation Board

### **DOCUMENTATION**

### **Application Notes**

- AN-112: Single Resistor Controls Wien Bridge Oscillator Frequency

- AN-21: 4-20 mA Digital-to-Process Current Transmitter

### Data Sheet

OP221: Dual Low Power Operational Amplifier, Single or Dual Supply Data Sheet

## TOOLS AND SIMULATIONS $\square$

OP221 SPICE Macro Models

### DESIGN RESOURCES

- OP221 Material Declaration

- PCN-PDN Information

- Quality And Reliability

- Symbols and Footprints

## DISCUSSIONS

View all OP221 EngineerZone Discussions.

### SAMPLE AND BUY

Visit the product page to see pricing options.

### TECHNICAL SUPPORT

Submit a technical question or find your regional support number.

## DOCUMENT FEEDBACK

Submit feedback for this data sheet.

# $OP221-SPECIFICATIONS (Electrical Characteristics at V_{s} = \pm 2.5 V to \pm 15 V, T_{A} = 25^{\circ}C, unless otherwise noted.)$

|                                     |                 | OP221G                                                                                                                                        |                   |            |            |      |

|-------------------------------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------|-------------------|------------|------------|------|

| Parameter                           | Symbol          | Conditions                                                                                                                                    | Min               | Тур        | Max        | Unit |

| Input Offset Voltage                | V <sub>OS</sub> |                                                                                                                                               |                   | 250        | 500        | μV   |

| Input Offset Current                | Ios             | $V_{CM} = 0$                                                                                                                                  |                   | 1.5        | 7          | nA   |

| Input Bias Current                  | I <sub>B</sub>  | $V_{CM} = 0$                                                                                                                                  |                   | 70         | 120        | nA   |

| Input Voltage Range                 | IVR             | $V+ = 5 V, V- = 0 V^1$<br>$V_S = \pm 15 V$                                                                                                    | 0/3.5<br>-15/13.5 |            |            | V    |

| Common-Mode<br>Rejection Ratio      | CMRR            | $\begin{array}{c} V+=-5 \ V, \ V-=0 \ V \\ 0 \ V \leq V_{CM} \leq 3.5 \ V \\ V_S=\pm 15 \ V \\ -15 \ V \leq V_{CM} \leq 13.5 \ V \end{array}$ | 75<br>80          | 85<br>90   |            | dB   |

| Power Supply<br>Rejection Ratio     | PSRR            | $V_{S} = \pm 2.5 V \text{ to } \pm 15 V$<br>V- = 0 V, V+ = 5 V to 30 V                                                                        |                   | 32<br>57   | 100<br>180 | μV/V |

| Large-Signal<br>Voltage Gain        | Avo             | $V_{\rm S} = \pm 15 \text{ V}, R_{\rm L} = 10 \text{ k}\Omega$ $V_{\rm O} = \pm 10 \text{ V}$                                                 | 800               |            |            | V/mV |

| Output Voltage<br>Swing             | Vo              | V+ = 5 V, V- = 0 V<br>$R_{L} = 10 k\Omega$<br>$V_{S} = 15 V, R_{L} = 10 k\Omega$                                                              | 0.8/4<br>±13.5    |            |            | V    |

| Slew Rate                           | SR              | $R_{\rm L} = 10 \ k\Omega^2$                                                                                                                  | 0.2               | 0.3        |            | V/µS |

| Bandwidth                           | BW              |                                                                                                                                               |                   | 600        |            | kHz  |

| Supply Current<br>(Both Amplifiers) | I <sub>SY</sub> | $V_S = \pm 2.5 V$ , No Load $V_S = \pm 15 V$ , No Load                                                                                        |                   | 550<br>850 | 650<br>900 | μΑ   |

|                                                    |                   | OP221G                                                                                                     |                   |            |             |       |

|----------------------------------------------------|-------------------|------------------------------------------------------------------------------------------------------------|-------------------|------------|-------------|-------|

| Parameter                                          | Symbol            | Conditions                                                                                                 | Min               | Тур        | Max         | Unit  |

| Average Input<br>Offset Voltage Drift <sup>1</sup> | TCV <sub>OS</sub> |                                                                                                            |                   | 2          | 3           | μV/°C |

| Input Offset Voltage                               | Vos               |                                                                                                            |                   | 400        | 700         | μV    |

| Input Offset Current                               | I <sub>OS</sub>   | $V_{CM} = 0$                                                                                               |                   | 2          | 10          | nA    |

| Input Bias Current                                 | I <sub>B</sub>    | $V_{CM} = 0$                                                                                               |                   | 80         | 140         | nA    |

| Input Voltage Range                                | IVR               | $V+ = 5 V, V- = 0 V^2$<br>$V_S = \pm 15 V$                                                                 | 0/3.2<br>-15/13.2 |            |             | V     |

| Common-Mode<br>Rejection Ratio                     | CMRR              | V + = -5 V, V - = 0 V<br>$0 V \le V_{CM} \le 3.5 V$<br>$V_{S} = \pm 15 V$<br>$-15 V \le V_{CM} \le 13.5 V$ | 70<br>75          | 80<br>85   |             | dB    |

| Power Supply<br>Rejection Ratio                    | PSRR              | $V_{S} = \pm 2.5 V \text{ to } \pm 15 V$<br>V- = 0 V, V+ = 5 V to 30 V                                     |                   | 57<br>100  | 180<br>320  | μV/V  |

| Large-Signal<br>Voltage Gain                       | A <sub>VO</sub>   | $V_{S} = \pm 15 \text{ V}, R_{L} = 10 \text{ k}\Omega$ $V_{O} = \pm 10 \text{ V}$                          | 600               |            |             | V/mV  |

| Output Voltage<br>Swing                            | Vo                | $V+ = 5 V, V- = 0 V R_L = 10 k\Omega V_S = 15 V, R_L = 10 k\Omega$                                         | 0.9/3.7<br>13.2   |            |             | V     |

| Supply Current<br>(Both Amplifiers)                | I <sub>SY</sub>   | $V_S = \pm 2.5 V$ , No Load<br>$V_S = \pm 15 V$ , No Load                                                  |                   | 600<br>950 | 750<br>1000 | μΑ    |

# **SPECIFICATIONS** (Electrical Characteristics at $V_s = \pm 2.5$ V to $\pm 15$ V, $-40^{\circ}C \le T_A \le +85^{\circ}C$ , unless otherwise noted.)

NOTES

<sup>1</sup>Sample tested.

<sup>2</sup>Guaranteed by CMRR test limits.

### Matching Characteristics at $V_s = \pm 15$ V, $T_A = 25^{\circ}$ C, unless otherwise noted.

|                                                       |                   | OP221G                                              |     |     |     |      |  |

|-------------------------------------------------------|-------------------|-----------------------------------------------------|-----|-----|-----|------|--|

| Parameter                                             | Symbol            | Conditions                                          | Min | Тур | Max | Unit |  |

| Input Offset<br>Voltage Match                         | $\Delta V_{OS}$   |                                                     |     | 250 | 600 | μV   |  |

| Average Noninverting<br>Bias Current                  | I <sub>B</sub> +  |                                                     |     |     | 120 | nA   |  |

| Noninverting Input<br>Offset Current                  | I <sub>OS</sub> + |                                                     |     | 4   | 10  | nA   |  |

| Common-Mode<br>Rejection Ratio<br>Match <sup>1</sup>  | ΔCMRR             | $V_{CM}$ = -15 V to 13.5 V                          | 72  |     |     | dB   |  |

| Power Supply<br>Rejection Ratio<br>Match <sup>2</sup> | ΔPSRR             | $V_{\rm S} = \pm 2.5 \text{ V to} \pm 15 \text{ V}$ |     |     | 140 | μV/V |  |

NOTES

$^{1}\Delta$ CMRR is 20 log<sub>10</sub> V<sub>CM</sub>/ $\Delta$ CME, where V<sub>CM</sub> is the voltage applied to both noninverting inputs and  $\Delta$ CME is the difference in common-mode input-referred error.  $^{2}\Delta$ PSRR is: Input-Referred Differential Error

$\Delta V_{S}$

#

|                                                       |                    |                            |     | OP221G |     |      |

|-------------------------------------------------------|--------------------|----------------------------|-----|--------|-----|------|

| Parameter                                             | Symbol             | Conditions                 | Min | Тур    | Max | Unit |

| Input Offset<br>Voltage Match                         | $\Delta V_{OS}$    |                            |     | 400    | 800 | μV   |

| Average Noninverting<br>Bias Current                  | I <sub>B</sub> +   | $V_{CM} = 0$               |     |        | 140 | nA   |

| Input Offset<br>Voltage Tracking                      | ICΔV <sub>OS</sub> |                            |     | 3      | 5   | μV°C |

| Noninverting Input<br>Offset Current                  | I <sub>OS</sub> +  | $V_{CM} = 0$               |     | 6      | 12  | nA   |

| Common-Mode<br>Rejection Ratio<br>Match <sup>1</sup>  | ΔCMRR              | $V_{CM}$ = -15 V to 13.2 V | 72  | 80     |     | dB   |

| Power Supply<br>Rejection Ratio<br>Match <sup>2</sup> | ΔPSRR              |                            |     | 140    |     | μV/V |

NOTES <sup>1</sup> $\Delta$ CMRR is 20 log<sub>10</sub> V<sub>CM</sub>/ $\Delta$ CME, where V<sub>CM</sub> is the voltage applied to both noninverting inputs and  $\Delta$ CME is the difference in common-mode input-referred error. <sup>2</sup> $\Delta$ PSRR is: Input-Referred Differential Error  $\Delta$ V<sub>S</sub>

#### **ABSOLUTE MAXIMUM RATINGS (Note 1)**

| Supply Voltage±18 V                                                            |

|--------------------------------------------------------------------------------|

| Differential Input Voltage                                                     |

| Input Voltage Supply Voltage                                                   |

| Output Short-Circuit Duration Indefinite                                       |

| Storage Temperature Range65°C to +150°C                                        |

| Operating Temperature Range                                                    |

| OP221G40°C to +85°C                                                            |

| Lead Temperature (Soldering 60 sec)                                            |

| Junction Temperature (T <sub>J</sub> ) $\dots -65^{\circ}C$ to $+150^{\circ}C$ |

|                                                                                |

| Package Type   | $\theta_{JA}$ (Note 2) | θ <sub>JC</sub> | Unit |  |

|----------------|------------------------|-----------------|------|--|

| 8-Lead SOIC(S) | 158                    | 43              | °C/W |  |

NOTES

<sup>1</sup>Absolute maximum ratings apply to both DICE and packaged parts, unless otherwise noted.

$^2\theta_{JA}$  is specified for device soldered to printed circuit board for SOIC package.

| ORDERING ( | JUIDE |

|------------|-------|

|------------|-------|

| $T_{A} = +25^{\circ}C$ $V_{OS} MAX$ ( $\mu$ V) | Plastic<br>8-Lead | Operating<br>Temperature<br>Range | Package<br>Options |

|------------------------------------------------|-------------------|-----------------------------------|--------------------|

| 150                                            |                   |                                   |                    |

| 150                                            |                   |                                   |                    |

| 300                                            |                   |                                   |                    |

| 500                                            |                   |                                   |                    |

| 500                                            |                   |                                   |                    |

| 500                                            | OP221GS           | XIND                              | RN-8               |

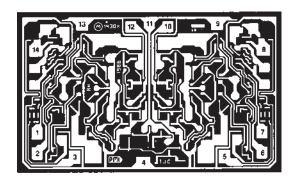

1. INVERTING INPUT (A) 2. NONINVERTING INPUT (A) 3. BALANCE (A) 4. V-5. BALANCE (B) 6. INVERTING INPUT (B) 7. NONINVERTING INPUT (B) 8. BALANCE (B) 9. V+ 10. OUT (B) 11. V+ 12. OUT (A) 13. V+ 14. BALANCE (A)

DIE SIZE 0.097 X 0.063 INCH, 6111 SQ. MILS (2.464 X 1.600 MM, 3.94 SQ. MM)

NOTE: ALL V+ PADS ARE INTERNALLY CONNECTED.

Figure 1. Dice Characteristics

### CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although the OP221 features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high-energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

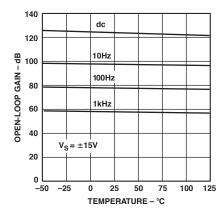

# **OP221–Typical Perfomance Characteristics**

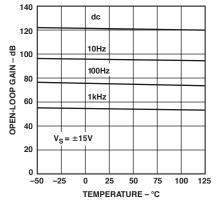

TPC 1. Open-Loop Gain at  $\pm 15 V vs$ . Temperature

TPC 2. Open-Loop Gain at ± 5 V vs. Temperature

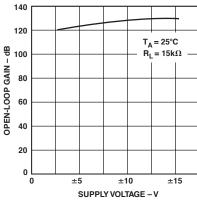

TPC 3. Open-Loop Gain at vs. Supply Voltage

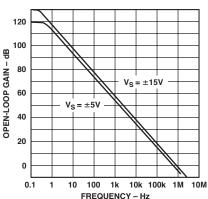

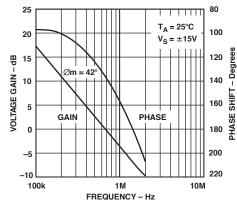

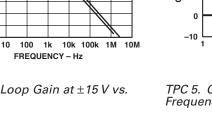

TPC 4. Open-Loop Gain at  $\pm 15 V vs$ . Frequency

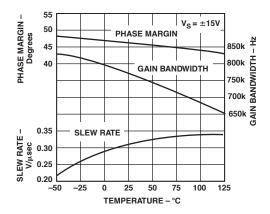

TPC 7. Phase Margin, Gain Bandwidth, and Slew Rate vs. Temperature

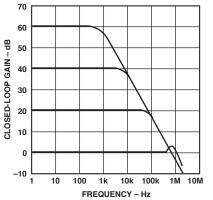

TPC 5. Closed-Loop Gain vs. Frequency

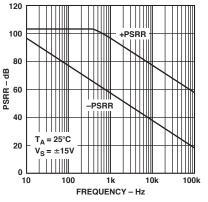

TPC 8. PSRR vs. Frequency

TPC 6. Gain and Phase Shift vs. Frequency

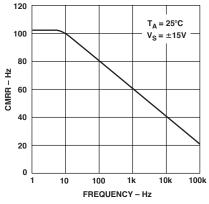

TPC 9. CMRR vs. Frequency

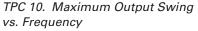

TPC 13. Voltage Noise Density vs. Frequency

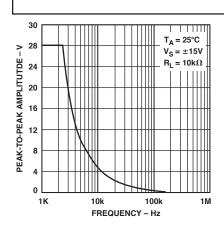

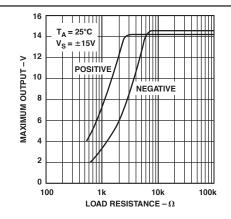

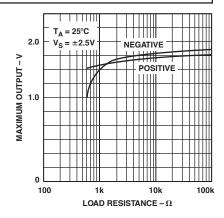

*TPC 11. Maximum Output Voltage vs. Load Resistance*

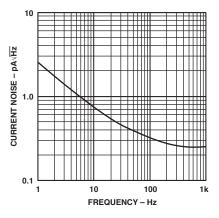

TPC 13. Current Noise Density vs. Frequency

TPC 12. Maximum Output Voltage vs. Load Resistance

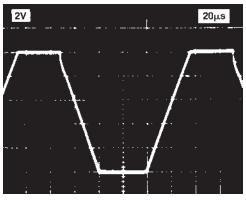

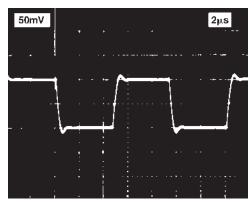

Figure 2a. Noninverting Step Response

Figure 2b. Noninverting Step Response

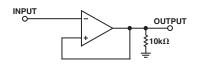

Figure 4. Noninverting Test Circuit

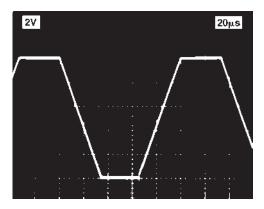

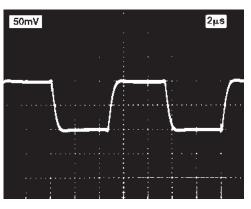

Figure 3a. Inverting Step Response

Figure 3b. Inverting Step Response

Figure 5. Inverting Test Circuit

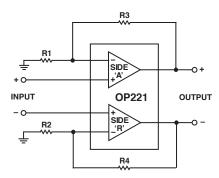

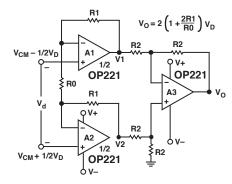

### SPECIAL NOTES ON THE APPLICATION OF DUAL MATCHED OPERATIONAL AMPLIFIERS Advantages of Dual Monolithic Operational Amplifiers

Dual matched operational amplifiers provide the engineer with a powerful tool for designing instrumentation amplifiers and many other differential-input circuits. These designs are based on the principle that careful matching between two operational amplifiers can minimize the effect of dc errors in the individual amplifiers.

Reference to the circuit shown in Figure 6, a differential-in, differential-out amplifier, shows how the reductions in error can be accomplished. Assuming the resistors used are ideally matched, the gain of each side will be identical. If the offset voltages of each amplifier are perfectly matched, then the net differential voltage at the amplifier's output will be zero. Note that the output offset error of this amplifier is not a function of the offset voltage of the individual amplifiers, but only a function of the difference (degree of matching) between the amplifiers' offset voltages. This error-cancellation principle holds for a considerable number of input referred error parameters-offset voltage, offset voltage drift, inverting and noninverting bias currents, common mode and power supply rejection ratios. Note also that the impedances of each input, both common-mode and differential-mode, are high and tightly matched, an important feature not practical with single operation amplifier circuits.

Figure 6. Differential-In, Differential-Out Amplifier

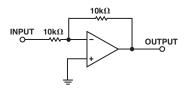

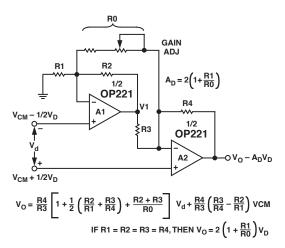

### INSTRUMENTATION AMPLIFIER APPLICATIONS Two-Op Amp Configuration

The two-op amp circuit (Figure 7) is recommended where the common-mode input voltage range is relatively limited; the common-mode and differential voltage both appear at V1. The high open-loop gain of the OP221 is very important in achieving good CMRR in this configuration. Finite open-loop gain of A1 (Ao1) causes undesired feedthrough of the common-mode input. For Ad/Ao, << 1, the common-mode error (CME) at the output due to this effect is approximately (2 Ad/Ao1) x VCM. This circuit features independent adjustment of CMRR and differential gain.

### Three-Op Amp Configuration

The three-op amp circuit (Figure 8) has increased commonmode voltage range because the common-mode voltage is not amplified as it is in Figure 7. The CMR of this amplifier is directly proportional to the match of the CMR of the input op amps. CMRR can be raised even further by trimming the output stage resistors.

Figure 8. Three-Op Amp Circuit

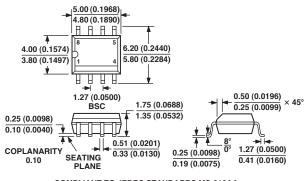

### **OUTLINE DIMENSIONS**

### 8-Lead Standard Small Outline Package [SOIC] Narrow Body

(RN-8)

Dimensions shown in millimeters and (inches)

COMPLIANT TO JEDEC STANDARDS MS-012AA CONTROLLING DIMENSIONS ARE IN MILLIMETERS; INCH DIMENSIONS (IN PARENTHESES) ARE ROUNDED-OFF MILLIMETER EQUIVALENTS FOR REFERENCE ONLY AND ARE NOT APPROPRIATE FOR USE IN DESIGN

# **Revision History**

| Location Page                                      |

|----------------------------------------------------|

| 10/02—Data Sheet changed from REV. B to REV. C.    |

| Deleted 8-Lead CERDIP Package (Q-8)Universal       |

| Edits to SPECIFICATIONS                            |

| Edits to ABSOLUTE MAXIMUM RATINGS                  |

| Edits to ORDERING GUIDE                            |

| Updated OUTLINE DIMENSIONS                         |

| 6/02—Data Sheet changed from REV. A to REV. B.     |

| Edits to 8-Lead SOIC Package (R-8)                 |

| 09/01—Data Sheet changed from REV. 0 to REV. A.    |

| Edits to PIN CONNECTIONS 1                         |

| Global deletion of references to OP221B and OP221C |

| Edits to WAFER TEST LIMITS                         |

| Edits to ABSOLUTE MAXIMUM RATINGS                  |

| Edits to ORDERING GUIDE                            |

| Edits to PACKAGE TYPE                              |

C00324-0-10/02(C)