DATA SHEET =

# **MB1502**

### SERIAL INPUT PLL FREQUENCY SYNTHESIZER

#### LOW POWER SERIAL INPUT PLL SYNTHESIZER WITH 1.1 GHz PRESCALER

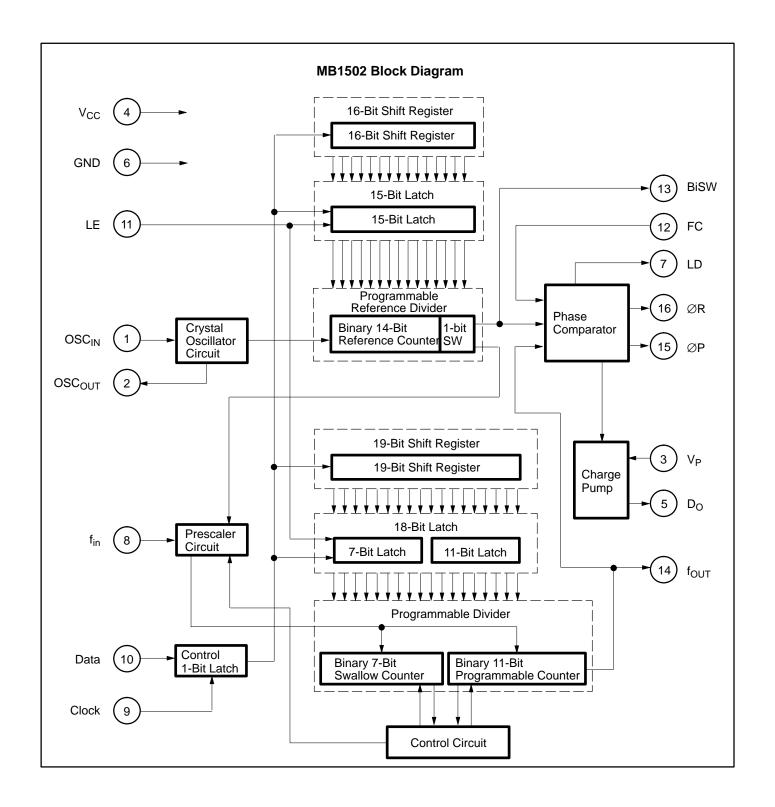

The Fujitsu MB1502, utilizing BI-CMOS technology, is a single chip serial input PLL synthesizer with pulse-swallow function. The MB1502 contains a 1.1GHz two modulus prescaler that can select of either 64/65 or 128/129 divide ratio, control signal generator, 16-bit shift register, 15-bit latch, programmable reference divider (binary 14-bit programmable reference counter), 1-bit switch counter, phase comparator with phase conversion function, charge pump, crystal oscillator, 19-bit shift register, 18-bit latch, programmable divider (binary 7-bit swallow counter and binary 11-bit programmable counter) and analog switch to speed up lock up time.

It operates supply voltage of 5V typ. and achieves very low supply current of 8mA typ. realized through the use of Fujitsu Advanced Process Technology.

#### **FEATURES**

- High operating frequency: f<sub>IN MAX</sub>=1.1GHz (V<sub>IN MIN</sub>=10dBm)

- Pulse swallow function: 64/65 or 128/129

- Low supply current: I<sub>CC</sub>=8mA typ.

- · Serial input 18-bit programmable divider consisting of:

- Binary 7-bit swallow counter: 0 to 127

- Binary 11-bit programmable counter: 16 to 2047

- Serial input 15-bit programmable reference divider consisting of:

- Binary 14-bit programmable reference counter: 8 to 16383

- 1-bit switch counter (SW) sets divide ratio of prescaler

- · On-chip analog switch achieves fast lock up time

- 2 types of phase detector output

- Ön-chip charge pump (Bipolar type)

- Output for external charge pump

- Wide operating temperature: -40°C to +85°C

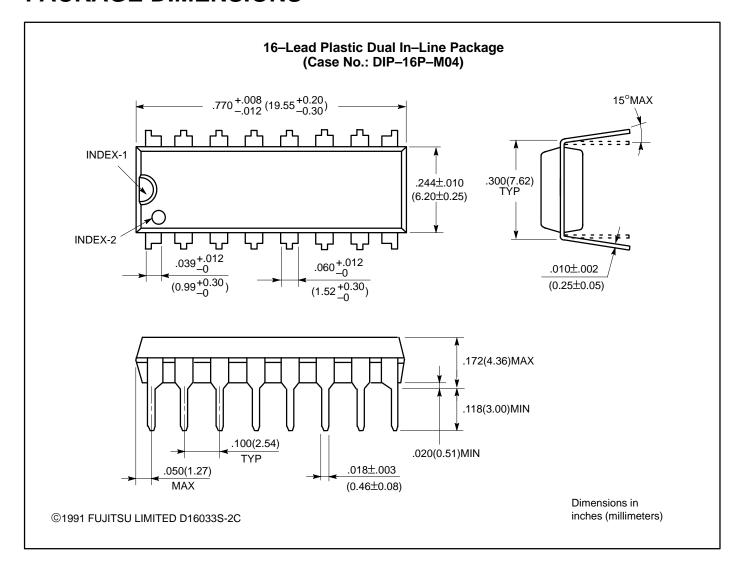

- 16-pin Plastic DIP Package (Suffix: —P)

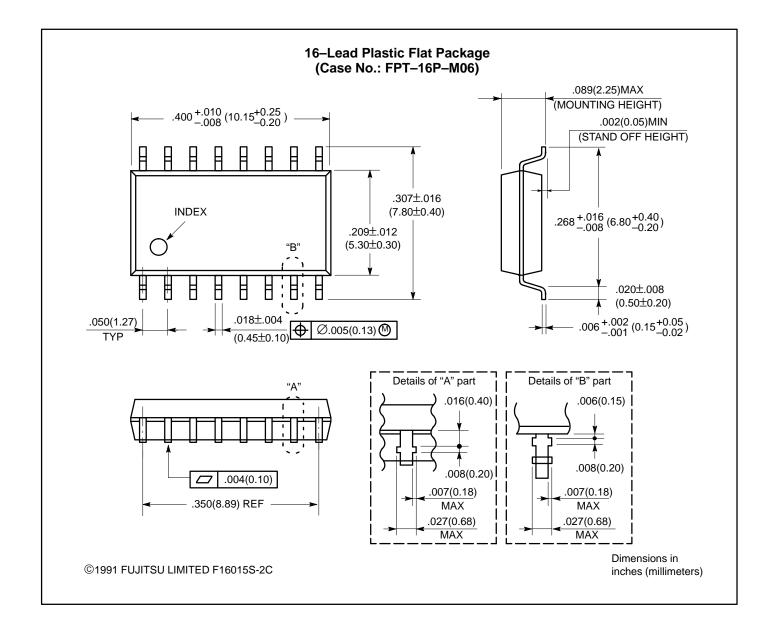

16-pin Plastic Flat Package (Suffix: —PF)

#### ABSOLUTE MAXIMUM RATINGS (See NOTE)

| Rating               | Symbol           | Value                        | Unit |

|----------------------|------------------|------------------------------|------|

| Dower Cumby Voltage  | V <sub>CC</sub>  | -0.5 to +7.0                 | V    |

| Power Supply Voltage | $V_{P}$          | V <sub>CC</sub> to 10.0      | V    |

| Output Voltage       | V <sub>OUT</sub> | –0.5 to V <sub>CC</sub> +0.5 | V    |

| Open-drain Voltage   | V <sub>OOP</sub> | -0.5 to 0.8                  | V    |

| Output Current       | I <sub>OUT</sub> | ± 10                         | mA   |

| Storage Temperature  | T <sub>STG</sub> | -55 to +125                  | °C   |

NOTE: Permanent device damage may occur if the above Absolute Maximum RatIngs are exceeded. Functional operation should be restricted to the conditions as detailed in the operational sections of this data sheet. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

This device contains circuitry to protect the inputs against damage due to high static voltages or electric fields. However, it is advised that normal precautions be taken to avoid application of any voltage higher than maximum rated voltages to this high impedance circuit.

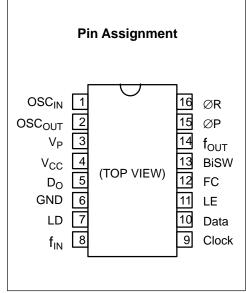

# **PIN DESCRIPTION**

| Pin<br>No. | Pin<br>Name                             | I/O | Description                                                                                                                                                                                                                                                                                                                          |

|------------|-----------------------------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 2        | OSC <sub>IN</sub><br>OSC <sub>OUT</sub> | 0   | Oscillator input. Oscillator output. A crystal is placed between OSC <sub>IN</sub> and OSC <sub>OUT</sub> .                                                                                                                                                                                                                          |

| 3          | V <sub>P</sub>                          | _   | Power supply input for charge pump and analog switch.                                                                                                                                                                                                                                                                                |

| 4          | V <sub>CC</sub>                         | _   | Power supply voltage input.                                                                                                                                                                                                                                                                                                          |

| 5          | D <sub>O</sub>                          | 0   | Charge pump output. The characteristics of charge pump is reversed depending upon FC input.                                                                                                                                                                                                                                          |

| 6          | GND                                     | _   | Ground                                                                                                                                                                                                                                                                                                                               |

| 7          | LD                                      | 0   | Phase comparator output. Normally this pin outputs high level. While the phase difference of $f_r$ , and $f_p$ exists, this pin outputs low level.                                                                                                                                                                                   |

| 8          | f <sub>IN</sub>                         | ı   | Prescaler input. The connection with an external VCO should be AC connection.                                                                                                                                                                                                                                                        |

| 9          | Clock                                   | ı   | Clock input for 19-bit shift register and 16-bit shift register. On rising edge of the clock shifts one bit of data into the shift registers.                                                                                                                                                                                        |

| 10         | Data                                    | ı   | Binary serial data input.  The last bit of the data is a control bit which specified destination of shift registers.  When this bit is high level and LE is high level, the data stored in shift register is transferred to 15-bit latch.  When this bit is low level and LE is high level, the data is transferred to 18-bit latch. |

| 11         | LE                                      | ı   | Load enable input (with internal pull up resistor).  When LE is high or open, the data stored in shift register is transferred into latch depending upon the control bit. At the time, internal charge pump output to be connected to BISW pin because internal analog switch becomes ON state.                                      |

| 12         | FC                                      | I   | Phase select input of phase comparator (with internal pull up resistor).  When FC is low level, the characteristics of charge pump, phase comparator is reversed.  FC input signal is also used to control fOUT pin (test pin) output level for f <sub>r</sub> or f <sub>p</sub> .                                                   |

| 13         | BISW                                    | 0   | Analog switch output.  Usually BISW pin is set high-impedance state. When internal analog switch is ON (LE pin is high level), this pin outputs internal charge pump state.                                                                                                                                                          |

| 14         | f <sub>OUT</sub>                        | 0   | Monitor pin of phase comparator input. $f_{OUT}$ pin outputs either programmable reference divider output $(f_r)$ or programmable divider output $(f_p)$ depending upon FC pin input level.                                                                                                                                          |

| 15<br>16   | ØP<br>ØR                                | 0   | Outputs for external charge pump. The characteristics are reversed according to FC input. ØP pin is N-channel open drain output.                                                                                                                                                                                                     |

### FUNCTIONAL DESCRIPTIONS

#### **SERIAL DATA INPUT**

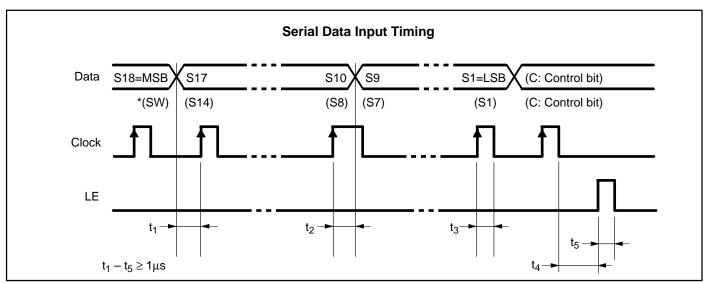

Serial data input is achieved by three inputs, such as Data pin, Clock pin and LE pin. Serial data input controls 15-bit programmable reference divider and 18-bit programmable divider, respectively.

Binary serial data is input to Data pin.

On rising edge of clock shifts one bit of serial data into the internal shift registers and when load enable pin is high level or open, stored data is transferred into latch depending upon the control bit.

Control data "H" data is transferred into 15-bit latch.

Control data "L" data is transferred into 18-bit latch.

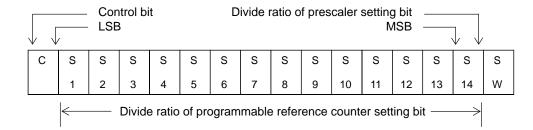

#### PROGRAMMABLE REFERENCE DIVIDER

Programmable reference divider consists of 16-bit shift register, 15-bit latch and 14-bit reference counter. Serial 16-bit data format is shown below.

#### 14-BIT PROGRAMMABLE REFERENCE COUNTER DIVIDE RATIO

| Divide<br>Ratio<br>R | S<br>14 | S<br>13 | S<br>12 | S<br>11 | S<br>10 | S<br>9 | S<br>8 | S<br>7 | S<br>6 | S<br>5 | S<br>4 | S<br>3 | S<br>2 | S<br>1 |

|----------------------|---------|---------|---------|---------|---------|--------|--------|--------|--------|--------|--------|--------|--------|--------|

| 8                    | 0       | 0       | 0       | 0       | 0       | 0      | 0      | 0      | 0      | 0      | 1      | 0      | 0      | 0      |

| 9                    | 0       | 0       | 0       | 0       | 0       | 0      | 0      | 0      | 0      | 0      | 1      | 0      | 0      | 1      |

| •                    | •       | •       | •       | •       | •       | •      | •      | •      | •      | •      | •      | •      | •      | •      |

| 16383                | 1       | 1       | 1       | 1       | 1       | 1      | 1      | 1      | 1      | 1      | 1      | 1      | 1      | 1      |

NOTES: Divide ratio less than 8 is prohibited.

Divide ratio: 8 to 16383

SW: This bit selects divide ratio of prescaler.

SW=H: 64

SW=L:128

S1 to S14: These bits select divide ratio of programmable reference divider.

C: Control bit (sets as high level).

Data is input from MSB side.

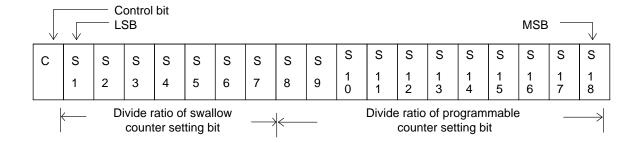

#### PROGRAMMABLE DIVIDER

Programmable divider consists of 19-bit shift register, 18-bit latch, 7-bit swallow counter and 11-bit programmable counter.

Serial 19-bit data format is shown on following page.

#### 7-BIT SWALLOW COUNTER DIVIDE RATIO

| Divide<br>Ratio | S | S | S | S | S | S | S |

|-----------------|---|---|---|---|---|---|---|

| A               | 7 | 6 | 5 | 4 | 3 | 2 | 1 |

| 0               | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 1               | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

| •               | • | • | • | • | • | • | • |

| 127             | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

NOTE: Divide ratio: 0 to 127

#### 11-BIT PROGRAMMABLE COUNTER DIVIDE RATIO

| Divide     | S      | S      | S      | S      | S      | S      | S      | S      | S      | S | S |

|------------|--------|--------|--------|--------|--------|--------|--------|--------|--------|---|---|

| Ratio<br>N | 1<br>8 | 1<br>7 | 1<br>6 | 1<br>5 | 1<br>4 | 1<br>3 | 1<br>2 | 1<br>1 | 1<br>0 | 9 | 8 |

| 16         | 0      | 0      | 0      | 0      | 0      | 0      | 1      | 0      | 0      | 0 | 1 |

| 17         | 0      | 0      | 0      | 0      | 0      | 0      | 1      | 0      | 0      | 0 | 1 |

| •          | •      | •      | •      | •      | •      | •      | •      | •      | •      | • | • |

| 2047       | 1      | 1      | 1      | 1      | 1      | 1      | 1      | 1      | 1      | 1 | 1 |

NOTES: Divide ratio less than 16 is prohibited.

Divide ratio: 16 to 2047

S1 to S7: Swallow counter divide ratio setting bit. (0 to 127)

S8 to S18: Programmable counter divide ratio setting bit. (16 to 2047)

C: Control bit (sets as low level). Data is input from MSB side.

#### **PULSE SWALLOW FUNCTION**

[(PxN)+A] x  $f_{osc} \div R$  $f_{VCO} =$

$f_{VCO}$ : Output frequency of external voltage controlled oscillator (VCO) N: Preset divide ratio of binary 11-bit programmable counter (16 to 2047) Preset divide ratio of binary 7-bit swallow counter (0≤A≤127, A<N) A:

Output frequency of the external reference frequency oscillator fosc: R: Preset divide ratio of binary 14-bit programmable reference counter (8 to 16383)

P: Preset modulus of external dual modulus prescaler (64 or 128)

**NOTES:** Parenthesis data is used for setting divide ratio of programmable reference divider. On rising edge of clock shifts one bit of data in the shift register.

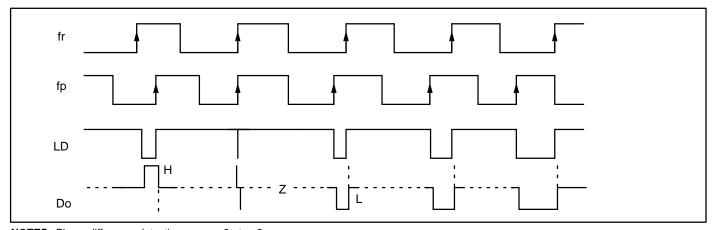

#### **PHASE CHARACTERISTICS**

FC pin is provided to change phase characteristics of phase comparator. Characteristics of internal charge pump output level ( $D_0$ ), phase comparator output level ( $D_0$ R,  $D_0$ R) are reversed depending upon FC pin input level. Also, monitor pin ( $D_0$ R) output level of phase comparator is controlled by FC pin input level. The relation between outputs ( $D_0$ ,  $D_0$ R,  $D_0$ R) and FC input level are shown below.

|             |    | FC=H c | r open |                      | FC=L |    |    |                      |  |  |

|-------------|----|--------|--------|----------------------|------|----|----|----------------------|--|--|

|             | Do | ØR     | ØP     | f <sub>OU</sub><br>T | Do   | ØR | ØP | f <sub>OU</sub><br>T |  |  |

| $f_r > f_p$ | Н  | L      | L      | (f <sub>r</sub> )    | L    | Н  | Z  | (f <sub>p</sub> )    |  |  |

| $f_r < f_p$ | L  | Н      | Z      | (f <sub>r</sub> )    | Н    | L  | L  | (f <sub>p</sub> )    |  |  |

| $f_r = f_p$ | Z  | L      | Z      | (f <sub>r</sub> )    | Z    | L  | Z  | (f <sub>p</sub> )    |  |  |

**Note:** Z = (High impedance)

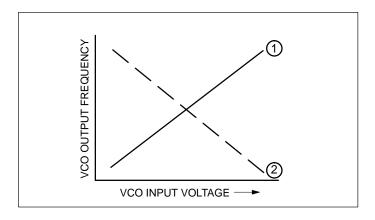

VCO CHARACTERISTICS Depending upon VCO characteristics, FC pin should be set accordingly:

- When VCO characteristics are like 1, FC should be set High or open circuit;

- When VCO characteristics are like 2, FC should be set Low.

**NOTES**: Phase difference detection range:  $-2\pi$  to  $+2\pi$

Spike appearance depends on charge pump characteristics. Also, the spike is output in order to diminish dead band. When  $f_r > f_p$  or  $f_r < f_p$ , spike might not appear depending upon charge pump characteristics.

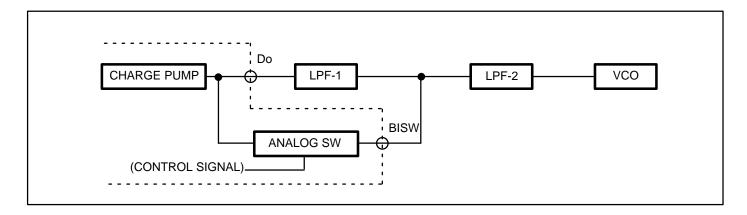

#### **ANALOG SWITCH**

ON/OFF of analog switch is controlled by LE input signal. When the analog switch is ON, internal charge pump output (DO) to be connected to BISW pin. When the analog switch is OFF, BISW pin is set to high-impedance state.

LE=H (Changing the divide ratio of internal prescaler): Analog switch=ON LE=L (Normal operating mode): Analog switch=OFF

LPF time constant is decreased in order to insert a analog switch between LPF1 and LPF2 when channel of PLL is changing. Thus, lock up time is decreased, that is, fast lock up time is achieved.

### RECOMMENDED OPERATING CONDITIONS

| Parameter             | Symbol          |                 | Unit           |                 |      |

|-----------------------|-----------------|-----------------|----------------|-----------------|------|

|                       | Symbol          | Min             | Тур            | Max             | Unit |

| Power Supply Voltage  | V <sub>CC</sub> | 4.5             | 5.0            | 5.5             | V    |

|                       | V <sub>P</sub>  | V <sub>CC</sub> | V <sub>P</sub> | 8.0             | V    |

| Input Voltage         | VI              | GND             |                | V <sub>CC</sub> | V    |

| Operating Temperature | T <sub>A</sub>  | -40             |                | 85              | °C   |

## **ELECTRICAL CHARACTERISTICS**

(Vcc=4.5 to 5.5V, TA=-40 to +85°C, unless otherwise noted.)

| Parameter                              |                           | Symbol           | Condition                                     |                      | Unit |                      |                 |

|----------------------------------------|---------------------------|------------------|-----------------------------------------------|----------------------|------|----------------------|-----------------|

|                                        |                           | Зушьог           | Condition                                     | Min                  | Тур  | Max                  | Unit            |

| Power Supply Current                   |                           | Icc              | Note 1                                        |                      | 8.0  | 12.0                 | mA              |

| 0                                      | f <sub>in</sub>           | f <sub>in</sub>  | Note2                                         | 10                   |      | 1100                 | MHz             |

| Operating Frequency                    | OSC <sub>IN</sub>         | fosc             |                                               |                      | 12   | 20                   | MHz             |

| Lancet One of the No.                  | f <sub>in</sub>           | V <sub>fin</sub> |                                               | -10                  |      | 6                    | dBm             |

| Input Sensitivity                      | OSC <sub>IN</sub>         | Vosc             |                                               | 0.5                  |      |                      | V <sub>PP</sub> |

| High-level Input Voltage               | Except f <sub>in</sub>    | V <sub>IH</sub>  |                                               | V <sub>CC</sub> x0.7 |      |                      | V               |

| Low-level Input Voltage                | and OSC <sub>IN</sub>     | V <sub>IL</sub>  |                                               |                      |      | V <sub>CC</sub> x0.3 | V               |

| High-level Input Current               | Data                      | I <sub>IH</sub>  |                                               |                      | 1.0  |                      | μА              |

| Low-level Input Current                | Clock                     | I <sub>IL</sub>  |                                               |                      | -1.0 |                      | μА              |

|                                        | OSC <sub>IN</sub>         | losc             |                                               |                      | ±50  |                      | μА              |

| Input Current                          | LE, FC                    | I <sub>LE</sub>  |                                               |                      | -60  |                      | μА              |

| High-level Output Current              | Except D <sub>O</sub>     | V <sub>OH</sub>  | V <sub>CC</sub> = 5 V                         | 4.4                  |      |                      | V               |

| Low-level Output Current               | and<br>OSC <sub>OUT</sub> | V <sub>OL</sub>  |                                               |                      |      | 0.4                  | V               |

| N-channel Open Drain Cutoff<br>Current | D <sub>O</sub> , ØP       | I <sub>OFF</sub> | $V_P = V_{CC}$ to 8V<br>$V_{OOP} = GND$ to 8V |                      |      | 1.1                  | μА              |

| Output Current                         | Except D <sub>O</sub>     | Іон              |                                               | -1.0                 |      |                      | mA              |

|                                        | and<br>OSC <sub>OUT</sub> | I <sub>OL</sub>  |                                               | 1.0                  |      |                      | mA              |

| Analog Switch On Resistor              | 1                         | R <sub>ON</sub>  |                                               |                      | 25   |                      | Ω               |

NOTE: 1: f in = 1.1GHz, OSC<sub>IN</sub>=12MHz, V<sub>CC</sub>=5V. Inputs are grounded and outputs are open. 2: AC coupling. Minimum operating frequency is measured when a capacitor 1000pF is connected.

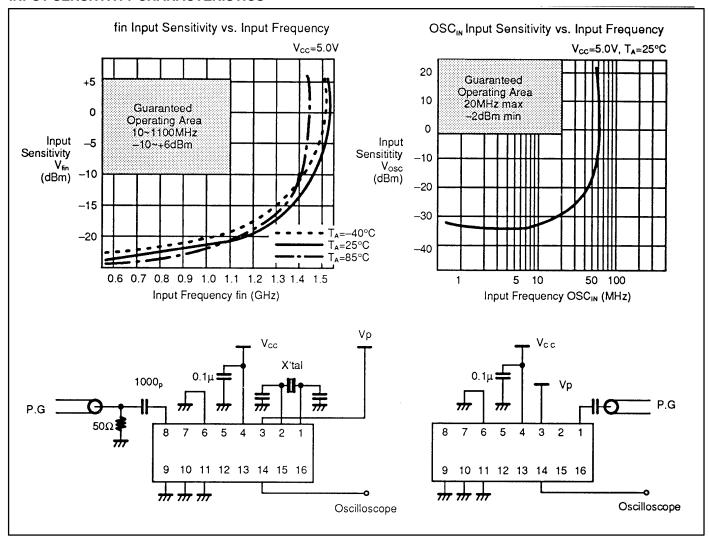

## **TYPICAL CHARACTERISTICS CURVES**

#### INPUT SENSITIVITY CHARACTERISTICS

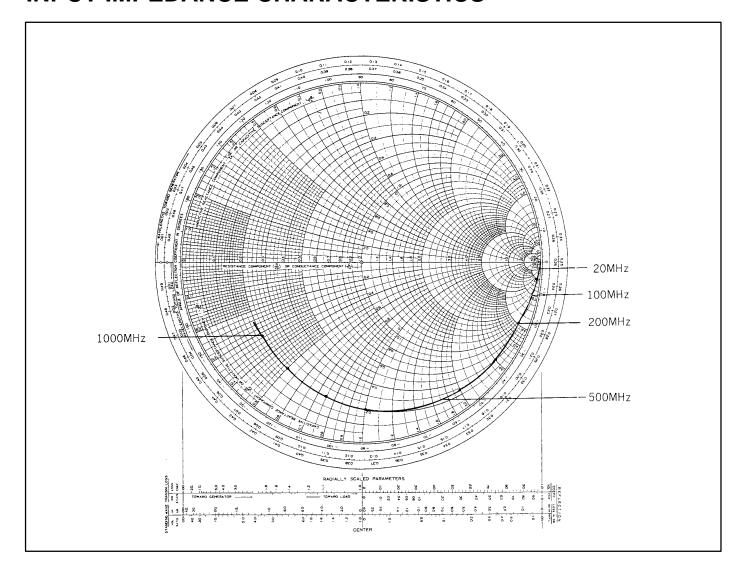

# **INPUT IMPEDANCE CHARACTERISTICS**

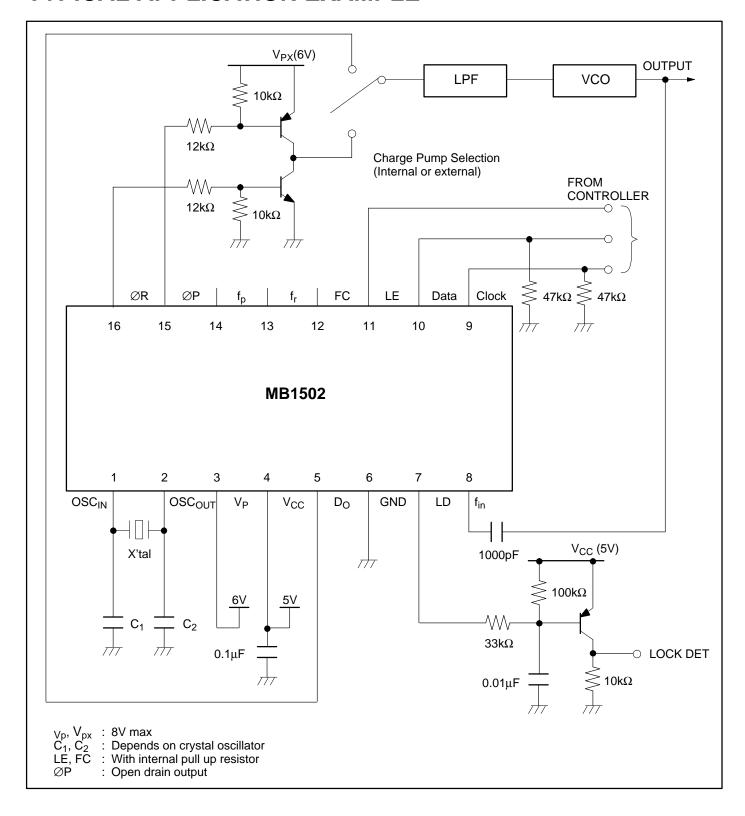

## **TYPICAL APPLICATION EXAMPLE**

## **PACKAGE DIMENSIONS**

#### All Rights Reserved.

Circuit diagrams utilizing Fujitsu products are included as a means of illustrating typical semiconductor applications. Complete Information sufficient for construction purposes is not necessarily given.

The information contained in this document has been carefully checked and is believed to be reliable. However, Fujitsu assumes no responsibility for inaccuracies.

The information contained in this document does not convey any license under the copyrights, patent rights or trademarks claimed and owned by Fujitsu.

Fujitsu reserves the right to change products or specifications without notice.

No part of this publication may be copied or reproduced in any form or by any means, or transferred to any third party without prior written consent of Fujitsu.

### **FUJITSU LIMITED**

For further information, please contact:

#### Japan

FUJITSU LIMITED Semiconductor Marketing Furukawa Sogo Bldg. 6-1,Marunouchi 2-chome Chiyoda-ku, Tokyo 100 Japan Tel: (03)3216-3211

Telex: 781-2224361 FAX: (03)3216-9771

#### North and South America

FUJITSU MICROELECTRONICS, INC. Semiconductor Division 3545 North First Street San Jose, CA 95134-1804 USA Tel: (408)922-9000

FAX: (408)432-9044

#### **Europe**

FUJITSU MIKROELEKTRONIK GmbH Arabella Centre 9.0G Lyoner Strasse 44-48 D-6000 Frankfurt 71 F.R. Germany

Tel: (069) 66320 Telex: 411963 FAX: (069) 6632122

#### Asia

FUJITSU MICROELECTRONICS ASIA PTE LIMITED 51 Bras Basah Road Plaza by the Park #06-04/07 Singapore 0718 Tel: 336-1600

Telex: 55373 FAX: 336-1609

© 1990 FUJITSU LIMITED Printed in Japan

JV0123-90YA3