# **ANALOG Isolated, Synchronous Forward Controller** with Active Clamn and Coupler

**Data Sheet**

# **ADP1074**

#### **FEATURES**

Current mode controller for active clamp forward topology Integrated 5 kV (wide body SOIC package) or 3.0 kV (LGA package) rated dielectric isolation voltage with Analog Devices, Inc., patented *i*Coupler technology Wide voltage supply range Primary V<sub>IN</sub>: up to 60 V Secondary VDD2: up to 36 V Integrated 1 A primary side MOSFET driver for power switch and active clamp reset switch Integrated 1 A secondary side MOSFET drivers for synchronous rectification Integrated error amplifier and <1% accurate reference voltage Programmable slope compensation Programmable frequency range: 50 kHz to 600 kHz typical **Frequency synchronization** Programmable maximum duty cycle limit **Programmable soft start** Smooth soft start from precharged load **Programmable dead time** Power saving light load mode using MODE pin Protection features such as short circuit, output overvoltage, and overtemperature protection Cycle-by-cycle input overcurrent protection Precision enable UVLO with hysteresis PGOOD pin for system flagging Tracking function from secondary side

Remote (secondary side) shutdown/reset function Safety and regulatory approvals (pending) **UL** recognition 5000 V rms for 1 minute per UL 1577 (for wide body SOIC package) 3000 V rms for 1 minute per UL 1577 (for LGA package) CSA component acceptance notice 5A VDE certificate of conformity DIN V VDE V 0884-10 (VDE V 0884-10):2006-12 V<sub>IORM</sub> = 849 V peak (for wide body SOIC package) V<sub>IORM</sub> = 560 V peak (for LGA package) CQC certification per GB4943.1-2011 Available in 24-lead SOIC\_W package and 24-terminal LGA package **AEC-Q100 Qualified for Automotive Applications** APPLICATIONS Isolated dc-to-dc power conversion Intermediate bus voltage generation

Telecom, industrial Base station and antenna RF power Small cell **PoE powered device Enterprise switches/routers** Core/edge/metro/optical routing **Power modules**

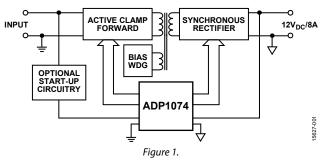

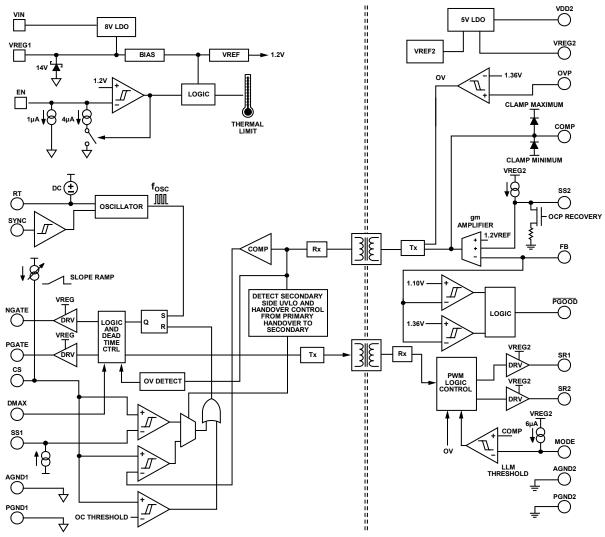

#### SIMPLIFIED BLOCK DIAGRAM

**Document Feedback**

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

Rev. D

## **TABLE OF CONTENTS**

| Features                                                          |

|-------------------------------------------------------------------|

| Applications 1                                                    |

| Simplified Block Diagram 1                                        |

| Revision History                                                  |

| General Description                                               |

| Specifications                                                    |

| Insulation and Safety Related Specifications7                     |

| Regulatory Information8                                           |

| DIN V VDE V 0884-10 (VDE V 0884-10) Insulation<br>Characteristics |

| DIN V VDE V 0884-10 (VDE V 0884-10) Insulation<br>Characteristics |

| Absolute Maximum Ratings 11                                       |

| Thermal Resistance11                                              |

| ESD Caution11                                                     |

| Pin Configurations and Function Descriptions12                    |

| Typical Performance Characteristics14                             |

| Theory of Operation16                                             |

| Detailed Block Diagram17                                          |

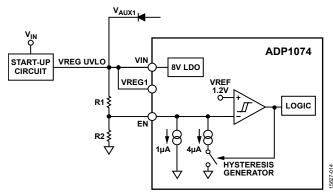

| Primary Side Supply, Input Voltage, and LDO18                     |

| Secondary Side Supply and LDO18                                   |

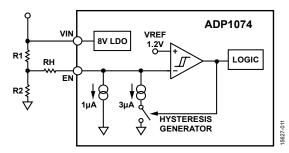

| Precision Enable                                                  |

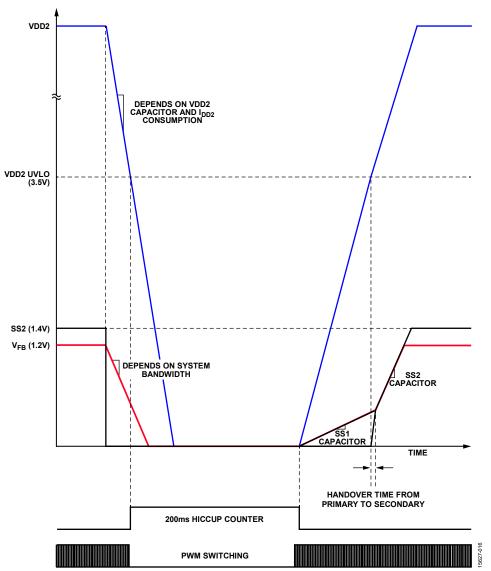

| Soft Start Procedure                                              |

| Output Voltage Sensing and Feedback                               |

| Loop Compensation and Steady State Operation                      |

#### **REVISION HISTORY**

| 6/2020—Rev. C to Rev. D                |    |

|----------------------------------------|----|

| Changes to Ordering Guide              | 31 |

|                                        |    |

| 4/2020—Rev. B to Rev. C                |    |

| Moved General Description Section      | 3  |

| Added Table 1; Renumbered Sequentially | 3  |

|                                        |    |

| 8/2018—Rev. A to Rev. B |  |

|-------------------------|--|

| Changes to Table 1      |  |

| 8/2018- | -Rev. 0 | to Rev. A |  |

|---------|---------|-----------|--|

| Added CC-24-6 Package       | Throughout |

|-----------------------------|------------|

| Changes to Features Section |            |

| Changes to Table 1          |            |

| Changes to Table 2          | 6          |

Changes to Input/Output Current-Limit Protection Section.... 19

| 3  | Slope Compensation                    | 20 |

|----|---------------------------------------|----|

| ]  | Input/Output Current-Limit Protection | 20 |

| ,  | Temperature Sensing                   | 21 |

| ]  | Frequency Setting (RT Pin)            | 21 |

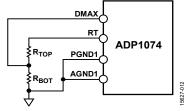

| j  | Maximum Duty Cycle                    | 21 |

| ]  | Frequency Synchronization             | 21 |

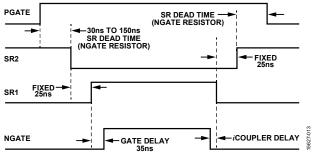

| :  | Synchronous Rectifier (SR) Drivers    | 22 |

|    | Output Overvoltage Protection (OVP)   | 22 |

|    | Active Clamp (PGATE)                  | 22 |

| ]  | Leading Edge Blanking                 | 22 |

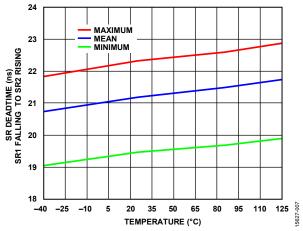

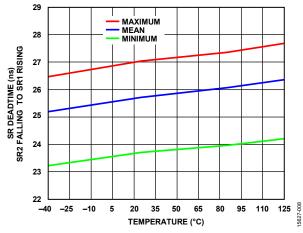

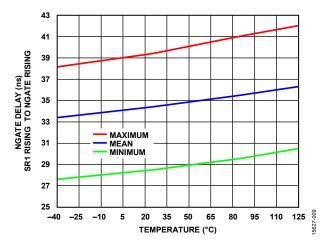

|    | Gate Delay and SR Dead Time           | 22 |

| ]  | Light Load Mode (LLM) and SR Phase In | 22 |

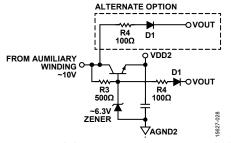

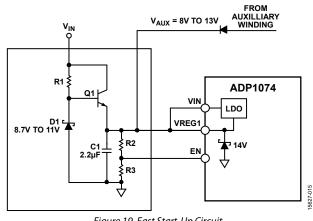

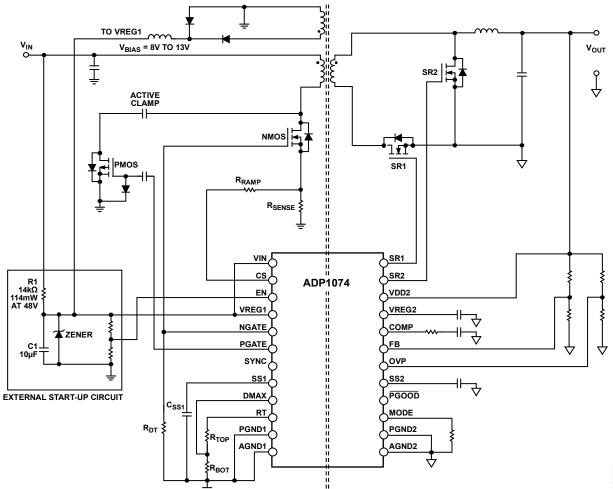

| ]  | External Start-Up Circuit             | 23 |

| :  | Soft Stop                             | 23 |

| ]  | Power Good                            | 23 |

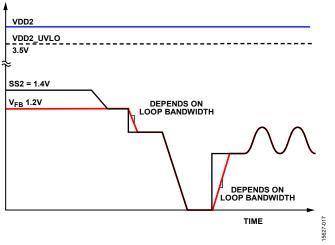

|    | OCP/Feedback Recovery                 | 24 |

|    | Output Voltage Tracking               | 24 |

| ]  | Remote System Reset                   | 24 |

|    | OCP Counter                           | 26 |

| ]  | Insulation Lifetime                   | 26 |

| ]  | Layout Guidelines                     | 27 |

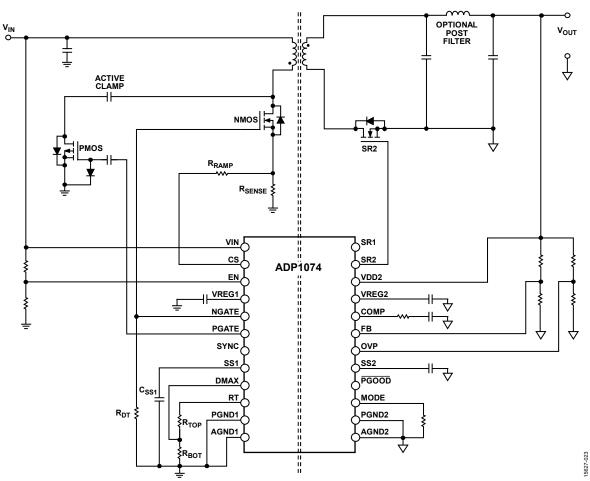

| Ту | pical Application Circuits            | 28 |

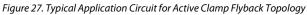

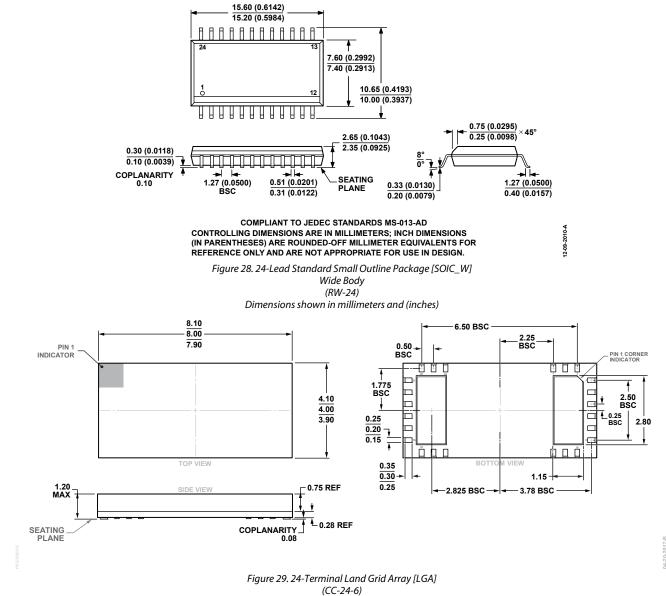

| Ou | Itline Dimensions                     | 31 |

|    | Ordering Guide                        | 31 |

|    |                                       |    |

| Added Table 4; Renumbered Sequentially7                     |

|-------------------------------------------------------------|

| Changes to Table 37                                         |

| Added DIN V VDE V 0884-10 (VDE V 0884-10) Insulation        |

| Characteristics Section, Table 5, and Figure 2; Renumbered  |

| Sequentially                                                |

| Added DIN V VDE V 0884-10 (VDE V 0884-10) Insulation        |

| Characteristics Section, Table 6, and Figure 39             |

| Added Table 10 10                                           |

| Changes to Table 8 and Table 9 10                           |

| Added Figure 5 11                                           |

| Changes to Input/Output Current Limit Protection Section 19 |

| Added Figure 15 20                                          |

| Updated Outline Dimensions                                  |

| Changes to Ordering Guide                                   |

10/2017—Revision 0: Initial Version

## **GENERAL DESCRIPTION**

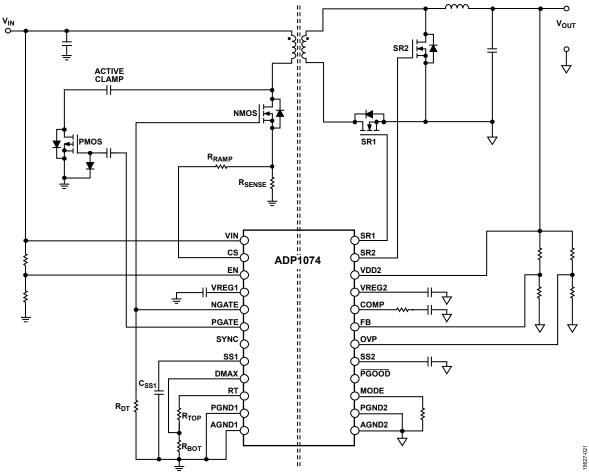

The ADP1074 is a current mode, fixed frequency, active clamp, synchronous forward controller designed for isolated dc to dc power supplies. Analog Devices proprietary *i*Couplers\* are integrated in the ADP1074 to eliminate the bulky signal transformers and optocouplers that transmit signals over the isolation boundary. Integrating the *i*Couplers reduces system design complexity, cost, and component count and improves overall system reliability. With the integrated isolators and metal-oxide semiconductor field effect transistor (MOSFET) drivers on both the primary and the secondary side, the ADP1074 offers a compact system level design and yields a higher efficiency than a non-synchronous forward converter at heavy loads.

The primary side pins provide functions for programming the switching frequency, maximum duty cycle, external frequency synchronization, and slope compensation.

The secondary side pins provide functions for differential output voltage sensing, overvoltage, power good, tracking, and programmable light load mode setting.

The feedback signal and timing of synchronous rectifier pulsewidth modulations (PWMs) are transmitted from primary to secondary or from secondary to primary sides through the *i*Couplers using a proprietary transmission scheme.

The ADP1074 also offers features such as input current protection, undervoltage lockout (UVLO), precision enable with adjustable hysteresis, overtemperature protection (OTP), and power saving light load mode (LLM).

#### Table 1. Related Products<sup>1</sup>

| Lead Free Finish    | Tape and Reel <sup>2</sup> | Part<br>Marking | Package Description                                        | Temperature<br>Range <sup>3</sup> |

|---------------------|----------------------------|-----------------|------------------------------------------------------------|-----------------------------------|

| LT8672EMS#WPBF      | LT8672EMS#WTRPBF           | LTGYT           | 10-lead plastic MSOP                                       | -40°C to +125°C                   |

| LT8672IMS#WPBF      | LT8672IMS#WTRPBF           | LTGYT           | 10-lead plastic MSOP                                       | -40°C to +125°C                   |

| LT8672JMS#WPBF      | LT8672JMS#WTRPBF           | LTGYT           | 10-lead plastic MSOP                                       | -40°C to +150°C                   |

| LT8672HMS#WPBF      | LT8672HMS#WTRPBF           | LTGYT           | 10-lead plastic MSOP                                       | -40°C to +150°C                   |

| LT8672EDDBM#WTRMPBF | LT8672EDDBM#WTRPBF         | LHJR            | 10-lead, 3 mm × 2 mm, plastic side wettable<br>DFN package | –40°C to +125°C                   |

| LT8672IDDBM#WTRMPBF | LT8672IDDBM#WTRPBF         | LHJR            | 10-lead, 3 mm × 2 mm, plastic side wettable<br>DFN package | –40°C to +125°C                   |

| LT8672JDDBM#WTRMPBF | LT8672JDDBM#WTRPBF         | LHJR            | 10-lead, 3 mm × 2 mm, plastic side wettable<br>DFN package | –40°C to +150°C                   |

<sup>1</sup> Versions of these devices are available with controlled manufacturing to support the quality and reliability requirements of automotive applications. These models are designated with a W suffix. Only the automotive grade products shown are available for use in automotive applications. Contact a local Analog Devices account representative for specific product ordering information and to obtain the specific automotive reliability reports for these models.

<sup>2</sup> Some packages are available in 500 unit reels through designated sales channels. These versions feature the #TRMPBF suffix.

<sup>3</sup> Contact the factory for devices specified with wider operating temperature ranges. The temperature grade is identified by a label on the shipping container.

## **SPECIFICATIONS**

VIN = 24 V, VDD2 = 12 V,  $T_J$  =  $-40^{\circ}C$  to +125°C, unless otherwise noted.

#### Table 2.

| Parameter                                             | Symbol           | Test Conditions/Comments                                                          | Min       | Тур   | Max       | Unit |

|-------------------------------------------------------|------------------|-----------------------------------------------------------------------------------|-----------|-------|-----------|------|

| SUPPLY (PRIMARY)                                      |                  |                                                                                   |           |       |           |      |

| Supply Voltage                                        | V <sub>IN</sub>  | 4.7 $\mu F$ capacitor from VIN to PGND1, 1 $\mu F$ capacitor from VREG1 to PGND1  | 4.7       | 24    | 60        | V    |

| Quiescent Supply Current                              | Ivin             | VIN > VIN UVLO, NGATE and PGATE unloaded                                          |           |       |           |      |

|                                                       |                  | At 100 kHz                                                                        |           | 5.3   |           | mA   |

|                                                       |                  | At 300 kHz                                                                        |           | 5.8   |           | mA   |

|                                                       |                  | At 600 kHz                                                                        |           | 6.8   |           | mA   |

|                                                       |                  | VIN > VIN UVLO, NGATE and PGATE<br>loaded with 2.2 nF and 410 pF,<br>respectively |           |       |           |      |

|                                                       |                  | At 100 kHz                                                                        |           | 7.5   |           | mA   |

|                                                       |                  | At 300 kHz                                                                        |           | 12    |           | mA   |

|                                                       |                  | At 600 kHz                                                                        |           | 19.5  |           | mA   |

| VIN Shutdown Current                                  |                  | EN pin voltage (V <sub>EN</sub> ) < 1.2 V, VREG1 = 0 V, VIN = 60 V                |           |       | 55        | μΑ   |

| (VIN + VREG1) Start-Up Current                        | IVIN_STARTUP     | $V_{EN} < 1.2 \text{ V}, \text{VREG1} = 12 \text{ V}, \text{VIN} = 12 \text{ V}$  |           |       | 160       | μA   |

| VIN UVLO                                              |                  | VIN rising                                                                        |           |       | 4.7       | V    |

|                                                       |                  | VIN falling                                                                       | 4.0       |       |           | V    |

| UVLO Hysteresis                                       |                  |                                                                                   |           | 0.19  |           | V    |

| Time from EN High to PGATE<br>Output Switching        |                  | $V_{\text{EN}}$ > 1.2 V, 1 $\mu\text{F}$ capacitor on VREG1                       |           |       | 1         | ms   |

| Time from EN Low to SR1/SR2<br>Output Stops Switching |                  | $V_{\text{EN}}$ < 1.0 V, 1 $\mu F$ capacitor on VREG1                             |           |       | 1         | μs   |

| SUPPLY (SECONDARY)                                    |                  |                                                                                   |           |       |           |      |

| Supply Voltage                                        | V <sub>DD2</sub> | 4.7 $\mu F$ capacitor from VDD2 to PGND2, 1 $\mu F$ capacitor from VREG2 to PGND2 | 4.5       | 12    | 36        | V    |

| Quiescent Supply Current                              | I <sub>DD2</sub> | SR1 and SR2 unloaded                                                              |           |       |           |      |

|                                                       |                  | At 100 kHz                                                                        |           | 6.5   |           | mA   |

|                                                       |                  | At 300 kHz                                                                        |           | 6.7   |           | mA   |

|                                                       |                  | At 600 kHz                                                                        |           | 7     |           | mA   |

|                                                       | I <sub>DD2</sub> | SR1 and SR2 loaded with 2.2 nF                                                    |           |       |           |      |

|                                                       |                  | At 100 kHz                                                                        |           | 8.3   |           | mA   |

|                                                       |                  | At 300 kHz                                                                        |           | 12    |           | mA   |

|                                                       |                  | At 600 kHz                                                                        |           | 18    |           | mA   |

| VDD2 UVLO Threshold                                   |                  | VDD2 rising                                                                       |           |       | 3.55      | V    |

|                                                       |                  | VDD2 falling                                                                      | 3.0       |       |           | V    |

| UVLO Hysteresis                                       |                  |                                                                                   |           | 0.145 |           | V    |

| Secondary UVLO Hiccup Time                            |                  |                                                                                   |           | 200   |           | ms   |

| OSCILLATOR                                            |                  |                                                                                   |           |       |           |      |

| Switching Frequency (f <sub>s</sub> )                 |                  | RT resistance ( $R_{RT}$ ) = 480 k $\Omega$ (±1%)                                 | 50 - 10%  | 50    | 50 + 10%  | kHz  |

|                                                       |                  | $R_{RT} = 240 \text{ k}\Omega (\pm 1\%)$                                          | 100 – 10% | 100   | 100 + 10% | kHz  |

|                                                       |                  | $R_{RT} = 120 \text{ k}\Omega (\pm 1\%)$                                          | 200 - 10% | 200   | 200 + 10% | kHz  |

|                                                       |                  | $R_{RT} = 80 \ k\Omega \ (\pm 1\%)$                                               | 300 - 10% | 300   | 300 + 10% | kHz  |

|                                                       |                  | $R_{RT} = 60 \text{ k}\Omega \text{ (}\pm1\%\text{)}$                             | 400 - 10% | 400   | 400 + 10% | kHz  |

|                                                       |                  | $R_{RT} = 40 \ k\Omega \ (\pm 1\%)$                                               | 600 - 10% | 600   | 600 + 10% | kHz  |

| VREG1 PIN                                             |                  |                                                                                   |           |       |           |      |

| VREG1 Voltage Clamp                                   |                  | VREG1 current ( $I_{VREG1}$ ) = 3 mA, $V_{EN}$ < 1.2 V                            | 13.5      | 14.3  | 15.2      | V    |

| VREG1 Clamp Series Resistance                         |                  | VREG1 forced current of 5 mA and 15 mA                                            |           | 16    |           | Ω    |

# ADP1074

| Parameter                                                | Symbol                    | <b>Test Conditions/Comments</b>                                               | Min | Тур | Max | Unit   |

|----------------------------------------------------------|---------------------------|-------------------------------------------------------------------------------|-----|-----|-----|--------|

| GATE DRIVERS (PRIMARY)                                   |                           |                                                                               |     |     |     |        |

| NGATE and PGATE High<br>Voltage                          |                           | $I_{VREG1} = 20 \text{ mA}, \text{VIN} > 9 \text{ V}$                         | 7.8 | 8   | 8.2 | V      |

| Gate Short-Circuit Peak<br>Current <sup>1</sup>          |                           | 8 V on VREG1                                                                  |     | 1.0 |     | А      |

| Rise Time                                                |                           | 10% to 90%                                                                    |     |     |     |        |

| NGATE                                                    |                           | $C_{NGATE} = 2.2 \text{ nF}$                                                  |     | 18  |     | ns     |

| PGATE                                                    |                           | $C_{PGATE} = 410 \text{ pF}$                                                  |     | 8   |     | ns     |

| Fall Time                                                |                           | 90% to 10%                                                                    |     |     |     |        |

| NGATE                                                    |                           | $C_{NGATE} = 2.2 \text{ nF}$                                                  |     | 16  |     | ns     |

| PGATE                                                    |                           | $C_{PGATE} = 410 \text{ pF}$                                                  |     | 7   |     | ns     |

| Source Resistance                                        | R <sub>ON_SOURCE</sub>    | Source 100 mA                                                                 |     |     |     |        |

| NGATE                                                    | _                         |                                                                               |     | 4   |     | Ω      |

| PGATE                                                    |                           |                                                                               |     | 6.5 |     | Ω      |

| Sink Resistance                                          | Ron_sink                  | Sink 100 mA                                                                   |     |     |     |        |

| NGATE                                                    |                           |                                                                               |     | 3   |     | Ω      |

| PGATE                                                    |                           |                                                                               |     | 3.5 |     | Ω      |

| NGATE Maximum Duty Cycle                                 | D <sub>MAX</sub>          | Divider bottom resistor ( $R_{BOT}$ ) = 0 $\Omega$                            | 45  | 50  | 55  | %      |

|                                                          |                           | Divider top resistor (R <sub>TOP</sub> ) = R <sub>BOT</sub> ,<br>1% resistors |     | 75  |     | %      |

| NGATE Minimum On Time                                    |                           | Includes propagation delay and CS comparator blanking time                    |     | 170 |     | ns     |

| SRx DRIVERS (SECONDARY)                                  |                           |                                                                               |     |     |     |        |

| SR1 and SR2 High Voltage                                 |                           | I <sub>VREG2</sub> = 15 mA, VDD2 > 5.5 V                                      | 4.9 | 5   | 5.1 | V      |

| Gate Short-Circuit Peak<br>Current <sup>1</sup>          |                           | 5 V on VREG2                                                                  |     | 1.0 |     | А      |

| SRx Time                                                 |                           | C <sub>SRx</sub> = 2.2 nF                                                     |     |     |     |        |

| Rise                                                     |                           | 10% to 90%                                                                    |     | 14  |     | ns     |

| Fall                                                     |                           | 90% to 10%                                                                    |     | 11  |     | ns     |

| Minimum On                                               |                           | Includes blanking time                                                        |     | 230 |     | ns     |

| SRx Resistance                                           |                           | _                                                                             |     |     |     |        |

| Source                                                   | Ron_sr_source             | Source 100 mA                                                                 |     | 3.5 |     | Ω      |

| Sink                                                     | Ron_sr_sink               | Sink 100 mA                                                                   |     | 2   |     | Ω      |

| DELAYS                                                   |                           |                                                                               |     |     |     |        |

| Gate Delay (SR1 Rising to NGATE Rising)                  |                           |                                                                               |     | 35  |     | ns     |

| Delay Between NGATE Falling<br>Edge and SR1 Falling Edge | <i>i</i> Coupler<br>delay |                                                                               |     | 21  |     | ns     |

| SR DEAD TIME (PGATE RISING<br>TO SR2 FALLING)            | ,                         | Resistor (±5%) at NGATE                                                       |     |     |     |        |

| - /                                                      |                           | Dead time resistor ( $R_{DT}$ ) = 10 k $\Omega$                               |     | 154 |     | ns     |

|                                                          |                           | $R_{DT} = 22 \ k\Omega$                                                       |     | 109 |     | ns     |

|                                                          |                           | $R_{DT} = 47 \text{ k}\Omega$                                                 |     | 72  |     | ns     |

|                                                          |                           | R <sub>DT</sub> is open                                                       |     | 42  |     | ns     |

| SR1 and SR2 Dead Time                                    |                           | Dead time between SR1 and SR2                                                 |     | 25  |     | ns     |

| CURRENT-LIMIT SENSE (PRIMARY)                            |                           |                                                                               |     |     |     | .=     |

| CS Limit Threshold                                       | Vcs lim                   | Over current sense limit threshold                                            |     | 120 |     | mV     |

| CS Leading Edge Blanking Time                            |                           |                                                                               |     | 150 |     | ns     |

| Current Source di/dt for Slope<br>Compensation           |                           | Switching period $(t_s) = 1/f_s$                                              |     | 20  |     | μA per |

## ADP1074

| Parameter                                        | Symbol          | Test Conditions/Comments                           | Min         | Тур        | Max         | Unit     |

|--------------------------------------------------|-----------------|----------------------------------------------------|-------------|------------|-------------|----------|

| Overcurrent Protection (OCP)<br>Comparator Delay |                 |                                                    |             | 40         |             | ns       |

| Time in OCP Before Entering<br>Hiccup Mode       |                 |                                                    |             | 1.5        |             | ms       |

| OCP Hiccup Time                                  |                 | See Input/Output Current-Limit Protection section  |             | 40         |             | ms       |

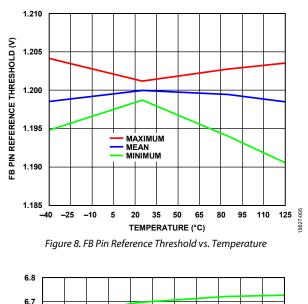

| FB PIN AND ERROR AMPLIFIER                       |                 |                                                    |             |            |             |          |

| Feedback Accuracy Voltage                        | V <sub>FB</sub> | $T_{J} = -40^{\circ}C \text{ to } +85^{\circ}C$    | 1.2 – 0.85% | +1.2       | 1.2 + 0.85% | v        |

| · · · · · · · · · · · · · · · · · · ·            |                 | $T_{J} = -40^{\circ}C \text{ to } +125^{\circ}C$   | 1.2 - 1.25% | +1.2       | 1.2 + 1.25% | v        |

| Temperature Coefficient                          |                 |                                                    |             |            | 76          | ppm/°C   |

| FB Input Bias Current                            |                 |                                                    | -100        | +1         | +100        | nA       |

| Transconductance                                 | gm              |                                                    | 230         | 250        | 270         | μA/V     |

| Output Current Clamp                             | 5               |                                                    |             | 200        |             | Pr. 1    |

| Minimum                                          |                 |                                                    |             | -57        |             | μA       |

| Maximum                                          |                 |                                                    |             | 43         |             | μA<br>μA |

| COMP Clamp Voltage                               |                 |                                                    |             | 45         |             | μΛ       |

| Minimum                                          |                 | 20 µA sinking current from COMP pin                |             | 0.7        |             | v        |

| Maximum                                          |                 | 20 µA sourcing current to COMP pin                 |             | 2.52       |             | v        |

| Open-Loop Gain                                   |                 |                                                    |             | 2.52<br>80 |             | dB       |

| Output Shunt Resistance                          |                 |                                                    |             | 5          |             | GΩ       |

| Gain Bandwidth Product                           |                 |                                                    |             | 1          |             | MHz      |

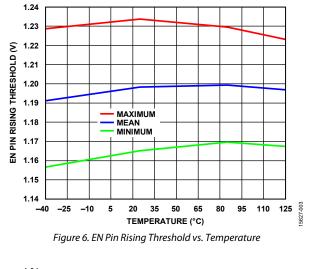

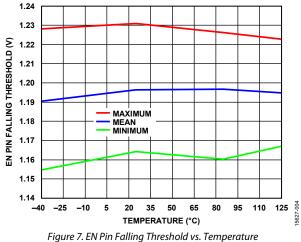

| PRECISION ENABLE THRESHOLD                       |                 |                                                    |             | I          |             |          |

|                                                  | M               |                                                    | 1 1 4       | 1 2        | 1.26        | v        |

| EN Threshold                                     | V <sub>EN</sub> | EN rising                                          | 1.14        | 1.2        | 1.20        |          |

| EN Hysteresis                                    |                 | V <sub>EN</sub> < 1.2 V<br>V <sub>EN</sub> > 1.2 V |             | 4<br>1     |             | μΑ       |

| EN Hystorosis Current                            |                 | $v_{\rm EN} > 1.2 v$                               |             | 3          |             | μA       |

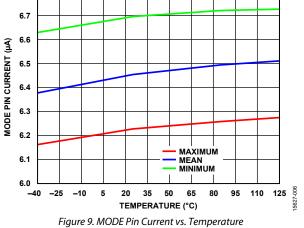

| EN Hysteresis Current<br>MODE PIN                |                 |                                                    |             | 3          |             | μA       |

| Light Load Mode Current                          |                 | Connect a resistor from MODE to AGND2              | 6           | 6.5        | 7           |          |

| Source                                           |                 | Connect a resistor from MODE to AGND2              | 0           | 0.5        | /           | μΑ       |

| Hysteresis                                       |                 |                                                    | 24          | 40         | 60          | mV       |

| TEMPERATURE                                      |                 |                                                    |             |            |             |          |

| Thermal Shutdown                                 |                 |                                                    |             | 155        |             | °C       |

| Hysteresis                                       |                 |                                                    |             | -15        |             | °C       |

| SOFT START SS1 AND SS2 PINS                      |                 |                                                    |             |            |             | -        |

| Primary Side SS1 Current                         |                 | During soft start only                             |             | 9.1        |             | μA       |

| Source                                           |                 | During solt start only                             |             | 2.1        |             | μ        |

| Secondary Side SS2 Current<br>Source             |                 | During soft start only, post handover              |             | 20         |             | μΑ       |

| SS2 Discharging Current                          |                 | During a fault condition or soft stop              |             | 30         |             | μA       |

| SYNC PIN                                         |                 |                                                    |             | 50         |             | μΛ       |

| Synchronization Range                            |                 |                                                    | 100         |            | 600         | kHz      |

| Input Pulse Width                                |                 |                                                    | 100         |            | 000         | ns       |

| Number of Cycles Before                          |                 |                                                    | 100         | 7          |             | Cycles   |

| Synchronization                                  |                 |                                                    |             | /          |             | Cycles   |

| Input Voltage                                    |                 |                                                    |             |            |             |          |

| Low                                              |                 |                                                    |             |            | 0.4         | v        |

| High                                             |                 |                                                    | 3           |            |             | v        |

| Leakage Current                                  |                 |                                                    |             |            | 1           | μA       |

| iCOUPLER DELAY                                   |                 |                                                    |             |            | •           | Pr' 1    |

| COMP Signal Delay Through                        |                 |                                                    |             | 600        |             | ns       |

|                                                  |                 |                                                    |             | 000        |             | ns       |

## ADP1074

| Parameter                                                 | Symbol | Test Conditions/Comments                                          | Min  | Тур  | Max  | Unit |

|-----------------------------------------------------------|--------|-------------------------------------------------------------------|------|------|------|------|

| FB, OVP, AND PGOOD<br>THRESHOLDS                          |        | Overvoltage (OV) threshold for PGOOD to toggle for FB and OVP pin | 1.3  | 1.36 | 1.42 | V    |

| FB Pin OV Hysteresis                                      |        |                                                                   |      | 36   |      | mV   |

| OVP Pin Hysteresis                                        |        |                                                                   |      | 36   |      | mV   |

| FB Pin UV Threshold                                       |        | Undervoltage (UV) threshold for PGOOD to toggle                   | 1.04 | 1.11 | 1.16 | V    |

| FB Pin UV Hysteresis                                      |        |                                                                   |      | 36   |      | mV   |

| OVP Comparator Delay<br>(Includes <i>i</i> Coupler Delay) |        |                                                                   |      | 320  |      | ns   |

| Time from Fault Condition to<br>PGOOD Toggling            |        | OVP pin fault to PGOOD toggling                                   |      | 90   |      | ns   |

|                                                           |        | FB pin OV/UV to PGOOD toggling                                    |      | 5    |      | μs   |

| OVP Pin Leakage Current                                   |        |                                                                   |      |      | 1    | μA   |

| PGOOD Pin Leakage Current                                 |        |                                                                   |      |      | 1    | μΑ   |

| OVP Hiccup                                                |        | Time in OVP before entering OVP hiccup mode                       |      | 200  |      | μs   |

|                                                           |        | Hiccup time triggered by OVP event                                |      | 200  |      | ms   |

$^{\rm 1}$  Short-circuit duration less than 1  $\mu s.$  Average power must conform to the limit shown in the Absolute Maximum Ratings section.

#### INSULATION AND SAFETY RELATED SPECIFICATIONS

#### Table 3.

| Parameter                                           | Symbol | Test Conditions/Comments                                                             | Min | Тур   | Max | Unit |

|-----------------------------------------------------|--------|--------------------------------------------------------------------------------------|-----|-------|-----|------|

| WIDE BODY SOIC                                      |        |                                                                                      |     |       |     |      |

| <i>i</i> Coupler                                    |        |                                                                                      |     |       |     |      |

| Rated Dielectric Insulation<br>Voltage              |        | 1 minute duration                                                                    |     | 5     |     | kV   |

| Minimum External Air Gap<br>(Clearance)             |        | Measured from input terminals to output terminals, shortest distance through air     | 7.6 |       |     | mm   |

| Minimum External Air Gap<br>(Creepage)              |        | Measured from input terminals to output terminals, shortest distance path along body | 7.6 |       |     | mm   |

| Minimum Internal Gap (Internal<br>Clearance)        |        | Insulation distance through insulation                                               |     | 0.030 |     | mm   |

| Tracking Resistance<br>(Comparative Tracking Index) | СТІ    | >4(                                                                                  |     | >400  |     | V    |

| Isolation Group                                     |        | Material Group II (DIN VDE 0110, 1/89, Table 1)                                      |     |       |     |      |

| LAND GRID ARRAY (LGA)                               |        |                                                                                      |     |       |     |      |

| <i>i</i> Coupler                                    |        |                                                                                      |     |       |     |      |

| Rated Dielectric Insulation<br>Voltage              |        | 1 minute duration                                                                    |     | 2.5   |     | kV   |

| Minimum External Air Gap<br>(Clearance)             |        | Measured from input terminals to output terminals, shortest distance through air     | 4   |       |     | mm   |

| Minimum External Air Gap<br>(Creepage)              |        | Measured from input terminals to output terminals, shortest distance path along body | 4   |       |     | mm   |

| Minimum Internal Gap (Internal<br>Clearance)        |        | Insulation distance through insulation                                               |     | 0.030 |     | mm   |

| Tracking Resistance<br>(Comparative Tracking Index) | СТІ    | >400                                                                                 |     |       | V   |      |

| Isolation Group                                     |        | Material Group I (DIN VDE 0110, 1/89, Table 1)                                       |     |       |     |      |

#### **REGULATORY INFORMATION**

See Table 4, Table 5, and the Insulation Lifetime section for details regarding recommended maximum working voltages for specific cross isolation waveforms and insulation levels.

| UL (Pending)                                                              | CSA (Pending)                                                                           | VDE (Pending)                                                                                                                                                                   | CQC (Pending)                                                         |

|---------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|

| Recognized Under UL 1577<br>Component Recognition<br>Program <sup>1</sup> | Approved under CSA Component<br>Acceptance Notice 5A                                    | Certified according to<br>DIN V VDE V 0884-10<br>(VDE V 0884-10):2006-12 <sup>2</sup>                                                                                           | Certified by<br>CQC11-471543-2012,<br>GB4943.1-2011:                  |

| Single Protection, 5000 V rms<br>Isolation Voltage                        | CSA 60950-1-07+A1+A2 and IEC 60950-1, second edition, +A1+A2 and IEC62368:              | Reinforced insulation,<br>maximum working<br>insulation voltage (V <sub>IORM</sub> ) =<br>849 V peak,<br>highest allowable<br>overvoltage (V <sub>IOTM</sub> ) =<br>8000 V peak | Basic insulation at 780 V rms<br>(1103 V peak)                        |

|                                                                           | Basic insulation at 780 V rms<br>(1103 V peak)                                          |                                                                                                                                                                                 | Reinforced insulation at 389 V rms<br>(552 V peak), tropical climate, |

|                                                                           | Reinforced insulation at 390 V rms<br>(552 V peak)                                      |                                                                                                                                                                                 | altitude ≤5000 meters                                                 |

|                                                                           | IEC 60601-1 Edition 3.1:                                                                |                                                                                                                                                                                 |                                                                       |

|                                                                           | Basic insulation (1 means of patient<br>protection (1 MOPP)), 490 V rms<br>(686 V peak) |                                                                                                                                                                                 |                                                                       |

|                                                                           | Reinforced insulation (2 MOPP),<br>238 V rms (325 V peak)                               |                                                                                                                                                                                 |                                                                       |

|                                                                           | CSA 61010-1-12 and IEC 61010-1 third edition:                                           |                                                                                                                                                                                 |                                                                       |

|                                                                           | Basic insulation at 300 V rms mains, 780 V secondary (1103 V peak)                      |                                                                                                                                                                                 |                                                                       |

| File (pending)                                                            | File (pending)                                                                          | File (pending)                                                                                                                                                                  | File (pending)                                                        |

Table 4. Regulatory Information for Wide Body SOIC Package

<sup>1</sup> In accordance with UL 1577, each product is proof tested by applying an insulation test voltage ≥6000 V rms for 1 sec. <sup>2</sup> In accordance with DIN V VDE V 0884-10, each product is proof tested by applying an insulation test voltage ≥1592 V peak for 1 sec (partial discharge detection limit = 5 pC). Note that the asterisk (\*) marking branded on the component designates DIN V VDE V 0884-10 approval.

#### Table 5. Regulatory Information for LGA Package

| UL (Pending)                                                              | CSA (Pending)                                                                                                       | VDE (Pending)                                                                                                      | CQC (Pending)                                                                                  |

|---------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

| Recognized Under UL 1577<br>Component Recognition<br>Program <sup>1</sup> | Approved under CSA Component<br>Acceptance Notice 5A                                                                | Certified according to<br>DIN V VDE V 0884-10<br>(VDE V 0884-10):2006-12 <sup>2</sup>                              | Certified by<br>CQC11-471543-2012,<br>GB4943.1-2011:                                           |

| Single Protection, 3000V rms<br>Isolation Voltage                         | CSA 60950-1-07+A1+A2 and IEC 60950-1,<br>second edition, +A1+A2 and IEC62368:                                       | Reinforced insulation,<br>$V_{IORM} = 565$ V peak,<br>$V_{IOTM} = 4242$ V peak<br>impulse voltage =<br>4242 V peak | Basic insulation at 400 V rms<br>(565 V peak)                                                  |

|                                                                           | Basic insulation at 400 V rms (565 V peak)<br>Reinforced insulation at 200 V rms<br>(283 V peak)                    |                                                                                                                    | Reinforced insulation at 200 V rms<br>(283 V peak), tropical climate,<br>altitude ≤5000 meters |

|                                                                           | IEC 60601-1 Edition 3.1:<br>Basic insulation (1 means of patient<br>protection (1 MOPP)), 250 V rms<br>(354 V peak) |                                                                                                                    |                                                                                                |

|                                                                           | CSA 61010-1-12 and IEC 61010-1 third edition:                                                                       |                                                                                                                    |                                                                                                |

|                                                                           | Basic insulation at 300 V rms mains, 400 V secondary (565 V peak)                                                   |                                                                                                                    |                                                                                                |

| File (pending)                                                            | File (pending)                                                                                                      | File (pending)                                                                                                     | File (pending)                                                                                 |

<sup>1</sup> In accordance with UL 1577, each product is proof tested by applying an insulation test voltage ≥3000 V rms for 1 sec.

<sup>2</sup> In accordance with DIN V VDE V 0884-10, each product is proof tested by applying an insulation test voltage ≥1059 V peak for 1 sec (partial discharge detection limit = 5 pC). Note that the asterisk (\*) marking branded on the component designates DIN V VDE V 0884-10 approval.

#### DIN V VDE V 0884-10 (VDE V 0884-10) INSULATION CHARACTERISTICS

This isolator is suitable for reinforced isolation within the safety limit data only. Maintenance of the safety data is ensured by protective circuits. Note that the asterisk (\*) marked on the package denotes DIN V VDE V 0884-10 approval for a 560 V peak working voltage.

| Description                                                 | Conditions                                                                                       | Symbol          | Characteristic | Unit              |

|-------------------------------------------------------------|--------------------------------------------------------------------------------------------------|-----------------|----------------|-------------------|

| Installation Classification per DIN VDE 0110                |                                                                                                  |                 |                |                   |

| For Rated Mains Voltage ≤ 150 V rms                         |                                                                                                  |                 | l to IV        |                   |

| For Rated Mains Voltage ≤ 300 V rms                         |                                                                                                  |                 | l to III       |                   |

| For Rated Mains Voltage ≤ 400 V rms                         |                                                                                                  |                 | l to ll        |                   |

| Climatic Classification                                     |                                                                                                  |                 | 40/105/21      |                   |

| Pollution Degree per DIN VDE 0110, Table 1                  |                                                                                                  |                 | 2              |                   |

| Maximum Working Insulation Voltage                          |                                                                                                  | VIORM           | 565            | VPEAK             |

| Input-to-Output Test Voltage, Method B1                     | $V_{IORM} \times 1.875 = V_{PR}$ , 100% production test, $t_m = 1$ sec, partial discharge < 5 pC | Vpr             | 1060           | VPEAK             |

| Input-to-Output Test Voltage, Method A                      | $V_{IORM} \times 1.6 = V_{PR}$ , $t_m = 60$ sec, partial discharge < 5 pC                        | VPR             |                |                   |

| After Environmental Tests Subgroup 1                        |                                                                                                  |                 | 905            | VPEAK             |

| After Input and/or Safety Test Subgroup 2<br>and Subgroup 3 | $V_{IORM} \times 1.2 = V_{PR}$ , $t_m = 60$ sec, partial discharge < 5 pC                        |                 | 679            | V <sub>PEAK</sub> |

| Highest Allowable Overvoltage                               | Transient overvoltage, $t_{TR} = 10$ seconds                                                     | VIOTM           | 7071           | VPEAK             |

| Surge Isolation Voltage Reinforced                          | $V_{PEAK} = 10 \text{ kV}$ , 1.2 $\mu$ s rise time, 50 $\mu$ s, 50% fall time                    | VIOSM           | 6000           | VPEAK             |

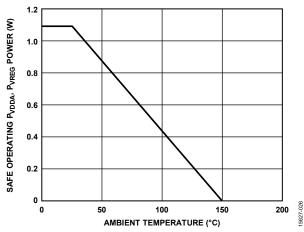

| Safety-Limiting Values                                      | Maximum value allowed in the event of a failure;<br>see Figure 2                                 |                 |                |                   |

| Case Temperature                                            |                                                                                                  | Ts              | 150            | °C                |

| Side 1 Current                                              |                                                                                                  | Is1             | 160            | mA                |

| Side 2 Current                                              |                                                                                                  | I <sub>S2</sub> | 170            | mA                |

| Insulation Resistance at Ts                                 | $V_{10} = 500 V$                                                                                 | Rs              | >109           | Ω                 |

Figure 2. Thermal Derative Curve, Dependence of Safety Limiting Values with Ambient Temperature per DINV VDE V 0884-10

#### DIN V VDE V 0884-10 (VDE V 0884-10) INSULATION CHARACTERISTICS

This isolator is suitable for reinforced isolation within the safety limit data only. Maintenance of the safety data is ensured by protective circuits. Note that the asterisk (\*) marked on the package denotes DIN V VDE V 0884-10 approval for a 560 V peak working voltage.

| Description                                                 | Conditions                                                                                       | Symbol          | Characteristic | Unit              |

|-------------------------------------------------------------|--------------------------------------------------------------------------------------------------|-----------------|----------------|-------------------|

| Installation Classification per DIN VDE 0110                |                                                                                                  |                 |                |                   |

| For Rated Mains Voltage ≤ 150 V rms                         |                                                                                                  |                 | l to IV        |                   |

| For Rated Mains Voltage ≤ 300 V rms                         |                                                                                                  |                 | l to III       |                   |

| For Rated Mains Voltage ≤ 400 V rms                         |                                                                                                  |                 | l to ll        |                   |

| Climatic Classification                                     |                                                                                                  |                 | 40/105/21      |                   |

| Pollution Degree per DIN VDE 0110, Table 1                  |                                                                                                  |                 | 2              |                   |

| Maximum Working Insulation Voltage                          |                                                                                                  | VIORM           | 565            | VPEAK             |

| Input-to-Output Test Voltage, Method B1                     | $V_{IORM} \times 1.875 = V_{PR}$ , 100% production test, $t_m = 1$ sec, partial discharge < 5 pC | Vpr             | 1060           | VPEAK             |

| Input-to-Output Test Voltage, Method A                      | $V_{IORM} \times 1.6 = V_{PR}$ , $t_m = 60$ sec, partial discharge < 5 pC                        | VPR             |                |                   |

| After Environmental Tests Subgroup 1                        |                                                                                                  |                 | 905            | VPEAK             |

| After Input and/or Safety Test Subgroup 2<br>and Subgroup 3 | $V_{IORM} \times 1.2 = V_{PR}$ , $t_m = 60$ sec, partial discharge < 5 pC                        |                 | 679            | V <sub>PEAK</sub> |

| Highest Allowable Overvoltage                               | Transient overvoltage, $t_{TR} = 10$ seconds                                                     | VTR             | 4242           | VPEAK             |

| Surge Isolation Voltage Reinforced                          | $V_{PEAK} = 10 \text{ kV}$ , 1.2 µs rise time, 50 µs, 50% fall time                              | VIOSM           | 6000           | VPEAK             |

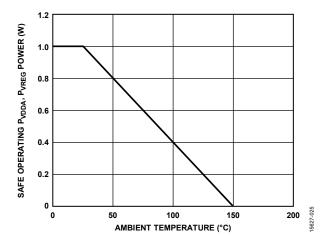

| Safety-Limiting Values                                      | Maximum value allowed in the event of a failure;<br>see Figure 3                                 |                 |                |                   |

| Case Temperature                                            |                                                                                                  | Ts              | 150            | °C                |

| Side 1 Current                                              |                                                                                                  | I <sub>S1</sub> | 160            | mA                |

| Side 2 Current                                              |                                                                                                  | I <sub>S2</sub> | 170            | mA                |

| Insulation Resistance at Ts                                 | $V_{10} = 500 V$                                                                                 | Rs              | >109           | Ω                 |

Figure 3. Thermal Derative Curve, Dependence of Safety Limiting Values with Ambient Temperature per DINV VDE V 0884-10

## ABSOLUTE MAXIMUM RATINGS

#### Table 8.

| Parameter                                | Rating          |

|------------------------------------------|-----------------|

| VIN, EN                                  | –0.3 V to +66 V |

| VDD2                                     | –0.3 V to +42 V |

| VREG1                                    | –0.3 V to +16 V |

| VREG2                                    | –0.3 V to +6 V  |

| NGATE, PGATE                             | –0.3 V to +16 V |

| RT, CS, SYNC, SS1, SS2, PGOOD, FB, COMP, | –0.3 V to +6 V  |

| OVP, MODE, DMAX, SR1, SR2                |                 |

| AGND1, PGND1, AGND2, PGND2               | ±0.3 V          |

| Common-Mode Transients <sup>1</sup>      | ±25 kV/μs       |

| Operating Temperature Range              | –40°C to +125°C |

| Storage Temperature Range                | –65°C to +150°C |

| Junction Temperature                     | 150°C           |

| Peak Solder Reflow Temperature           |                 |

| SnPb Assemblies (10 sec to 30 sec)       | 240°C           |

| RoHS Compliant Assemblies                | 260°C           |

| (20 sec to 40 sec)                       |                 |

| Electrostatic Discharge (ESD)            |                 |

| Charged Device Model (CDM)               | ±1250 V         |

| Human Body Model (HBM)                   | ±2 kV           |

<sup>1</sup> Refers to common-mode transients across the insulation barrier. Commonmode transients exceeding the absolute maximum rating can cause latch-up or permanent damage.

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

#### THERMAL RESISTANCE

Thermal performance is directly linked to printed circuit board (PCB) design and operating environment. Careful attention to PCB thermal design is required.

#### Table 9. Thermal Resistance<sup>1</sup>

| Package Type           | θ <sub>JA</sub> | θ」   | Unit |

|------------------------|-----------------|------|------|

| RW-24 (Wide Body SOIC) | 65.4            | 43.8 | °C/W |

| CC-24-6 (LGA)          | 62.1            | 43   | °C/W |

<sup>1</sup> Thermal impedance simulated values are based on JEDEC 2S2P thermal test board. See JEDEC JESD-51.

# Table 10. Maximum Continuous Working Voltage, WideBody SOIC1

| Waveform   | Maximum<br>Voltage (V <sub>PEAK</sub> ) | Constraint               |

|------------|-----------------------------------------|--------------------------|

| AC Voltage |                                         |                          |

| Bipolar    | 565                                     | 50-year minimum lifetime |

| Unipolar   | 1131                                    | 50-year minimum lifetime |

| DC Voltage | 1131                                    | 50-year minimum lifetime |

<sup>1</sup> Refers to continuous voltage magnitude imposed across the isolation barrier. See the Insulation Lifetime section for more details.

#### Table 11. Maximum Continuous Working Voltage, LGA<sup>1</sup>

| Waveform   | Maximum<br>Voltage (V <sub>РЕАК</sub> ) | Constraint               |

|------------|-----------------------------------------|--------------------------|

| AC Voltage |                                         |                          |

| Bipolar    | 565                                     | 50-year minimum lifetime |

| Unipolar   | 909                                     | Limited by creepage      |

| DC Voltage | 565                                     | Limited by creepage      |

<sup>1</sup> Refers to continuous voltage magnitude imposed across the isolation barrier. See the Insulation Lifetime section for more details.

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

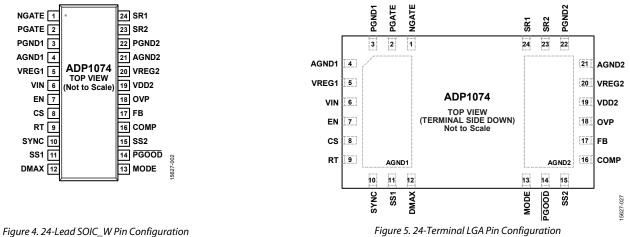

## **PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS**

#### Table 12. Pin Function Descriptions

| Pin No. | Mnemonic | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|---------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | NGATE    | Driver Output for the Main Power MOSFET on the Primary Side. Multiple function pin. Connect a resistor from NGATE to PGND1 to set up the predetermined dead time between PGATE and SR2.                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 2       | PGATE    | Driver for the Active Clamp MOSFET of the Forward Topology. This pin is referenced to PGND1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 3       | PGND1    | Power Ground on the Primary Side. Star connect this pin to AGND1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 4       | AGND1    | Analog Ground on the Primary Side. Star connect this pin to PGND1. Use this pin to differentially sense the primary current sensed with the sense resistor between the CS and AGND1 pins.                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 5       | VREG1    | 8 V Output for the MOSFET Drivers. Connect 1 $\mu$ F or greater at this pin. Do not put an external load on this pin. Reference this pin to PGND1.                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 6       | VIN      | Input Voltage. Connect a 4.7 μF capacitor to this pin. The size of this capacitor can be reduced if the input<br>voltage to this pin is guaranteed stable. Reference this pin to PGND1.                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 7       | EN       | Precision Enable Input. The controller is enabled when the voltage at the EN pin is above the EN threshold voltage. Soft stop is enabled when EN drops below the EN threshold voltage. This pin also has a programmable EN hysteresis. Reference this pin to AGND1.                                                                                                                                                                                                                                                                                                                                       |

| 8       | CS       | Input Current Sensing. This pin senses the input pulse width modulated current. Place a current sense resistor between the source terminal of the power MOSFET and PGND1. This current sense resistor sets up the input current limit. This pin is also used for an external slope compensator. Connect a resistor from CS to the current sense resistor to generate a voltage ramp for the slope compensation. Reference this pin to AGND1. Connect a 33 pF to 100 pF capacitor to this pin to act as a resistor capacitor (RC) filter along with the slope compensation resistor in noisy environments. |

| 9       | RT       | Switching Period Resistor. Connect two resistors in series that sum up to the appropriate resistor from RT to AGND1 to set the switching frequency. See the DMAX pin for more information. Also see the Frequency Setting (RT Pin) section and the Maximum Duty Cycle section for the relevant equations.                                                                                                                                                                                                                                                                                                 |

| 10      | SYNC     | Frequency Synchronization. Connect an external clock to the SYNC pin to synchronize the internal oscillator to this external clock frequency. Connect SYNC to AGND1 if this feature is not used. It is recommended that the SYNC frequency be within 10% of the frequency set by the RT pin.                                                                                                                                                                                                                                                                                                              |

| 11      | SS1      | Soft Start 1. Connect a capacitor at this pin to set up the open-loop soft start time. Reference this pin to AGND1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 12      | DMAX     | Maximum Duty Cycle Control. Connect DMAX to the center tap of the resistive divider at the RT pin to set up the maximum duty cycle. See the Frequency Setting (RT Pin) section and the Maximum Duty Cycle section for the relevant equations.                                                                                                                                                                                                                                                                                                                                                             |

| 13      | MODE     | Light Load Mode Setting. Connect MODE to AGND2 to disable discontinuous conduction mode (DCM) operation, or to a high logic (2.5 V or higher, such as the VREG2 pin) to force LLM operation, or to a resistor to set up a fixed LLM threshold voltage.                                                                                                                                                                                                                                                                                                                                                    |

| 14      | PGOOD    | Power Good Pin. Open-drain output. Connect a pull-up resistor from PGOOD to VREG2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 15      | SS2      | Soft Start on the Secondary Side. Connect a capacitor from SS2 to AGND2 to set up the soft start time on the secondary side.                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |