## High Power DC/DC Step-Up Controller

### **FEATURES**

- High Voltage: Operation Up to 60V

- High Current: N-Channel Drive Handles Up to 10,000pF Gate Capacitance

- Programmable Average Current Limiting

- 5V Reference Output with 10mA External Loading Capability

- Fixed Frequency Current Mode Operation

- Oscillator Synchronizable Up to 200kHz

- Undervoltage Lockout with Hysteresis

- Programmable Start Inhibit for Power Supply Sequencing and Protection

- User Adjustable Slope Compensation

### **APPLICATIONS**

- High Power Single Board Systems

- Distributed Power Converters

- Industrial Control Systems

- Lead-Acid Battery Back-Up Systems

- Automotive and Heavy Equipment

## DESCRIPTION

The LT®1680 is a high power, current mode switching power supply controller optimized for boost topologies. The IC drives an N-channel MOSFET switch for DC/DC converter applications up to 60V input. A high current gate drive output handles up to 10,000pF gate capacitance, enabling the construction of high power DC/DC converters. Current sense common mode range up to 60V allows current sensing to be referenced to the input supply, eliminating the need for sense blanking circuits.

The LT1680 incorporates programmable average current limiting allowing accurate limiting of DC current in the magnetics, independent of ripple current. User adjustable slope compensation provides stable operation at duty cycles up to 90%.

The LT1680 operating frequency is programmable and can be synchronized up to 200kHz. Minimum off-time operation provides switch protection. The IC also incorporates a soft start feature that is gated by both shutdown and undervoltage lockout conditions.

(C), LTC and LT are registered trademarks of Linear Technology Corporation.

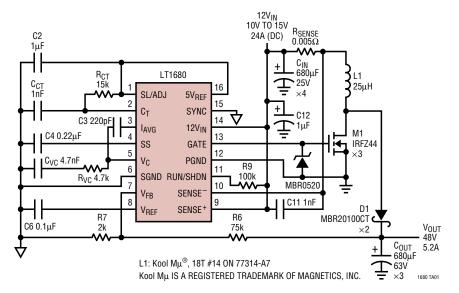

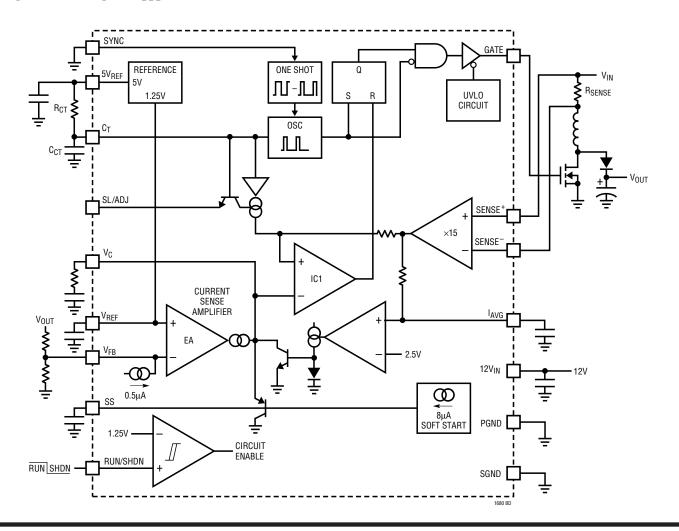

## TYPICAL APPLICATION

12V to 48V, 250W Boost Converter

## **ABSOLUTE MAXIMUM RATINGS**

#### (Note 1)

| Power Supply Voltage (12V <sub>IN</sub> ) | 0.3V to 20V                       |

|-------------------------------------------|-----------------------------------|

| Sense Amplifier Input Common Mc           | ode0.3V to 60V                    |

| GATE Pin Voltage                          | -0.3V to 12V <sub>IN</sub> + 0.3V |

| RUN/SHDN Pin Voltage                      | $-0.3V$ to $12V_{IN}$             |

| All Other Pin Voltages                    | 0.3V to 7V                        |

| 5V Reference Output Current               | 65mA                              |

| Operating Ambient Temperature Ra          | ange                              |

| LT1680C                                   | 0°C to 70°C                       |

| LT1680I                                   | 40°C to 85°C                      |

| Storage Temperature Range                 | 65°C to 150°C                     |

| Lead Temperature (Soldering, 10 s         | ec) 300°C                         |

|                                           |                                   |

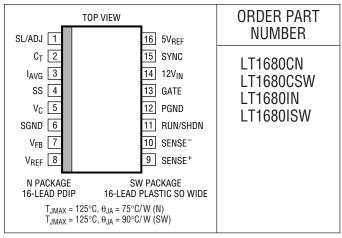

## PACKAGE/ORDER INFORMATION

Consult factory for parts specified with wider operating temperature ranges.

## **ELECTRICAL CHARACTERISTICS**

The ullet denotes the specifications which apply over the full operating temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$ .  $12V_{IN} = 12V$ ,  $V_{VC} = 2V$ ,  $V_{FB} = V_{REF} = 1.25V$ ,  $C_{GATE} = 3000 pF$ , unless otherwise noted.

| SYMBOL                | PARAMETER                                                                                                              | CONDITIONS                                 |   | MIN            | TYP                 | MAX            | UNITS        |

|-----------------------|------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|---|----------------|---------------------|----------------|--------------|

| Supply and            | I Protection                                                                                                           |                                            |   |                |                     |                |              |

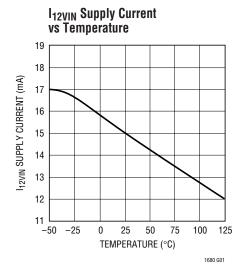

| I <sub>12VIN</sub>    | DC Active Supply Current (Note 2)                                                                                      | Gate Output On<br>Gate Output Off          | • |                | 15<br>12            | 22             | mA<br>mA     |

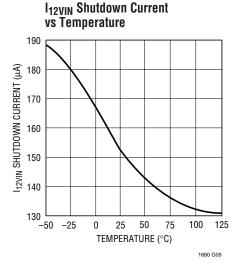

|                       | DC Standby Supply Current                                                                                              | V <sub>RUN</sub> < 0.5V                    | • |                | 150                 | 250            | μΑ           |

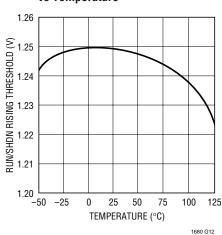

| V <sub>RUN/SHDN</sub> | Shutdown Rising Threshold                                                                                              |                                            | • | 1.15           | 1.25                | 1.35           | V            |

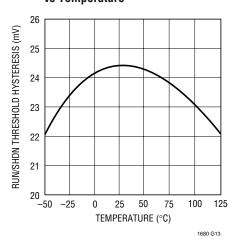

| V <sub>SSHYST</sub>   | Shutdown Threshold Hysteresis                                                                                          |                                            |   |                | 25                  |                | mV           |

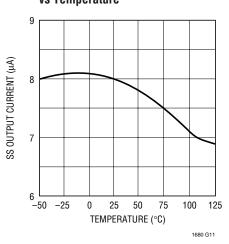

| I <sub>SS</sub>       | Soft Start Charge Current                                                                                              |                                            | • | 5              | 8                   | 14             | μΑ           |

| V <sub>UVLO</sub>     | Undervoltage Lockout Threshold - Falling<br>Undervoltage Lockout Threshold - Rising<br>Undervoltage Lockout Hysteresis |                                            | • | 8.20<br>200    | 9.00<br>9.35<br>350 | 9.75<br>9.95   | V<br>V<br>mV |

| 5V Referen            | nce                                                                                                                    |                                            |   |                |                     |                |              |

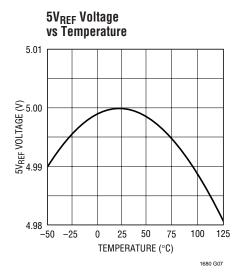

| V <sub>REF5</sub>     | 5V Reference Voltage                                                                                                   | Line, Load and Temperature                 | • | 4.75           | 5                   | 5.25           | V            |

|                       | 5V Reference Line Regulation                                                                                           | 10V ≤ 12V <sub>IN</sub> ≤ 15V              | • |                | 3                   | 5              | mV/V         |

| I <sub>REF5</sub>     | 5V Reference Load Range - DC<br>Pulse                                                                                  |                                            | • |                |                     | 10<br>20       | mA<br>mA     |

|                       | 5V Reference Load Regulation                                                                                           | 0 ≤ I <sub>REF5</sub> ≤ 20mA               | • |                | -1.25               | -2             | V/A          |

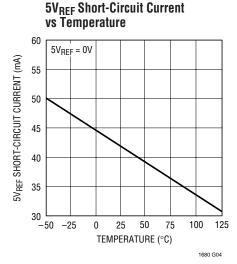

| I <sub>SC</sub>       | 5V Reference Short-Circuit Current                                                                                     |                                            |   |                | 45                  |                | mA           |

| Error Ampl            | ifier                                                                                                                  |                                            |   |                |                     |                |              |

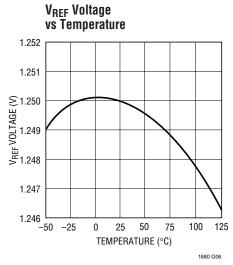

| V <sub>FB</sub>       | Error Amplifier Reference Voltage                                                                                      | Measured at Feedback Pin                   | • | 1.242<br>1.235 | 1.250               | 1.258<br>1.265 | V            |

| I <sub>FB</sub>       | Feedback Input Current                                                                                                 | V <sub>FB</sub> = V <sub>REF</sub>         | • | 0.1            | 0.5                 | 1.0            | μΑ           |

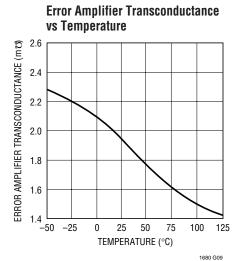

| g <sub>m</sub>        | Error Amplifier Transconductance                                                                                       |                                            | • | 1200           | 2000                | 3200           | μmho         |

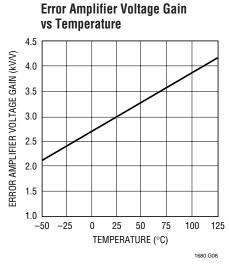

| A <sub>V</sub>        | Error Amplifier Voltage Gain                                                                                           |                                            | • | 1500           | 3000                |                | V/V          |

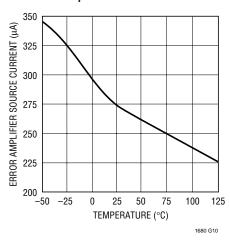

| I <sub>VC</sub>       | Error Amplifier Source Current<br>Error Amplifier Sink Current                                                         | V <sub>FB</sub> – V <sub>REF</sub> = 500mV | • | 200<br>280     | 275<br>400          |                | μA<br>μA     |

| $V_{VC}$              | Absolute V <sub>C</sub> Clamp Voltage                                                                                  | Measured at V <sub>C</sub> Pin             |   |                | 3.5                 |                | V            |

## **ELECTRICAL CHARACTERISTICS**

The  $\bullet$  denotes the specifications which apply over the full operating temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$ .  $12V_{IN} = 12V$ ,  $V_{VC} = 2V$ ,  $V_{FB} = V_{REF} = 1.25V$ ,  $C_{GATE} = 3000 pF$ , unless otherwise noted.

| SYMBOL             | PARAMETER                                                                                                   | CONDITIONS                                                                        |   | MIN            | TYP                | MAX                     | UNITS       |

|--------------------|-------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|---|----------------|--------------------|-------------------------|-------------|

| Error Amp          | olifier                                                                                                     |                                                                                   |   |                |                    |                         |             |

| V <sub>SENSE</sub> | Peak Current Limit Threshold<br>Average Current Limit Threshold                                             | Measured at Sense Inputs Measured at Sense Inputs, V <sub>CMSENSE</sub> = 10V     | • | 170<br>110     | 190<br>120         | 130                     | mV<br>mV    |

| V <sub>IAVG</sub>  | Average Current Limit Threshold                                                                             | Measured at I <sub>AVG</sub> Pin                                                  |   |                | 2.5                |                         | V           |

| Current S          | ense Amplifier                                                                                              |                                                                                   |   |                |                    |                         |             |

| A <sub>V</sub>     | Amplifier DC Gain                                                                                           | Measured at I <sub>AVG</sub> Pin                                                  |   |                | 15                 |                         | V/V         |

| V <sub>OS</sub>    | Amplifier Input Offset Voltage                                                                              | 2V < V <sub>CMSENSE</sub> < 60V,<br>SENSE <sup>+</sup> - SENSE <sup>-</sup> = 5mV | • | 0.1            |                    |                         | mV          |

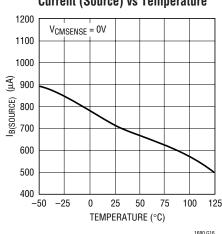

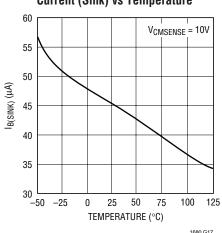

| I <sub>BIAS</sub>  | Input Bias Current                                                                                          | Sink (V <sub>CMSENSE</sub> > 5V)<br>Source (V <sub>CMSENSE</sub> = 0V)            | • |                | 45<br>700          | 75<br>1200              | μA<br>μA    |

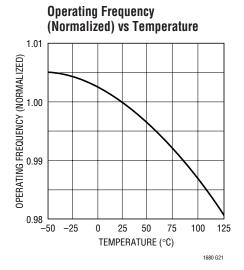

| Oscillator         |                                                                                                             |                                                                                   |   |                |                    |                         |             |

| $f_0$              | Operating Frequency, Free Run<br>Frequency Programming Error                                                | $f_0 \le 200 \text{kHz}, R_{CT} = 16.9 \text{k}, C_{CT} = 1000 \text{pF}$         | • | -5             |                    | 200<br>5                | kHz<br>%    |

| I <sub>CT</sub>    | Timing Capacitor Discharge Current                                                                          | LT1680C<br>LT1680I                                                                | • | 2.20<br>2.10   | 2.5<br>2.5         | 2.75<br>2.75            | mA<br>mA    |

| V <sub>SYNC</sub>  | SYNC Input Threshold                                                                                        | Rising Edge                                                                       | • | 0.8            |                    | 2.0                     | V           |

| f <sub>SYNC</sub>  | SYNC Frequency Range                                                                                        | f <sub>SYNC</sub> ≤ 200kHz                                                        | • | f <sub>0</sub> |                    | 1.4f <sub>0</sub>       |             |

| Output Dr          | ivers                                                                                                       |                                                                                   |   |                |                    |                         |             |

| V <sub>GATE</sub>  | Undervoltage Output Clamp<br>Standby Mode Output Clamp<br>Gate Output On Voltage<br>Gate Output Off Voltage | $12V_{IN} \le 8.2V$ $V_{RUN} < 0.5V$                                              | • | 11             | 0.4<br>11.9<br>0.4 | 0.7<br>0.1<br>12<br>0.7 | V<br>V<br>V |

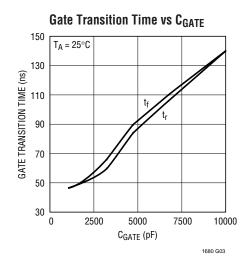

| t <sub>GATER</sub> | Gate Output Rise Time                                                                                       |                                                                                   | • |                | 60                 | 200                     | ns          |

| t <sub>GATEF</sub> | Gate Output Fall Time                                                                                       |                                                                                   | • |                | 60                 | 140                     | ns          |

**Note 1:** Absolute Maximum Ratings are those values beyond which the life of a device may be impaired.

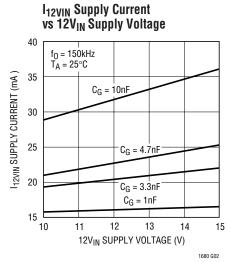

**Note 2:** Supply current specification does not include external FET gate charge currents. Actual supply currents will be higher and vary with operating frequency, operating voltages and the type of external FETs used. See Applications Information.

## TYPICAL PERFORMANCE CHARACTERISTICS

## TYPICAL PERFORMANCE CHARACTERISTICS

## Error Amplifier Source Current vs Temperature

## SS Output Current vs Temperature

## RUN/SHDN Rising Threshold vs Temperature

## RUN/SHDN Threshold Hysteresis vs Temperature

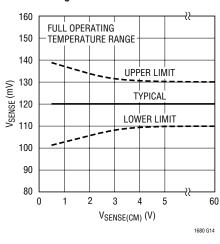

Average Current Limit Threshold Sense Voltage vs Common Mode Voltage

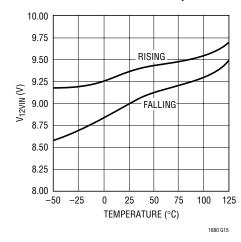

**UVLO** Thresholds vs Temperature

#### Sense Amplifier Input Bias Current (Source) vs Temperature

#### Sense Amplifier Input Bias Current (Sink) vs Temperature

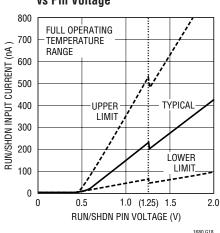

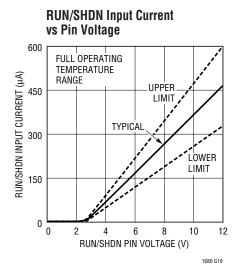

## RUN/SHDN Input Current vs Pin Voltage

## TYPICAL PERFORMANCE CHARACTERISTICS

## PIN FUNCTIONS

**SL/ADJ (Pin 1):** Slope Compensation Adjustment. Allows increased slope compensation for certain high duty cycle applications. Resistive loading of this pin increases effective slope compensation. A resistor divider from the  $5V_{REF}$  pin can tailor the onset of additional slope compensation to specific regions in each switch cycle. Pin can be floated or connected to  $5V_{REF}$  if no additional slope compensation is required. (See Applications Information section for slope compensation details.)

$C_T$  (Pin 2): Oscillator Timing Pin. Connect a capacitor ( $C_{CT}$ ) to ground and a pull-up resistor ( $R_{CT}$ ) to the  $5V_{REF}$  supply. Typical values are  $C_{CT} = 1000 pF$  and  $10k \le R_{CT} \le 30k$ .

$I_{AVG}$  (Pin 3): Average Current Limit Integration. The frequency response characteristic is set using  $50k\Omega$  output impedance of this pin and external capacitor. The external capacitor is typically connected from the  $I_{AVG}$  pin to the  $V_C$  pin, but can also be connected from the  $I_{AVG}$  pin to ground. Connecting the capacitor from the  $I_{AVG}$  pin to the  $V_C$  pin uses an internal gain block to form an active integrator, minimizing the capacitance required for stable operation. A typical value for this integration capacitor is 220pF from  $I_{AVG}$  to  $V_C$ . Shorting this pin to SGND will disable the average current limit function.

**SS (Pin 4):** Soft Start. Generates ramping threshold for regulator current limit during start-up and after UVLO events by sourcing about 8μA into an external capacitor.

**V<sub>C</sub>** (**Pin 5**): Error Amplifier Output. RC load creates dominant compensation in power supply regulation feedback loop to provide optimum transient response. (See Applications Information section for compensation details.)

**SGND (Pin 6):** Small-Signal Ground. Connect to negative terminal of  $C_{OLIT}$ .

$V_{FB}$  (Pin 7): Error Amplifier Inverting Input. Used as voltage feedback input node for regulator loop. Pin sources about  $0.5\mu A$  DC bias current to protect from an open feedback path condition.

$V_{REF}$  (Pin 8): Bandgap Generated Voltage Reference Decoupling. Connect a capacitor to signal ground. (Typical capacitor value  $\approx 0.1 \mu F$ .)

**SENSE**<sup>+</sup> (**Pin 9**): Current Sense Amplifier Inverting Input. Connect to most positive (DC) terminal of current sense resistor.

**SENSE**<sup>-</sup> (**Pin 10**): Current Sense Amplifier Noninverting Input. Connect to most negative (DC) terminal of current sense resistor.

## PIN FUNCTIONS

**RUN/SHDN (Pin 11):** Precision Referenced Shutdown. Can be used as logic level input for shutdown control or as an analog monitor for input supply undervoltage protection, etc. IC is enabled when RUN/SHDN pin rising edge exceeds 1.25V. 25mV of hysteresis helps assure stable mode switching. All internal functions are disabled in shutdown mode. If this function is not desired, connect RUN/SHDN to  $12V_{\rm IN}$  (typically through a 100k resistor). See Applications Information.

**PGND** (Pin 12): Power Ground. References the output switch and internal driver control circuits. Connect with low impedance trace to  $V_{\text{IN}}$  decoupling capacitor negative (ground) terminal.

**GATE (Pin 13):** Driver Output. Connect to gate of external power FET switch.

**12V**<sub>IN</sub> (**Pin 14**): 12V Power Supply Input. Bypass with at least  $1\mu$ F to PGND.

**SYNC** (Pin 15): Oscillator Synchronization Pin with TTL-Level Compatible Input. Input drives internal rising edge triggered one shot; SYNC signal on/off times should be  $\geq 1 \mu s$  (10% to 90% duty cycle at 100kHz). Does not contain internal pull-up. Connect to SGND if not used.

$5V_{REF}$  (Pin 16): 5V Reference Output. Allows connection of external loads up to 10mA DC. Reference is not available during shutdown. Typically bypassed with at least  $1\mu F$  capacitor to SGND.

## **BLOCK DIAGRAM**

## **OPERATION**

#### **Basic Control Loop**

The LT1680 uses a constant frequency, current mode architecture. The timing of the IC is provided through an internal oscillator circuit that can be synchronized to an external clock and is programmable to operate at frequencies up to 200kHz. The oscillator creates a modified sawtooth wave at its timing node ( $C_T$ ) with a slow charge, rapid discharge characteristic.

During typical boost converter operation, the MOSFET switch is enabled at the start of each oscillator cycle. The switch stays enabled until the current through the switched inductor, sensed via the voltage across a series sense resistor ( $R_{SENSE}$ ), is sufficient to trip the current comparator (IC1) and reset the RS latch. When the switch is disabled, the inductor current is redirected to the supply output. If the current comparator threshold is not reached throughout the entire oscillator charge period, the RS latch is bypassed and the main switch is disabled during the oscillator discharge time. This "minimum off time" protects the switch, and is typically about 1 $\mu$ s.

The current comparator trip threshold is set on the  $V_{C}$  pin, which is the output of a transconductance amplifier, or error amplifier (EA). The error amplifier integrates the difference between a feedback voltage (on the  $V_{FB}$  pin) and an internal bandgap generated reference voltage of 1.25V, forming a signal that represents required load current. If the supplied current is insufficient for a given load, the output will droop, thus reducing the feedback voltage. The error amplifier responds by forcing current out of the  $V_{C}$  pin, increasing the current comparator threshold. Thus, the circuit will servo until the provided current is equal to the required load and the average output voltage is at the value programmed by the feedback resistors.

#### **Input Average Current Limit**

The output of the sense amplifier is monitored by a single pole integrator comprised of an external capacitor on the  $I_{AVG}$  pin and an output impedance of approximately  $50k\Omega$ . If this averaged value signal exceeds a level corresponding to 120mV across the external sense resistor, the current comparator threshold is clamped and cannot continue to rise in response to the error amplifier. Thus, if average input current requirements exceed 120mV/R\_SENSE, the

supply will current limit and the output voltage will fall out of regulation. The average current limit circuit monitors the sense amplifier output without slope compensation or ripple current contributions. Therefore, the average input current limit threshold is unaffected by duty cycle.

#### **Undervoltage Lockout**

The LT1680 employs an undervoltage lockout circuit (UVLO) that monitors the  $12V_{\rm IN}$  supply rail. This circuit disables the output drive capability of the LT1680 if the 12V supply drops below 9V. Unstable mode switching is prevented through 350mV of UVLO threshold hysteresis.

#### Shutdown

The LT1680 can be put into low current shutdown by pulling the RUN/SHDN pin low, disabling all circuit functions. The shutdown threshold is a bandgap referred voltage of 1.25V typical. Use of a precision threshold on the shutdown circuit enables use of this pin for undervoltage protection of the  $V_{IN}$  supply and/or power supply sequencing.

#### **Soft Start**

The LT1680 incorporates a soft start function that operates by slowly increasing current limit. This limit is controlled by internally clamping the  $V_{C}$  pin to a low voltage that climbs with time as an external capacitor on the SS pin is charged with about  $8\mu A$ . This forces a graceful climb of output current source capability, and thus a graceful increase in output voltage until steady-state regulation is achieved. The soft start timing capacitor is clamped to ground during shutdown and during undervoltage lockout, yielding a graceful output recovery from either condition.

#### **5V Internal Reference**

Power for the oscillator timing elements and most other internal LT1680 circuits is derived from an internal 5V reference, accessible at the  $5V_{REF}$  pin. This supply pin can be loaded with up to 10mA DC (20mA pulsed) for convenient biasing of local elements such as control logic, etc.

## **OPERATION**

#### Slope Compensation

For duty cycles greater than 50%, slope compensation is required to prevent current mode duty cycle instability in the regulator control loop. The LT1680 employs internal slope compensation that is adequate for most applica-

tions. However, if additional slope compensation is desired, it is available through the SL/ADJ pin. Excessive slope compensation will cause reduction in maximum load current capability and is generally not desirable.

## APPLICATIONS INFORMATION

### **R<sub>SENSE</sub> Selection for Input Current Limit**

$R_{SENSE}$  generates a voltage that is proportional to the inductor current for use by the LT1680 current sense amplifier. The value of  $R_{SENSE}$  is based on the required input current. The average current limit function has a typical threshold of 120mV/ $R_{SENSE}$ , or:

$$R_{SENSE} = 120 \text{mV/I}_{LIMIT}$$

Operation with  $V_{SENSE}$  common mode voltage below 4.5V may slightly degrade current limit accuracy. See Average Current Limit Threshold Tolerance vs Common Mode Voltage in the Typical Performance Characteristics section for more information.

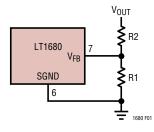

#### **Output Voltage Programming**

Output voltage is programmed through a resistor feed-back network to the  $V_{FB}$  pin (Pin 7) on the LT1680. This pin is the inverting input of the error amplifier, which is internally referenced to 1.25V. The divider is ratioed to provide 1.25V at the  $V_{FB}$  pin when the output is at its desired value. Output voltage is thus set following the relation:

$$V_{OUT} = 1.25V(1 + R2/R1)$$

when an external resistor divider is connected to the output as shown in Figure 1.

Figure 1. Programming LT1680 Output Voltage

If high value feedback resistors are used, the input bias current of the  $V_{FB}$  pin (1µA maximum) could cause a slight increase in output voltage. A Thevenin resistance at the  $V_{FB}$  pin of <5k is recommended.

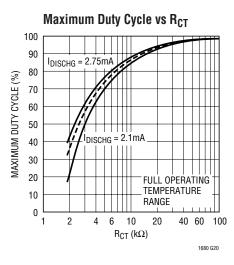

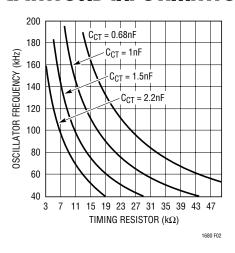

### Oscillator Components $R_{CT}$ and $C_{CT}$

The LT1680 oscillator creates a modified sawtooth at its timing node ( $C_T$ ) with a slow charge, rapid discharge characteristic. The discharge time ( $t_{DISCH}$ ) corresponds to the minimum off time of the PWM controller. This limits maximum duty cycle ( $DC_{MAX}$ ) to:

$$DC_{MAX} = 1 - (t_{DISCH})(f_0)$$

This relation corresponds to the minimum value of the timing resistor ( $R_{CT}$ ), which can be determined according to the following relation ( $R_{CT}$  vs  $DC_{MAX}$  graph appears in the Typical Performance Characteristics section):

$$R_{CT(MIN)} \approx [(0.8)(10^{-3})(1 - DC_{MAX})]^{-1}$$

Values for  $R_{CT} > 15k$  yield maximum duty cycles above 90%. Given a timing resistor value, the value of the timing capacitor ( $C_{CT}$ ) can then be determined for desired operating frequency ( $f_{O}$ ) using the relation:

$$C_{CT} \approx \frac{\left(1/f_{0}\right) - \left(100\right)\!\!\left(10^{-9}\right)}{\left(R_{CT} / 1.85\right) + \frac{1.75}{\left(2.5\right)\!\!\left(10^{-3}\right) - \left(3.375 / R_{CT}\right)}}$$

A plot of Operating Frequency vs  $R_{CT}$  and  $C_{CT}$  is shown in Figure 2. Typical 100kHz operational values are  $C_{CT}$  = 1000pF and  $R_{CT}$  = 16.9k.

Figure 2. Operating Frequency vs R<sub>CT</sub>, C<sub>CT</sub>

#### **Average Current Limit**

The average current limit function is implemented using an external capacitor ( $C_{AVG}$ ) connected either from the  $I_{AVG}$  pin to the  $V_C$  pin or from the  $I_{AVG}$  pin to SGND. This capacitor forms a single-pole integrator with the  $50 k\Omega$  output impedance of the  $I_{AVG}$  pin. Precise integration frequencies can be determined using a ground reference integration capacitor using the relation:

$$f_{-3dB} = (3.2)(10^{-6})/C_{AVG}$$

Connecting a capacitor from the  $I_{AVG}$  pin to the  $V_C$  pin uses an internal gain block to form an active integrator circuit, minimizing the required capacitance for stable operation. A typical value for this integration capacitor is 220pF from  $I_{AVG}$  to  $V_C$ .

Shorting the I<sub>AVG</sub> pin to SGND will disable the average current limit function.

#### **Soft Start Programming**

The current control pin ( $V_C$ ) limits sensed inductor current to zero at voltages less than a transistor  $V_{BE}$ , to full average current limit at  $V_C = V_{BE} + 1.8 \text{V}$ . This generates a 1.8V full regulation range for average load current. An internal voltage clamp forces the  $V_C$  pin to a  $V_{BE} - 100 \text{mV}$  above the SS pin voltage. This 100 mV "dead zone" assures 0% duty cycle operation at the start of the soft start cycle or when the soft start pin is pulled to ground. Given the typical soft start current of  $8\mu\text{A}$  and a soft start timing

capacitor  $C_{SS}$ , the start up delay time to full available average current will be:

$$t_{SS} = (1.5)(10^5)(C_{SS})$$

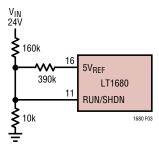

# Shutdown Function—Input Undervoltage Detect and Threshold Hysteresis

The LT1680 RUN/SHDN pin uses a bandgap generated reference threshold of about 1.25V. This precision threshold allows use of the RUN/SHDN pin for both logic-level shutdown applications and analog monitoring applications such as power supply sequencing.

Because an LT1680 controlled converter is a power transfer device, a voltage that is lower than expected on the input supply could require currents that exceed the sourcing capabilities of that supply, causing the system to lock-up in an undervoltage state. Input supply start-up protection can be achieved by enabling the RUN/SHDN pin using a resistor divider from the input supply to ground. Setting the divider output to 1.25V when the supply is almost fully enabled prevents the LT1680 regulator from drawing large currents until the input supply is able to supply the required power.

If additional hysteresis is desired for the enable function, an external feedback resistor can be used from the LT1680 regulator output. If connection to the regulator output is not desired, the  $5V_{REF}$  internal supply pin can be used. Figure 3 shows an input supply sequencing configuration on a 24V input converter. This configuration yields an enable condition of 90%  $V_{IN}$  (~21.5V) with about 10% threshold hysteresis.

The shutdown function can be disabled by connecting the RUN/SHDN pin to the  $12V_{IN}$  rail. This pin is internally

Figure 3. Input Supply Sequencing Programming

clamped to 2.5V through a 20k series input resistance and will therefore draw 0.5mA when tied directly to 12V. This additional current can be minimized by making the connection through an external resistor (100k is typically used).

#### **Oscillator Synchronization**

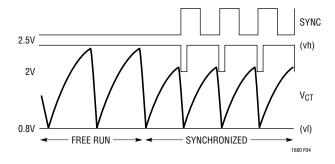

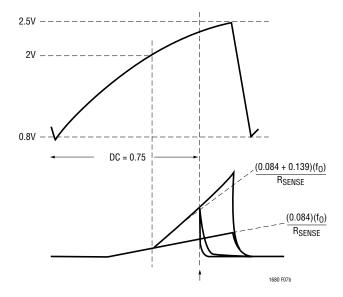

The LT1680 oscillator generates a modified sawtooth waveform at the  $C_T$  pin between low and high thresholds of 0.8V (vl) and 2.5V (vh) respectively. The oscillator can be synchronized by driving a TTL level pulse into the SYNC pin. This pin connects to a one shot circuit that reduces the oscillator high threshold to 2V for about 200ns. The SYNC input signal should have minimum on/off times of  $\geq 1 \mu s$ .

Figure 4. Free Run and Synchronized Oscillator Waveforms (at  $C_T$  Pin)

#### **Inductor Selection**

The inductor for an LT1680 converter is selected based on output power, operating frequency and efficiency requirements. Generally, the selection of inductor value can be reduced to desired maximum ripple current in the inductor  $(\Delta I)$ . For a boost converter, the minimum inductor value for a given operating ripple current can be determined using the following relation:

$$L_{MIN} = \frac{V_{IN} (V_{OUT} - V_{IN})}{(\Delta I)(f_0)(V_{OUT})}$$

Given an inductor value (L), the peak inductor current is the sum of the average inductor current ( $I_{AVG}$ ) and half the inductor ripple current ( $\Delta I$ ), or:

$$I_{PK} = I_{AVG} + \frac{V_{IN} \big( V_{OUT} - V_{IN} \big)}{\big( 2 \big) \big( L \big) \big( f_0 \big) \big( V_{OUT} \big)}$$

The inductor core type is determined by peak current and efficiency requirements. The inductor core must withstand this peak current without saturating, and the series winding resistance and core losses should be kept as small as is practical to maximize conversion efficiency.

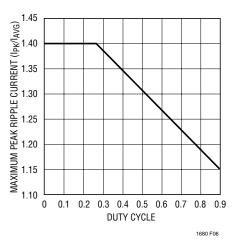

The LT1680 peak current threshold is 40% greater than the average limit threshold. Slope compensation effects reduce this margin as duty cycle increases. This margin must be maintained to prevent peak current limit from corrupting the programmed value for average current limit. Programming the peak ripple current to less than 15% of the desired average current limit value will assure proper operation of the average current limit feature through 90% duty cycle (see Slope Compensation).

#### **Slope Compensation**

Current mode switching regulators that operate with a duty cycle greater than 50% and have continuous inductor current can exhibit duty cycle instability. While a regulator will not be damaged and may even continue to function acceptably during this type of subharmonic oscillation, an irritating high-pitched squeal is usually produced.

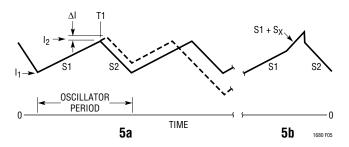

The criterion for current mode duty cycle instability is met when the increasing slope of the inductor ripple current is less than the decreasing slope, which is the case at duty cycles greater than 50%. This condition is illustrated in Figure 5a. The inductor ripple current starts at  $I_1$ , the beginning of each oscillator switch cycle. Current increases at a rate S1 until the current reaches the control trip level  $I_2$ . The controller servo loop then disables the switch and inductor current begins to decrease at a rate S2. If the current switch point ( $I_2$ ) is perturbed slightly and increased by  $\Delta I$ , the cycle time ends such that the minimum current point is increased by a factor of 1 + (S2/S1) to start the next cycle. On each successive cycle, this error is multiplied by a factor of S2/S1. Therefore, if S2/S1 is  $\geq 1$ , the system is unstable.

Subharmonic oscillations can be eliminated by augmenting the increasing ripple current slope (S1) in the control loop. This is accomplished by adding an artificial ramp on the inductor current waveform internal to the IC (with a slope  $S_X$ ) as shown in Figure 5b. If the sum of the slopes

Figure 5. Inductor Current at DC > 50% and Slope Compensation Adjusted Signal

$S1 + S_X$  is greater than S2, this condition for subharmonic oscillation no longer exists.

For boost topologies, the required additional current waveform slope, or "Slope Compensation," follows the relation:

$$S_X \ge \frac{\left(S1\right)\!\left(2DC - 1\right)}{\left(1 - DC\right)}$$

For duty cycles less than 50% (DC < 0.5),  $S_X$  is negative and is not required. For duty cycles greater than 50%,  $S_X$  takes on values dependent on S1 and duty cycle. S1 is simply  $V_{IN}$ /L. This leads to a minimum inductance requirement for a given  $V_{IN}$ , duty cycle and slope compensation ( $S_X$ ) of:

$$L_{MIN} = \frac{\left(\frac{V_{IN}}{S_X}\right)(2DC - 1)}{1 - DC}$$

The LT1680 contains an internal slope compensation ramp that has an equivalent current referred value of:

$$S_X = 0.084 \left( \frac{f_0}{R_{SENSE}} \right)$$

Amp/s

where  $f_0$  is oscillator frequency and  $R_{SENSE}$  is the external current sense resistor. This yields a minimum inductance requirement of:

$$L_{MIN} \ge \frac{(V_{IN})(R_{SENSE})(2DC-1)}{[(0.084)(f_0)(1-DC)]}$$

A down side of slope compensation is that, since the IC servo loop senses an increase in perceived inductor current, the internal current limit functions are affected such that the maximum current capability of a regulator is reduced by the same amount as the effective current

referred slope compensation. The LT1680, however, uses a current limit scheme that is independent of the slope compensation effects (Average Current Limiting). This provides operation at any duty cycle with no reduction in current sourcing capability, provided ripple current peak amplitude is less than 15% of the current limit value. For example, if the converter is set up to average current limit at 10A, as long as the peak inductor current is less than 11.5A, duty cycles up to 90% can be achieved without compromising the average current limit value.

Figure 6. Maximum Peak Ripple Current (Normalized) vs Duty Cycle for Average Current Limit

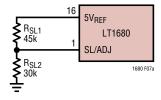

If an inductor smaller than the minimum required for internal slope compensation (calculated above as  $L_{MIN}$ ) is desired, additional slope compensation is necessary. The LT1680 provides this capability through the SL/ADJ pin. This feature is implemented by referencing this pin via a resistor divider from the  $5V_{REF}$  pin to ground. The additional slope compensation will be affected at the point in the oscillator waveform (at pin  $C_T$ ) corresponding to the voltage set by the resistor divider. Additional slope compensation can be calculated using the relation:

$$S_{X} = \frac{(2500)(f_{0})}{(R_{TH})(R_{SENSE})}$$

Amp/s

where R<sub>TH</sub> is the Thevenin resistance of the resistor divider. Actual compensation will actually be somewhat greater due to internal curvature correction circuitry that

imposes an exponential increase in the slope compensation waveform, further increasing the effective compensation slope up to 20% for a given setting.

Design example:

$$\begin{split} &V_{IN}=20V\\ &V_{OUT}=80V\;(DC=0.75)\\ &R_{SENSE}=0.01\Omega\\ &f_0=100kHz\\ &L=20\mu H \end{split}$$

The minimum inductor usable with no additional slope compensation is:

$$L_{MIN} \ge \frac{\left(20V\right)\!\left(0.01\Omega\right)\!\left(1.5-1\right)}{\left(0.084\right)\!\left(100000\right)\!\left(1-0.75\right)} = 47.6\mu H$$

Since L =  $20\mu H$  is less than L<sub>MIN</sub>, additional slope compensation is necessary. The total slope compensation required is:

$$S_X \ge \frac{\left(\frac{20V}{20\mu H}\right)(1.5-1)}{1-0.75} = (2)(10^6)$$

Amp/s

Subtracting the internally generated slope compensation and solving for the required effective resistance at SL/ADJ yields:

$$R_{EQ} \le \frac{(2500)(f_0)}{(2)(10^6)(R_{SENSE}) - (0.084)(f_0)} = 21.5k$$

Setting the resistor divider reference voltage to 2V assures that the additional compensation waveform will be enabled at a 75% duty cycle. As shown in Figure 7a, using  $R_{SL1}=45k$  and  $R_{SL2}=30k$  sets the desired reference voltage and has a  $R_{TH}$  of 18k, which meets both design requirements. Figure 7b shows the slope compensation effective waveforms both with and without the SL/ADJ external resistors.

Figure 7a. External Slope Compensation Resistors

Figure 7b. Slope Compensation Waveforms

#### **Power MOSFET and Output Rectifying Diode Selection**

LT1680 converter system parameters that dictate selection criteria for the switch MOSFET and output rectifying diode include maximum load current ( $I_{OUT}$ ), inductor average current ( $I_{AVG}$ ) and inductor ripple current ( $\Delta I$ ), and maximum input and output voltages.

The switch MOSFETs selected must have a maximum operating  $V_{DSS}$  exceeding the maximum output voltage  $(V_{OUT})$ .  $V_{GS}$  rated operating maximums must exceed the  $12V_{IN}$  supply voltage. Once voltage requirements have been determined, switch conduction resistance  $(R_{DS(ON)})$  can be determined based on allowable power dissipation. In a typical LT1680 boost converter, the switch current is equal to the inductor current, but is chopped according to duty cycle (DC). The conduction loss  $(P_{LOSS})$  for a given FET  $R_{DS(ON)}$  can be calculated using the relation:

$$P_{LOSS} \approx (DC)(R_{DS(ON)})(I_{AVG}^2 + [\Delta I^2/12])$$

where  $I_{AVG}$  = average inductor current and  $\Delta I$  = peak-to-peak inductor ripple current.

The output diode is often a major source of power loss in switching regulators and selection of adequately rated diodes is important. In a boost converter, when the output voltage is significantly higher than the input voltage, the peak diode current becomes much higher than average

output currents and diode current ratings must be observed with caution. The peak diode current is:

$$I_{D(PEAK)} = I_{AVG} + \Delta I/2$$

and the average power dissipation (P<sub>D</sub>) in the diode is:

$$P_D = (I_{OUT})(V_f)$$

where  $V_f$  is the forward voltage of the diode at peak current. The output diode must also be rated for maximum reverse voltages exceeding  $V_{OUT}$ .

## $C_{IN}$ and $C_{OUT}$ Supply Decoupling Capacitor Selection

The large currents typical of LT1680 applications require special consideration for the regulator input and output supply decoupling capacitors.

Under normal steady state boost operation, output current provided by the converter is a square wave of duty cycle  $V_{IN}/V_{OUT}$ , the average value being equal to the required DC load current ( $I_{OUT}$ ). The continuity of the load current is maintained by the output bypass capacitors. To prevent excessive output voltage ripple and undue capacitor heating (and associated catastrophic failure), low ESR output capacitors sized for the maximum RMS current must be used. This maximum capacitor RMS current follows the relation:

$$I_{RMS} \approx I_{OUT} \left( \frac{V_{OUT}}{V_{IN}} - 1 \right)^{1/2}$$

Capacitor ripple current ratings are often based on only 2000 hours (3 months) lifetime; it is advisable to derate either the ESR or temperature rating of capacitors for increased MTBF.

The input bypass capacitors generally have less ripple current than the output bypass capacitors as the input current in a boost converter is continuous. Input bypass capacitor selection can be made using ripple current ratings. Peak-to-peak ripple current is equal to the inductor ripple current ( $\Delta I_L$ ).

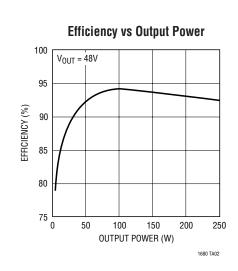

#### **Efficiency Considerations and Heat Dissipation**

High output power applications create an inherent concern regarding power dissipation in regulator components. Although high efficiencies are achieved using the LT1680, the power dissipated in the regulator climbs to relatively high values when the load draws large amounts

of power. Even at 90% efficiency, a 500W application has conversion loss of 55W.

$I^2R$  dissipation in the MOSFET switch, sense resistor and inductor series resistance can generate substantial conversion loss under high current conditions. Generally, the dominant  $I^2R$  loss is evidenced in the FET switch, which is proportional to the steady-state duty cycle, or conduction time of the switch. For example, in a 5V to 48V boost converter, the duty cycle is:

$$DC = 1 - (V_{IN}/V_{OUT})$$

$$DC = 1 - 5/48 \approx 90\%$$

The FET switch conducts inductor current for almost 90% of the cycle time, and thus may require increased consideration for dissipating I<sup>2</sup>R power.

#### **Gate Drive Buffer**

The LT1680 is designed to drive relatively large capacitive loads. However, in certain applications, efficiency improvements can be realized by adding an external buffer stage to drive the gate of the FET switch. When the switch gate loads the driver output such that rise/fall times exceed 100ns, buffers can sometimes result in efficiency gains. Buffers can also reduce effects of back injection into the gate driver output due to coupling of switch node transitions through the switch FET  $C_{\rm MILLER}$ .

### Optimizing Transient Response-Compensation Component Values

The dominant compensation point for an LT1680 converter is the  $V_C$  pin (Pin 5), or error amplifier output. This pin connects to an external series RC network,  $R_{VC}$  and  $C_{VC}$ . The infinite permutations of input/output filtering, capacitor ESR, input voltage, load current, etc. make for an empirical method of optimizing loop response for a specific set of conditions.

Loop response can be observed by injecting a step change in load current. This can be achieved by using a switchable load. With the load switching, the transient response of the output voltage can be observed with an oscilloscope. Iterating through RC combinations will yield optimized response. Refer to Application Note 19 in the 1990 Linear Applications Handbook, Volume 1 for more information.

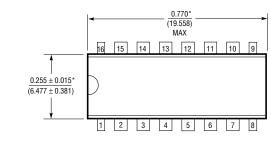

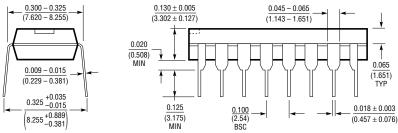

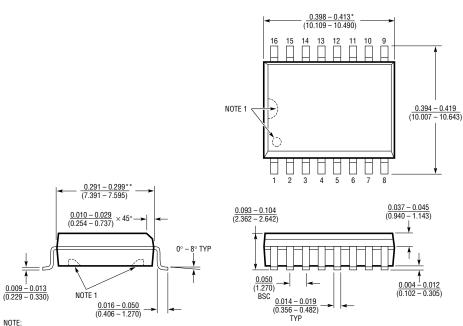

## PACKAGE DESCRIPTION Dimensions in inches (millimeters) unless otherwise noted.

#### N Package 16-Lead PDIP (Narrow 0.300)

(LTC DWG # 05-08-1510)

<sup>\*</sup>THESE DIMENSIONS DO NOT INCLUDE MOLD FLASH OR PROTRUSIONS. MOLD FLASH OR PROTRUSIONS SHALL NOT EXCEED 0.010 INCH (0.254mm)

S16 (WIDE) 1098

#### SW Package 16-Lead Plastic Small Outline (Wide 0.300)

(LTC DWG # 05-08-1620)

NOTE.

I. PIN 1 IDENT, NOTCH ON TOP AND CAVITIES ON THE BOTTOM OF PACKAGES ARE THE MANUFACTURING OPTIONS.

THE PART MAY BE SUPPLIED WITH OR WITHOUT ANY OF THE OPTIONS

\*DIMENSION DOES NOT INCLUDE MOLD FLASH, MOLD FLASH SHALL NOT EXCEED 0.006" (0.152mm) PER SIDE

\*\*DIMENSION DOES NOT INCLUDE INTERLEAD FLASH. INTERLEAD FLASH SHALL NOT EXCEED 0.010" (0.254mm) PER SIDE

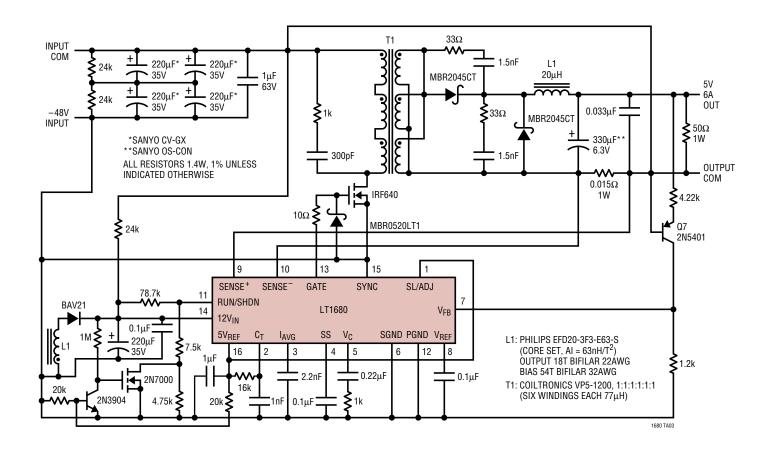

## TYPICAL APPLICATION

#### -48V to 5V 30W Forward Converter

## **RELATED PARTS**

| PART NUMBER     | DESCRIPTION                                                                  | COMMENTS                                                                                                  |  |

|-----------------|------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|--|

| LT1268          | 7.5A, 150kHz Switching Regulator                                             | Integrated Switch Can Be Used in Isolated Flyback Mode                                                    |  |

| LT1270A         | 10A, 60kHz Switching Regulator                                               | Integrated Switch Can Be Used in Isolated Flyback Mode                                                    |  |

| LT1339          | High Power Synchronous DC/DC Controller                                      | Operation to 60V, No Shoot-Through N-Channel Output Drivers                                               |  |

| LT1370          | 500kHz, 6A Boost Switching Regulator                                         | Integrated Switch, Regulates Positive or Negative Outputs                                                 |  |

| LT1371          | 500kHz, 3A Boost Switching Regulator                                         | Integrated Switch, Regulates Positive or Negative Outputs                                                 |  |

| LT1619          | Low Voltage Current Mode DWM Controller                                      | 8-lead MSOP, 1.9V ≤ V <sub>IN</sub> ≤ 18V                                                                 |  |

| LTC1700         | No R <sub>SENSE</sub> ™ Synchronous Current Mode Step-Up<br>DC/DC Controller | 95% Efficient, $0.9V \le V_{IN} \le 5V$ , $550kHz$                                                        |  |

| LT1738          | Ultralow Noise DC/DC Boost Controller                                        | Greatly Reduced Conducted and Radiated EMI, N-Channel MOSFET Driver, 20kHz to 250kHz Oscillator Frequency |  |

| LTC3401/LTC3402 | 1A/2A 3MHz Micropower Synchronous Boost Converter                            | 10-Lead MSOP, $0.5V \le V_{IN} \le 5V$                                                                    |  |

No  $R_{\mbox{\footnotesize SENSE}}$  is a trademark of Linear Technology Corporation.