# Si88x2x Data Sheet

## Dual Digital Isolators with DC-DC Converter

The Si88xx integrates Silicon Labs' proven digital isolator technology with an on-chip isolated dc-dc converter that provides regulated output voltages of 3.3 or 5.0 V (or >5 V with external components) at peak output power levels of up to 5 W. These devices provide up to two digital channels. The dc-dc converter has user-adjustable frequency for minimizing emissions, a soft-start function for safety, a shutdown option and loop compensation. The device requires only minimal passive components and a miniature transformer.

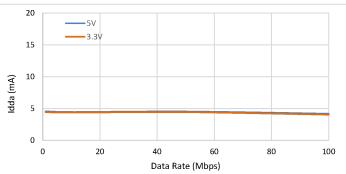

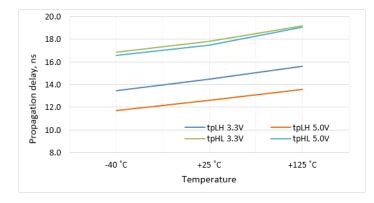

The ultra-low-power digital isolation channels offer substantial data rate, propagation delay, size and reliability advantages over legacy isolation technologies. Data rates up to 100 Mbps max are supported, and all devices achieve propagation delays of only 23 ns max. Ordering options include a choice of dc-dc converter features, isolation channel configurations and a fail-safe mode. All products are certified by UL, CSA, VDE, and CQC.

## Applications:

- · Industrial automation systems

- · Hybrid electric and electric vehicles

- Isolated power supplies

- Inverters

## Safety Approval (Pending):

- · UL 1577 recognized

- · Up to 5000 Vrms for 1 minute

- CSA component notice 5A approval • IEC 60950

- · Data acquisition

- · Motor control

- · PLCs, distributed control systems

- · VDE certification conformity • VDE0884-10

- CQC certification approval

- GB4943.1

#### **KEY FEATURES**

- · High-speed isolators with integrated dc-dc converter

- Fully-integrated secondary sensing feedback-controlled converter with dithering for low EMI

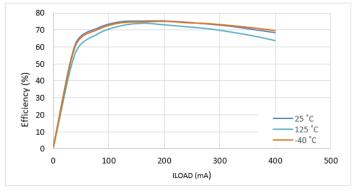

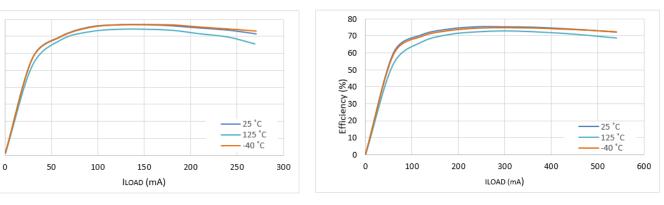

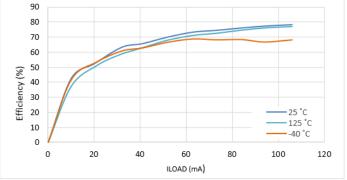

- dc-dc converter peak efficiency of 83% with external power switch

- Up to 5 W isolated power with external power switch

- Options include dc-dc shutdown, frequency control, and soft start

- Standard Voltage Conversion

- 3/5 V to isolated 3/5 V

- 24 V to isolated 3/5 V

- 3/5 V to isolated 24 V

- 24 V to isolated 24 V

- · Precise timing on digital isolators

- 0 100 Mbps

- 18 ns typical prop delay

- · Highly-reliable: 100 year lifetime

- · High electromagnetic immunity and ultralow emissions

- · RoHS compliant packages

- · SOIC-20 wide body

- · SOIC-16 wide body

- · Isolation of up to 5000 Vrms

- High transient immunity of 100 kV/µs (typical)

- AEC-Q100 qualified

- · Wide temp range

- –40 to +125 °C

# **Table of Contents**

| 1. | Features List                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | . 4              |  |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|--|

| 2. | Ordering Guide                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | . 5              |  |

| 3. | Functional Description.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | . 7              |  |

|    | 3.1 Theory of Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | . 7              |  |

|    | 3.2 Digital Isolation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | . 7              |  |

|    | 3.3 DC-DC Converter Application Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                  |  |

|    | 3.3.1 Shutdown                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                  |  |

|    | 3.3.2 Soft-Start                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                  |  |

|    | 3.3.4 External Transformer Driver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                  |  |

|    | 3.3.5 VREGA, VREGB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                  |  |

|    | 3.3.6 Output Voltage Control.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                  |  |

|    | 3.3.7 Compensation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                  |  |

|    | 3.3.9 Cycle Skipping                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                  |  |

|    | 3.3.10 Low-Voltage Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                  |  |

|    | 3.3.11 Low-Voltage to High-Voltage Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                  |  |

|    | 3.3.12 High-Voltage to Low-Voltage Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                  |  |

|    | 3.4 Transformer Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                  |  |

| 4  | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                  |  |

| 4. | Electrical Specifications       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .        .       . <th .<<="" th=""><th></th></th> | <th></th>        |  |

| _  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                  |  |

| 5. | Digital Isolator Device Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                  |  |

|    | 5.1 Device Startup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                  |  |

|    | 5.2 Undervoltage Lockout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                  |  |

|    | 5.3 Layout Recommendations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                  |  |

|    | 5.3.1 Supply Bypass                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                  |  |

|    | 5.4 Fail-Safe Operating Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                  |  |

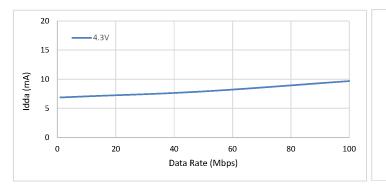

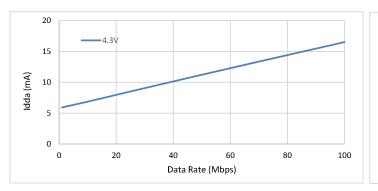

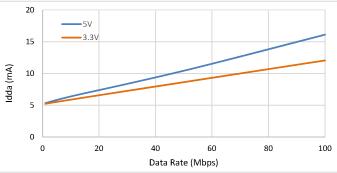

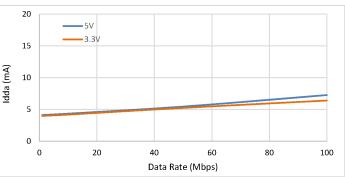

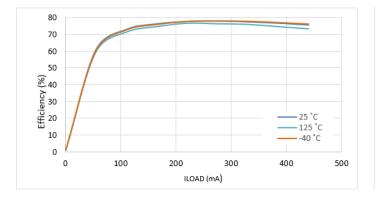

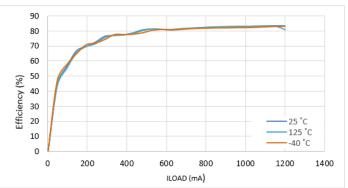

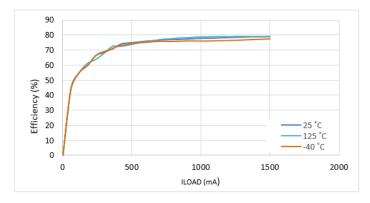

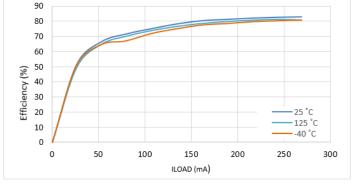

|    | 5.5 Typical Performance Characteristics.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                  |  |

| 6. | Pin Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                  |  |

|    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                  |  |

| 1. | Package Outlines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                  |  |

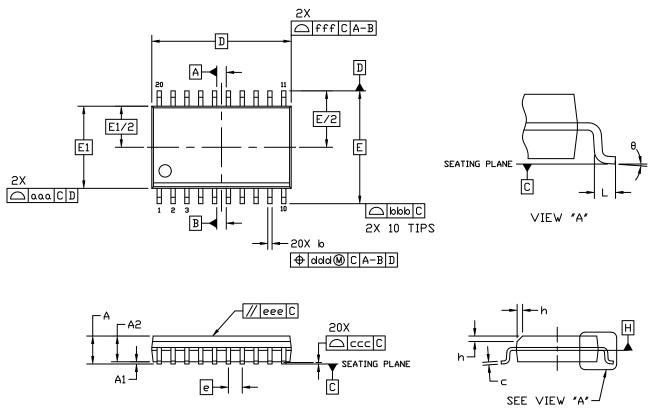

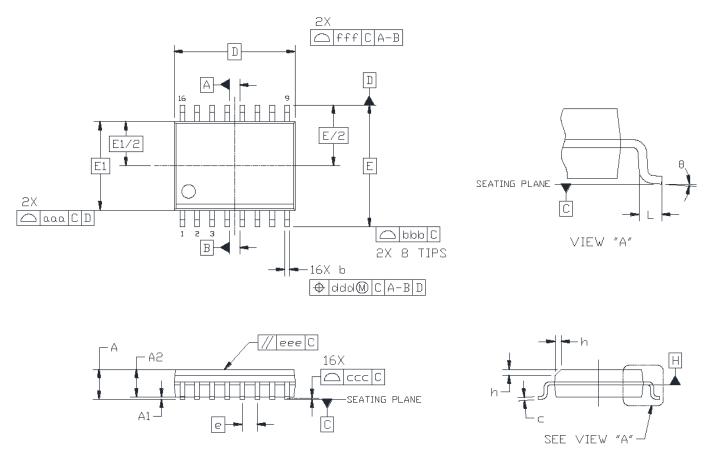

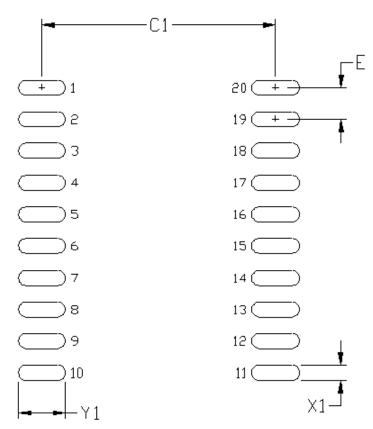

|    | 7.1 Package Outline: 20-Pin Wide Body SOIC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | .39              |  |

|    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                  |  |

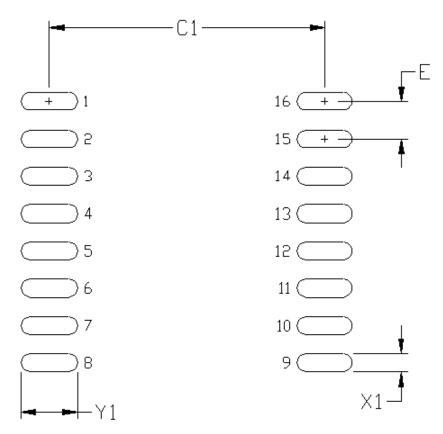

|    | 7.2 Package Outline: 16-Pin Wide Body SOIC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                  |  |

| 8. | 7.2 Package Outline: 16-Pin Wide Body SOIC.    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    . <td>43</td>                                                                                                                                                                                                                           | 43               |  |

| 8. | 7.2 Package Outline: 16-Pin Wide Body SOIC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 43               |  |

| 8. | 7.2 Package Outline: 16-Pin Wide Body SOIC.    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    . <th><b>43</b><br/>.43</th>                                                                                                                                                                                                            | <b>43</b><br>.43 |  |

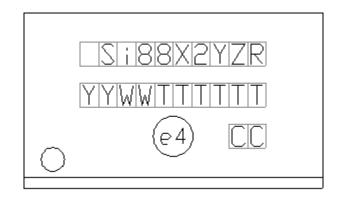

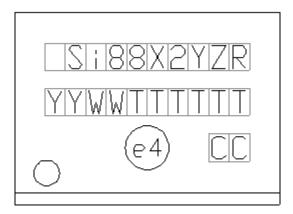

| 9.1 Si88x2x Top Marking: 20-Pin Wide Body SOIC . |   |  |  |   |   | • |   | • |   | • |  |   | .45 |

|--------------------------------------------------|---|--|--|---|---|---|---|---|---|---|--|---|-----|

| 9.2 Si88x2x Top Marking: 16-Pin Wide Body SOIC . |   |  |  |   |   | • |   |   | • | • |  |   | .46 |

| 10. Revision History                             | • |  |  | • | • | • | • | • | • | • |  | • | 47  |

## 1. Features List

- High-speed isolators with integrated dc-dc converter

- Fully-integrated secondary sensing feedback-controlled converter with dithering for low EMI

- dc-dc converter peak efficiency of 83% with external power switch

- · Up to 5 W isolated power with external power switch

- Options include dc-dc shutdown, frequency control, and soft start

- Standard Voltage Conversion

- 3/5 V to isolated 3/5 V

- 24 V to isolated 3/5 V

- 3/5 V to isolated 24 V

- · 24 V to isolated 24 V

- Precise timing on digital isolators

- 0-100 Mbps

- 18 ns typical prop delay

- Highly-reliable: 100 year lifetime

- High electromagnetic immunity and ultra-low emissions

- RoHS compliant packages

- SOIC-20 wide body

- SOIC-16 wide body

- Isolation of up to 5000 Vrms

- High transient immunity of 100 kV/µs (typical)

- AEC-Q100 qualified

- Wide temp range

- –40 to +125 °C

# 2. Ordering Guide

| Table 2.1. | Si88x2x | Ordering | Guide <sup>1,2,3,4</sup> |

|------------|---------|----------|--------------------------|

|------------|---------|----------|--------------------------|

| Ordering Part<br>Number | DC-DC<br>Shutdown | Soft<br>Start | Frequency<br>Control | External<br>Switch | Forward<br>Digital | Reverse<br>Digital | Insulation<br>Rating<br>(kVrms) | Package    |

|-------------------------|-------------------|---------------|----------------------|--------------------|--------------------|--------------------|---------------------------------|------------|

| Available Now           |                   |               |                      |                    |                    |                    |                                 |            |

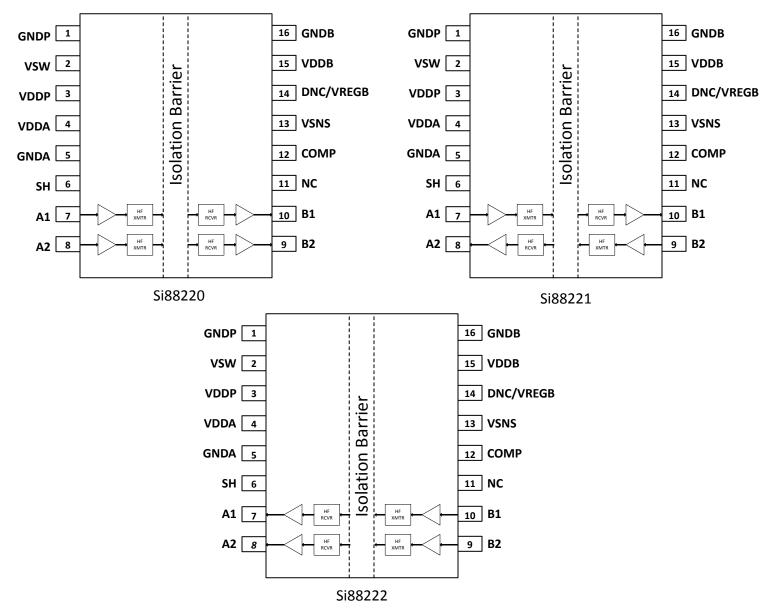

| Si88220BC-IS            | Y                 | Ν             | N                    | N                  | 2                  | 0                  | 3.75                            | WB SOIC-16 |

| Si88221BC-IS            | Y                 | Ν             | N                    | N                  | 1                  | 1                  | 3.75                            | WB SOIC-16 |

| Si88222BC-IS            | Y                 | Ν             | N                    | N                  | 0                  | 2                  | 3.75                            | WB SOIC-16 |

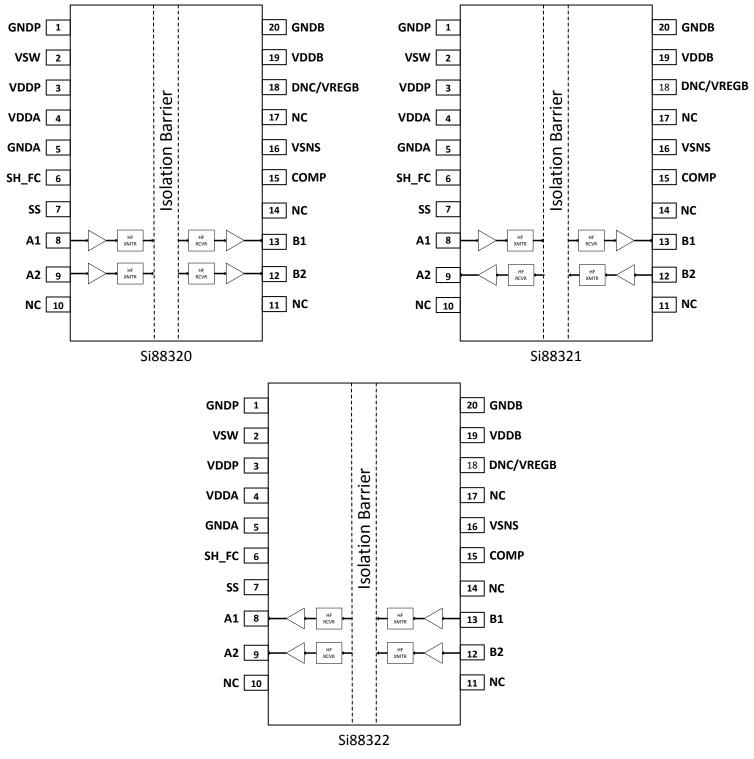

| Si88320BC-IS            | Y                 | Y             | Y                    | N                  | 2                  | 0                  | 3.75                            | WB SOIC-20 |

| Si88321BC-IS            | Y                 | Y             | Y                    | N                  | 1                  | 1                  | 3.75                            | WB SOIC-20 |

| Si88322BC-IS            | Y                 | Y             | Y                    | N                  | 0                  | 2                  | 3.75                            | WB SOIC-20 |

| Si88420BC-IS            | N                 | Ν             | N                    | Y                  | 2                  | 0                  | 3.75                            | WB SOIC-16 |

| Si88421BC-IS            | N                 | Ν             | N                    | Y                  | 1                  | 1                  | 3.75                            | WB SOIC-16 |

| Si88422BC-IS            | N                 | Ν             | N                    | Y                  | 0                  | 2                  | 3.75                            | WB SOIC-16 |

| Si88620BC-IS            | Y                 | Y             | Y                    | Y                  | 2                  | 0                  | 3.75                            | WB SOIC-20 |

| Si88621BC-IS            | Y                 | Y             | Y                    | Y                  | 1                  | 1                  | 3.75                            | WB SOIC-20 |

| Si88622BC-IS            | Y                 | Y             | Y                    | Y                  | 0                  | 2                  | 3.75                            | WB SOIC-20 |

| Si88220EC-IS            | Y                 | N             | N                    | N                  | 2                  | 0                  | 3.75                            | WB SOIC-16 |

| Si88221EC-IS            | Y                 | Ν             | N                    | N                  | 1                  | 1                  | 3.75                            | WB SOIC-16 |

| Si88222EC-IS            | Y                 | Ν             | N                    | N                  | 0                  | 2                  | 3.75                            | WB SOIC-16 |

| Si88320EC-IS            | Y                 | Y             | Y                    | N                  | 2                  | 0                  | 3.75                            | WB SOIC-20 |

| Si88321EC-IS            | Y                 | Y             | Y                    | N                  | 1                  | 1                  | 3.75                            | WB SOIC-20 |

| Si88322EC-IS            | Y                 | Y             | Y                    | N                  | 0                  | 2                  | 3.75                            | WB SOIC-20 |

| Si88420EC-IS            | N                 | N             | N                    | Y                  | 2                  | 0                  | 3.75                            | WB SOIC-16 |

| Si88421EC-IS            | N                 | Ν             | N                    | Y                  | 1                  | 1                  | 3.75                            | WB SOIC-16 |

| Si88422EC-IS            | N                 | Ν             | N                    | Y                  | 0                  | 2                  | 3.75                            | WB SOIC-16 |

| Si88620EC-IS            | Y                 | Y             | Y                    | Y                  | 2                  | 0                  | 3.75                            | WB SOIC-20 |

| Si88621EC-IS            | Y                 | Y             | Y                    | Y                  | 1                  | 1                  | 3.75                            | WB SOIC-20 |

| Si88622EC-IS            | Y                 | Y             | Y                    | Y                  | 0                  | 2                  | 3.75                            | WB SOIC-20 |

| Sampling Now            |                   |               | I                    | 1                  | 1                  |                    |                                 |            |

| Si88220BD-IS            | Y                 | Ν             | N                    | N                  | 2                  | 0                  | 5.0                             | WB SOIC-16 |

| Si88221BD-IS            | Y                 | Ν             | N                    | N                  | 1                  | 1                  | 5.0                             | WB SOIC-16 |

| Si88222BD-IS            | Y                 | Ν             | N                    | N                  | 0                  | 2                  | 5.0                             | WB SOIC-16 |

| Si88320BD-IS            | Y                 | Y             | Y                    | N                  | 2                  | 0                  | 5.0                             | WB SOIC-20 |

| Si88321BD-IS            | Y                 | Y             | Y                    | N                  | 1                  | 1                  | 5.0                             | WB SOIC-20 |

| Si88322BD-IS            | Y                 | Y             | Y                    | N                  | 0                  | 2                  | 5.0                             | WB SOIC-20 |

| Ordering Part<br>Number | DC-DC<br>Shutdown | Soft<br>Start | Frequency<br>Control | External<br>Switch | Forward<br>Digital | Reverse<br>Digital | Insulation<br>Rating<br>(kVrms) | Package    |

|-------------------------|-------------------|---------------|----------------------|--------------------|--------------------|--------------------|---------------------------------|------------|

| Si88420BD-IS            | N                 | Ν             | N                    | Y                  | 2                  | 0                  | 5.0                             | WB SOIC-16 |

| Si88421BD-IS            | N                 | N             | N                    | Y                  | 1                  | 1                  | 5.0                             | WB SOIC-16 |

| Si88422BD-IS            | N                 | N             | N                    | Y                  | 0                  | 2                  | 5.0                             | WB SOIC-16 |

| Si88620BD-IS            | Y                 | Y             | Y                    | Y                  | 2                  | 0                  | 5.0                             | WB SOIC-20 |

| Si88621BD-IS            | Y                 | Y             | Y                    | Y                  | 1                  | 1                  | 5.0                             | WB SOIC-20 |

| Si88622BD-IS            | Y                 | Y             | Y                    | Y                  | 0                  | 2                  | 5.0                             | WB SOIC-20 |

| Si88220ED-IS            | Y                 | N             | N                    | N                  | 2                  | 0                  | 5.0                             | WB SOIC-16 |

| Si88221ED-IS            | Y                 | N             | N                    | N                  | 1                  | 1                  | 5.0                             | WB SOIC-16 |

| Si88222ED-IS            | Y                 | N             | N                    | N                  | 0                  | 2                  | 5.0                             | WB SOIC-16 |

| Si88320ED-IS            | Y                 | Y             | Y                    | N                  | 2                  | 0                  | 5.0                             | WB SOIC-20 |

| Si88321ED-IS            | Y                 | Y             | Y                    | N                  | 1                  | 1                  | 5.0                             | WB SOIC-20 |

| Si88322ED-IS            | Y                 | Y             | Y                    | N                  | 0                  | 2                  | 5.0                             | WB SOIC-20 |

| Si88420ED-IS            | N                 | N             | N                    | Y                  | 2                  | 0                  | 5.0                             | WB SOIC-16 |

| Si88421ED-IS            | N                 | N             | N                    | Y                  | 1                  | 1                  | 5.0                             | WB SOIC-16 |

| Si88422ED-IS            | N                 | N             | N                    | Y                  | 0                  | 2                  | 5.0                             | WB SOIC-16 |

| Si88620ED-IS            | Y                 | Y             | Y                    | Y                  | 2                  | 0                  | 5.0                             | WB SOIC-20 |

| Si88621ED-IS            | Y                 | Y             | Y                    | Y                  | 1                  | 1                  | 5.0                             | WB SOIC-20 |

| Si88622ED-IS            | Y                 | Y             | Y                    | Y                  | 0                  | 2                  | 5.0                             | WB SOIC-20 |

## Notes:

1. All packages are RoHS-compliant with peak solder reflow temperatures of 260°C according to the JEDEC industry standard classifications.

2. "Si" and "SI" are used interchangeably.

3. AEC-Q100 qualified.

4. All Si88xxxEx product options are default output high on input power loss. All Si88xxxBx product options are default low. See Section 5. Digital Isolator Device Operation for more details about default output behavior.

## 3. Functional Description

## 3.1 Theory of Operation

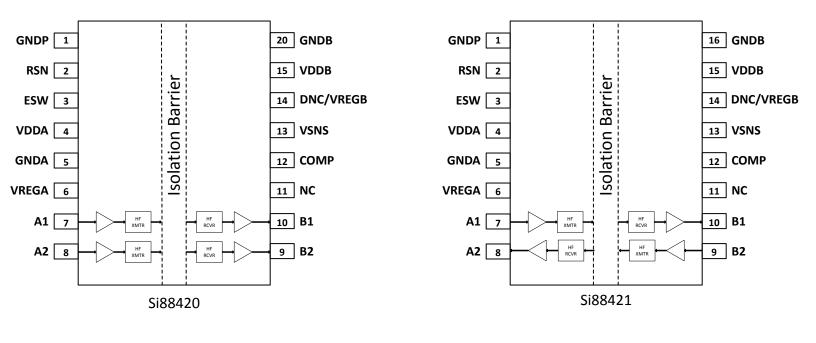

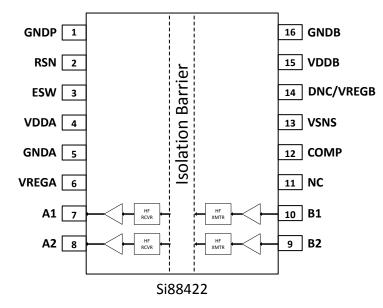

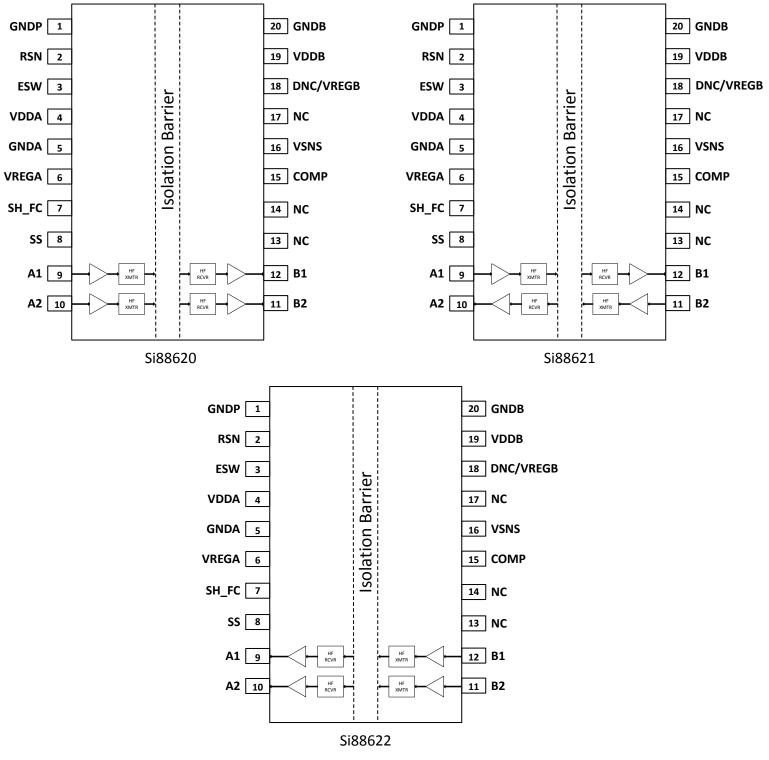

The Si88xx family of products is capable of transmitting and receiving digital data signals from an isolated power domain to a local system power domain with up to 5 kV of isolation. Each part has four unidirectional digital isolation channels. In addition, Si88xx products include an integrated controller and switches for a dc-dc converter which regulates output voltage by sensing it on the isolated side.

## 3.2 Digital Isolation

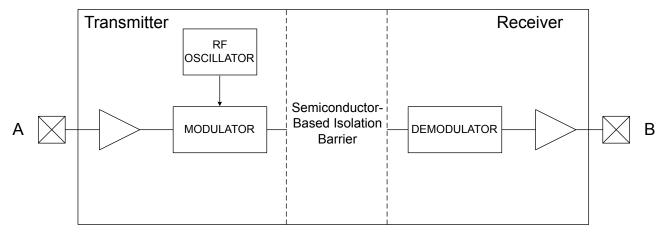

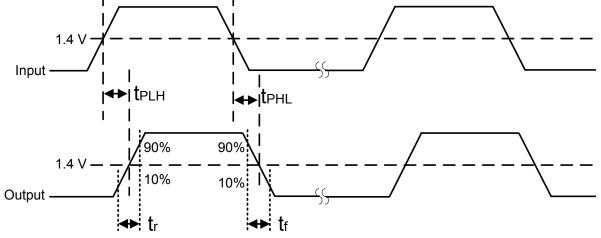

The operation of an Si88xx digital channel is analogous to that of a digital buffer, except an RF carrier transmits data across the isolation barrier. This simple architecture provides a robust isolated data path and requires no special considerations or initialization at startup. A simplified block diagram for a single Si88xx channel is shown in Figure 3.1 Simplified Si88xx Channel Diagram on page 7.

Figure 3.1. Simplified Si88xx Channel Diagram

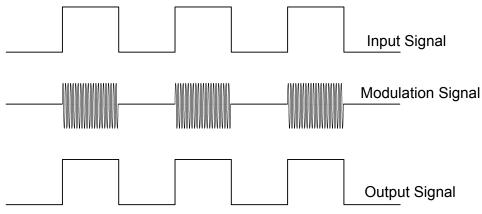

A channel consists of an RF Transmitter and RF Receiver separated by a silicon dioxide capacitive isolation barrier. In the transmitter, input A modulates the carrier provided by an RF oscillator using on/off keying. The receiver contains a demodulator that decodes the input state according to its RF energy content and applies the result to output B via the output driver. This RF on/off keying scheme is superior to pulse code schemes as it provides best-in-class noise immunity, low power consumption, and better immunity to magnetic fields. See the figure below for more details.

Figure 3.2. Modulation Scheme

#### 3.3 DC-DC Converter Application Information

The Si88xx isolated dc-dc converter is based on a modified fly-back topology and uses an external transformer and Schottky rectifying diode for low cost and high operating efficiency. The PWM controller operates in closed-loop, peak current mode control and generates isolated output voltages with 2 W average output power at 5.0 V. Options are available for up to 24 Vdc input or output operation and externally configured switching frequency.

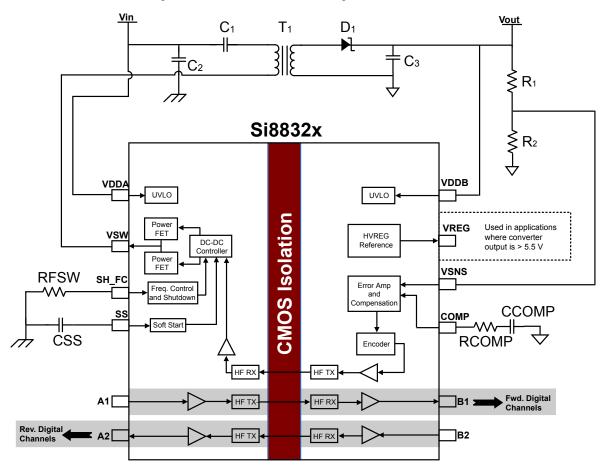

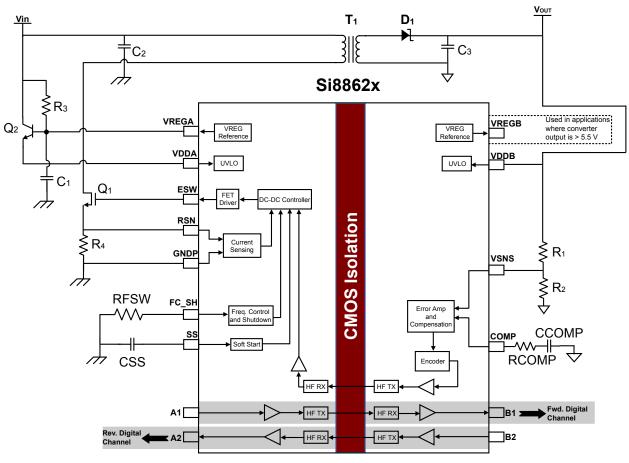

The dc-dc controller modulates a pair of internal primary-side power switches (see Figure 3.3 Si883xx Block Diagram: 3 V-5 V Input to 3 V-5 V Output on page 10) to generate an isolated voltage at external diode D1 cathode. Closed-loop feedback is provided by a compensated error amplifier, which compares the voltage at the VSNS pin to an internal voltage reference. The resulting error voltage is fed back through the isolation barrier via an internal feedback path to the controller, thus completing the control loop.

For higher input supply voltages than 5 V, an external FET Q2 is modulated by a driver pin ESW as shown in (see Figure 3.5 Si886xx Block Diagram: 24 V Input to 5 V Output on page 12). A shunt resistor based voltage sense pin RSN provides current sensing capability to the controller.

Additional features include an externally-triggered shutdown of the converter functionality using the SH pin and a programmable soft start configured by a capacitor connected to the SS pin. The Si88xx can be used in low- or high-voltage configurations. These features and configurations are explained in more detail below.

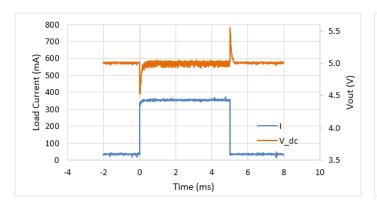

#### 3.3.1 Shutdown

This feature allows the operation of the dc-dc converter to be shut down when asserted high. This function is provided by pin 6 (labeled "SH" on the Si882xx) and pin 7 (labeled "SH\_FC" on the Si883xx and Si886xx). This feature is not available on the Si884xx. Pin 6 or pin 7 provide the exact same functionality and shut down the dc-dc converter when asserted high. For normal operation, pins 6 and 7 should be connected to ground.

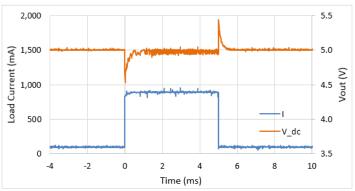

#### 3.3.2 Soft-Start

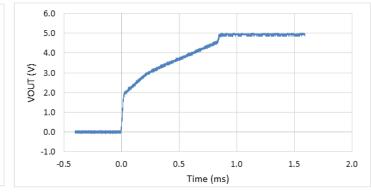

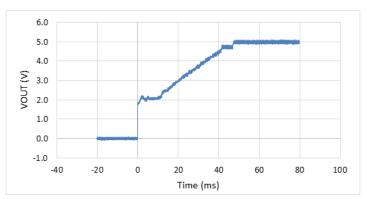

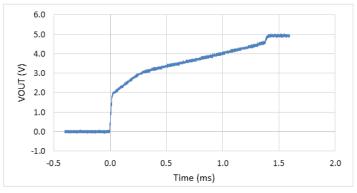

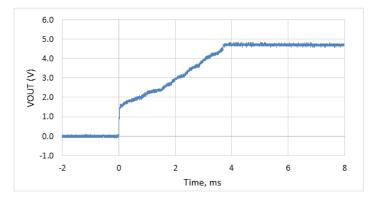

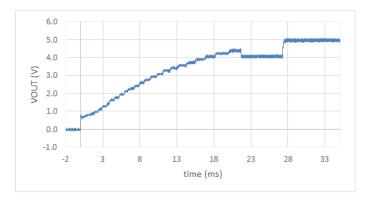

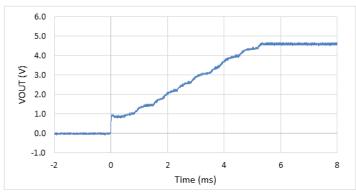

The dc-dc controller has an internal timer that controls the power conversion start-up to limit inrush current. There is also the Soft Start option where users can program the soft start up by an external capacitor connected to the SS pin. This feature is available on the Si883xx and the Si886xx.

#### 3.3.3 Programmable Frequency

The frequency of the PWM modulator is set to a default of 250 kHz for Si882xx/4xx. Users can program their desired frequency within a given band of 200 kHz to 800 kHz by controlling the time constant of an external RC connected to the SH\_FC and SS pins for Si883xx/ 6xx.

#### 3.3.4 External Transformer Driver

The dc-dc controller has internal switches (VSW) for driving the transformer with up-to a 5.5 V voltage supply. For higher voltages on the primary side, a driver output (ESW) is provided that can drive an external NMOS power transistor for driving the transformer. When this configuration is used, a shunt resistor based voltage sense pin (RSN) provides current sensing to the controller.

#### 3.3.5 VREGA, VREGB

For supporting voltages greater than 5.5 V, an internal voltage regulator (VREGA, VREGB) needs to be used in conjunction with an external NPN transistor, a resistor and a capacitor to provide regulated voltage to the IC.

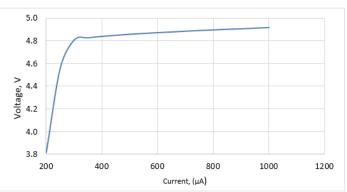

### 3.3.6 Output Voltage Control

The isolated output voltage (VOUT) is sensed by a resistor divider that provides feedback to the controller through the VSNS pin. The voltage error is encoded and transmitted back to the primary side controller across the isolation barrier, which in turn changes the duty cycle of the transformer driver. The equation for VOUT is as follows:

$$VOUT = VSNS \times \left(1 + \frac{R1}{R2}\right) + R1 \times I_{OFFSET}$$

#### 3.3.7 Compensation

The dc-dc converter uses peak current mode control. The loop is compensated by connecting an external resistor in series with a capacitor from the COMP pin to GNDB. The compensation resistance, RCOMP is fixed at 49.9 k $\Omega$  for Si882xx/3xx and 100 k $\Omega$  for Si884xx/6xx to match internal resistance. Capacitance value is given by the following equation, where f<sub>C</sub> is crossover frequency:

$$CCOMP = \frac{6}{2 \times \pi \times f_C \times RCOMP}$$

For more details on the calculations involved, see AN892: Design Guide for Isolated DC/DC Using the Si882xx/883xx.

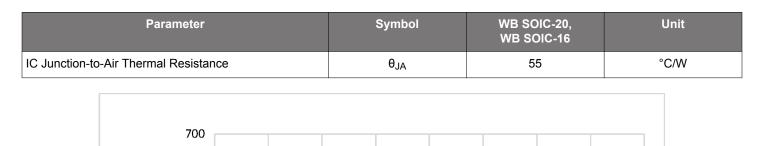

### 3.3.8 Thermal Protection

A thermal shutdown circuit is included to protect the system from over-temperature events. The thermal shutdown is activated at a junction temperature that prevents permanent damage from occurring.

#### 3.3.9 Cycle Skipping

Cycle skipping is included to reduce switching power losses at light loads. This feature is transparent to the user and is activated automatically at light loads. The product options with integrated power switches (Si882xx/3xx) may never experience cycle skipping during operation even at light loads while the external power switch options (Si884xx/6xx) are likely to have cycle skipping start at light loads.

### 3.3.10 Low-Voltage Configuration

The low-voltage configuration is used for converting 3.0 V to 5.5 V. All product options of the Si882xx and Si883xx are intended for this configuration.

An advantage of Si88xx devices over other converters that use this same topology is that the output voltage is sensed on the secondary side without requiring additional optocouplers and support circuitry to bias those optocouplers. This allows the dc-dc to operate with superior line and load regulation while reducing external components and increasing lifetime reliability.

In a typical digital signal isolation application, the dc-dc powers the Si882xx and Si883xx VDDB as shown in the figure below. In addition to powering the isolated side of the dc-dc, it can deliver up to 2 W of power to external loads. The dc-dc requires an input capacitor, C2, blocking capacitor, C1, transformer, T1, rectifying diode, D1, and an output capacitor, C3. Resistors R1 and R2 divide the output voltage to match the internal reference of the error amplifier. Type 1 loop compensation made by RCOMP and CCOMP are required at the COMP pin. Though it is not necessary for normal operation, we recommend that a snubber be used to minimize radiated emissions. More details can be found in *AN892: Design Guide for Isolated DC-DC Using the Si882xx/883xx*.

Figure 3.3. Si883xx Block Diagram: 3 V–5 V Input to 3 V–5 V Output

#### 3.3.11 Low-Voltage to High-Voltage Configuration

The low-voltage to high-voltage configuration is used for converting 3.0 V - 5.5 V up to 24 V.

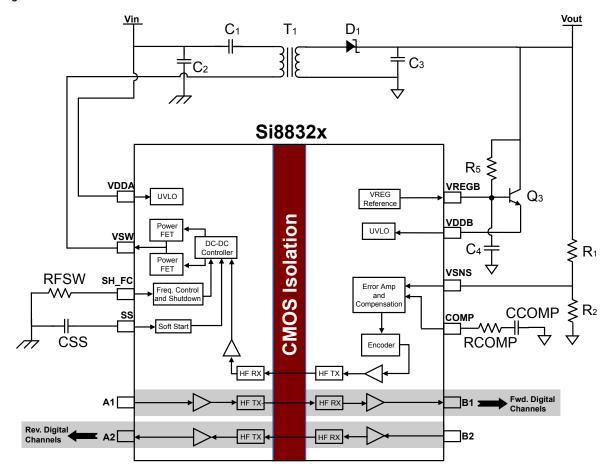

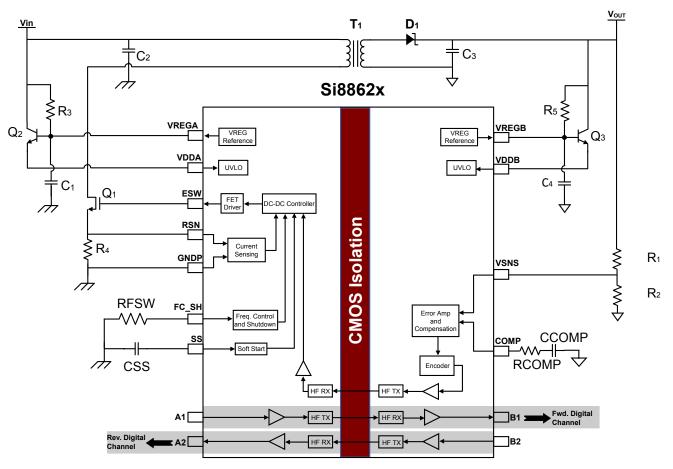

In a typical digital signal isolation application, the dc-dc powers the Si882xx and Si883xx VOUT as shown in the figure below. In addition to powering the isolated side of the dc-dc, it can deliver up to 2 W of power to external loads. The dc-dc requires an input capacitor, C2, blocking capacitor, C1, transformer, T1, rectifying diode, D1, and an output capacitor, C3. Resistors R1 and R2 divide the output voltage to match the internal reference of the error amplifier. To supply VDDB, Q3 transistor is biased and filtered by R5 and C4. Type 1 loop compensation made by RCOMP and CCOMP are required at the COMP pin. Though it is not necessary for normal operation, we recommend that a snubber be used to minimize radiated emissions. More details can be found in *AN892: Design Guide for Isolated DC-DC Using the Si882xx/883xx*.

Figure 3.4. Si883xx Block Diagram: 3 V – 5 V Input to up to 24 V Output

## 3.3.12 High-Voltage to Low-Voltage Configuration

The high-voltage configuration is used for converting up to 24 V to 3.3 V or 5.0 V. All product options of the Si884xx and Si886xx are intended for this configuration.

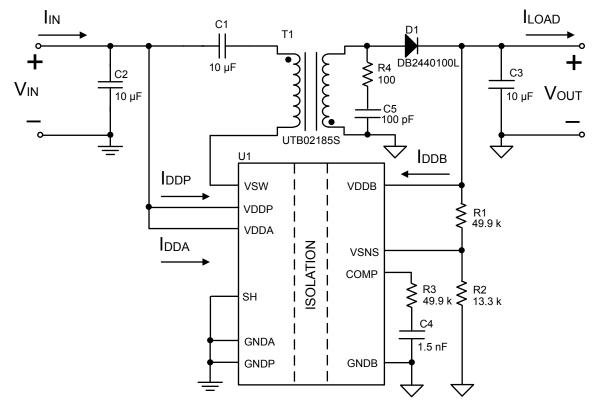

Si884xx and Si886xx can be used for dc-dc applications that have primary side voltage greater than 5.5 V. The dc-dc converter uses the isolated flyback topology. With this topology, the switch and sense resistor are external, allowing higher switching voltages. Digital isolator supply VDDA of the Si884xx and Si886xx require a supply less than or equal to 5.5 V. If a suitable supply is not available on the primary side, the VREGA voltage reference with external NPN transistor can supply VDDA. This eliminates the need to design an additional linear regulator circuit. Like the Si882xx and Si883xx, the output voltage is sensed on the secondary side without requiring additional optocouplers and support circuitry to bias those optocouplers. This allows the dc-dc to operate with superior line and load regulation.

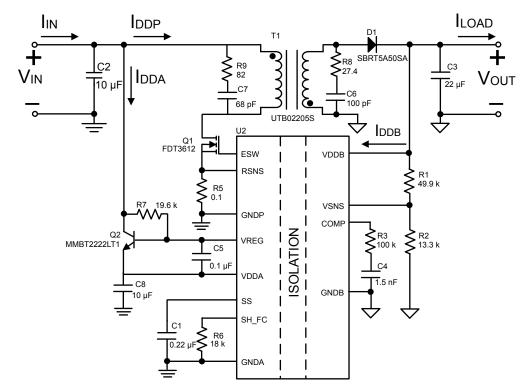

The figure below shows the block diagram of an Si886xx with external components. Si886xx is different from the Si882xx/883xx as it has externally-controlled switching frequency and soft start. The dc-dc requires input capacitor C2, transformer T1, switch Q1, sense resistor R4, rectifying diode D1 and an output capacitor C3. To supply VDDA, Q2 transistor is biased and filtered by R3 and C1. External frequency and soft start behavior is set by CSS and RFSW. Resistors R1 and R2 divide the output voltage to match the internal reference of the error amplifier. Type 1 loop compensation made by RCOMP and CCOMP are required at the COMP pin. Though it is not necessary for normal operation, we recommend to use a snubber, to minimize high-frequency emissions. For further details, see *AN901: Design Guide for Isolated DC-DC Using the Si884xx/886xx*.

Figure 3.5. Si886xx Block Diagram: 24 V Input to 5 V Output

#### 3.3.13 High-Voltage to High-Voltage Configuration

The high-voltage configuration is used for converting up to 24 V to up to 24 V.

Si884xx and Si886xx can be used for dc-dc applications that have primary side voltage greater than 5.5 V. The dcdc converter uses the isolated flyback topology. With this topology, the switch and sense resistor are external, allowing higher switching voltages. Digital isolator supply VDDA of the Si884xx and Si886xx require a supply less than or equal to 5.5 V. If a suitable supply is not available on the primary side, the VREGA voltage reference with external NPN transistor can supply VDDA. This eliminates the need to design an additional linear regulator circuit. Like the Si882xx and Si883xx, the output voltage is sensed on the secondary side without requiring additional optocouplers and support circuitry to bias those optocouplers. This allows the dc-dc to operate with superior line and load regulation.

The figure below shows the block diagram of an Si886xx with external components. Si886xx is different from the Si882xx/883xx as it has externally-controlled switching frequency and soft start. The dc-dc requires input capacitor C2, transformer T1, switch Q1, sense resistor R4, rectifying diode D1 and an output capacitor C3. To supply VDDA, Q2 transistor is biased and filtered by R3 and C1. External frequency and soft start behavior is set by CSS and RFSW. Resistors R1 and R2 divide the output voltage to match the internal reference of the error amplifier. To supply VDDB, Q3 transistor is biased and filtered by R5 and C4. Type 1 loop compensation made by RCOMP and CCOMP are required at the COMP pin. Though it is not necessary for normal operation, we recommend to use a snubber, to minimize high-frequency emissions. For further details, see *AN901: Design Guide for Isolated DC-DC Using the Si884xx/886xx*.

Figure 3.6. Si886xx Block Diagram: Up to 24 V Input to up to 24 V Output

## 3.4 Transformer Design

The table below provides a list of transformers and their parametric characteristics that have been validated to work with Si882xx/3xx products (input voltage of 3 to 5 V) and Si884xx/Si886xx products (input voltage of 24 V). It is recommended that users order the transformers from the vendors per the part numbers given below. Refer to *AN892: Design Guide for Isolated DC/DC using the Si882xx/*883xx and *AN901: Design Guide for Isolated DC/DC using the Si884xx/*886xx for voltage translation applications not listed below.

To manufacture transformers from your preferred suppliers that may not be listed below, please specify to supplier the parametric characteristics as specified in the table below for a given input voltage and isolation rating.

| Transformer<br>Supplier                                       | Ordering Part # | Input<br>Voltage | Output<br>Voltage  | Turns<br>Ratio P:S    | Leakage<br>Inductance | Primary<br>Inductance | Primary<br>Resistance | Isolation<br>Rating   |

|---------------------------------------------------------------|-----------------|------------------|--------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|

| UMEC (http://<br>www.umec-<br>usa.com)                        | UTB02185s       | 4.5 – 5.5 V      | 3.0 – 5.5V         | 1.0:4.0               | 100 nH max            | 2 µH ± 5%             | 0.05 Ω max            | 2.5 kV <sub>RMS</sub> |

| UMEC (http://<br>www.umec-<br>usa.com)                        | UTB02205s       | 12V, 24V         | 3.3 – 5.0V,<br>15V | 3.0:1.0               | 800 nH max            | 25 µH ± 5%            | 0.135 Ω max           | 2.5 kV <sub>RMS</sub> |

| UMEC (http://<br>www.umec-<br>usa.com)                        | UTB02240s       | 4.5 – 5.5V       | 3.0 – 5.5V         | 1.0:4.0               | 100 nH max            | 2 µH ±5%              | 0.05 Ω max            | 5 kV <sub>RMS</sub>   |

| UMEC (http://<br>www.umec-<br>usa.com)                        | UTB02250s       | 7 – 24 V         | 3.3 – 5.5V         | 3.0:1.0               | 600 nH max            | 25 μH ± 5%            | 0.135 Ω max           | 5 kV <sub>RMS</sub>   |

| Coilcraft <sup>1</sup><br>(http://<br>www.coil-<br>craft.com) | TA7608-AL       | 4.5 – 5.5 V      | 3.0 – 5.5V         | 1.0:4.0               | 60 nH max             | 2 µH ± 5%             | 0.033 Ω max           | 2.5 kV <sub>RMS</sub> |

| Coilcraft <sup>1</sup><br>(http://<br>www.coil-<br>craft.com) | TA7618-AL       | 4.5 – 5.5V       | 3.0 – 5.5V         | 1.0:4.0               | 64 nH max             | 2.0 μH ±5%            | 0.031 Ω max           | 5 kV <sub>RMS</sub>   |

| Coilcraft <sup>1</sup><br>(http://<br>www.coil-<br>craft.com) | TA7788-AL       | 12V              | 5V, 15V            | 1.00 :<br>1.25 : 0.75 | 554 nH max            | 25 μH ±5%             | 0.49 Ω max            | 5 kV <sub>RMS</sub>   |

| Coilcraft <sup>1</sup><br>(http://<br>www.coil-<br>craft.com) | UA7902          | 12V              | 5V, 15V            | 3.0:1.0               | 971 nH max            | 25 μH ±5%             | 0.075 Ω max           | 5 kV <sub>RMS</sub>   |

| TDK (http://<br>www.tdk.com)                                  | P100940_A1      | 4.5 – 5.5V       | 3.0 – 5.5V         | 1.0:4.0               | 40 nH max             | 2.0 µH ±10%           | 0.1 Ω max             | 2.4 kV <sub>RMS</sub> |

| Mentech <sup>1</sup><br>(http://<br>www.mnc-<br>tek.com)      | TTER09-0457S1   | 8 - 24 V         | 15V, 24V           | 1.0:1.0               | 550 nH max            | 25 µH ±10%            | 0.4 Ω max             | 2.5 kV <sub>RMS</sub> |

| Mentech <sup>1</sup><br>(http://<br>www.mnc-<br>tek.com)      | TTER09-0458S1   | 8 - 24 V         | 8 - 24 V           | 1.0:1.0               | 550 nH max            | 25 µH ±10%            | 0.4 Ω max             | 5 kV <sub>RMS</sub>   |

### **Table 3.1. Transformer Specifications**

| Transformer<br>Supplier                                  | Ordering Part # | Input<br>Voltage | Output<br>Voltage | Turns<br>Ratio P:S | Leakage<br>Inductance | Primary<br>Inductance | Primary<br>Resistance | lsolation<br>Rating   |

|----------------------------------------------------------|-----------------|------------------|-------------------|--------------------|-----------------------|-----------------------|-----------------------|-----------------------|

| Mentech <sup>1</sup><br>(http://<br>www.mnc-<br>tek.com) | TTEP09-0568S1   | 3.0 - 5.5 V      | 5.0 V             | 1.0:4.0            | 100 nH max            | 1.5 μH ±8%            | 0.05 Ω max            | 5 kV <sub>RMS</sub>   |

| Pulse (http://<br>www.pulsee-<br>lectron-<br>ics.com/)   | PA4896NL        | 8 – 24 V         | 7 – 24 V          | 1.0:1.0            | 650 nH max            | 25 µH ±10%            | 0.25 Ω max            | 2.5 kV <sub>RMS</sub> |

| Pulse (http://<br>www.pulsee-<br>lectron-<br>ics.com/)   | PA4897NL        | 8 – 24 V         | 7 – 24 V          | 1.0:1.0            | 650 nH max            | 25 µH ±10%            | 0.25 Ω max            | 5 kV <sub>RMS</sub>   |

Notes:

1. AEC-Q200 qualified.

2. For reference design details, see AN892: Design Guide for Isolated DC/DC using the Si882xx/883xx or AN901: Design Guide for Isolated DC/DC using the Si884xx/886xx.

## 4. Electrical Specifications

## Table 4.1. Recommended Operating Conditions

| Parameter                     | Symbol         | Min | Тур | Мах | Unit |

|-------------------------------|----------------|-----|-----|-----|------|

| Ambient Operating Temperature | T <sub>A</sub> | -40 | 25  | 125 | °C   |

| Power Input Voltage           | VDDP           | 3.0 | _   | 5.5 | V    |

| Supply Voltage                | VDDA           | 3.0 | _   | 5.5 | V    |

|                               | VDDB           | 3.0 | _   | 5.5 | V    |

## Table 4.2. Electrical Characteristics<sup>1</sup>

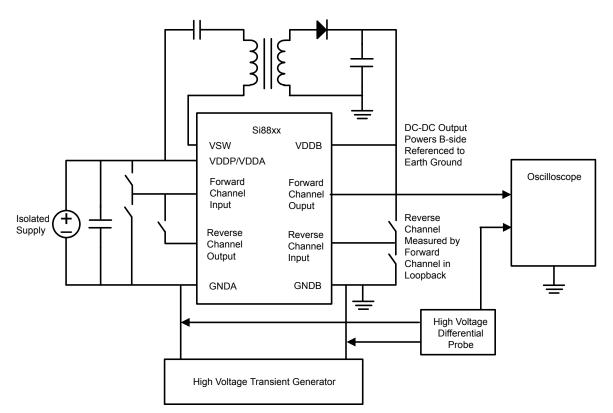

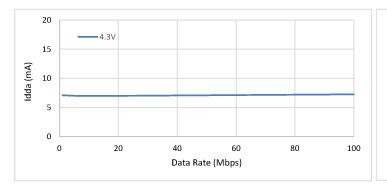

$V_{IN}$  = 24 V;  $V_{DDA}$  =  $V_{DDP}$  = 3.0 to 5.5 V (see Figure 4.2 Measurement Circuit for Converter Efficiency and Regulation for Si882xx, Si883xx on page 23) for all Si8822x/32x;  $V_{DDA}$  = 4.3 V (see Figure 4.3 Measurement Circuit for Converter Efficiency and Regulation for Si884xx, Si886xx on page 23) for all Si8842x/62x;  $T_A$  = -40 to 125 °C unless otherwise noted.

| Parameter                               | Symbol              | Test Condition                                                                                                                                                                             | Min   | Тур  | Мах   | Unit |

|-----------------------------------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|-------|------|

| DC/DC Converter                         | l                   |                                                                                                                                                                                            |       |      |       |      |

| Switching Frequency<br>Si8822x, Si8842x | FSW                 | _                                                                                                                                                                                          | 225   | 250  | 275   | kHz  |

| Switching Frequency<br>Si8832x, Si8862x |                     | $R_{FSW} = 23.3 \text{ k}\Omega$ $FSW = 1025.5/(RFSW \times CSS)$ $CSS = 220 \text{ nF}$ (see Figure 3.5 Si886xx Block Diagram: 24 V Input to 5 V Output on page 12) (1% tolerance on BOM) | 180   | 200  | 220   | kHz  |

|                                         | FSW                 | R <sub>FSW</sub> = 9.3 kΩ<br>FSW = 1025.5/(RFSW x CSS)<br>CSS = 220 nF<br>(see Figure 3.5 Si886xx Block<br>Diagram: 24 V Input to 5 V<br>Output on page 12)<br>(1% tolerance on BOM)       | 450   | 500  | 550   | kHz  |

|                                         |                     | R <sub>FSW</sub> = 5.18 kΩ,<br>CSS = 220 nF<br>(see Figure 3.5 Si886xx Block<br>Diagram: 24 V Input to 5 V<br>Output on page 12)                                                           | 810   | 900  | 990   | kHz  |

| VSNS voltage                            | VSNS                |                                                                                                                                                                                            | 1.002 | 1.05 | 1.097 | V    |

| VSNS current offset                     | I <sub>offset</sub> | ILOAD = 0 A                                                                                                                                                                                | -500  | —    | 500   | nA   |

| Output Voltage<br>Accuracy <sup>2</sup> | _                   | See Figure 4.2 Measurement<br>Circuit for Converter Efficiency<br>and Regulation for Si882xx,<br>Si883xx on page 23<br>ILOAD = 0 mA                                                        | -5    | _    | +5    | %    |

| Parameter                                                                                                                                                                   | Symbol                  | Test Condition                                                                                                                                                                       | Min | Тур                                      | Мах          | Unit   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------------------------------------------|--------------|--------|

| Line Regulation                                                                                                                                                             | ΔVOUT(line)/<br>ΔVDDP   | See Figure 4.2 Measurement<br>Circuit for Converter Efficiency<br>and Regulation for Si882xx,<br>Si883xx on page 23<br>ILOAD = 50 mA                                                 | _   | 1                                        | _            | mV/V   |

|                                                                                                                                                                             |                         | VDDP varies from 4.5 to 5.5 V                                                                                                                                                        |     |                                          |              |        |

| Load Regulation                                                                                                                                                             | ΔVOUT(load)/<br>VOUT    | See Figure 4.2 Measurement<br>Circuit for Converter Efficiency<br>and Regulation for Si882xx,<br>Si883xx on page 23                                                                  | _   | 0.1                                      |              | %      |

|                                                                                                                                                                             |                         | ILOAD = 50 to 400 mA                                                                                                                                                                 |     |                                          |              |        |

|                                                                                                                                                                             |                         | ILOAD = 100 mA                                                                                                                                                                       |     |                                          |              |        |

| Output Voltage<br>Ripple<br>Si8822x, Si8832x                                                                                                                                | _                       | See Figure 4.2 Measurement<br>Circuit for Converter Efficiency<br>and Regulation for Si882xx,<br>Si883xx on page 23                                                                  | _   | 100                                      | _            | mV p-p |