**Data Sheet**

#### FEATURES

Wideband, dual-channel, active downconversion mixers Low distortion, fast settling, IF DGAs RF input frequency range: 690 MHz to 3.8 GHz **Programmable baluns on RF inputs** For RF = 1950 MHz, IF = 281 MHz, high linearity mode Voltage conversion gain, including IF filter loss: -5 dB to +26.5 dB Input IP3: 29 dBm at minimum DGA gain Input P1dB: 12 dBm at minimum DGA gain SSB NF: 13 dB at maximum DGA gain Output IP3: 40 dBm at maximum DGA gain Output P1dB: 19 dBm at maximum DGA gain Channel isolation: 52 dB **Differential and single-ended LO input modes** Differential IF output impedance:  $100 \Omega$ Flexible power-down modes for low power operation Power-up time after enabling channels: 100 ns, typical Programmable via a 3-wire serial port interface (SPI) Single 3.3 V supply High linearity mode: 440 mA Low power mode: 260 mA

#### APPLICATIONS

Cellular base stations and wireless infrastructure receivers (W-CDMA, TD-SCDMA, WiMAX, GSM, LTE, PCS, DCS, DECT) Active antenna systems PTP radio link down converters Wireless LANs and CATV equipment

### GENERAL DESCRIPTION

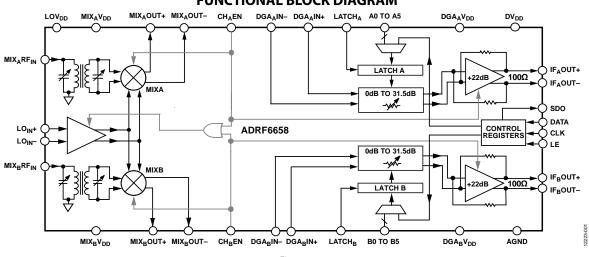

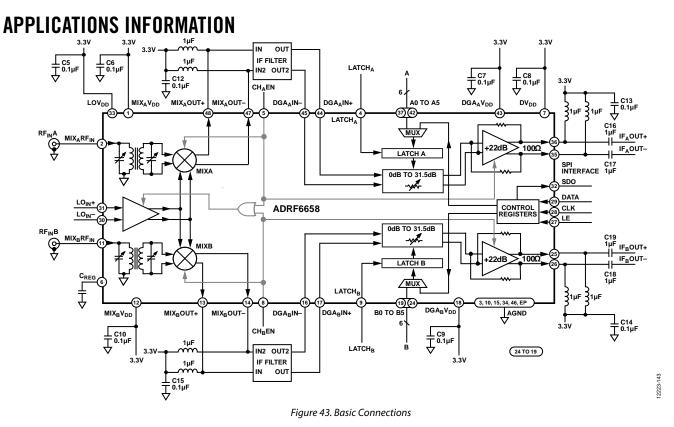

The ADRF6658 is a high performance, low power, wideband, dual-channel radio frequency (RF) downconverter with integrated intermediate frequency (IF) digitally controlled amplifiers (DGAs) for wideband, low distortion base station radio receivers.

The dual Rx mixers are doubly balanced Gilbert cell mixers with high linearity and excellent image rejection. Both mixers convert 50  $\Omega$  RF inputs to open-collector broadband IF outputs. Internal tunable baluns on the RF inputs enable suppression of RF signal harmonics and attenuation of out-of-band signals before the mixer inputs, reducing input reflections and out-ofband interference signals. A flexible local oscillator (LO) architecture allows the use of differential or single-ended LO signals.

The dual-channel IF DGAs are based on the ADL5201 and ADL5202 and have a fixed, differential output impedance of 100  $\Omega$ . The gain is adjustable over a 31.5 dB range with a 0.5 dB step size via the on-chip SPI, or through independent, 6-bit parallel ports that support latch functionality. Each channel, from the mixer inputs to the IF amplifier outputs, together with an LC interstage band-pass filter, achieves a maximum voltage conversion gain of 26.5 dB.

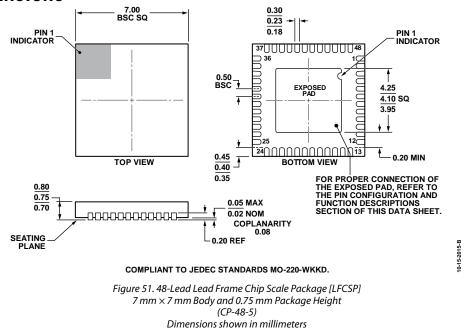

Fabricated with the Analog Devices, Inc., high speed SiGe process, the ADRF6658 is available in a compact, 7 mm  $\times$  7 mm, 48-lead LFCSP package, and operates over the -40°C to +105°C temperature range.

#### FUNCTIONAL BLOCK DIAGRAM

Rev. A Document Feedback Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 ©2015 Analog Devices, Inc. All rights reserved. Technical Support www.analog.com

# Wideband, Dual Rx Mixers with Integrated IF Amplifiers

# **ADRF6658**

Figure 1.

# **TABLE OF CONTENTS**

| Features                                          |

|---------------------------------------------------|

| Applications1                                     |

| General Description 1                             |

| Functional Block Diagram 1                        |

| Revision History 2                                |

| Specifications                                    |

| Supplemental Information for Mixers and IF DGAs 5 |

| Timing Specifications6                            |

| Absolute Maximum Ratings7                         |

| ESD Caution7                                      |

| Pin Configuration and Function Descriptions       |

| Typical Performance Characteristics               |

| Theory of Operation                               |

| Dual Mixer Cores                                  |

| DGA Basic Structure                               |

| Serial Input Shift Registers14                    |

| Program Modes14                                   |

| Register Maps15                                   |

| Register 0 Through Register 418                   |

#### **REVISION HISTORY**

| 11/15—Rev. 0 to Rev. A                                 |    |

|--------------------------------------------------------|----|

| Changes to Features Section                            | 1  |

| Changes to Total Current, Low Power Mode Parameter,    |    |

| Table 1                                                | 4  |

| Change to Figure 4                                     | 8  |

| Changes to Mixer A Enabled Section and Mixer B Enabled |    |

| Section                                                | 23 |

| Changes to Figure 51 Caption                           | 31 |

1/15—Revision 0: Initial Version

| 19 |

|----|

| 20 |

| 21 |

| 22 |

| 23 |

| 24 |

| 25 |

| 26 |

| 26 |

| 26 |

| 26 |

| 27 |

| 27 |

| 28 |

| 30 |

| 31 |

| 31 |

|    |

## **SPECIFICATIONS**

$MIX_AV_{DD} = MIX_BV_{DD} = DV_{DD} = LOV_{DD} = DGA_AV_{DD} = DGA_BV_{DD} = 3.3 V \pm 5\%$ ; AGND = 0 V.  $T_A = T_{MIN}$  to  $T_{MAX}$ . The operating temperature range =  $-40^{\circ}C$  to  $+105^{\circ}C$ . Parameters are measured on a standard test circuit with an IF filter;  $f_{RF} = 1.95$  GHz, RF input power ( $P_{RF}$ ) = -10 dBm,  $f_{LO} = 2.231$  GHz, LO input power ( $P_{LO}$ ) = 0 dBm, and  $f_{IF} = 281$  MHz, using standard register settings. For IP2 and IP3 measurements,  $f_{RF1} = 1.949$  GHz and  $f_{RF2} = 1.951$  GHz, maximum DGA gain, high linearity mode, unless otherwise noted.  $R_{SOURCE} = 50 \Omega$ ,  $R_{LOAD} = 100 \Omega$ , differential.

| Parameter                                        | Min | Тур  | Мах  | Unit    | Test Conditions/Comments                                                                                                         |

|--------------------------------------------------|-----|------|------|---------|----------------------------------------------------------------------------------------------------------------------------------|

| OPERATING CONDITIONS                             |     |      |      |         |                                                                                                                                  |

| RF Input Frequency                               | 690 |      | 3800 | MHz     |                                                                                                                                  |

| LO Power Level                                   | -6  | 0    | +6   | dBm     |                                                                                                                                  |

| LO Frequency                                     | 690 |      | 4100 | MHz     |                                                                                                                                  |

| CHANNEL CHARACTERISTICS                          |     |      |      |         |                                                                                                                                  |

| RF Input Return Loss                             |     | -12  |      | dB      | Register 13, Bits[DB12:DB7] programmed<br>according to RF frequency                                                              |

| IF Output Return Loss                            |     | -10  |      | dB      | Within IF filter passband                                                                                                        |

| IF Lower Cutoff Frequency <sup>1</sup>           |     | 10   |      | MHz     | f <sub>-3dB</sub> , MIX <sub>x</sub> OUT <sub>y</sub> connected to DGA <sub>x</sub> IN <sub>y</sub> through a dc block capacitor |

| IF Upper Cutoff Frequency                        |     | 520  |      | MHz     | $f_{-3dB}$ , MIX <sub>x</sub> OUT <sub>y</sub> connected to DGA <sub>x</sub> IN <sub>y</sub> through a dc block capacitor        |

| Voltage Conversion Gain                          |     | 26.5 |      | dB      | Maximum DGA gain                                                                                                                 |

| Voltage Conversion Gain                          |     | -5   |      | dB      | Minimum DGA gain                                                                                                                 |

| Input P1dB                                       |     |      |      |         | _                                                                                                                                |

| High Linearity Mode                              |     | 12   |      | dBm     | Register 13, Bits[DB24:DB22] = 4                                                                                                 |

| Low Power Mode                                   |     | 4    |      | dBm     | Register 13, Bits[DB24:DB22] = 1                                                                                                 |

| Second Order Input Intercept (IIP2)              |     | 49   |      | dBm     | $P_{RF} = 0$ dBm per tone, minimum DGA gain, high linearity mode                                                                 |

| Third Order Input Intercept (IIP3)               |     |      |      |         | $P_{RF} = 0$ dBm per tone, minimum DGA gain                                                                                      |

| High Linearity Mode                              |     | 29   |      | dBm     |                                                                                                                                  |

| Low Power Mode                                   |     | 17   |      | dBm     |                                                                                                                                  |

| SSB NF                                           |     |      |      |         | High linearity mode                                                                                                              |

| RF = 855 MHz                                     |     | 12.8 |      | dB      |                                                                                                                                  |

| RF = 1950 MHz                                    |     | 13   |      | dB      |                                                                                                                                  |

| RF = 3795 MHz                                    |     | 14.4 |      | dB      |                                                                                                                                  |

| With a 5 dBm Blocker                             |     | 25   |      | dB      |                                                                                                                                  |

| LO to RF Leakage                                 |     | -30  |      | dBm     |                                                                                                                                  |

| LO to IF Leakage                                 |     | -40  |      | dBm     |                                                                                                                                  |

| RF to IF Leakage                                 |     | -50  |      | dBc     | Relative to IF output level                                                                                                      |

| 2 LO – 2 RF                                      |     | -55  |      | dBc     |                                                                                                                                  |

| 3 LO – 3 RF                                      |     | -55  |      | dBc     |                                                                                                                                  |

| IF Output and LO Leakage<br>Intermodulation Spur | -70 | -100 |      | dBc     | $f_{LO}$ = 3.249 GHz, $f_{RF}$ = 3.5 GHz, IF DGA output power ( $P_{IFOUT}$ ) = 9 dBm, $f_{SPUR}$ = 237 MHz and 265 MHz          |

| Channel Isolation                                |     | 52   |      | dB      | $f_{\text{RF}} = 1.95$ GHz, $f_{\text{LO}} = 2.231$ GHz, maximum DGA gain                                                        |

| Mixer V to I Bias Adjustment Effects             |     |      |      |         | Register 13, Bits[DB24:DB22] changing from 4 to 1                                                                                |

| Amplitude Variation                              |     | 0.19 |      | dB      |                                                                                                                                  |

| Gain Step                                        |     | 0.5  |      | dB      |                                                                                                                                  |

| Gain Conformance Error                           |     | 0.05 |      | dB      | Any two adjacent steps                                                                                                           |

| Phase Conformance Error                          |     | 0.5  |      | Degrees | Any two adjacent steps                                                                                                           |

| Output P1dB                                      |     | 19   |      | dBm     | Maximum DGA gain                                                                                                                 |

| Output IP3                                       |     | 40   |      | dBm     | Maximum DGA gain                                                                                                                 |

| Differential Output Impedance                    |     | 100  |      | Ω       |                                                                                                                                  |

| Second Harmonic Level                            |     | -65  |      | dBc     | At 2 V p-p                                                                                                                       |

| Third Harmonic Level                             |     | -65  |      | dBc     | At 2 V p-p                                                                                                                       |

| Parameter                                                                       | Min                      | Тур       | Max       | Unit | Test Conditions/Comments                                 |

|---------------------------------------------------------------------------------|--------------------------|-----------|-----------|------|----------------------------------------------------------|

| LOGIC INPUTS                                                                    |                          |           |           |      |                                                          |

| Input High Voltage, V <sub>INH</sub>                                            | 1.17                     |           | 3.6       | V    |                                                          |

| Input Low Voltage, V <sub>INL</sub>                                             | -0.5                     |           | +0.63     | V    |                                                          |

| Input Current, IINH/IINL                                                        |                          |           | ±1        | μΑ   |                                                          |

| Input Capacitance, C <sub>IN</sub>                                              |                          | 2         |           | pF   |                                                          |

| LOGIC OUTPUTS                                                                   |                          |           |           |      | SDO (Pin 32)                                             |

| Output High Voltage, Vон                                                        | $V_{\text{LOGIC}} - 0.4$ |           |           | V    | VLOGIC selected with Register 5, Bit DB24                |

| Output High Current, I <sub>он</sub>                                            |                          |           | 500       | μA   |                                                          |

| Output Low Voltage, Vol                                                         |                          |           | 0.4       | V    | $I_{OL} = 500 \ \mu A$                                   |

| POWER SUPPLIES                                                                  |                          |           |           |      |                                                          |

| DV <sub>DD</sub>                                                                | 3.15                     | 3.3       | 3.45      | V    |                                                          |

| MIXAVDD, MIXBVDD, DGAAVDD,<br>DGABVDD, and LOVDD                                |                          | $DV_{DD}$ |           |      | The voltages on these pins must equal $DV_{\mathtt{DD}}$ |

| External IF <sub>x</sub> OUT± Pull-Up Supply                                    |                          |           | $DV_{DD}$ | V    |                                                          |

| Mixer Current in High Linearity<br>Mode                                         |                          | 80        |           | mA   | Mixer V to I bias (Register 13, Bits[DB24:DB22]) = 4     |

| Mixer Current in Low Power Mode                                                 |                          | 40        |           | mA   | Mixer V to I bias (Register 13, Bits[DB24:DB22]) = 1     |

| IF DGA Current                                                                  |                          | 140       |           | mA   | Per amplifier                                            |

| Total Current                                                                   |                          |           |           |      | Dual Rx enabled                                          |

| High Linearity Mode                                                             |                          | 440       | 550       | mA   | Mixer V to I bias (Register 13, Bits[DB24:DB22]) = 4     |

| Low Power Mode                                                                  |                          | 260       |           | mA   | Mixer V to I bias (Register 13, Bits[DB24:DB22]) = 1     |

| Low Power Sleep Mode                                                            |                          | 450       | 1000      | μΑ   |                                                          |

| Standby Mode                                                                    |                          | 65        |           | mA   | Both mixers and DGAs in standby mode                     |

| TIMING <sup>2</sup>                                                             |                          |           |           |      |                                                          |

| Channel Power-Up from Standby<br>Mode After Changing State of<br>CHAEN or CHBEN |                          | 100       | 400       | ns   | From standby mode to normal operation                    |

$^{\rm 1}$  DC-coupled; lower cutoff frequency determined mostly by external components.  $^{\rm 2}$  Not tested in production; guaranteed by characterization.

#### SUPPLEMENTAL INFORMATION FOR MIXERS AND IF DGAS

$MIX_AV_{DD} = MIX_BV_{DD} = DV_{DD} = DOV_{DD} = DGA_AV_{DD} = DGA_BV_{DD} = 3.3 V \pm 5\%$ ;  $AGND = 0 V. T_A = T_{MIN}$  to  $T_{MAX}$ . The operating temperature range =  $-40^{\circ}$ C to  $+105^{\circ}$ C. Parameters are measured on a standard test circuit with an IF filter;  $f_{RF} = 1.95$  GHz, PRF = -10 dBm,  $f_{LO} = 2.231$  GHz, and  $f_{IF} = 281$  MHz, using standard register settings, maximum DGA gain, high linearity mode, unless otherwise noted. For IP2 and IP3 measurements,  $f_{RF1} = 1.949$  GHz and  $f_{RF2} = 1.951$  GHz, minimum DGA gain.

| Table 2.                            | B.4.1- | <b>T</b> |     | 11      | To at Care distance (Carena anta |

|-------------------------------------|--------|----------|-----|---------|----------------------------------|

| Parameter                           | Min    | Тур      | Max | Unit    | Test Conditions/Comments         |

| MIXER CHARACTERISTICS               |        |          |     |         |                                  |

| Voltage Conversion Gain             |        | 7        |     | dB      |                                  |

| Input P1dB                          |        |          |     |         |                                  |

| High Linearity Mode                 |        | 12       |     | dBm     |                                  |

| Low Power Mode                      |        | 4        |     | dBm     |                                  |

| Second-Order Input Intercept (IIP2) |        | 55       |     | dBm     | 0 dBm per tone, minimum DGA gain |

| Third-Order Input Intercept (IIP3)  |        |          |     |         | 0 dBm per tone, minimum DGA gain |

| High Linearity Mode                 |        | 29       |     | dBm     |                                  |

| Low Power Mode                      |        | 17       |     | dBm     |                                  |

| SSB NF                              |        |          |     |         |                                  |

| RF = 1950 MHz                       |        | 12       |     | dB      |                                  |

|                                     |        |          |     |         |                                  |

| LO to RF Leakage                    |        | -30      |     | dBm     |                                  |

| LO to IF Leakage                    |        | -40      |     | dBm     |                                  |

| RF to IF Leakage                    |        | -50      |     | dBc     | Relative to IF output level      |

| IF DGAs                             |        |          |     |         |                                  |

| Voltage Gain                        |        | 22       |     | dB      |                                  |

| Gain Step                           |        | 0.5      |     | dB      |                                  |

| Gain Conformance Error              |        | 0.05     |     | dB      | Any two adjacent steps           |

| Phase Conformance Error             |        | 0.5      |     | Degrees | Any two adjacent steps           |

| Output P1dB                         |        | 19       |     | dBm     |                                  |

| Output IP3 (OIP3)                   |        | 40       |     | dBm     |                                  |

| Bandwidth                           |        | 520      |     | MHz     |                                  |

| SSB NF                              |        | 7        |     | dB      |                                  |

| Second Harmonic Level               |        | -65      |     | dBc     | At 2 V p-p                       |

| Third Harmonic Level                |        | -65      |     | dBc     | At 2 V p-p                       |

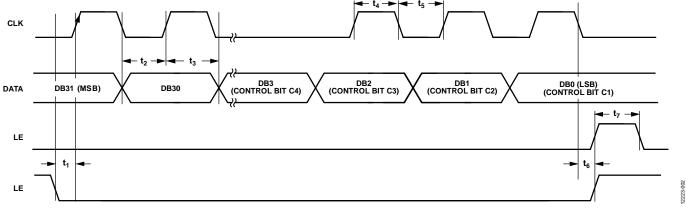

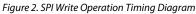

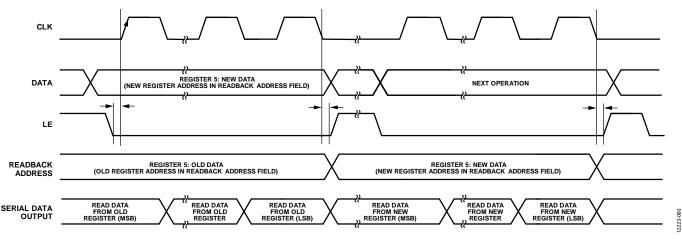

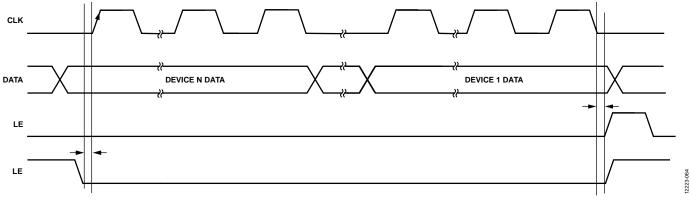

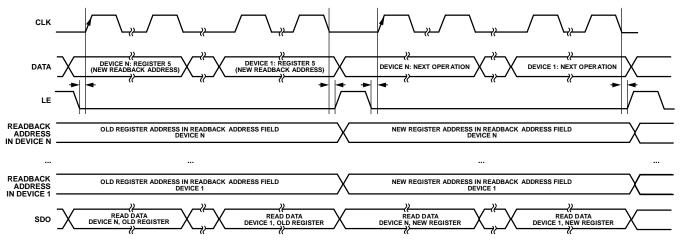

#### TIMING SPECIFICATIONS

$MIX_{A}V_{DD} = MIX_{B}V_{DD} = DV_{DD} = LOV_{DD} = DGA_{A}V_{DD} = DGA_{B}V_{DD} = 3.3 \text{ V} \pm 5\%; \text{ AGND} = 0 \text{ V}. 1.8 \text{ V} \text{ and } 3.3 \text{ V} \text{ logic levels used. } T_{A} = T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise noted.}$

#### Table 3.

| Parameter                   | Symbol         | Min Typ | Max | Unit | Test Conditions/Comments |

|-----------------------------|----------------|---------|-----|------|--------------------------|

| LE Setup Time               | t <sub>1</sub> | 20      |     | ns   |                          |

| DATA to CLK Setup Time      | t <sub>2</sub> | 10      |     | ns   |                          |

| DATA to CLK Hold Time       | t <sub>3</sub> | 10      |     | ns   |                          |

| CLK High Duration           | t4             | 25      |     | ns   |                          |

| CLK Low Duration            | t <sub>5</sub> | 25      |     | ns   |                          |

| CLK to LE Setup Time        | t <sub>6</sub> | 10      |     | ns   |                          |

| LE Pulse Width              | t7             | 20      |     | ns   |                          |

| CLK Low to SDO Output Valid | t <sub>8</sub> |         | 20  | ns   | During readback          |

#### **Timing Diagram**

Figure 3. SPI Readback Operation Timing Diagram

## **ABSOLUTE MAXIMUM RATINGS**

$T_A = 25^{\circ}C$ , unless otherwise noted.

#### Table 4.

| Parameter                                                           | Rating                             |

|---------------------------------------------------------------------|------------------------------------|

| Supply Voltage Pins <sup>1</sup> to GND <sup>2</sup>                | –0.3 V to +3.9 V                   |

| Supply Voltage Pins <sup>1</sup> to DV <sub>DD</sub>                | –0.3 V to +0.3 V                   |

| Digital Input Output (I/O) Voltage to GND                           | -0.3 V to DV <sub>DD</sub> + 0.3 V |

| Analog I/O Voltage to GND                                           | -0.3 V to DV <sub>DD</sub> + 0.3 V |

| RF Input Power                                                      | 20 dBm                             |

| LO Input Power                                                      | 10 dBm                             |

| ESD Ratings                                                         |                                    |

| Human Body Model (HBM)                                              | 1.5 kV                             |

| Field Induced Charged Device Model<br>(FICDM)                       | 500 V                              |

| Operating Temperature Range                                         | –40°C to +105°C                    |

| Storage Temperature Range                                           | –65°C to +125°C                    |

| Maximum Junction Temperature                                        | 150°C                              |

| Thermal Resistance (θ <sub>JA</sub> ), with Exposed<br>Pad Soldered | 27.26°C/W                          |

| Reflow Soldering                                                    |                                    |

| Peak Temperature                                                    | 260°C                              |

| Time at Peak Temperature                                            | 40 sec                             |

$^1$  The supply voltage pins include  $MIX_AV_{DD},$   $DV_{DD},$   $MIX_BV_{DD},$   $DGA_BV_{DD},$   $LOV_{DD},$  and  $DGA_AV_{DD}.$

$^{2}$ GND = AGND = DGND = 0 V

$^3$  The digital I/O pins include LATCH\_A, CH\_AEN, CH\_BEN, LATCH\_B, B5 to B0, LE, CLK, DATA, SDO, and A0 to A5.

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

The ADRF6658 is a high performance RF integrated circuit, and it is ESD sensitive. Take proper precautions for handling and assembly.

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

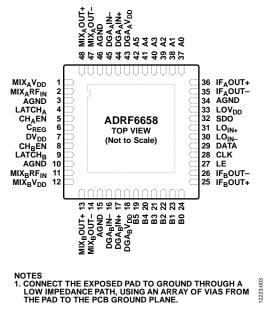

## **PIN CONFIGURATION AND FUNCTION DESCRIPTIONS**

Figure 4. Pin Configuration

#### **Table 5. Pin Function Descriptions**

| Pin No.                   | Mnemonic                          | Description                                                                                                                                                                                                                                                                                                                                    |

|---------------------------|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                         | MIX <sub>A</sub> V <sub>DD</sub>  | Supply for Mixer A. The voltage level on this pin must be equal to that on DV <sub>DD</sub> . Place decoupling capacitors to the ground plane as close as possible to this pin.                                                                                                                                                                |

| 2                         | MIX <sub>A</sub> RF <sub>IN</sub> | RF Input for Mixer A. This pin has an input impedance of 50 $\Omega$ .                                                                                                                                                                                                                                                                         |

| 3                         | AGND                              | Analog Ground. This is a ground return path for $MIX_AV_{DD}$ (Pin 1).                                                                                                                                                                                                                                                                         |

| 4                         | LATCH <sub>A</sub>                | Channel A Latch Buffer Control. This pin controls the latch buffer between the 6-bit parallel control port (Pin A0 to Pin A5) and the Channel A DGA.                                                                                                                                                                                           |

| 5                         | CHAEN                             | Channel A Enable. This pin provides external control of the power-down mode for Channel A.                                                                                                                                                                                                                                                     |

| 6                         | Creg                              | Internal Regulator Output. A capacitor of approximately 220 nF must be placed between this output and ground.                                                                                                                                                                                                                                  |

| 7                         | DV <sub>DD</sub>                  | Supply Connection for Digital Circuits. The voltage on this pin ranges from 3.15 V to 3.45 V. Place decoupling capacitors to the ground plane as close as possible to this pin.                                                                                                                                                                |

| 8                         | CH₀EN                             | Channel B Enable. This pin provides external control of the power-down mode for Channel B.                                                                                                                                                                                                                                                     |

| 9                         | LATCH <sub>B</sub>                | Channel B Latch Buffer Control. This pin controls the latch buffer between the 6-bit parallel control port (Pin B0 to Pin B5) and the Channel B DGA.                                                                                                                                                                                           |

| 10                        | AGND                              | Analog Ground. This is a ground return path for $MIX_BV_{DD}$ (Pin 12).                                                                                                                                                                                                                                                                        |

| 11                        | $MIX_BRF_{IN}$                    | RF Input for Mixer B. This pin has an input impedance 50 $\Omega$ .                                                                                                                                                                                                                                                                            |

| 12                        | MIX <sub>B</sub> V <sub>DD</sub>  | Supply for Mixer B. The voltage level on this pin must be equal to that on D <sub>VDD</sub> . Place decoupling capacitors to the ground plane as close as possible to this pin.                                                                                                                                                                |

| 13, 14                    | MIX₀OUT+,<br>MIX₀OUT–             | Differential Mixer B Outputs, 300 $\Omega$ Impedance. A pull-up inductor must be connected to each of these output pins. The values of the inductors depend on the IF frequency range.                                                                                                                                                         |

| 15                        | AGND                              | Analog Ground. This is a ground return path for $DGA_{\mathbb{B}}V_{DD}$ (Pin 18).                                                                                                                                                                                                                                                             |

| 16, 17                    | DGABIN–,<br>DGABIN+               | Differential DGA B Inputs, 300 $\Omega$ Impedance.                                                                                                                                                                                                                                                                                             |

| 18                        | $DGA_{B}V_{DD}$                   | Supply for DGA B. The voltage level on this pin must be equal to that on DV <sub>DD</sub> . Place decoupling capacitors to the analog ground plane as close as possible to this pin.                                                                                                                                                           |

| 19, 20, 21,<br>22, 23, 24 | B5, B4, B3, B2,<br>B1, B0         | 6-Bit Parallel Control Ports for DGA B.                                                                                                                                                                                                                                                                                                        |

| 25, 26                    | IFBOUT+,<br>IFBOUT–               | Channel B Differential IF Outputs, 100 $\Omega$ Resistance from DGA B. Requires a pull-up inductor dependent on IF frequency.                                                                                                                                                                                                                  |

| 27                        | LE                                | Latch Enable. When the LE input pin goes low, data is clocked into the 32-bit shift register on the CLK rising edge. Only the last 32 bits are retained. When the LE input pin goes high, the data stored in the shift register is loaded into one of the 16 registers, the relevant latch being selected by the four LSBs of the 32-bit word. |

# **Data Sheet**

ADRF6658

| Pin No.                   | Mnemonic                                        | Description                                                                                                                                                                                                                         |  |  |  |  |  |

|---------------------------|-------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 28                        | CLK                                             | Serial Clock Input. Data is clocked into the 32-bit shift register on the CLK rising edge. This input is a high impedance CMOS input.                                                                                               |  |  |  |  |  |

| 29                        | DATA                                            | Serial Data Input. The serial data input is loaded MSB first with the four LSBs control the destination for the data. This input is a high impedance CMOS input.                                                                    |  |  |  |  |  |

| 30                        | LO <sub>IN-</sub>                               | Complimentary External Local Oscillator Input. In differential LO mode, this pin is one of the input pins of the differential input and must be ac-coupled. In single-ended LO mode, terminate this pin to ground with a capacitor. |  |  |  |  |  |

| 31                        | LO <sub>IN+</sub>                               | External Local Oscillator Input. In differential LO mode, this pin one of the input pins of the differential input.<br>In single-ended LO mode, it is the input of the LO signal. AC couple this pin.                               |  |  |  |  |  |

| 32                        | SDO                                             | Serial Data Output. This output is used to read back the register content.                                                                                                                                                          |  |  |  |  |  |

| 33                        | LOVDD                                           | Power Supply for the LO Path. The voltage level on this pin must be equal to that on DVDD. Place decoupling capacitors to the ground plane as close as possible to this pin.                                                        |  |  |  |  |  |

| 34                        | AGND                                            | Analog Ground. This is a ground return path for LOV <sub>DD</sub> (Pin 33).                                                                                                                                                         |  |  |  |  |  |

| 35, 36                    | IF <sub>A</sub> OUT–,<br>IF <sub>A</sub> OUT+   | Channel A Differential IF Outputs, 100 $\Omega$ Resistance from DGA A. Requires a pull-up inductor dependent on IF frequency.                                                                                                       |  |  |  |  |  |

| 37, 38, 39,<br>40, 41, 42 | A0, A1, A2, A3,<br>A4, A5                       | 6-Bit Parallel Control Ports for DGA A.                                                                                                                                                                                             |  |  |  |  |  |

| 43                        | DGA <sub>A</sub> V <sub>DD</sub>                | Supply for DGA A. The voltage level on this pin must be equal to that on DV <sub>DD</sub> . Place decoupling capacitors to the analog ground plane as close as possible to this pin.                                                |  |  |  |  |  |

| 44, 45                    | DGA <sub>A</sub> IN+,<br>DGA <sub>A</sub> IN–   | Differential DGA A Inputs, 300 $\Omega$ Impedance.                                                                                                                                                                                  |  |  |  |  |  |

| 46                        | AGND                                            | Analog Ground. This is a ground return path for $DGA_AV_{DD}$ (Pin 43).                                                                                                                                                             |  |  |  |  |  |

| 47, 48                    | MIX <sub>A</sub> OUT–,<br>MIX <sub>A</sub> OUT+ | Differential Mixer A Outputs, 300 $\Omega$ Impedance. A pull-up inductor must be connected to each of these output pins. The values of the inductors depend on the IF frequency range.                                              |  |  |  |  |  |

| 49                        | EP                                              | Exposed Pad. Connect the exposed pad to ground through a low impedance path, using an array of vias from the pad to the PCB ground plane.                                                                                           |  |  |  |  |  |

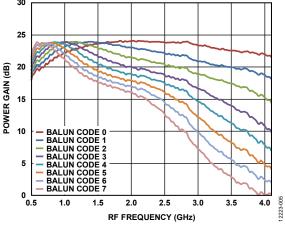

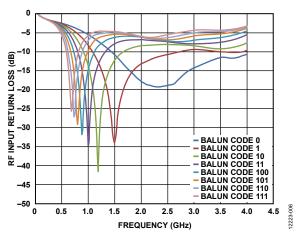

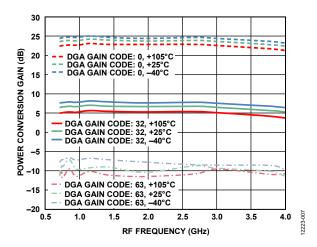

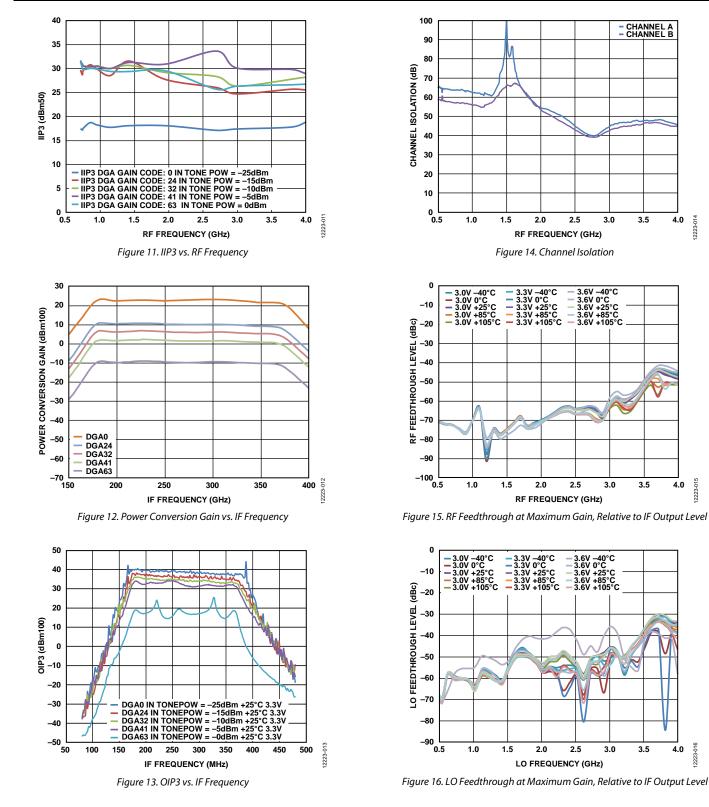

## **TYPICAL PERFORMANCE CHARACTERISTICS**

Figure 5. Power Gain vs. RF Frequency and Balun Codes

Figure 6. RF Input Return Loss vs. Frequency and Balun Codes

Figure 7. Power Conversion Gain vs. RF Frequency for DGA Gain Code = 0, 32, and 63

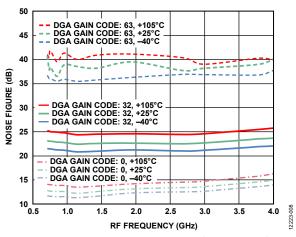

Figure 8. Noise Figure vs. RF Frequency and DGA Gain Codes

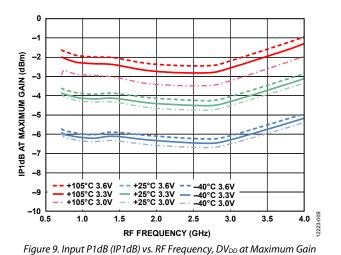

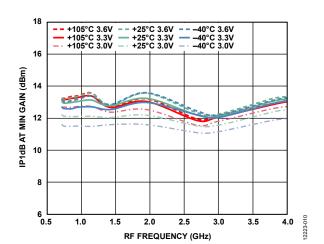

Figure 10. IP1dB vs. RF Frequency and DV<sub>DD</sub> at Minimum Gain

## **Data Sheet**

# ADRF6658

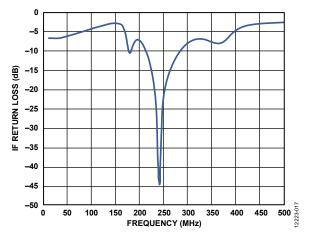

Figure 17. IF DGA Output Return Loss Measured Through Balun

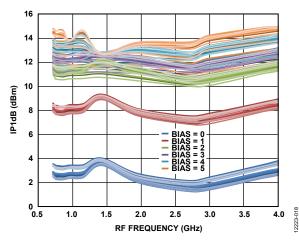

Figure 18. IP1dB vs. RF Frequency and V to I Bias

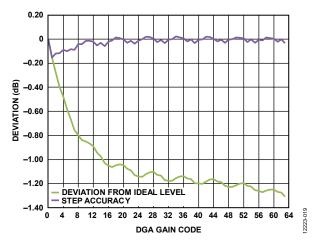

Figure 19. DGA Step Accuracy

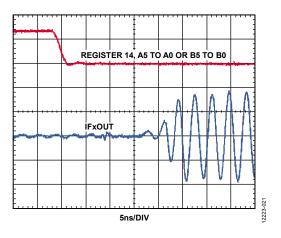

Figure 20. Gain Step Response, Maximum Gain to Minimum Gain

Figure 21. Gain Step Response, Minimum Gain to Maximum Gain

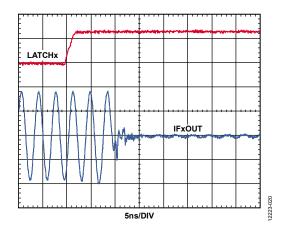

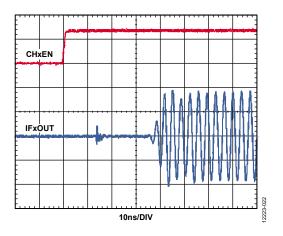

Figure 22. Channel Enable Response

## THEORY OF OPERATION DUAL MIXER CORES

The ADRF6658 provides two double balanced active mixers based on the Gilbert cell design. The RF inputs, LO inputs, and IF outputs of the mixers are all differential, providing maximum usable bandwidth at the input and output ports. The mixers are designed for a 50  $\Omega$  input impedance and a 300  $\Omega$  output impedance, with external RF chokes connected to the supply.

#### **Mixer RF Inputs**

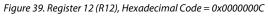

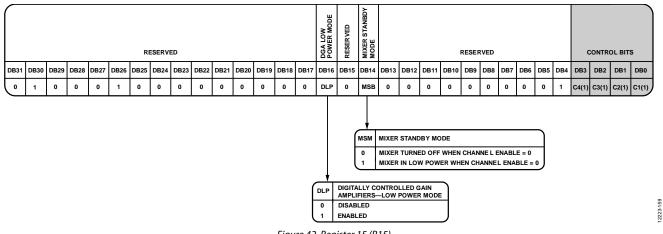

At the RF input of each channel (MIX<sub>A</sub>RF<sub>IN</sub> and MIX<sub>B</sub>RF<sub>IN</sub>) of the ADRF6658, a tunable balun converts the single-ended input signal into differential form, to be fed into the mixer section. The tuning of the balun is controlled by the two sets of register bits: RF balun input cutoff ( $C_{IN}$ ) in Register 13, Bits[DB12:DB10], and RF balun output cutoff ( $C_{OUT}$ ) in Register 13, Bits[DB9:DB7].

#### **Mixers Bias Circuit**

A band gap reference circuit generates the reference currents used by mixers. The bias current for the LO circuit of the mixers can be programmed via the mixer LO I<sub>BIAS</sub> bits in Register 13, Bits[DB26:DB25].

#### RF Voltage to Current (V to I) Converter

The differential RF input signal, created in the internal balun from the external, single-ended RF signal provided to the  $MIX_ARF_{IN}$  or  $MIX_BRF_{IN}$  pin, is applied to a V to I converter that converts the differential input voltage to output currents. The V to I converter provides a 50  $\Omega$  input impedance. The V to I section bias current can be adjusted up or down using the mixer V to I I<sub>BIAS</sub> bits in Register 13, Bits[DB24:DB22]. Adjusting the current up improves IIP3 and P1dB input, but degrades the SSB NF. Adjusting the current down improves the SSB NF but degrades IIP3 and the input P1dB. The conversion gain remains nearly constant over a wide range of mixer V to I I<sub>BIAS</sub> settings, allowing the device to be adjusted dynamically without affecting the conversion gain. A setting of 3 or 4 provides a good trade-off of IP3 and SSB NF.

#### **Mixer Power-Down**

It is possible to power down either mixer by programming the relevant bits. For Channel A, program the Mixer A enable bit (Bit DB5 in Register 13). For Channel B, program the Mixer B Enable bit (Bit DB4 in Register 13). The mixers can be powered down independently.

#### **Mixer Output**

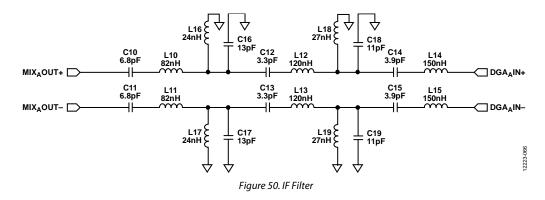

The mixer load uses a pair of 150  $\Omega$  resistors connected to the positive supply. This provides a 300  $\Omega$  differential output resistance, which matches the input impedance of the internal IF DGA block. Pull the mixer outputs to the positive supply externally using a pair of RF chokes, or by using an output transformer with the center tap connected to the positive supply. The mixer outputs are dc-coupled, and they can operate up to approximately 500 MHz into a 300  $\Omega$  load.

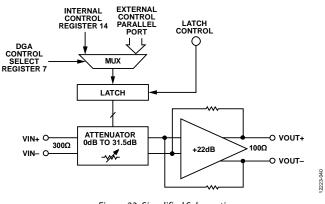

#### DGA BASIC STRUCTURE

In each channel, the ADRF6658 has a built-in, variable gain DGA. Each amplifier consists of a digitally controlled, passive attenuator of a 300  $\Omega$  differential input impedance followed by a highly linear transconductance amplifier with feedback. The output impedance of the gain amplifier is 100  $\Omega$ , differentially. The input impedance of the DGA block matches the output impedance of the internal mixer.

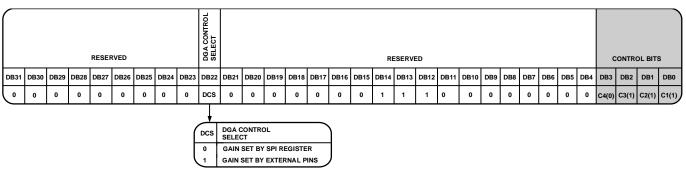

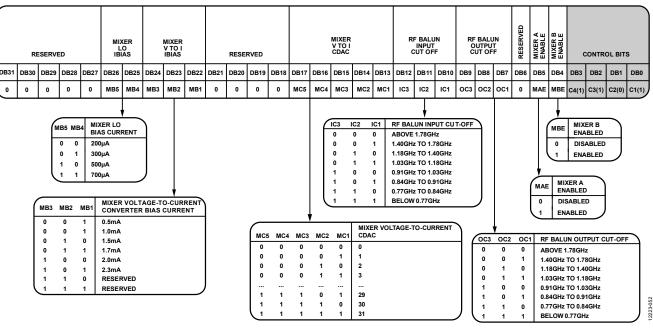

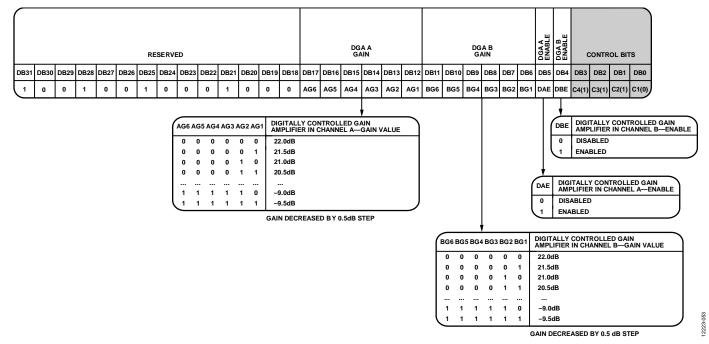

The gain of each amplifier can be programmed independently, either via the DGA control bits in the serial control registers, or via an external, 6-bit parallel port. The choice of serial or parallel control is determined by the DGA control select bit, Bit DB22 in Register 7. Programming this bit to 0 allows the gain to be set by programming Register 14 (Bits[DB17:DB12] for Channel A, or Bits[DB11:DB6] for Channel B). When the DGA Control Select bit is set to 1, the gain is set by the binary value applied to the 6-bit, external parallel control interface (Pin A5 through Pin A0 for Channel A, or Pin B5 through Pin B0 for Channel B).

Figure 23. Simplified Schematic

#### Input System

The dc voltage level at the inputs of each amplifier is set to approximately 1.1 V by two independent internal voltage reference circuits. These reference circuits are not accessible and cannot be adjusted.

Power down each amplifier by setting Bit DB5 and Bit DB4.in Register 14. When powered down, the total current of each amplifier reduces to 10  $\mu$ A (typical). The dc level at the inputs remains at approximately 1.6 V, regardless of the state of Bit DB5 and Bit DB4 in Register 14.

#### **Output Amplifier**

The gain of the output amplifier is set to 22 dB when driving a 100  $\Omega$  load. The input resistance of this amplifier is set to 300  $\Omega$  in matched condition, and its output resistance is set to 100  $\Omega$ . If the load resistance is different from 100  $\Omega$ , use the following equations to determine the resulting gain and input/output resistances:

$A_{V} = 0.15 \times (3800)/R_{L}$   $R_{IN} = (3800 + R_{L})/(1 + 0.15 \times R_{L})$   $S21 (Gain) = 2 \times R_{IN}/(R_{IN} + 300) \times A_{V}$   $R_{OUT} = (2000 + R_{S})/(1 + 0.09 \times R_{S})$

where:

Av is the voltage gain.

$R_L$  is the load resistance.

$R_{IN}$  is the input resistance.

*S21* is the insertion gain.

$R_{OUT}$  is the output resistance.

Note that at the maximum attenuation setting,  $R_s$ , as seen by the output amplifier, is the output resistance of the attenuator, which is 300  $\Omega$ . However, at minimum attenuation,  $R_s$  is the source resistance connected to the DGA inputs of the device.

The dc current to the outputs of each amplifier is supplied through two external chokes. The inductance of the chokes and the resistance of the load, in parallel with the output resistance of the device, adds a low frequency pole to the response. The parasitic capacitance of the chokes adds to the output capacitance of the device. This total capacitance, in parallel with the load and output resistance, sets the high frequency pole of the device. Generally, the larger the inductance of the choke, the higher its parasitic capacitance. Therefore, this trade-off must be considered when the value and type of the choke are selected.

For an operation frequency of 45 MHz to 500 MHz when driving a 100  $\Omega$  load, 1.2  $\mu$ H chokes with a self resonant frequency (SRF) of 375 MHz or higher are recommended (such as the 0805AF-122XJRB from Coilcraft). If higher value chokes are used, gain peaking may occur at the low frequency end of the pass band due to ac-coupling in the internal feedback path of the amplifier. The supply current of each amplifier takes about 80 mA through the two chokes combined in high linearity mode (Register 13, Bits[DB24:DB22] = 4). The current increases with temperature at approximately 2.5 mA per 10°C.

#### **Gain Control**

The gain of each amplifier can be adjusted using the parallel control interface or the SPI. The gain step size is 0.5 dB. Each amplifier has a maximum gain of +22 dB (Code 0) to -9.5 dB (Code 63). LATCH<sub>A</sub> or LATCH<sub>B</sub> must be at or transitioned to logic high after programming through the parallel or serial interface for the gain change to take effect.

The NF of each amplifier is approximately 4 dB at the maximum gain setting, relative to a 300  $\Omega$  source. This represents approximately 22.5 nV $\sqrt{\text{Hz}}$  noise referred to the amplifier output. The NF increases as the gain is reduced, and this increase is equal to the reduction in gain. The linearity of the device measured at the output is first-order independent of the gain setting. From -4 dB to +22 dB gain, OIP3 is approximately 40 dBm into a 100  $\Omega$  load at 281 MHz (+1 dBm per tone). At gain settings below -4 dB, OIP3 drops to approximately 28 dBm.

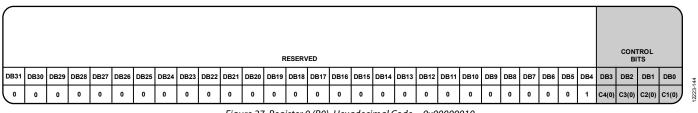

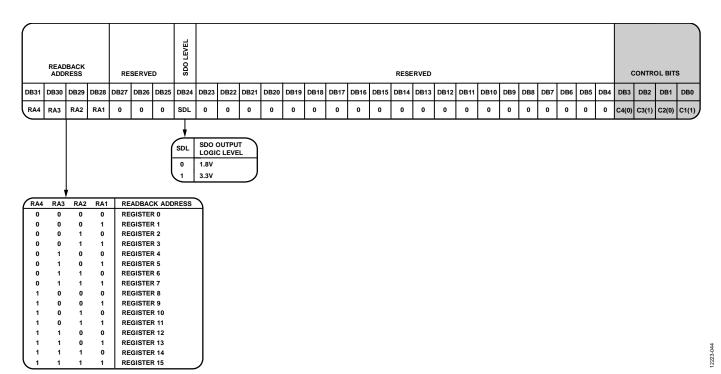

#### SERIAL INPUT SHIFT REGISTERS

Data is clocked into the 32-bit shift register on each rising edge of CLK, MSB first. Data transfers from the shift register to one of sixteen latches on the rising edge of LE. The destination latch is determined by the state of the four control bits (C4, C3, C2, and C1) in the shift register. As shown in Figure 2, these are the four LSBs: DB3, DB2, DB1, and DB0. See Table 6 for the truth table for these bits. Figure 27 through Figure 42 describe the function of the control registers in the ADRF6658. The Register Maps section summarizes how to program the latches.

#### **PROGRAM MODES**

Table 6 and Figure 27 through Figure 42 show how to set up the program modes in the ADRF6658.

Table 6. Truth Table for Control Bits C4, C3, C2, and C1

|    | Cor | ntrol Bits |    |                   |

|----|-----|------------|----|-------------------|

| C4 | C3  | C2         | C1 | Register          |

| 0  | 0   | 0          | 0  | Register 0 (R0)   |

| 0  | 0   | 0          | 1  | Register 1 (R1)   |

| 0  | 0   | 1          | 0  | Register 2 (R2)   |

| 0  | 0   | 1          | 1  | Register 3 (R3)   |

| 0  | 1   | 0          | 0  | Register 4 (R4)   |

| 0  | 1   | 0          | 1  | Register 5 (R5)   |

| 0  | 1   | 1          | 0  | Register 6 (R6)   |

| 0  | 1   | 1          | 1  | Register 7 (R7)   |

| 1  | 0   | 0          | 0  | Register 8 (R8)   |

| 1  | 0   | 0          | 1  | Register 9 (R9)   |

| 1  | 0   | 1          | 0  | Register 10 (R10) |

| 1  | 0   | 1          | 1  | Register 11 (R11) |

| 1  | 1   | 0          | 0  | Register 12 (R12) |

| 1  | 1   | 0          | 1  | Register 13 (R13) |

| 1  | 1   | 1          | 0  | Register 14 (R14) |

| 1  | 1   | 1          | 1  | Register 15 (R15) |

## **REGISTER MAPS**

|      |      |      |      |      |      |      |      |      |      |      |      |      |       | RE   | GIST | ER 0 |      |      |      |      |      |     |     |     |     |     |          |       |       |            |       |

|------|------|------|------|------|------|------|------|------|------|------|------|------|-------|------|------|------|------|------|------|------|------|-----|-----|-----|-----|-----|----------|-------|-------|------------|-------|

|      |      |      |      |      |      |      |      |      |      |      |      | R    | ESERV | /ED  |      |      |      |      |      |      |      |     |     |     |     |     | RESERVED |       | CONT  | TROL<br>TS |       |

| DB31 | DB30 | DB29 | DB28 | DB27 | DB26 | DB25 | DB24 | DB23 | DB22 | DB21 | DB20 | DB19 | DB18  | DB17 | DB16 | DB15 | DB14 | DB13 | DB12 | DB11 | DB10 | DB9 | DB8 | DB7 | DB6 | DB5 | DB4      | DB3   | DB2   | DB1        | DB0   |

| C    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0     | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0   | 0   | 0   | 0   | 0   | 1        | C4(0) | C3(0) | C2(0)      | C1(0) |

|           |      |      |      |          |          |          |      |          |      |      |      |      |       | RE   | GIST     | ER 1 |      |      |      |          |      |     |     |     |     |          |     |       |       |       |       |

|-----------|------|------|------|----------|----------|----------|------|----------|------|------|------|------|-------|------|----------|------|------|------|------|----------|------|-----|-----|-----|-----|----------|-----|-------|-------|-------|-------|

| $\bigcap$ |      |      |      |          |          |          |      |          |      |      |      |      |       |      |          |      |      |      |      |          |      |     |     |     |     |          |     |       |       |       |       |

|           |      |      |      |          |          |          |      |          |      |      |      |      |       |      |          |      |      |      |      |          |      |     |     |     |     |          |     |       |       |       |       |

|           |      |      |      |          |          |          |      |          |      |      |      |      |       |      |          |      |      |      |      |          |      |     |     |     |     |          |     |       | CON   | TROL  |       |

|           |      |      |      |          |          |          |      |          |      |      |      | R    | ESERV | 'ED  |          |      |      |      |      |          |      |     |     |     |     |          |     |       | BI    | ITS   |       |

| DB31      | DB30 | DB29 | DB28 | DB27     | DB26     | DB25     | DB24 | DB23     | DB22 | DB21 | DB20 | DB19 | DB18  | DB17 | DB16     | DB15 | DB14 | DB13 | DB12 | DB11     | DB10 | DB9 | DB8 | DB7 | DB6 | DB5      | DB4 | DB3   | DB2   | DB1   | DB0   |

| 0         | 0    | 0    | 0    | 0        | 0        | 0        | 0    | 0        | 0    | 0    | 0    | 0    | 0     | 0    | 0        | 0    | 0    | 0    | 0    | 0        | 0    | 0   | 0   | 0   | 0   | 0        | 0   | C4(0) | C3(0) | C2(0) | C1(1) |

| Ľ         | 0    | 0    | 0    | <b>1</b> | <b>1</b> | <b>1</b> | v    | <b>1</b> | U    | U    | 0    | J    | U     |      | <b>1</b> | J    |      | J    |      | <b>,</b> | J    | U   | U   | J   | U   | <b>"</b> | J   | C4(0) | C3(0) | C2(0) | Ľ     |

| $\left[ \right]$ |      |      |      |      |      |      |      |      |      |      |      | P | ESERV |   |      |      |      |      |      |      |      |     |     |     |     |     |     |       | CONT  |       |       |

|------------------|------|------|------|------|------|------|------|------|------|------|------|---|-------|---|------|------|------|------|------|------|------|-----|-----|-----|-----|-----|-----|-------|-------|-------|-------|

| DB31             | DB30 | DB29 | DB28 | DB27 | DB26 | DB25 | DB24 | DB23 | DB22 | DB21 | DB20 |   | -     |   | DB16 | DB15 | DB14 | DB13 | DB12 | DB11 | DB10 | DB9 | DB8 | DB7 | DB6 | DB5 | DB4 | DB3   |       | -     | DB0   |

| ŀ                | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0 | 0     | 0 | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0   | 0   | 0   | 0   | 0   | 0   | C4(0) | C3(0) | C2(1) | C1(0) |

|        |      |      |      |      |      |      |      |      |      |      |      |      |       |      |      | -    |      |      |      |      |      |     |     |     |     |     |     |       |            |       |       |

|--------|------|------|------|------|------|------|------|------|------|------|------|------|-------|------|------|------|------|------|------|------|------|-----|-----|-----|-----|-----|-----|-------|------------|-------|-------|

| $\int$ |      |      |      |      |      |      |      |      |      |      |      |      |       |      |      |      |      |      |      |      |      |     |     |     |     |     |     |       |            |       |       |

|        |      |      |      |      |      |      |      |      |      |      |      | R    | ESERV | ED   |      |      |      |      |      |      |      |     |     |     |     |     |     |       | CONT<br>BI |       |       |

| DB31   | DB30 | DB29 | DB28 | DB27 | DB26 | DB25 | DB24 | DB23 | DB22 | DB21 | DB20 | DB19 | DB18  | DB17 | DB16 | DB15 | DB14 | DB13 | DB12 | DB11 | DB10 | DB9 | DB8 | DB7 | DB6 | DB5 | DB4 | DB3   | DB2        | DB1   | DB0   |

| O      | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0     | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0   | 0   | 0   | 0   | 0   | 0   | C4(0) | C3(0)      | C2(1) | C1(1) |

|           |      |      |      |      |      |      |      |      |      |      |      |      |       | RE   | GIST | ER 4 |      |      |      |      |      |     |     |     |     |     |     |       |       |       |       |

|-----------|------|------|------|------|------|------|------|------|------|------|------|------|-------|------|------|------|------|------|------|------|------|-----|-----|-----|-----|-----|-----|-------|-------|-------|-------|

| $\bigcap$ |      |      |      |      |      |      |      |      |      |      |      |      |       |      |      |      |      |      |      |      |      |     |     |     |     |     |     |       |       |       |       |

|           |      |      |      |      |      |      |      |      |      |      |      |      |       |      |      |      |      |      |      |      |      |     |     |     |     |     |     |       |       |       |       |

|           |      |      |      |      |      |      |      |      |      |      |      | P    | ESERV | 'ED  |      |      |      |      |      |      |      |     |     |     |     |     |     |       | CONT  |       |       |

|           | -    |      |      |      |      |      |      |      |      |      |      |      |       |      |      |      |      |      |      |      |      |     |     |     |     |     |     |       |       |       |       |

| DB31      | DB30 | DB29 | DB28 | DB27 | DB26 | DB25 | DB24 | DB23 | DB22 | DB21 | DB20 | DB19 | DB18  | DB17 | DB16 | DB15 | DB14 | DB13 | DB12 | DB11 | DB10 | DB9 | DB8 | DB7 | DB6 | DB5 | DB4 | DB3   | DB2   | DB1   | DB0   |

| 0         | 0    | 1    | 1    | 1    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0     | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0   | 0   | 0   | 0   | 0   | 0   | C4(0) | C3(1) | C2(0) | C1(0) |

|      |             |      |      |      |       |      |           |      |      |      |      |      |      | RE   | GISTE | R 5  |      |      |      |      |      |     |     |     |     |     |     |       |       |        |       |

|------|-------------|------|------|------|-------|------|-----------|------|------|------|------|------|------|------|-------|------|------|------|------|------|------|-----|-----|-----|-----|-----|-----|-------|-------|--------|-------|

|      | READ<br>ADD | BACK |      | RE   | SERVE | D    | SDO LEVEL |      |      |      |      |      |      |      |       |      | RESE | RVED |      |      |      |     |     |     |     |     |     | c     | ONTRO | DL BIT | s     |

| DB31 | DB30        | DB29 | DB28 | DB27 | DB26  | DB25 | DB24      | DB23 | DB22 | DB21 | DB20 | DB19 | DB18 | DB17 | DB16  | DB15 | DB14 | DB13 | DB12 | DB11 | DB10 | DB9 | DB8 | DB7 | DB6 | DB5 | DB4 | DB3   | DB2   | DB1    | DB0   |

| RA4  | RA3         | RA2  | RA1  | 0    | 0     | 0    | SDL       | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0     | 0    | 0    | 0    | 0    | 0    | 0    | 0   | 0   | 0   | 0   | 0   | 0   | C4(0) | C3(1) | C2(0)  | C1(1) |

Figure 24. Register Summary (Register 0 Through Register 5)

# **Data Sheet**

Downloaded from Arrow.com.

**ADRF6658**

## **REGISTER 2**

## **REGISTER 3**

### REGISTER 5

Downloaded from Arrow.com.

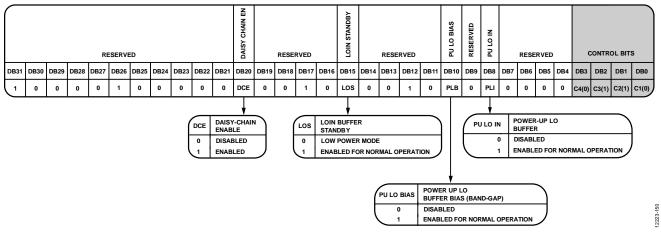

|      |      |      |      |      |        |      |      |      |      |      |                |      |      | RE   | GIST | ER 6         |      |      |      |      |            |          |          |     |      |      |     |       |        |        |       |

|------|------|------|------|------|--------|------|------|------|------|------|----------------|------|------|------|------|--------------|------|------|------|------|------------|----------|----------|-----|------|------|-----|-------|--------|--------|-------|

|      |      |      |      | RE   | ESERVE | Đ    |      |      |      |      | DAISY-CHAIN EN |      | RESE | RVED |      | LOIN STANDBY |      | RESE | RVED |      | PU LO BIAS | RESERVED | PU LO IN |     | RESE | RVED | 1   | c     | CONTRO | DL BIT | s     |

| DB31 | DB30 | DB29 | DB28 | DB27 | DB26   | DB25 | DB24 | DB23 | DB22 | DB21 | DB20           | DB19 | DB18 | DB17 | DB16 | DB15         | DB14 | DB13 | DB12 | DB11 | DB10       | DB9      | DB8      | DB7 | DB6  | DB5  | DB4 | DB3   | DB2    | DB1    | DB0   |

|      | 0    | 0    | 0    | 0    | 1      | 0    | 0    | 0    | 0    | 0    | DCE            | 0    | 0    | 1    | 0    | LOS          | 0    | 0    | 1    | 0    | PLB        | 0        | PLI      | 0   | 0    | 0    | 0   | C4(0) | C3(1)  | C2(1)  | C1(0) |

|      |      |      |      |       |      |      |      |      |                       |      |      |      |      | RE   | GIST | ER 7 |      |        |      |      |      |     |     |     |     |     |     |       |       |         |       |

|------|------|------|------|-------|------|------|------|------|-----------------------|------|------|------|------|------|------|------|------|--------|------|------|------|-----|-----|-----|-----|-----|-----|-------|-------|---------|-------|

|      |      |      |      | RESEF | RVED |      |      |      | DGA CONTROL<br>SELECT |      |      |      |      |      |      |      | RE   | ESERVE | ED   |      |      |     |     |     |     |     |     | c     | CONTR | OL BITS | s     |

| DB31 | DB30 | DB29 | DB28 | DB27  | DB26 | DB25 | DB24 | DB23 | DB22                  | DB21 | DB20 | DB19 | DB18 | DB17 | DB16 | DB15 | DB14 | DB13   | DB12 | DB11 | DB10 | DB9 | DB8 | DB7 | DB6 | DB5 | DB4 | DB3   | DB2   | DB1     | DB0   |

| O    | 0    | 0    | 0    | 0     | 0    | 0    | 0    | 0    | DCS                   | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 1    | 1      | 1    | 0    | 0    | 0   | 0   | 0   | 0   | 0   | 0   | C4(0) | C3(1) | C2(1)   | C1(1) |

|        |      |      |      |      |      |      |      |      |      |      |      |      |       |      | .01311 |      |      |      |      |      |      |     |     |     |     |     |     |       |       |       |       |

|--------|------|------|------|------|------|------|------|------|------|------|------|------|-------|------|--------|------|------|------|------|------|------|-----|-----|-----|-----|-----|-----|-------|-------|-------|-------|

| $\int$ |      |      |      |      |      |      |      |      |      |      |      |      |       |      |        |      |      |      |      |      |      |     |     |     |     |     |     |       |       |       |       |

|        |      |      |      | _    | _    |      |      |      |      |      |      | R    | ESERV | 'ED  |        |      |      |      |      |      |      |     |     |     |     |     |     |       | CON   | TS    |       |

| DB31   | DB30 | DB29 | DB28 | DB27 | DB26 | DB25 | DB24 | DB23 | DB22 | DB21 | DB20 | DB19 | DB18  | DB17 | DB16   | DB15 | DB14 | DB13 | DB12 | DB11 | DB10 | DB9 | DB8 | DB7 | DB6 | DB5 | DB4 | DB3   | DB2   | DB1   | DB0   |

| 0      | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0     | 0    | 0      | 0    | 0    | 0    | 0    | 0    | 0    | 0   | 0   | 0   | 0   | 0   | 0   | C4(1) | C3(0) | C2(0) | C1(0) |

|                  |      |      |      |      |      |      |      |      |      |      |      |      |       | RE   | GIST | ER 9 |      |      |      |      |      |     |     |     |     |     |     |       |       |       |       |

|------------------|------|------|------|------|------|------|------|------|------|------|------|------|-------|------|------|------|------|------|------|------|------|-----|-----|-----|-----|-----|-----|-------|-------|-------|-------|

|                  |      |      |      |      |      |      |      |      |      |      |      |      |       |      |      |      |      |      |      |      |      |     |     |     |     |     |     |       |       |       |       |

|                  |      |      |      |      |      |      |      |      |      |      |      |      |       |      |      |      |      |      |      |      |      |     |     |     |     |     |     |       |       |       |       |

|                  |      |      |      |      |      |      |      |      |      |      |      |      |       |      |      |      |      |      |      |      |      |     |     |     |     |     |     |       |       |       |       |

|                  |      |      |      |      |      |      |      |      |      |      |      |      |       |      |      |      |      |      |      |      |      |     |     |     |     |     |     |       | CONT  |       |       |

|                  |      |      |      |      |      |      |      |      | -    |      | -    | R    | ESER\ | /ED  |      |      |      |      |      |      |      |     |     |     |     |     |     |       | BI    | ITS   |       |

| DB3 <sup>-</sup> | DB30 | DB29 | DB28 | DB27 | DB26 | DB25 | DB24 | DB23 | DB22 | DB21 | DB20 | DB19 | DB18  | DB17 | DB16 | DB15 | DB14 | DB13 | DB12 | DB11 | DB10 | DB9 | DB8 | DB7 | DB6 | DB5 | DB4 | DB3   | DB2   | DB1   | DB0   |

|                  |      |      |      |      |      |      |      |      |      |      |      |      |       |      |      |      |      |      |      |      |      |     |     |     |     |     |     |       |       |       |       |

| $\checkmark$     | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0     | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0   | 0   | 0   | 0   | 0   | 0   | C4(1) | C3(0) | C2(0) | C1(1) |

|        |      |      |      |      |      |      |      |      |      |      |      |      |       | RE   | GISTE | R 10 |      |      |      |      |      |     |     |     |     |     |     |       |       |          |       |

|--------|------|------|------|------|------|------|------|------|------|------|------|------|-------|------|-------|------|------|------|------|------|------|-----|-----|-----|-----|-----|-----|-------|-------|----------|-------|

|        |      |      |      |      |      |      |      |      |      |      |      |      |       |      |       |      |      |      |      |      |      |     |     |     |     |     |     |       |       |          |       |

|        |      |      |      |      |      |      |      |      |      |      |      |      |       |      |       |      |      |      |      |      |      |     |     |     |     |     |     |       |       |          |       |

|        |      |      |      |      |      |      |      |      |      |      |      |      |       |      |       |      |      |      |      |      |      |     |     |     |     |     |     |       |       |          |       |

|        |      |      |      |      |      |      |      |      |      |      |      |      |       |      |       |      |      |      |      |      |      |     |     |     |     |     |     |       |       |          |       |

|        |      |      |      |      |      |      |      |      |      |      |      |      | ESERV |      |       |      |      |      |      |      |      |     |     |     |     |     |     |       | CONT  | TROL     |       |

|        |      |      |      |      |      |      |      |      |      |      |      | к    | ESERV | ED   |       | -    |      |      |      |      |      |     |     |     | _   |     | _   |       |       | 13       |       |

| DB31   | DB30 | DB29 | DB28 | DB27 | DB26 | DB25 | DB24 | DB23 | DB22 | DB21 | DB20 | DB19 | DB18  | DB17 | DB16  | DB15 | DB14 | DB13 | DB12 | DB11 | DB10 | DB9 | DB8 | DB7 | DB6 | DB5 | DB4 | DB3   | DB2   | DB1      | DB0   |

|        |      | -    |      |      |      |      |      |      |      |      |      |      |       |      |       |      |      |      |      |      |      |     |     |     |     |     |     |       |       | <u> </u> |       |

| 0      | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0     | 0    | 0     | 0    | 0    | 0    | 0    | 0    | 0    | 0   | 0   | 0   | 0   | 0   | 0   | C4(1) | C3(0) | C2(1)    | C1(0) |

| $\sim$ |      |      |      |      |      |      |      |      |      |      |      |      |       |      |       |      |      |      |      |      |      |     |     |     |     |     |     |       |       |          |       |

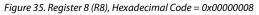

Figure 25. Register Summary (Register 6 Through Register 10)

**Data Sheet**

12223-042

## REGISTER 8

#### REGISTER 10

**Data Sheet**

ſ

(

**REGISTER 11**

|      |      |      |      |      |      |      |      |      |      |      |      | R    | ESERV | 'ED  |      |      |      |      |      |      |      |     |     |     |     |     |     |       | CONT  | TROL<br>TS |       |

|------|------|------|------|------|------|------|------|------|------|------|------|------|-------|------|------|------|------|------|------|------|------|-----|-----|-----|-----|-----|-----|-------|-------|------------|-------|

| DB31 | DB30 | DB29 | DB28 | DB27 | DB26 | DB25 | DB24 | DB23 | DB22 | DB21 | DB20 | DB19 | DB18  | DB17 | DB16 | DB15 | DB14 | DB13 | DB12 | DB11 | DB10 | DB9 | DB8 | DB7 | DB6 | DB5 | DB4 | DB3   | DB2   | DB1        | DB0   |

| C    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0     | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0   | 0   | 0   | 0   | 0   | 0   | C4(1) | C3(0) | C2(1)      | C1(1) |

#### **REGISTER 12**

|      |      |      |      |      |      |      |      |      |      |      |      | R    | ESERV | 'ED  |      |      |      |      |      |      |      |     |     |     |     |     |     |       | CONT  | TROL  |       |

|------|------|------|------|------|------|------|------|------|------|------|------|------|-------|------|------|------|------|------|------|------|------|-----|-----|-----|-----|-----|-----|-------|-------|-------|-------|

| DB31 | DB30 | DB29 | DB28 | DB27 | DB26 | DB25 | DB24 | DB23 | DB22 | DB21 | DB20 | DB19 | DB18  | DB17 | DB16 | DB15 | DB14 | DB13 | DB12 | DB11 | DB10 | DB9 | DB8 | DB7 | DB6 | DB5 | DB4 | DB3   | DB2   | DB1   | DB0   |

| C    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0     | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0   | 0   | 0   | 0   | 0   | 0   | C4(1) | C3(1) | C2(0) | C1(0) |

|      |      |       |      |      |      |                 |      |                          |      |      |      |                    |      | RE   | GISTE | R 13                    |      |      |      |                           |      |     |        |     |          |                   |                   |       |       |         |       |

|------|------|-------|------|------|------|-----------------|------|--------------------------|------|------|------|--------------------|------|------|-------|-------------------------|------|------|------|---------------------------|------|-----|--------|-----|----------|-------------------|-------------------|-------|-------|---------|-------|

|      | RESI | ERVED |      |      | L 1  | (ER<br>O<br>IAS |      | MIXER<br>V TO I<br>IBIAS |      |      |      | (ER<br>TO I<br>DAC |      |      |       | MIXER<br>V TO I<br>CDAC |      |      |      | F BALU<br>INPUT<br>CUT OF |      | 0   | F BALL | т   | RESERVED | MIXER A<br>ENABLE | MIXER B<br>ENABLE | c     | ONTR  | OL BIT: | 5     |

| DB31 | DB30 | DB29  | DB28 | DB27 | DB26 | DB25            | DB24 | DB23                     | DB22 | DB21 | DB20 | DB19               | DB18 | DB17 | DB16  | DB15                    | DB14 | DB13 | DB12 | DB11                      | DB10 | DB9 | DB8    | DB7 | DB6      | DB5               | DB4               | DB3   | DB2   | DB1     | DB0   |

| 0    | 0    | 0     | 0    | 0    | MB5  | MB4             | MB3  | MB2                      | MB1  | MR4  | MR3  | MR2                | MR1  | MC5  | MC4   | мсз                     | MC2  | MC1  | IC3  | IC2                       | IC1  | OC3 | OC2    | OC1 | 0        | MAE               | MBE               | C4(1) | C3(1) | C2(0)   | C1(1) |

|      |      |      |      |      |      |      |      |      |      |      |      |      |      | RE   | GISTE | R 14     |      |      |      |      |      |           |     |     |     |                 |                 |       |       |         |       |

|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|-------|----------|------|------|------|------|------|-----------|-----|-----|-----|-----------------|-----------------|-------|-------|---------|-------|

|      |      |      |      |      |      | RESE | RVED |      |      |      |      |      |      |      |       | DG<br>GA |      |      |      |      |      | DG/<br>GA |     |     | _   | DGA A<br>ENABLE | DGA B<br>ENABLE | c     | CONTR | OL BIT: | 5     |

| DB31 | DB30 | DB29 | DB28 | DB27 | DB26 | DB25 | DB24 | DB23 | DB22 | DB21 | DB20 | DB19 | DB18 | DB17 | DB16  | DB15     | DB14 | DB13 | DB12 | DB11 | DB10 | DB9       | DB8 | DB7 | DB6 | DB5             | DB4             | DB3   | DB2   | DB1     | DB0   |

| ( 1  | 0    | 0    | 1    | 0    | 0    | 1    | 0    | 0    | 0    | 1    | 0    | 0    | 0    | AG6  | AG5   | AG4      | AG3  | AG2  | AG1  | BG6  | BG5  | BG4       | BG3 | BG2 | BG1 | DAE             | DBE             | C4(1) | C3(1) | C2(1)   | C1(0) |

|      |      |      |      |      |      |      |        |      |      |      |      |      |      | RE   | GISTE                 | R 15     |               |      |      |      |      |       |      |     |     |     |     |       |       |        |       |

|------|------|------|------|------|------|------|--------|------|------|------|------|------|------|------|-----------------------|----------|---------------|------|------|------|------|-------|------|-----|-----|-----|-----|-------|-------|--------|-------|

|      |      |      |      |      |      | RI   | ESERVI | ED   |      |      |      |      |      |      | DGA LOW<br>POWER MODE | RESERVED | MIXER STANBDY |      |      |      |      | RESEF | RVED |     |     |     |     | C     | CONTR | OL BIT | s     |

| DB31 | DB30 | DB29 | DB28 | DB27 | DB26 | DB25 | DB24   | DB23 | DB22 | DB21 | DB20 | DB19 | DB18 | DB17 | DB16                  | DB15     | DB14          | DB13 | DB12 | DB11 | DB10 | DB9   | DB8  | DB7 | DB6 | DB5 | DB4 | DB3   | DB2   | DB1    | DB0   |

| C    | 1    | 0    | 0    | 0    | 1    | 0    | 0      | 0    | 0    | 0    | 0    | 0    | 0    | 0    | DLP                   | 0        | MSB           | 0    | 0    | 0    | 0    | 0     | 0    | 0   | 0   | 0   | 1   | C4(1) | C3(1) | C2(1)  | C1(1) |

Figure 26. Register Summary (Register 11 Through Register 15)

# **ADRF6658**

# 12223-043

#### **REGISTER 0 THROUGH REGISTER 4**

Program Register 0 through Register 4 with the assigned values as shown in the register maps, Figure 27 through Figure 31.

Figure 27. Register 0 (R0), Hexadecimal Code = 0x00000010