# Please note that Cypress is an Infineon Technologies Company.

The document following this cover page is marked as "Cypress" document as this is the company that originally developed the product. Please note that Infineon will continue to offer the product to new and existing customers as part of the Infineon product portfolio.

# **Continuity of document content**

The fact that Infineon offers the following product as part of the Infineon product portfolio does not lead to any changes to this document. Future revisions will occur when appropriate, and any changes will be set out on the document history page.

# **Continuity of ordering part numbers**

Infineon continues to support existing part numbers. Please continue to use the ordering part numbers listed in the datasheet for ordering.

www.infineon.com

# HX3PD USB 3.1 Gen 2 Type-C Hub with PD

## **Functional Description**

HX3PD is a family of USB 3.1 Gen 2 Type-C hub with USB Power Delivery (PD) that complies with the USB 3.1 Gen 2 (10 Gbps) specification, and the latest Type-C and PD standards. HX3PD supports SuperSpeed USB (10 Gbps), SuperSpeed (5 Gbps), High-Speed (HS), Full-Speed (FS), and Low-Speed (LS) on selective ports. HX3PD provides a complete Type-C and USB PD port controller solution in Upstream (US) and one Downstream (DS) port.

#### **Features**

- USB-IF Certified USB 3.1 Gen 2 Hub Silicon, TID#5030000008

- USB 3.1 Gen 2-compliant Hub Controller with 7 downstream ports

- □ Five downstream ports support SS (10 Gbps), SS (5 Gbps), and are backward-compatible with HS (480 Mbps), FS (12 Mbps), and LS (1.5 Mbps)

- Two downstream ports support HS, and are backward-compatible with FS, and LS

- □ SS (10 Gbps), SS (5 Gbps) and USB 2.0 Link Power Management (LPM)

- □ Dedicated Hi-Speed Transaction Translators (Multi-TT)

- Integrated Type-C transceivers, supporting Type-C plug orientation

- ☐ Type-C supported in four ports (1 US port and 3 DS ports)

- □ Integrated transceiver (baseband PHY)

- □ Integrated UFP (R<sub>D</sub>), and current sources for DFP (R<sub>P</sub>)

- Integrated PD controllers, supporting PD 3.0 specification in US port and 1 DS port

- Upstream: Configurable as either Type-C or Type-B port

- Downstream: Configurable as either three Type-C and four Type-A ports, or seven Type-A ports

- Compound USB PD hub with integrated USB device controller support:

- USB Billboard

- □ In-system firmware upgrade

- □ Vendor specific messaging

- Integrated Dock Management Controller support

- □ Signed and unsigned firmware updates

- ☐ Firmware upgrade over USB

- □ Dynamic configurations of port enable and disable from Embedded Controllers over I2C

- Charging Standard support:

- □ USB PD 3.0, Battery Charging v1.2 and Apple Charging Standards

- PD policy engine configures power profiles dynamically

- Ghost Charge™: Charging DS port without US connection

- 192-ball BGA (12 mm × 12 mm, 0.8-mm ball-pitch)

## **Block Diagram**

Cypress Semiconductor Corporation

Document Number: 002-16615 Rev. \*I

198 Champion Court

San Jose, CA 95134-1709

408-943-2600

Revised March 19, 2021

## **Contents**

| Architecture Overview                    | 3  |

|------------------------------------------|----|

| SS (10 Gbps) Hub Controller              | 3  |

| USB 2.0 Hub Controller                   | 3  |

| USB-PD Controller                        | 3  |

| SPI, I2C, and GPIO Interfaces            | 3  |

| Dock Management Controller               | 3  |

| Crypto Block                             | 4  |

| Application Diagrams                     | 4  |

| Docking Stations                         | 4  |

| HX3PD Product Options                    | 6  |

| Pinouts                                  | 6  |

| Pin Description                          | 7  |

| System Interfaces                        | 12 |

| Upstream Port (US)                       | 12 |

| Downstream Ports (DS1, 2, 3, 4, 5, 6, 7) | 12 |

| Communication Interfaces                 |    |

| Configuration Options                    | 13 |

| Absolute Maximum Ratings                 |    |

| Flectrical Specifications                |    |

| DC Electrical Characteristics           | 15 |

|-----------------------------------------|----|

| Power Consumption                       | 16 |

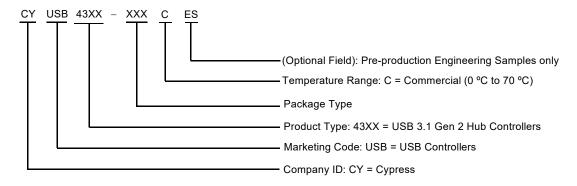

| Ordering Information                    | 17 |

| Ordering Code Definitions               | 17 |

| Package Diagram                         | 18 |

| Silicon Revision History                |    |

| Method of Identification                | 19 |

| Acronyms                                |    |

| Reference Documents                     |    |

| Document Conventions                    | 20 |

| Units of Measure                        | 20 |

| Errata                                  |    |

| Document History Page                   |    |

| Sales, Solutions, and Legal Information |    |

| Worldwide Sales and Design Support      |    |

| Products                                |    |

| PSoC® Solutions                         | 25 |

| Cypress Developer Community             |    |

| Tachnical Cupport                       |    |

#### Architecture Overview

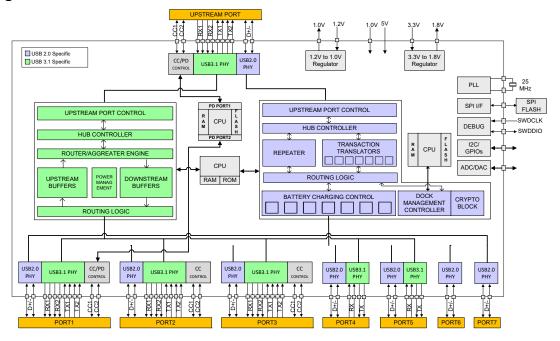

The Block Diagram on page 1 shows the HX3PD architecture. HX3PD consists of two independent hub controllers (SS (10 Gbps) and USB 2.0), the Arm<sup>®</sup> Cortex<sup>®</sup>-M0 CPU subsystem, 2-port USB-PD controllers, Dock Management Controller (DMC), SPI interface, Serial communication block, and GPIOs.

#### SS (10 Gbps) Hub Controller

This block supports the SS (10 Gbps) hub functionality based on the USB 3.1 Gen 2 (10 Gbps) specification. The SS (10 Gbps) hub controller supports the following:

- USB precision time management (PTM)

- Link power management (U0, U1, U2, U3 states)

- Store and forward packet architecture

- Full-duplex data transmission

#### **USB 2.0 Hub Controller**

This block supports the LS, FS, and HS hub functionalities. It includes the repeater, frame timer, and seven transaction translators. The USB 2.0 hub controller block supports the following:

- USB 2.0 link power management (L0, L1, L2, L3 states)

- Suspend, resume, and remote wake-up signaling

- Multi-TT (one TT for each DS port)

The hub is also integrated with USB device, which can function as a DMC and USB Billboard.

#### **USB-PD Controller**

HX3PD supports two USB PD ports, consisting of USB Type-C baseband transceivers and physical-layer logic. The USB-PD PHY consists of a transmitter and receiver that communicate Biphase Mark Coding (BMC) and 4b/5b encoded data over the CC channel based on the PD 3.0 standard. In addition, the USB-PD block includes all termination resistors ( $R_P$  and  $R_D$ ) as required by the USB Type-C spec.  $R_P$  and  $R_D$  resistors are required to implement connection detection, plug orientation detection, and for establishing the USB source/sink roles.

The integrated  $R_P$  resistor enables the PD port to be configured as a DFP. The  $R_P$  resistor is implemented as a current source and can be programmed to support the complete range of current capacity on the VBUS defined in the USB Type-C Spec.

The  $R_D$  resistor is used to identify the HX3PD port as a UFP in a DRP application. The  $R_D$  resistor on the CC pins is required even when the part is not powered for dead battery termination detection and charging. HX3PD's PD ports respond to all USB-PD communication.

HX3PD is designed to be fully interoperable with revision 3.0 as well as revision 2.0 of the USB PD specification. HX3PD supports Extended Messages containing data up to 260 bytes. The Extended Messages will be larger than expected by the USB-PD 2.0 hardware. To accommodate Revision 2.0 based systems, a Chunking mechanism is implemented such that Messages are limited to Revision 2.0 sizes unless it is discovered that both systems support the longer Message lengths.

The CPU in HX3PD's USB-PD controller is a Cortex-M0 32-bit MCU controller, which is optimized for low-power operation with extensive clock gating. It includes a nested vectored interrupt controller (NVIC) block with 32 interrupt inputs and also includes a Wakeup Interrupt Controller (WIC). The WIC can wake the processor up from the Deep Sleep mode, allowing power to be switched off to the main processor when the chip is in the Deep Sleep mode. The Cortex-M0 CPU provides a Non-Maskable Interrupt (NMI) input, which is made available to the user when it is not in use for system functions requested by the user. The CPU also includes a serial wire debug (SWD) interface, which is a two-wire form of JTAG.

#### SPI, I<sup>2</sup>C, and GPIO Interfaces

HX3PD has dedicated SPI flash interfaces, used for downloading configuration/firmware of the hub during boot-up.

HX3PD has dedicated I<sup>2</sup>C interfaces for Hub, DMC, and PD controllers. These I<sup>2</sup>C interfaces shall be used for configurations of individual blocks, communication between individual blocks, and/or interface with external controllers.

HX3PD contains many GPIOs which can be configured as input, output to support custom features, these I/Os can be used for serial communication with external master/slave devices. The serial communication protocols supported are I2C, SPI, and UART.

#### **Dock Management Controller**

Dock Management Controller (DMC) integrates a Full-Speed USB controller that is designed for managing the USB dock system. DMC supports USB Billboard as well as firmware download over USB to externally interfaced peripherals (over I2C/SPI).

#### Firmware Update Support

DMC has the capability to do firmware update to Hub controller, PD controller, DMC, and other dock components. It implements the firmware update functionality and status reporting on a vendor interface using a full-speed USB 2.0 device controller.

#### Unsigned Firmware Update

The firmware update procedure expects the host to send the metadata of the programmable component's FW information.

This metadata includes SHA-256 of the individual firmware image. DMC notifies the host to send the individual component's firmware image one by one and update to the dock components. DMC verifies the firmware validity by comparing the received SHA-256 with the calculated SHA-256 of the firmware received.

#### Signed Firmware Update

The signed firmware update follows the same procedure as the unsigned firmware update but is uses RSA-2018/SHA-256 for signing.

Contact Cypress customer support for more information on the signed firmware update.

#### Crypto Block

HX3PD integrates a Crypto block for hardware assisted authentication of firmware images. It supports field upgradeability of firmware in a trusted ecosystem. The Crypto block provides cryptography functionality. It includes hardware acceleration blocks for Advanced Encryption Standard (AES) block cipher, Secure Hash Algorithm (SHA), Cyclic Redundancy Check (CRC), and pseudo random number generation.

#### **Application Diagrams**

#### **Docking Stations**

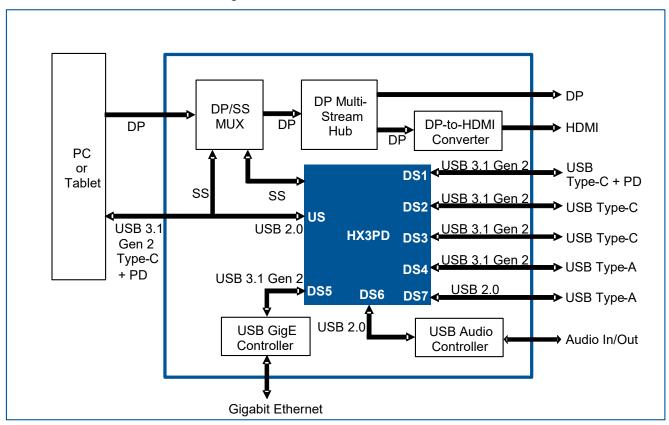

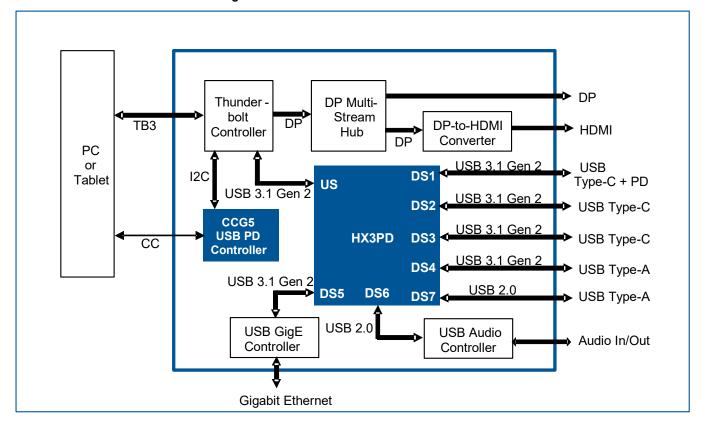

Figure 1 and Figure 2 show USB-C Dock design application diagrams using HX3PD.

HX3PD integrates five chips (two 4-port USB Hubs, two USB-PD controllers, and Dock Management controller) in typical dock designs to a single chip; significantly reducing BOM and design complexity. HX3PD Dock solution provides seven downstream ports (five USB 3.1 Gen 2, and two USB 2.0) and supports PD 3.0, BC 1.2, and Apple charging standards. It also supports signed firmware upgrades via DMC, thereby enable to keep pace with future specification changes.

Figure 1. USB-C Dock for Notebook PCs

Figure 2. Thunderbolt Dock for Notebook PCs

# **HX3PD Product Options**

Table 1. HX3PD Product Options

| Marketing<br>Part Number | Application                 | No of DS<br>Ports | US PD<br>Port | DS PD<br>Port | Legacy Charging on DS | USB<br>Billboard | Signed FW<br>Download | Package      |

|--------------------------|-----------------------------|-------------------|---------------|---------------|-----------------------|------------------|-----------------------|--------------|

| CYUSB4347                | Docking Station,<br>Monitor | 7                 | DRP           | DFP           | Yes                   | Yes              | No                    | 192-Ball BGA |

| CYUSB4357                | Docking Station,<br>Monitor | 7                 | DRP           | DFP           | Yes                   | Yes              | Yes                   | 192-Ball BGA |

## **Pinouts**

Figure 3. 192-Ball BGA Pin Diagram

|   | 1       | 2       | 3            | 4                          | 5                           | 6                        | 7               | 8                           | 9            | 10               | 11           | 12               | 13      | 14      |

|---|---------|---------|--------------|----------------------------|-----------------------------|--------------------------|-----------------|-----------------------------|--------------|------------------|--------------|------------------|---------|---------|

| A | ı       | DM_P7   | DP_P7        | VBUS -<br>DISCHĀR<br>GE_P1 | VDDD_P<br>D                 | XIN                      | XOUT            | HPD_P1                      | I2C_SCL2     | SPI_MIS<br>O_DMC | DMC_P24      | DM_P6            | DP_P6   | -       |

| В | DM_P1   | DP_P1   | CC2_P0       | SWDCLK<br>_PD              | VBUS_M<br>ON_P1             | VCCD_P<br>D              | VSEL_<br>GPIO3  | VSEL_GPI<br>O4              | I2C_SDA2     | SPI_SS_<br>DMC   | DMC_P25      | DMC_P2           | DM_P2   | DP_P2   |

| С | TXP1_P1 | TXN1_P1 | VDDIO        | V5P0_P0                    | VBUS_C_<br>CTRL_P1          | OCP_DE<br>T_P1           | CC2_P1          | VCONN_M<br>ON_P1/PD<br>_P27 | VDDD_DM<br>C | SWDIO_<br>DMC    | XRES_D<br>MC | VDDIO            | TXP2_P2 | TXN2_P2 |

| D | RXP1_P1 | RXN1_P1 | CC1_P0       | VBUS_M<br>ON_P0            | VSEL_GP<br>IO1              | VBUS_P_<br>CTRL_P1       | V5P0_P<br>1     | CC1_P1                      | VCCD_DM<br>C | SWDCLK<br>_DMC   | I2C_SDA<br>1 | SPI_CLK<br>_DMC  | RXP2_P2 | RXN2_P2 |

| E | RXN2_P1 | RXP2_P1 | PD_P15       | VBUS_P_<br>CTRL_P0         | HPD_P0                      | VBUS<br>DISCHAR<br>GE_P0 | V5P0            | AVDD33                      | PWREN_P<br>2 | PGANG            | I2C_SCL1     | DMC_P3           | RXN1_P2 | RXP1_P2 |

| F | TXN2_P1 | TXP2_P1 | SWDIO_P<br>D | DVDD10                     | VSEL_GP<br>IO2              | GND                      | GND             | GND                         | GND          | OVCUR_<br>P2     | DVDD10       | SPI_MO<br>SI_DMC | TXN1_P2 | TXP1_P2 |

| G | TXP_P5  | TXN_P5  | V3P3         | V1P0_P7                    | OCP_DE<br>T_P0              | GND                      | GND             | GND                         | GND          | I2C_S-<br>DA_HUB | V1P0_P6      | V3P3             | RXN_P4  | RXP_P4  |

| н | RXP_P5  | RXN_P5  | V1P0_P1      | VBUS_C_<br>CTRL_P0         | SPI_MOS<br>I_HUB            | GND                      | GND             | GND                         | GND          | OVCUR_<br>P6     | V1P0_P2      | V1P0_P2          | TXN_P4  | TXP_P4  |

| J | DP_P5   | DM_P5   | V1P0_P1      | DVDD10                     | SPI_MIS<br>O_HUB            | PWREN_<br>P1             | GND             | GND                         | GND          | PWREN_<br>P6     | DVDD10       | VDDIO            | DM_P4   | DP_P4   |

| ĸ | DM_P0   | DP_P0   | V1P0_P5      | XRES_P<br>D                | VCONN_<br>MON_P0/<br>PD_P24 | OVCUR_<br>P1             | SPI_CL<br>K_HUB | AVDD10                      | CC1_P2       | CC2_P2           | PSELF        | V1P0_P4          | DM_P3   | DP_P3   |

| L | TXP1_P0 | TXN1_P0 | V3P3         | V1P0_P0                    | OVCUR_<br>P5                | PWREN_<br>P5             | OVCUR<br>_P4    | CC1_P3                      | CC2_P3       | VDDIO            | V1P0_P3      | V3P3             | TXP2_P3 | TXN2_P3 |

| М | RXP1_P0 | RXN1_P0 | V3P3         | V1P0_P0                    | I2C_S-<br>CL_HUB            | SPI_SS_<br>HUB           | VBUS            | RESET_H<br>UB               | CHIPEN       | RTERM            | OVCUR_<br>P7 | V1P0_P3          | RXP2_P3 | RXN2_P3 |

| N | RXN2_P0 | RXP2_P0 | PWREN_<br>P4 | V1P0_ME<br>M_B             | V1P0_ME<br>M_A              | V1P2                     | GPIO4_<br>HUB   | V1P0_PHY                    | V1P0_PHY     | FB               | PWREN_<br>P3 | OVCUR_<br>P3     | RXP1_P3 | RXN1_P3 |

| P | -       | TXN2_P0 | TXP2_P0      | V1P2                       | V1P2                        | V1P2                     | GPIO3_<br>HUB   | V1P0_PHY                    | V1P0_PHY     | V3P3_RE<br>G     | PWREN_<br>P7 | TXP1_P           | TXN1_P3 | -       |

Refer to the Application Note "AN222944 - HX3PD Hardware Design Guidelines and Checklist" for recommendation on individual pin schematics.

# **Pin Description**

| No.        | Pin Name            | Туре | Pin Number | Description                                        |

|------------|---------------------|------|------------|----------------------------------------------------|

| Upstream l | Port USB Signals    |      |            |                                                    |

| 1          | DP_P0               | I/O  | K2         | Upstream port USB 2.0 data plus                    |

| 2          | DM_P0               | I/O  | K1         | Upstream port USB 2.0 data minus                   |

| 3          | TXP1_P0             | 0    | L1         | Upstream port, SuperSpeed transmit plus lane 1     |

| 4          | TXN1_P0             | 0    | L2         | Upstream port, SuperSpeed transmit minus lane 1    |

| 5          | RXP1_P0             | I    | M1         | Upstream port, SuperSpeed receive plus lane 1      |

| 6          | RXN1_P0             | I    | M2         | Upstream port, SuperSpeed receive minus lane 1     |

| 7          | TXP2_P0             | 0    | P3         | Upstream port, SuperSpeed transmit plus lane 2     |

| 8          | TXN2_P0             | 0    | P2         | Upstream port, SuperSpeed transmit minus lane 2    |

| 9          | RXP2_P0             | I    | N2         | Upstream port, SuperSpeed receive plus lane 2      |

| 10         | RXN2_P0             | I    | N1         | Upstream port, SuperSpeed receive minus lane 2     |

| Downstrea  | m Port1 USB Signals |      |            |                                                    |

| 11         | DP_P1               | I/O  | B2         | Downstream port1, USB 2.0 data plus                |

| 12         | DM_P1               | I/O  | B1         | Downstream port1, USB 2.0 data minus               |

| 13         | TXP1_P1             | 0    | C1         | Downstream port1, SuperSpeed transmit plus lane 1  |

| 14         | TXN1_P1             | 0    | C2         | Downstream port1, SuperSpeed transmit minus lane 1 |

| 15         | RXP1_P1             | I    | D1         | Downstream port1, SuperSpeed receive plus lane 1   |

| 16         | RXN1_P1             | I    | D2         | Downstream port1, SuperSpeed receive minus lane 1  |

| 17         | TXP2_P1             | 0    | F2         | Downstream port1, SuperSpeed transmit plus lane 2  |

| 18         | TXN2_P1             | 0    | F1         | Downstream port1, SuperSpeed transmit minus lane 2 |

| 19         | RXP2_P1             | I    | E2         | Downstream port1, SuperSpeed receive plus lane 2   |

| 20         | RXN2_P1             | I    | E1         | Downstream port1, SuperSpeed receive minus lane 2  |

| Downstrea  | m Port2 USB Signals |      |            |                                                    |

| 21         | DP_P2               | I/O  | B14        | Downstream port2, USB 2.0 data plus                |

| 22         | DM_P2               | I/O  | B13        | Downstream port2, USB 2.0 data minus               |

| 23         | TXP1_P2             | 0    | F14        | Downstream port2, SuperSpeed transmit plus lane 1  |

| 24         | TXN1_P2             | 0    | F13        | Downstream port2, SuperSpeed transmit minus lane 1 |

| 25         | RXP1_P2             | I    | E14        | Downstream port2, SuperSpeed receive plus lane 1   |

| 26         | RXN1_P2             | I    | E13        | Downstream port2, SuperSpeed receive minus lane 1  |

| 27         | TXP2_P2             | 0    | C13        | Downstream port2, SuperSpeed transmit plus lane 2  |

| 28         | TXN2_P2             | 0    | C14        | Downstream port2, SuperSpeed transmit minus lane 2 |

| 29         | RXP2_P2             | I    | D13        | Downstream port2, SuperSpeed receive plus lane 2   |

| 30         | RXN2_P2             | I    | D14        | Downstream port2, SuperSpeed receive minus lane 2  |

| Downstrea  | m Port3 USB Signals |      |            |                                                    |

| 31         | DP_P3               | I/O  | K14        | Downstream port3, USB 2.0 data plus                |

| 32         | DM_P3               | I/O  | K13        | Downstream port3, USB 2.0 data minus               |

| 33         | TXP1 P3             | 0    | P12        | Downstream port3, SuperSpeed transmit plus lane 1  |

| No.       | Pin Name             | Type | Pin Number | Description                                        |

|-----------|----------------------|------|------------|----------------------------------------------------|

| 34        | TXN1_P3              | 0    | P13        | Downstream port3, SuperSpeed transmit minus lane 1 |

| 35        | RXP1_P3              | I    | N13        | Downstream port3, SuperSpeed receive plus lane 1   |

| 36        | RXN1_P3              | I    | N14        | Downstream port3, SuperSpeed receive minus lane 1  |

| 37        | TXP2_P3              | 0    | L13        | Downstream port3, SuperSpeed transmit plus lane 2  |

| 38        | TXN2_P3              | 0    | L14        | Downstream port3, SuperSpeed transmit minus lane 2 |

| 39        | RXP2_P3              | I    | M13        | Downstream port3, SuperSpeed receive plus lane 2   |

| 40        | RXN2_P3              | I    | M14        | Downstream port3, SuperSpeed receive minus lane 2  |

| Downstrea | am Port4 USB Signals | 1    |            |                                                    |

| 41        | DP_P4                | I/O  | J14        | Downstream port4, USB 2.0 data plus                |

| 42        | DM_P4                | I/O  | J13        | Downstream port4, USB 2.0 data minus               |

| 43        | TXP_P4               | 0    | H14        | Downstream port4, SuperSpeed transmit plus         |

| 44        | TXN_P4               | 0    | H13        | Downstream port4, SuperSpeed transmit minus        |

| 45        | RXP_P4               | I    | G14        | Downstream port4, SuperSpeed receive plus          |

| 46        | RXN_P4               | I    | G13        | Downstream port4, SuperSpeed receive minus         |

| Downstrea | am Port5 USB Signals |      |            |                                                    |

| 47        | DP_P5                | I/O  | J1         | Downstream port5, USB 2.0 data plus                |

| 48        | DM_P5                | I/O  | J2         | Downstream port5, USB 2.0 data minus               |

| 49        | TXP_P5               | 0    | G1         | Downstream port5, SuperSpeed transmit plus         |

| 50        | TXN_P5               | 0    | G2         | Downstream port5, SuperSpeed transmit minus        |

| 51        | RXP_P5               | I    | H1         | Downstream port5, SuperSpeed receive plus          |

| 52        | RXN_P5               | I    | H2         | Downstream port5, SuperSpeed receive minus         |

| Downstrea | am Port6 USB Signals |      |            |                                                    |

| 53        | DP_P6                | I/O  | A13        | Downstream port6, USB 2.0 data plus                |

| 54        | DM_P6                | I/O  | A12        | Downstream port6, USB 2.0 data minus               |

| Downstrea | am Port7 USB Signals |      |            |                                                    |

| 55        | DP_P7                | I/O  | A3         | Downstream port7, USB 2.0 data plus                |

| 56        | DM_P7                | I/O  | A2         | Downstream port7, USB 2.0 data minus               |

| USB Port  | Control Signals      |      |            |                                                    |

| 57        | OVCUR_P1             | I    | K6         | Downstream port1, Active low Over current detect   |

| 58        | OVCUR_P2             | I    | F10        | Downstream port2, Active low Over current detect   |

| 59        | OVCUR_P3             | l    | N12        | Downstream port3, Active low Over current detect   |

| 60        | OVCUR_P4             | I    | L7         | Downstream port4, Active low Over current detect   |

| 61        | OVCUR_P5             | I    | L5         | Downstream port5, Active low Over current detect   |

| 62        | OVCUR_P6             | I    | H10        | Downstream port6, Active low Over current detect   |

| 63        | OVCUR_P7             | I    | M11        | Downstream port7, Active low Over current detect   |

| 64        | PWREN_P1             | 0    | J6         | Downstream port1, Active low Power enable          |

| 65        | PWREN_P2             | 0    | E9         | Downstream port2, Active low Power enable          |

| 66        | PWREN_P3             | 0    | N11        | Downstream port3, Active low Power enable          |

| 67        | PWREN_P4             | 0    | N3         | Downstream port4, Active low Power enable          |

| 68        | PWREN_P5             | 0    | L6         | Downstream port5, Active low Power enable          |

| No.       | Pin Name          | Туре | Pin Number | Description                                                                                                                    |

|-----------|-------------------|------|------------|--------------------------------------------------------------------------------------------------------------------------------|

| 69        | PWREN_P6          | 0    | J10        | Downstream port6, Active low Power enable                                                                                      |

| 70        | PWREN_P7          | 0    | P11        | Downstream port7, Active low Power enable                                                                                      |

| 71        | VBUS              | I    | M7         | Upstream VBUS input                                                                                                            |

| Upstream  | PD Control        |      |            |                                                                                                                                |

| 72        | VBUS_MON_P0       | Α    | D4         | GPIO used as VBUS monitor for Upstream PD port                                                                                 |

| 73        | VBUS_P_CTRL_P0    | I/O  | E4         | GPIO used for controlling provider power switch of<br>Upstream PD port                                                         |

| 74        | VBUS_C_CTRL_P0    | I/O  | H4         | GPIO used for controlling consumer power switch of Upstream PD port                                                            |

| 75        | VBUS_DISCHARGE_P0 | I/O  | E6         | GPIO for controlling VBUS discharge switch of<br>Upstream PD port                                                              |

| Downstre  | am PD Control     |      |            |                                                                                                                                |

| 76        | VBUS_MON_P1       | Α    | B5         | GPIO used as VBUS monitor for Downstream PD port                                                                               |

| 77        | VBUS_P_CTRL_P1    | I/O  | D6         | GPIO used for controlling provider power switch of Downstream PD port                                                          |

| 78        | VBUS_C_CTRL_P1    | I/O  | C5         | GPIO used for controlling consumer power switch of Downstream PD port                                                          |

| 79        | VBUS_DISCHARGE_P1 | I/O  | A4         | GPIO for controlling VBUS discharge switch of Downstream PD port                                                               |

| Type-C PE | Control Signals   |      |            |                                                                                                                                |

| 80        | CC1_P0            | Α    | D3         | Upstream port connect detect/Configuration Channel 1                                                                           |

| 81        | CC1_P1            | Α    | D8         | Downstream port1 connect detect/Configuration Channel 1                                                                        |

| 82        | CC1_P2            | Α    | K9         | Downstream port2 connect detect/Configuration Channel 1                                                                        |

| 83        | CC1_P3            | Α    | L8         | Downstream port3 connect detect/Configuration Channel 1                                                                        |

| 84        | CC2_P0            | Α    | В3         | Upstream port connect detect/Configuration Channel 2                                                                           |

| 85        | CC2_P1            | Α    | C7         | Downstream port1 connect detect/Configuration Channel 2                                                                        |

| 86        | CC2_P2            | Α    | K10        | Downstream port2 connect detect/Configuration Channel 2                                                                        |

| 87        | CC2_P3            | Α    | L9         | Downstream port3 connect detect/Configuration<br>Channel 2                                                                     |

| 88        | OCP_DET_P0        | 1    | G5         | Over current detection input for upstream Type-C port                                                                          |

| 89        | OCP_DET_P1        | I    | C6         | Over current detection input for downstream Type-C port 1                                                                      |

| 90        | VSEL_GPI01        | I/O  | D5         | GPIO for selecting VBUS voltage level of PD ports; When used for I2C interface, this pin must be used as I2C_MASTER_SDA.       |

| 91        | VSEL_GPIO2        | I/O  | F5         | GPIO for selecting VBUS voltage level of PD ports;<br>When used for I2C interface, this pin must be used as<br>I2C_MASTER_SCL. |

| 92        | VSEL_GPIO3        | I/O  | B7         | GPIO                                                                                                                           |

| 93        | VSEL_GPIO4        | I/O  | B8         | GPIO                                                                                                                           |

| No.       | Pin Name                   | Type | Pin Number | Description                                                                  |

|-----------|----------------------------|------|------------|------------------------------------------------------------------------------|

| SPI, I2C, | and GPIOs                  |      |            |                                                                              |

| 94        | SPI_CLK_HUB                | 0    | K7         | SPI clock. Connect to SPI EEPROM                                             |

| 95        | SPI_SS_HUB                 | 0    | M6         | SPI select. Connect to SPI EEPROM                                            |

| 96        | SPI_MISO_HUB               | I    | J5         | SPI data in. Connect to SPI EEPROM                                           |

| 97        | SPI_MOSI_HUB               | 0    | H5         | SPI data out. Connect to SPI EEPROM                                          |

| 98        | SPI_MISO_DMC               | I/O  | A10        | SPI data in. This SPI interface from DMC block                               |

| 99        | SPI_SS_DMC                 | I/O  | B10        | SPI slave select. This SPI interface from DMC block                          |

| 100       | SPI_MOSI_DMC               | I/O  | F12        | SPI data out. This SPI interface from DMC block                              |

| 101       | SPI_CLK_DMC                | I/O  | D12        | SPI clock. This SPI interface from DMC block                                 |

| 102       | I2C_SCL1                   | I/O  | E11        | I2C clock - 1; Connected to DMC (I2C master)                                 |

| 103       | I2C_SDA1                   | I/O  | D11        | I2C data - 1; Connected to DMC (I2C master)                                  |

| 104       | I2C_SCL2                   | I/O  | A9         | I2C clock - 2; Connected to DMC (I2C slave)                                  |

| 105       | I2C_SDA2                   | I/O  | В9         | I2C data - 2; Connected to DMC (I2C slave)                                   |

| 106       | I2C_SCL_HUB                | I/O  | M5         | I2C clock, Connected to Hub controller (I2C slave) block                     |

| 107       | I2C_SDA_HUB                | I/O  | G10        | I2C data, Connected to Hub controller (I2C slave) block                      |

| 108       | GPIO3_HUB                  | I/O  | P7         | GPIO from Hub                                                                |

| 109       | GPIO4_HUB                  | I/O  | N7         | GPIO from Hub                                                                |

| 110       | DMC_P24                    | I/O  | A11        | GPIO                                                                         |

| 111       | DMC_P25                    | I/O  | B11        | GPIO                                                                         |

| 112       | DMC_P26                    | I/O  | B12        | GPIO                                                                         |

| 113       | DMC_P32                    | I/O  | E12        | GPIO                                                                         |

| 114       | HPD_P0                     | I/O  | E5         | GPIO used as Hot plug detect input from DisplayPort (DP) of Upstream PD port |

| 115       | HPD_P1                     | I/O  | A8         | GPIO used as Hot plug detect output to DP of Downstream PD port              |

| 116       | PD_P15                     | I/O  | E3         | GPIO                                                                         |

| 117       | VCONN_MON_P0/PD_P2<br>4    | I/O  | K5         | GPIO                                                                         |

| 118       | VCONN_MON_P1/PD_P2<br>7    | I/O  | C8         | GPIO                                                                         |

| Clock, Re | eset, Debug, and Mode Sele | ct   |            |                                                                              |

| 119       | XIN                        | Α    | A6         | Crystal In                                                                   |

| 120       | XOUT                       | Α    | A7         | Crystal Out                                                                  |

| 121       | CHIPEN                     | I    | M9         | Chip enable, Recommend to connect it HIGH. Chip has a weak internal pull-up. |

| 122       | RESET_HUB                  | I    | M8         | Active Low reset input of hub controller                                     |

| 123       | XRES_DMC                   | I    | C11        | Active Low reset input of DMC                                                |

| 124       | XRES_PD                    | I    | K4         | Active Low reset input of PD controller                                      |

| 125       | SWDCLK_DMC                 | I/O  | D10        | SWD clock input for DMC                                                      |

| 126       | SWDIO_DMC                  | I/O  | C10        | SWD data I/O for DMC                                                         |

| 127       | SWDCLK_PD                  | I/O  | B4         | SWD clock input for PD controller                                            |

| No.       | Pin Name     | Туре | Pin Number                                                       | Description                                                                                              |

|-----------|--------------|------|------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|

| 128       | SWDIO_PD     | I/O  | F3                                                               | SWD data I/O for PD controller                                                                           |

| 129       | PSELF        | I    | K11                                                              | Self/Bus power mode: This pin must be pulled HIGH for SELF power mode and pulled LOW for BUS power mode. |

| 130       | PGANG        | I    | E10                                                              | Gang/Individual mode: This pin must be pulled HIGH for GANG mode and pulled LOW for INDIVIDUAL mode.     |

| 131       | RTERM        | А    | M10                                                              | Connect this pin to a precision resistor (20 kΩ ±1%)                                                     |

| Ground, P | ower, and NC |      |                                                                  |                                                                                                          |

| 132       | AVDD10       | PWR  | K8                                                               | 1.0-V Input (1.0-V power for Analog)                                                                     |

| 133       | AVDD33       | PWR  | E8                                                               | 3.3-V Input (3.3-V power for Analog)                                                                     |

| 134–137   | DVDD10       | PWR  | F4, F11, J4, J11                                                 | 1.0-V Input (1.0-V power for Digital)                                                                    |

| 138       | FB           | PWR  | N10                                                              | Reserved. Connect this pin to Ground.                                                                    |

| 139       | VCCD_DMC     | PWR  | D9                                                               | Regulator output of DMC                                                                                  |

| 140       | VCCD_PD      | PWR  | B6                                                               | Regulator output of PD controller                                                                        |

| 141–144   | VDDIO        | PWR  | C3, C12, L10, J12                                                | 3.3-V I/O supply                                                                                         |

| 145       | VDDD_DMC     | PWR  | C9                                                               | 3.3-V supply for DMC                                                                                     |

| 146       | VDDD_PD      | PWR  | A5                                                               | 3.3-V supply for PD controller                                                                           |

| 147       | V1P0_MEM_A   | PWR  | N5                                                               | 1.0-V supply for internal memory                                                                         |

| 148       | V1P0_MEM_B   | PWR  | N4                                                               | 1.0-V supply for internal memory                                                                         |

| 149–150   | V1P0_P0      | PWR  | L4, M4                                                           | 1.0-V supply for US port                                                                                 |

| 151–152   | V1P0_P1      | PWR  | J3, H3                                                           | 1.0-V supply for port 1                                                                                  |

| 153–154   | V1P0_P2      | PWR  | H12, H11                                                         | 1.0-V supply for port 2                                                                                  |

| 155–156   | V1P0_P3      | PWR  | M12, L11                                                         | 1.0-V supply for port 3                                                                                  |

| 157       | V1P0_P4      | PWR  | K12                                                              | 1.0-V supply for port 4                                                                                  |

| 158       | V1P0_P5      | PWR  | K3                                                               | 1.0-V supply for port 5                                                                                  |

| 159       | V1P0_P6      | PWR  | G11                                                              | 1.0-V supply for port 6                                                                                  |

| 160       | V1P0_P7      | PWR  | G4                                                               | 1.0-V supply for port 7                                                                                  |

| 161–164   | V1P0_PHY     | PWR  | P8, N8, P9, N9                                                   | 1.0-V supply for PHY                                                                                     |

| 165–168   | V1P2         | PWR  | P4, P5, P6, N6                                                   | 1.2-V input for internal LDO                                                                             |

| 169       | V3P3_REG     | PWR  | P10                                                              | 3.3-V input for internal LDO. Connect to VDDIO                                                           |

| 170–174   | V3P3         | PWR  | L3, G3, G12, L12, M3                                             | 3.3-V supply for USB 2.0                                                                                 |

| 175       | V5P0_P0      | PWR  | C4                                                               | 5-V VCONN input to Upstream PD port                                                                      |

| 176       | V5P0_P1      | PWR  | D7                                                               | 5-V VCONN input to Downstream PD port                                                                    |

| 177       | V5P0         | PWR  | E7                                                               | 5-V input supply to hub controller                                                                       |

| 178–192   | GND          | GND  | F6, F7, F8, F9, G6,<br>G7, G8, G9, H6, H7,<br>H8, H9, J7, J8, J9 | Ground                                                                                                   |

## System Interfaces

### **Upstream Port (US)**

The HX3PD USB port can function in Type-C or Legacy Type-B modes; it operates in the USB 3.1 Gen 2 (10 Gbps) specification. This port includes an integrated 1.5-k $\Omega$  pull-up resistor and termination resistors. The HX3PD US port has an integrated PD controller, which supports the PD 3.0 specification and can charge up to 5A at 20 V.

#### Downstream Ports (DS1, 2, 3, 4, 5, 6, 7)

The following table summarizes the operations of HX3PD DS ports.

Table 2. Operations of HX3PD DS Ports

| DS<br>Port | Connector | USB<br>Speed     | Charging Mode | Max Charging<br>Current |

|------------|-----------|------------------|---------------|-------------------------|

| DS1        | Type-C    | USB 3.1<br>Gen 2 | PD 3.0        | 5A at 20 V              |

| DS2        | Type-C    | USB 3.1<br>Gen 2 | BC 1.2, Apple | 3A at 5 V               |

| DS3        | Type-C    | USB 3.1<br>Gen 2 | BC 1.2, Apple | 3A at 5 V               |

| DS4        | Type-A    | USB 3.1<br>Gen 2 | BC 1.2, Apple | 2.4A at 5 V             |

| DS5        | Type-A    | USB 3.1<br>Gen 2 | BC 1.2, Apple | 2.4A at 5 V             |

| DS6        | Type-A    | USB 2.0          | BC 1.2, Apple | 2.4A at 5 V             |

| DS7        | Type-A    | USB 2.0          | BC 1.2, Apple | 2.4A at 5 V             |

Three HX3PD DS ports (DS1, DS2, and DS3) work in the Type-C mode. The other ports work in the Type-A mode. USB 3.1 Gen 2 (10 Gbps) is supported in ports DS1 to DS5 and USB 2.0 (480 Mbps) is supported in ports DS6 and DS7. All DS ports support, by default, the Battery Charging Specification 1.2. DS1 has an integrated PD controller which supports the PD 3.0 specification. Port enable/disable and charging modes shall be configured using configuration options.

#### **Communication Interfaces**

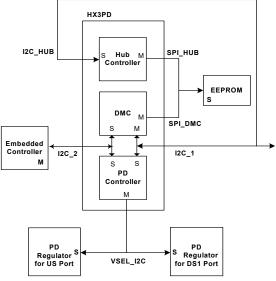

Figure 4. Communication Interfaces

Note

M = Master; S = Slave

HX3PD supports SPI and I<sup>2</sup>C interfaces for communications between individual blocks and with the Embedded Controller (EC).

HX3PD has two SPI and four I<sup>2</sup>C interfaces.

#### SPI\_HUB

This interface is connected to an SPI EEPROM. Hub controller uses this interface to read firmware and configurations from EEPROM.

#### SPI DMC

DMC also shall access SPI EEPROM using the SPI\_DMC interface.

#### I2C\_1

The I<sup>2</sup>C interface I2C-1 is connected to the DMC and PD controllers. DMC acts as an I<sup>2</sup>C master and PD controller acts as the I<sup>2</sup>C slave for this interface.

#### 12C 2

The I<sup>2</sup>C interface I2C-2 is connected to the DMC and PD controllers – DMC I<sup>2</sup>C is a slave; and PD I<sup>2</sup>C is unused with default firmware. An external I<sup>2</sup>C master, such as Embedded Controller (EC), shall use this interface to communicate to the DMC and PD controllers.

#### I2C HUB

The I<sup>2</sup>C interface I2C HUB is connected to the Hub controller – Hub controller acting as I<sup>2</sup>C slave. DMC shall access I2C HUB by connecting externally using I2C\_1 to read hub status and write hub configurations.

#### VSEL\_I2C

VSEL\_GPIO1 and VSEL\_GPIO2 shall be used for selecting the VBUS voltage level of PD ports. VSEL\_GPIO1 acts as I2C\_MASTER\_SDA and VSEL\_GPIO2 acts as I2C\_MASTER\_SCL. These pins must be connected to the external Power Regulator's I<sup>2</sup>C interface to configure voltage levels for PD ports.

#### Reset

There are three reset pins for the HX3PD device. These pins control reset operations for the Hub controller (RESET\_HUB), reset to DMC (XRES\_DMC), and reset to PD controller (XRES\_PD). Additionally, the HX3PD reset shall be controlled by DMC using a Software reset mechanism during configuration and initialization.

#### Clock

HX3PD requires an external crystal connected to XIN/XOUT with 25 MHz ( $\pm 150$  ppm), parallel resonant, fundamental mode, and be capable of low drive level (<200  $\mu$ W) with a peak-to-peak jitter less than 50 ps.

#### **Configuration Options**

EZ-USB HX3PD Configuration Utility can be used to update firmware and configurations of Hub controller, PD controller, and DMC. Firmware and configuration image for the hub controller is stored in an external SPI EEPROM. PD controller and DMC images will be stored in device flash.

Following configuration options are available in EZ-USB HX3PD Configuration tool.

Table 3. EZ-USB HX3PD Configuration Options

| No        | Settings                           | Description                                                                                                                                                                                                         |

|-----------|------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Hub Cont  | roller Configurations              |                                                                                                                                                                                                                     |

| 1         | VID                                | Custom Vendor ID                                                                                                                                                                                                    |

| 2         | USB 2.0 PID                        | Custom Product ID for USB 2.0 Hub                                                                                                                                                                                   |

| 3         | USB 3.1 PID                        | Custom Product ID for USB 3.1 Hub                                                                                                                                                                                   |

| 4         | Power good time                    | Time for Power-On sequence start in a port to Power is good to that port                                                                                                                                            |

| 5         | PolyFuse                           | Set the hub for polyfuse mode operation. Power good time is set to '0' for polyfused mode                                                                                                                           |

| 6         | String descriptor: Vendor          | String descriptor for Vendor name                                                                                                                                                                                   |

| 7         | String descriptor: USB 2.0 Product | String descriptor for USB 2.0 Hub Product Name                                                                                                                                                                      |

| 8         | String descriptor: USB 3.1 Product | String descriptor for USB 3.1 Hub Product Name                                                                                                                                                                      |

| 9         | Serial                             | Product Serial Number                                                                                                                                                                                               |

| 10        | Number of USB 2.0 ports            | Number of active USB 2.0 ports                                                                                                                                                                                      |

| 11        | Number of USB 3.1 ports            | Number of active USB 3.1 ports.  Note "Number of USB 3.1 ports" should be equal or lower than "Number of USB 2.0 ports".                                                                                            |

| 12        | Charging port                      | Enable or disable of BC 1.2 or Apple charging for DS ports                                                                                                                                                          |

| 13        | Compound hub                       | Removable or non-removable settings for DS ports.  Note DMC port is always set as "Non-removable".                                                                                                                  |

| 14        | DFP fast charging                  | Enable or disable of CDP, Pure DCP, and Auto DCP modes in downstream ports.  Note Pure DCP used for compliance tests. Auto DCP allows fast charging for Apple 2.1A/2.4A supported device or Samsung Galaxy devices. |

| 15        | USB type-C current                 | Maximum Type-C current for DS2 and DS3, 1.5A or 3.0 A                                                                                                                                                               |

| 16        | High active power switch           | Enable Active-High power switch                                                                                                                                                                                     |

| PD Contro | oller Configurations               |                                                                                                                                                                                                                     |

| 1         | VID                                | PD controller Vendor ID                                                                                                                                                                                             |

| 2         | PID                                | PD controller Product ID                                                                                                                                                                                            |

| 3         | PD version                         | PD version supported by device. PD controller support PD 2.0 and PD 3.0 versions supported.                                                                                                                         |

| 4         | Port power role                    | Selection of Sink, Source, or Dual Role modes                                                                                                                                                                       |

| 5         | Rp supported                       | Rp values supported by the PD ports. Both PD ports support Default, 1.5A and 3A current levels                                                                                                                      |

Document Number: 002-16615 Rev. \*I Page 13 of 25

Table 3. EZ-USB HX3PD Configuration Options (continued)

| No                            | Settings                  | Description                                                                                               |  |  |  |

|-------------------------------|---------------------------|-----------------------------------------------------------------------------------------------------------|--|--|--|

| Hub Controller Configurations |                           |                                                                                                           |  |  |  |

| 6                             | Power data objects (PDOs) | Power source and sink capabilities of the PD ports. Default PD firmware support 5V, 9V, 15V and 20V PDOs. |  |  |  |

| 7                             | Overvoltage protection    | Enable, threshold, and debounce of Over voltage protection                                                |  |  |  |

| 8                             | Overcurrent protection    | Enable, threshold, and debounce of Over current protection                                                |  |  |  |

| 9                             | VCONN OCP                 | Enable, threshold, and debounce of VCONN over current protection                                          |  |  |  |

| DMC Confi                     | gurations                 |                                                                                                           |  |  |  |

| 1                             | VID                       | DMC Vendor ID                                                                                             |  |  |  |

| 2                             | PID                       | DMC Product ID                                                                                            |  |  |  |

| 3                             | Billboard enable          | Billboard enable selection                                                                                |  |  |  |

You can download the EZ-USB HX3PD Configuration tool and its associated documentation at the following link: www.cypress.com/products/ez-usb-hx3pd-usb-31-gen-2-hub-power-delivery

# **Absolute Maximum Ratings**

Exceeding maximum ratings may shorten the useful life of the device.

# **Electrical Specifications**

HX3PD meets all USB-IF Electrical Compliance specifications.

#### **DC Electrical Characteristics**

| Parameter                               | Description                                             | Min  | Тур | Max  | Unit |

|-----------------------------------------|---------------------------------------------------------|------|-----|------|------|

| V1P2                                    | 1.2-V voltage supply                                    | 1.14 | 1.2 | 1.26 | V    |

| $V_{DDIO}$                              | 3.3-V I/O voltage supply                                | 3.0  | 3.3 | 3.6  | V    |

| V3P3                                    | 3.3-V voltage supply                                    | 3    | 3.3 | 3.6  | V    |

| $V_{DD10}$                              | 1.0-V core supply voltage                               | 0.95 | 1.0 | 1.05 | V    |

| V3P3_U2                                 | 3.3-V supply for the USB 2.0 PHY                        | 3    | 3.3 | 3.6  | V    |

| V <sub>DDD (PD)</sub>                   | 3.3-V supply input to PD controller                     | 3    | 3.3 | 5.5  | V    |

| V <sub>CCD_PD</sub>                     | Regulator output for PD controller                      | _    | 1.8 | _    | V    |

| V <sub>DDD (DMC)</sub>                  | 3.3-V supply input to DMC                               | 2.7  | 3.3 | 5.5  | V    |

| V <sub>CCD_DMC</sub>                    | Regulator output for DMC                                | _    | 1.8 | _    | V    |

| V <sub>BUS</sub>                        | VBUS for upstream port                                  | 0    | 5   | 5.25 | V    |

| V5P0_P0                                 | VCONN input to Upstream PD port                         | 2.7  | _   | 5.5  | V    |

| V5P0_P1                                 | VCONN input to Downstream PD port                       | 2.7  | _   | 5.5  | V    |

| VRAMP                                   | Voltage ramp rate on core and I/O supplies              | 0.05 | _   | 5    | V/s  |

| ESD_HBM                                 | Electrostatic discharge human body model                | _    | _   | 2200 | V    |

| ESD_CDM                                 | Electrostatic discharge charged device model            | _    | _   | 500  | V    |

| LU                                      | Pin current for latch-up                                | -100 | _   | 100  | mA   |

| Power Supply                            | Specifications                                          |      |     |      |      |

| ICC12                                   | 1.2 V supplies operating current                        | _    | _   | 750  | mA   |

| Іссзз                                   | 3.3 V supplies operating current                        | _    | _   | 70   | mA   |

| ISB12                                   | 1.2 V supplies combined suspend current                 | _    | 23  | _    | mA   |

| ISB33                                   | 3.3 V supplies combined suspend current                 | _    | 3   | _    | mA   |

| I/O Specifications - Except USB Signals |                                                         |      |     |      |      |

| V <sub>IH</sub>                         | Input voltage HIGH threshold                            | 2    | _   | 5.5  | V    |

| V <sub>IL</sub>                         | Input voltage LOW threshold                             | _    | _   | 0.8  | V    |

| V <sub>OH</sub>                         | Output voltage HIGH level (when I <sub>OH</sub> = 4 mA) | 2.4  | _   | _    | V    |

| V <sub>OL</sub>                         | Output voltage LOW level (when I <sub>OL</sub> = 8 mA)  | _    | _   | 0.4  | V    |

| I <sub>IL</sub>                         | Input leakage current                                   | -1   | _   | 1    | μΑ   |

## **Power Consumption**

Table 4 provides the power consumption estimates for HX3PD under different conditions.

**Table 4. Power Consumption**

|                      | Hub Occuption Condition                   | Measured C | Measured Current (mA) |  |  |

|----------------------|-------------------------------------------|------------|-----------------------|--|--|

|                      | Hub Operating Condition                   | VP12       | VP33                  |  |  |

| Upstream Not Conne   | cted to Host                              | 52.0       | 36.0                  |  |  |

| Hub in Suspend Mod   | е                                         | 25.0       | 12.8                  |  |  |

| Connected to Host ar | nd Hub in Idle Mode                       | 63.0       | 48.5                  |  |  |

| Hub in Reset Mode    |                                           | 14.5       | 2.5                   |  |  |

| Write                | 1 USB 3.1 device connected                | 298.0      | 50.0                  |  |  |

|                      | 2 USB 3.1 devices connected               | 376.0      | 49.3                  |  |  |

|                      | 3 USB 3.1 devices connected               | 442.0      | 49.3                  |  |  |

|                      | 4 USB 3.1 devices connected               | 485.0      | 49.3                  |  |  |

|                      | 5 USB 3.1 devices connected               | 520.0      | 49.3                  |  |  |

|                      | 5 USB 3.1 and 1 USB 2.0 devices connected | 535.0      | 49.3                  |  |  |

|                      | 5 USB 3.1 and 2 USB 2.0 devices connected | 548.0      | 49.3                  |  |  |

| Read                 | 1 USB 3.1 device connected                | 295.0      | 49.3                  |  |  |

|                      | 2 USB 3.1 devices connected               | 375.0      | 49.3                  |  |  |

|                      | 3 USB 3.1 devices connected               | 442.0      | 49.3                  |  |  |

|                      | 4 USB 3.1 devices connected               | 482.0      | 49.3                  |  |  |

|                      | 5 USB 3.1 devices connected               | 519.0      | 49.3                  |  |  |

|                      | 5 USB 3.1 and 1 USB 2.0 devices connected | 535.0      | 49.3                  |  |  |

|                      | 5 USB 3.1 and 2 USB 2.0 devices connected | 548.0      | 49.3                  |  |  |

# **Ordering Information**

The following table lists HX3PD's ordering information. The table contains only the part numbers that are currently available for order. Additional part numbers with customized configurations can be made available on request. For more information, visit the Cypress website or contact the local sales representative.

Table 5. Ordering Information

| Ordering Part Number | No of Ports | US PD Port | DS PD Port | Signed FW<br>Download |

|----------------------|-------------|------------|------------|-----------------------|

| CYUSB4347-BZXC       | 7           | DRP        | DFP        | No                    |

| CYUSB4357-BZXC       | 7           | DRP        | DFP        | Yes                   |

## **Ordering Code Definitions**

Document Number: 002-16615 Rev. \*I Page 17 of 25

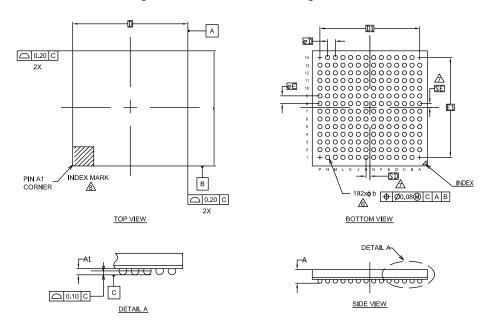

# **Package Diagram**

Figure 5. 192-Ball FBGA Package Outline

| SYMBOL  | DIMENSIONS |          |      |  |

|---------|------------|----------|------|--|

| STIMBUL | MIN.       | NOM.     | MAX. |  |

| А       |            | _        | 1.45 |  |

| A1      | 0.25       | 0.35     | 0.45 |  |

| D       | 1          | 2.00 BS  | С    |  |

| E       | 1          | 2.00 BS  | С    |  |

| D1      | 10.40 BSC  |          |      |  |

| E 1     | 10.40 BSC  |          |      |  |

| MD      | 14         |          |      |  |

| ME      | 14         |          |      |  |

| n       |            | 192      |      |  |

| ФЬ      | 0.35       | 0.45     | 0.55 |  |

| eD      | 0.80 BSC   |          |      |  |

| eE      | 0.80 BSC   |          |      |  |

| SD/SE   | (          | 0.40 BSC | ;    |  |

#### <u>NOTES</u>

- 1. ALL DIMENSIONS ARE IN MILLIMETERS.

- 2. DIMENSIONS AND TOLERANCES METHODS PER ASME Y14.5-2009. THIS OUTLINE CONFORMS TO JEP95, SECTION 4.5.

- 3. BALL POSITION DESIGNATION PER JEP95, SECTION 3, SPP-010.

- 4. "e" REPRESENTS THE SOLDER BALL GRID PITCH.

- 5. SYMBOL "MD" IS THE BALL MATRIX SIZE IN THE "D" DIRECTION. SYMBOL "ME" IS THE BALL MATRIX SIZE IN THE "E" DIRECTION. IN IS THE NUMBER OF POPULATED SOLDER BALL POSITIONS FOR MATRIX SIZE MD X ME.

- ⚠ DIMENSION "b" IS MEASURED AT THE MAXIMUM BALL DIAMETER IN A PLANE PARALLEL TO DATUM C.

- ↑ "SD" AND "SE" ARE MEASURED WITH RESPECT TO DATUMS A AND B AND

DEFINE THE POSITION OF THE CENTER SOLDER BALL IN THE OUTER ROW.

WHEN THERE IS AN ODD NUMBER OF SOLDER BALLS IN THE OUTER ROW,

"SD" OR "SE" =0.

\*\*TOTAL CONTROL

SET SOLDER

"SD" OR "SE" =0.

\*\*TOTAL CONTROL

SET SOLDER

"SD" OR "SE" =0.

\*\*TOTAL CONTROL

SET SOLDER

SE

- WHEN THERE IS AN EVEN NUMBER OF SOLDER BALLS IN THE OUTER ROW, "SD" = eD/2 AND "SE" = eE/2.

- A1 CORNER TO BE IDENTIFIED BY CHAMFER, LASER OR INK MARK. METALLIZED MARK INDENTATION OR OTHER MEANS.

- 9. "+" INDICATES THE THEORETICAL CENTER OF DEPOPULATED BALLS.

002-13493 \*A

## Silicon Revision History

This datasheet is applicable for USB-IF certified (TID# 5030000008) HX3PD Rev B and Rev A silicon.

Rev B: This silicon improves the yield of HX3PD, and fixed the Errata #2 ("Hub LVS Test "TD 10.102" Failure in DS1 to DS5 ports [1]") applicable to the Rev A silicon. There is no need to change the board design or layout to use the HX3PD Rev B Silicon. Products are completely compatible with the HX3 Rev A Silicon.

However Rev B silicon requires a different firmware compared to Rev A silicon. Refer to EZ-USB HX3PD Firmware webpage for more details

#### Method of Identification

Markings on row 3 of the HX3PD package differentiate Rev. B Silicon from Rev. A Silicon as indicated in the example below. Cypress maintains traceability of product to wafer level, including wafer fabrication location, through the lot number marked on the package.

Figure 6. HX3PD REV A Silicon

Figure 7. HX3PD REV B Silicon

## Acronyms

Table 6. Acronyms Used in this Document

| Acronym | Description                                            |  |

|---------|--------------------------------------------------------|--|

| AES     | Advanced Encryption Standard                           |  |

| ВС      | Battery Charging                                       |  |

| CC      | Configuration Channel                                  |  |

| CDP     | Charging Downstream Port                               |  |

| CPU     | Central Processing Unit                                |  |

| CRC     | Cyclic Redundancy Check, an Error-Checking Protocol    |  |

| DS      | DownStream                                             |  |

| DCP     | Dedicated Charging Port                                |  |

| DFP     | Downstream Facing Port                                 |  |

| DMC     | Dock Management Controller                             |  |

| DNU     | Do Not Use                                             |  |

| DP      | DisplayPort                                            |  |

| DRP     | Dual-Role Power Port                                   |  |

| DWG     | Device Working Group                                   |  |

| EC      | Embedded Controller                                    |  |

| EEPROM  | Electrically Erasable Programmable Read-Only Memory    |  |

| FS      | Full-Speed                                             |  |

| FW      | FirmWare                                               |  |

| GND     | GrouND                                                 |  |

| GPIO    | General-Purpose Input/Output                           |  |

| HS      | Hi-Speed                                               |  |

| I2C     | Inter Integrated Circuit, a communications protocol    |  |

| ISP     | In-System Programming                                  |  |

| I/O     | Input/Output                                           |  |

| LS      | Low-Speed                                              |  |

| MCU     | Microcontroller Unit                                   |  |

| NC      | No Connect                                             |  |

| OTG     | On-The-Go                                              |  |

| PD      | Power Delivery                                         |  |

| PID     | Product ID                                             |  |

| POR     | Power-On Reset                                         |  |

| ROM     | Read-Only Memory                                       |  |

| SCL     | Serial CLock                                           |  |

| SDA     | Serial DAta                                            |  |

| SHA     | Secure Hash Algorithm                                  |  |

| SPI     | Serial Peripheral Interface, a communications protocol |  |

Table 6. Acronyms Used in this Document

| Acronym | Description            |  |  |

|---------|------------------------|--|--|

| SS      | SuperSpeed             |  |  |

| TT      | Transaction Translator |  |  |

| UFP     | Upstream Facing Port   |  |  |

| US      | UpStream               |  |  |

| USB     | Universal Serial Bus   |  |  |

| VID     | Vendor ID              |  |  |

#### **Reference Documents**

USB 2.0 Specification

USB 3.1 Specification

Battery Charging Specifications

USB Type-C Specification

USB Power Delivery Specification

## **Document Conventions**

#### **Units of Measure**

Table 7. Units of Measure

| Symbol | Unit of Measure    |  |  |

|--------|--------------------|--|--|

| °C     | degree celsius     |  |  |

| Ω      | ohm                |  |  |

| Gbps   | gigabit per second |  |  |

| KB     | kilobyte           |  |  |

| kHz    | kilohertz          |  |  |

| kΩ     | kilo-ohm           |  |  |

| Mbps   | megabit per second |  |  |

| MHz    | megahertz          |  |  |

| μΑ     | microampere        |  |  |

| mA     | milliampere        |  |  |

| ms     | millisecond        |  |  |

| mW     | milliwatt          |  |  |

| ns     | nanosecond         |  |  |

| ppm    | parts per million  |  |  |

| V      | volt               |  |  |

#### **Errata**

|   | No. | Errata                                                         | Applicability                 |

|---|-----|----------------------------------------------------------------|-------------------------------|

|   | 1   | Type-C Compliance Test "TD 4.1.2" Failure in DS2 and DS3 ports | HX3PD Rev A and Rev B silicon |

| Ī | 2   | Hub LVS Test "TD 10.102" Failure in DS1 to DS5 ports           | HX3PD Rev A silicon only      |

#### 1. Type-C Compliance Test "TD 4.1.2" Failure in DS2 and DS3 ports

- Problem Definition: DS2 and DS3 ports present Rd when HX3PD is in Power-off state that leads to this compliance failure.

- Parameters Affected: N/A

- Trigger Condition(s): Type-C compliance test "TD 4.1.2 Unpowered CC Voltage Test" shows this failure condition. This is because test expects no power to be present when HX3PD is in Power-off state.

- Scope of Impact: There is no functional impact to the end user. This Errata is applicable only when DS2 and DS3 ports are used as Type-C ports and there will be no impact when DS2 and DS3 are used as Legacy Type-A ports. Also, Type-C compliance test "TD 4.1.2 Unpowered CC Voltage Test" failure is applicable only when DS2 and DS3 ports are expected to connect to a VBUS Source (such as power adapter) which is not a real use case.

- Workaround: No workaround available. This issue will not cause any functional issues or damage to silicon. Need waiver for compliance tests.

- Fix Status: No fix planned.

- 2. Hub LVS Test "TD 10.102" Failure in DS1 to DS5 ports [1]

- Problem Definition: HX3PD's Hub port shows wrong value for PORT\_LINK\_STATE parameter during link loopback mode.

- Parameters Affected: N/A

- Trigger Condition(s): Hub LVS test "TD 10.102" shows this failure condition. This failure will never happen in functional modes.

- Scope of Impact: Hub LVS test "TD 10.102 Power Off Upstream Port Test" failure is applicable only in test mode; in a normal functional mode, HX3PD will never be in test mode and hence no impact.

- Workaround: No workaround available for Rev A silicon. Issue fixed in Rev B silicon.

- Fix Status: Errata seen only in Rev A silicon. It is fixed in Rev B silicon.

#### Note

1. Applicable only for Rev A silicon.

# **Document History Page**

| Revision | ECN     | Submission<br>Date | Description of Change                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|----------|---------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| **       | 5894940 | 10/03/2017         | New data sheet.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |