### Active Clamp Synchronous Forward Controller

#### **FEATURES**

- Input Voltage Range: 8.5V to 100V

- Programmable Volt-Second Clamp

- High Efficiency Control: Active Clamp,

Synchronous Rectification, Programmable Delays

- Short-Circuit (Hiccup Mode) Overcurrent Protection

- Programmable Soft-Start/Stop

- Programmable OVLO and UVLO with Hysteresis

- Programmable Frequency (100kHz to 500kHz)

- Synchronizable to an External Clock

#### **APPLICATIONS**

- Industrial, Automotive and Military Systems

- 48V Telecommunication Isolated Power Supplies

#### DESCRIPTION

The LT®3753 is a current mode PWM controller optimized for an active clamp forward converter topology, allowing up to 100V input operation.

A programmable volt-second clamp allows primary switch duty cycles above 50% for high switch, transformer and rectifier utilization. Active clamp control reduces switch voltage stress and increases efficiency. A synchronous output is available for controlling secondary side synchronous rectification.

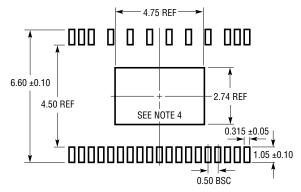

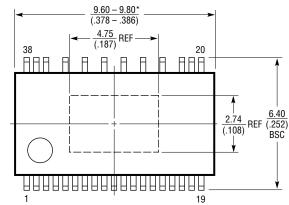

The LT3753 is available in a 38-lead plastic TSSOP package with missing pins for high voltage spacings.

All registered trademarks and trademarks are the property of their respective owners.

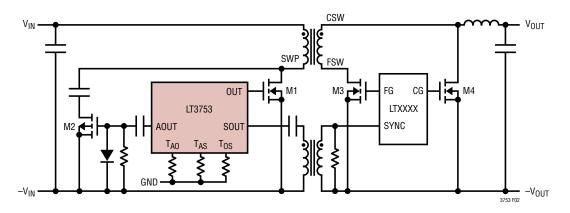

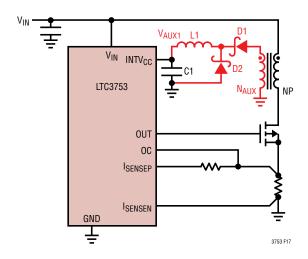

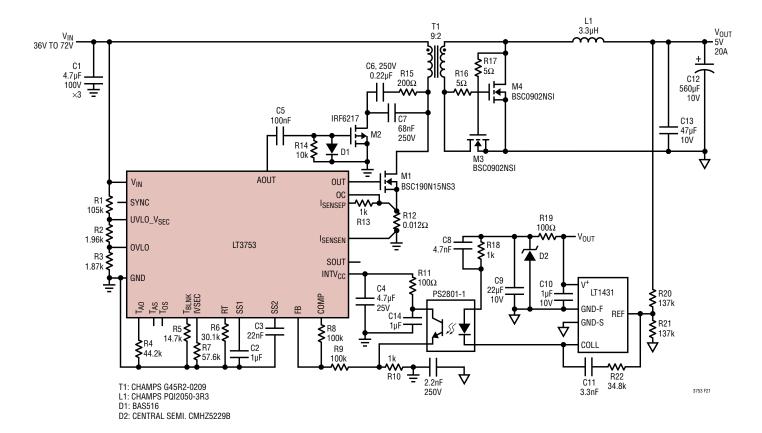

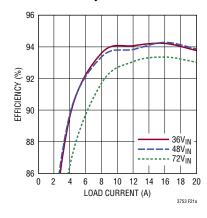

#### TYPICAL APPLICATION

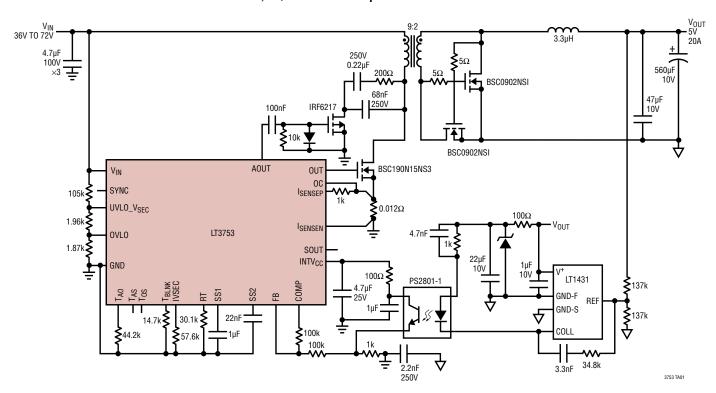

#### 36V to 72V, 5V/20A Active Clamp Isolated Forward Converter

Rev. C

Downloaded from Arrow.com.

## LT3753

### TABLE OF CONTENTS

| Features                                        | 1  |

|-------------------------------------------------|----|

| Applications                                    | 1  |

| Typical Application                             | 1  |

| Description                                     |    |

| Table of Contents                               | 2  |

| Absolute Maximum Ratings                        | 3  |

| Order Information                               |    |

| Pin Configuration                               |    |

| Electrical Characteristics                      |    |

| Typical Performance Characteristics             | 7  |

| Pin Functions                                   |    |

| Block Diagram                                   | 11 |

| Timing Diagrams                                 | 12 |

| Operation                                       |    |

| Introduction                                    | 14 |

| Part Start-Up                                   |    |

| Applications Information                        | 15 |

| Programming System Input Undervoltage           |    |

| Lockout (UVLO) Threshold and Hysteresis         | 15 |

| Soft-Stop Shutdown                              | 15 |

| Micropower Shutdown                             | 15 |

| Programming System Input Overvoltage            |    |

| Lockout (OVLO) Threshold                        | 15 |

| Programming Switching Frequency                 | 16 |

| Synchronizing to an External Clock              |    |

| $INTV_{CC}$ Regulator Bypassing and Operation . | 16 |

| Adaptive Leading Edge Blanking Plus             |    |

| Programmable Extended Blanking                  | 17 |

| Current Sensing and Programmable Slope          |    |

| Compensation                                    | 18 |

| Overcurrent: Hiccup Mode                        | 18 |

| Programming Maximum Duty Cycle Clamp:           |    |

| D <sub>VSEC</sub> (Volt-Second Clamp)           | 18 |

| D <sub>VSEC</sub> Open Loop Control: No Opto-Coupler,   |      |

|---------------------------------------------------------|------|

| Error Amplifier or Reference                            | 19   |

| R <sub>IVSEC</sub> : Open Pin Detection Provides Safety | 19   |

| Transformer Reset: Active Clamp Technique               | 20   |

| LO Side Active Clamp Topology (LT3753)                  | 20   |

| HI Side Active Clamp Topology (LT3752-1)                | 22   |

| Active Clamp Capacitor Value and Voltage                |      |

| Ripple                                                  | 22   |

| Active Clamp MOSFET Selection                           | 23   |

| Programming Active Clamp Switch Timing:                 |      |

| AOUT to OUT $(t_{AO})$ and OUT to AOUT $(t_{OA})$       |      |

| - · · · · · · · · · · · · · · · · · · ·                 | 24   |

| Programming Synchronous Rectifier Timing:               |      |

| SOUT to OUT ( $t_{SO}$ ) and OUT to SOUT ( $t_{OS}$ )   |      |

| Delays                                                  | 24   |

| Soft-Start (SS1, SS2)                                   | 25   |

| Soft-Stop (SS1)                                         |      |

| Hard-Stop (SS1, SS2)                                    |      |

| OUT, AOUT, SOUT Pulse-Skipping Mode                     |      |

| AOUT Timeout                                            |      |

| Main Transformer Selection                              |      |

| Generating Auxiliary Supplies                           | 28   |

| Primary-Side Auxiliary Supply                           | 29   |

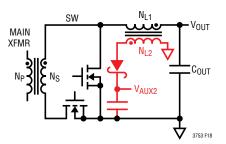

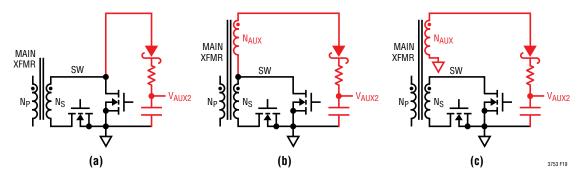

| Secondary-Side Auxiliary Supply                         |      |

| Primary-Side Power MOSFET Selection                     |      |

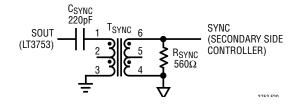

| Synchronous Control (SOUT)                              | 31   |

| Output Inductor Value                                   |      |

| Output Capacitor Selection                              |      |

| Input Capacitor Selection                               | 32   |

| PCB Layout/Thermal Guidelines                           | 33   |

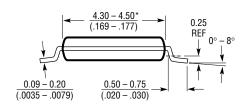

| Package Description                                     | 35   |

| Revision History                                        |      |

| Typical Application                                     |      |

| Related Parts                                           | - 36 |

### **ABSOLUTE MAXIMUM RATINGS**

#### (Note 1)

| V <sub>IN</sub> 100V                                       |

|------------------------------------------------------------|

| UVLO_V <sub>SEC</sub> , OVLO20V                            |

| INTV <sub>CC</sub> , SS216V                                |

| FB, SYNC6V                                                 |

| SS1, COMP, TEST1, RT3V                                     |

| I <sub>SENSEP</sub> , I <sub>SENSEN</sub> , OC, TEST20.35V |

| IVSEC–250μA                                                |

| Operating Junction Temperature Range (Notes 2, 3)          |

| LT3753EFE40°C to 125°C                                     |

| LT3753IFE40°C to 125°C                                     |

| LT3753HFE40°C to 150°C                                     |

| LT3753MPFE–55°C to 150°C                                   |

| Storage Temperature Range65°C to 150°C                     |

| Lead Temperature (Soldering, 10 Sec) 300°C                 |

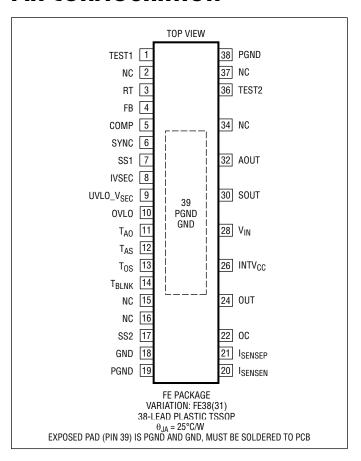

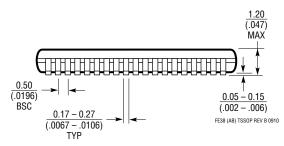

#### PIN CONFIGURATION

### **ORDER INFORMATION**

| LEAD FREE FINISH | TAPE AND REEL    | PART MARKING* | PACKAGE DESCRIPTION   | TEMPERATURE RANGE |

|------------------|------------------|---------------|-----------------------|-------------------|

| LT3753EFE#PBF    | LT3753EFE#TRPBF  | LT3753FE      | 38-Lead Plastic TSSOP | -40°C to 125°C    |

| LT3753IFE#PBF    | LT3753IFE#TRPBF  | LT3753FE      | 38-Lead Plastic TSSOP | -40°C to 125°C    |

| LT3753HFE#PBF    | LT3753HFE#TRPBF  | LT3753FE      | 38-Lead Plastic TSSOP | -40°C to 150°C    |

| LT3753MPFE#PBF   | LT3753MPFE#TRPBF | LT3753FE      | 38-Lead Plastic TSSOP | −55°C to 150°C    |

Contact the factory for parts specified with wider operating temperature ranges. \*The temperature grade is identified by a label on the shipping container.

Tape and reel specifications. Some packages are available in 500 unit reels through designated sales channels with #TRMPBF suffix.

# **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ . $V_{IN} = 12V$ , $UVLO\_V_{SEC} = 2.5V$ .

| PARAMETER                                                                                  | CONDITIONS                                            |   | MIN       | TYP      | MAX      | UNITS    |

|--------------------------------------------------------------------------------------------|-------------------------------------------------------|---|-----------|----------|----------|----------|

| Operational Input Voltage                                                                  |                                                       | • | 8.5       |          | 100      | V        |

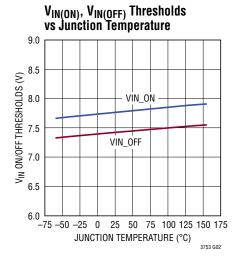

| V <sub>IN(ON)</sub>                                                                        |                                                       | • |           | 7.75     | 8.4      | V        |

| V <sub>IN(OFF)</sub>                                                                       |                                                       |   |           | 7.42     |          | V        |

| V <sub>IN(ON/OFF)</sub> Hysteresis                                                         |                                                       | • | 0.11      | 0.33     | 0.55     | V        |

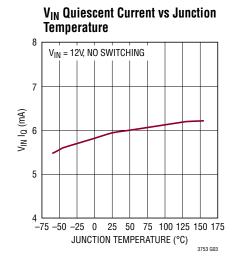

| V <sub>IN</sub> Quiescent Current                                                          | FB = 1.5V (Not Switching)                             |   |           | 5.9      | 7.5      | mA       |

| UVLO_V <sub>SEC</sub> Micropower Threshold (V <sub>SD</sub> )                              | I <sub>VIN</sub> < 20μA                               | • | 0.2       | 0.4      | 0.6      | V        |

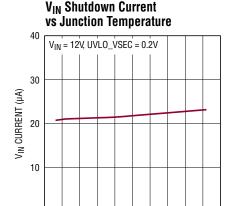

| V <sub>IN</sub> Shutdown Current (Micropower)                                              | UVLO_V <sub>SEC</sub> = 0.2V                          |   |           | 20       | 40       | μА       |

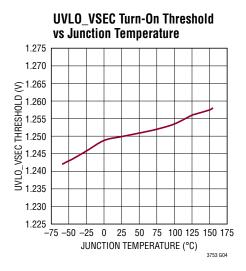

| UVLO_V <sub>SEC</sub> Threshold (V <sub>SYS_UV</sub> )                                     |                                                       | • | 1.180     | 1.250    | 1.320    | V        |

| V <sub>IN</sub> Shutdown Current (After Soft-Stop)                                         | UVLO_V <sub>SEC</sub> = 1V                            |   |           | 165      | 220      | μА       |

| UVLO_V <sub>SEC</sub> (ON) Current                                                         | UVLO_V <sub>SEC</sub> = V <sub>SYS_UV</sub> + 50mV    |   |           | 0        |          | μА       |

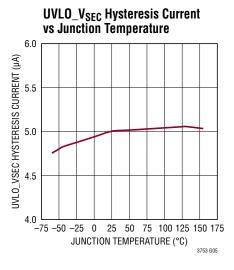

| UVLO_V <sub>SEC</sub> (OFF) Current Hysteresis Current With One-Shot Communication Current | $UVLO_{VSEC} = V_{SYS\_UV} - 50mV$ (Note 13)          | • | 4.0       | 5<br>25  | 6.0      | μΑ<br>μΑ |

| OVLO (Rising) (No Switching, Reset SS1)                                                    |                                                       | • | 1.220     | 1.250    | 1.280    | V        |

| OVLO (Falling) (Restart SS1)                                                               |                                                       |   |           | 1.215    | -        | V        |

| OVLO Hysteresis                                                                            |                                                       | • | 23        | 35       | 47       | mV       |

| OVLO Pin Current (Note 8)                                                                  | OVLO = 0V                                             |   |           | 5        | 100      | nA       |

|                                                                                            | 0VL0 = 1.5V (SS1 = 2.7V)<br>0VL0 = 1.5V (SS1 = 1.0V)  |   |           | 0.9<br>5 | 100      | mA<br>nA |

| Oscillator                                                                                 |                                                       |   |           |          |          |          |

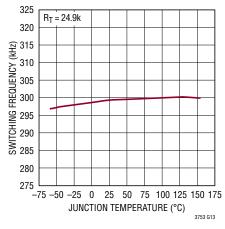

| Frequency: f <sub>OSC</sub> = 100kHz                                                       | $R_T = 82.5k$                                         |   | 94        | 100      | 106      | kHz      |

| Frequency: f <sub>OSC</sub> = 300kHz                                                       | $R_T = 24.9k$                                         | • | 279       | 300      | 321      | kHz      |

| Frequency: f <sub>OSC</sub> = 500kHz                                                       | R <sub>T</sub> = 14k                                  |   | 470       | 500      | 530      | kHz      |

| f <sub>OSC</sub> Line Regulation                                                           | $R_T = 24.9k, 8.5V < V_{IN} < 100V$                   |   |           | 0.05     | 0.1      | %/V      |

| Frequency and D <sub>VSEC</sub> Foldback Ratio (Fold)                                      | $SS1 = V_{SSACT} + 25mV$ , $SS2 = 2.7V$               |   |           | 4        |          |          |

| SYNC Input High Threshold                                                                  | (Note 4)                                              | • |           | 1.2      | 1.8      | V        |

| SYNC Input Low Threshold                                                                   | (Note 4)                                              | • | 0.6       | 1.025    |          | V        |

| SYNC Pin Current                                                                           | SYNC = 6V                                             |   |           | 75       |          | μA       |

| SYNC Frequency/Programmed f <sub>OSC</sub>                                                 |                                                       |   | 1.0       |          | 1.25     | kHz/kHz  |

| Linear Regulator (INTV <sub>CC</sub> )                                                     |                                                       |   |           |          |          |          |

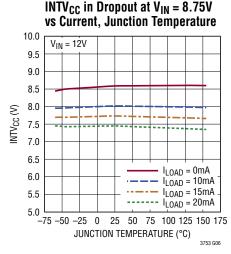

| INTV <sub>CC</sub> Regulation Voltage                                                      |                                                       |   | 9.4       | 10       | 10.4     | V        |

| Dropout (V <sub>IN</sub> -INTV <sub>CC</sub> )                                             | $V_{IN} = 8.75V$ , $I_{INTVCC} = 10mA$                |   |           | 0.6      |          | V        |

| INTV <sub>CC</sub> UVLO(+)                                                                 | (Start Switching)                                     |   |           | 7        | 7.4      | V        |

| INTV <sub>CC</sub> UVLO(-)                                                                 | (Stop Switching)                                      |   |           | 6.8      | 7.2      | V        |

| INTV <sub>CC</sub> UVLO Hysteresis                                                         |                                                       |   | 0.1       | 0.2      | 0.3      | V        |

| INTV <sub>CC</sub> OVLO(+)                                                                 | (Stop Switching)                                      |   | 15.9      | 16.5     | 17.2     | V        |

| INTV <sub>CC</sub> OVLO(-)                                                                 | (Start Switching)                                     |   | 15.4      | 16       | 16.7     | V        |

| INTV <sub>CC</sub> OVLO Hysteresis                                                         |                                                       |   | 0.38      | 0.5      | 0.67     | V        |

| INTV <sub>CC</sub> Current Limit                                                           | INTV <sub>CC</sub> = 0V<br>INTV <sub>CC</sub> = 8.75V | • | 9.5<br>19 | 13<br>27 | 17<br>32 | mA<br>mA |

# **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ . $V_{IN} = 12V$ , $UVLO\_V_{SEC} = 2.5V$ .

| PARAMETER                                               | CONDITIONS                                                                                                                                                                              |   | MIN        | TYP         | MAX         | UNITS    |

|---------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|------------|-------------|-------------|----------|

| Error Amplifier                                         |                                                                                                                                                                                         |   |            |             |             |          |

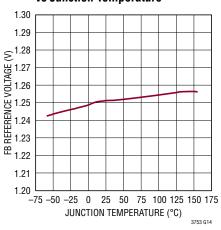

| FB Reference Voltage                                    |                                                                                                                                                                                         | • | 1.220      | 1.250       | 1.275       | V        |

| FB Line Reg                                             | 8.5V < V <sub>IN</sub> < 100V                                                                                                                                                           |   |            | 0.1         | 0.3         | mV/V     |

| FB Load Reg                                             | $COMP_SW - 0.1V < COMP < COMP_V_{OH} - 0.1V$                                                                                                                                            |   |            | 0.1         | 0.3         | mV/V     |

| FB Input Bias Current                                   | (Note 8)                                                                                                                                                                                |   |            | 50          | 200         | nA       |

| Open-Loop Voltage Gain                                  |                                                                                                                                                                                         |   |            | 85          |             | dB       |

| Unity-Gain Bandwidth                                    | (Note 6)                                                                                                                                                                                |   |            | 2.5         |             | MHz      |

| COMP Source Current                                     | FB = 1V, COMP = 1.75V (Note 8)                                                                                                                                                          |   | 6          | 11          |             | mA       |

| COMP Sink Current                                       | FB = 1.5V, COMP = 1.75V                                                                                                                                                                 |   | 6.5        | 11.5        |             | mA       |

| COMP Output High Clamp                                  | FB = 1V                                                                                                                                                                                 |   |            | 2.6         |             | V        |

| COMP Switching Threshold                                |                                                                                                                                                                                         |   |            | 1.25        |             | V        |

| Current Sense                                           |                                                                                                                                                                                         |   |            |             |             |          |

| I <sub>SENSEP</sub> Maximum Threshold                   | FB = 1V, OC = 0V                                                                                                                                                                        |   | 180        | 220         | 260         | mV       |

| COMP Current Mode Gain                                  | ΔV <sub>COMP</sub> /ΔV <sub>ISENSEP</sub>                                                                                                                                               |   |            | 6.1         |             | V/V      |

| I <sub>SENSEP</sub> Input Current (D = 0%)              | (Note 8)                                                                                                                                                                                |   |            | 2           |             | μA       |

| I <sub>SENSEP</sub> Input Current (D = 80%)             | (Note 8)                                                                                                                                                                                |   |            | 33          |             | μA       |

| I <sub>SENSEN</sub> Input Current                       | FB = 1.5V (COMP Open) (Note 8)                                                                                                                                                          |   |            | 20          | 30          | μA       |

|                                                         | FB = 1V (COMP Open) (Note 8)                                                                                                                                                            |   |            | 90          | 135         | μA       |

| OC Overcurrent Threshold                                |                                                                                                                                                                                         | • | 82.5       | 96          | 107.5       | mV       |

| OC Input Current                                        |                                                                                                                                                                                         |   |            | 200         | 500         | nA       |

| AOUT Driver (Active Clamp Switch Control)               |                                                                                                                                                                                         |   |            |             |             |          |

| AOUT Rise Time                                          | C <sub>L</sub> = 1nF (Note 5), INTV <sub>CC</sub> = 12V                                                                                                                                 |   |            | 23          |             | ns       |

| AOUT Fall Time                                          | C <sub>L</sub> = 1nF (Note 5), INTV <sub>CC</sub> = 12V                                                                                                                                 |   |            | 19          |             | ns       |

| AOUT Low Level                                          |                                                                                                                                                                                         |   |            | 0.1         |             | V        |

| AOUT High Level                                         | INTV <sub>CC</sub> = 12V                                                                                                                                                                |   | 11.9       |             |             | V        |

| AOUT High Level in Shutdown                             | UVLO_ $V_{SEC}$ = 0V, INTV $_{CC}$ = 8V, I <sub>AOUT</sub> = 1mA Out of the Pin                                                                                                         |   | 7.8        |             |             | V        |

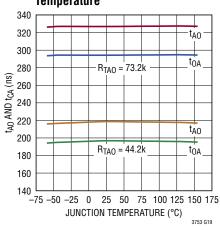

| AOUT Edge to OUT (Rise): (t <sub>AO</sub> )             | $C_{SOUT}$ = 1nF, $C_{OUT}$ = 3.3nF, INTV <sub>CC</sub> = 12V<br>$R_{TAO}$ = 44.2k<br>$R_{TAO}$ = 73.2k (Note 9)                                                                        |   | 168<br>253 | 218<br>328  | 268<br>403  | ns<br>ns |

| OUT (Fall) to AOUT Edge: (t <sub>OA</sub> )             | $C_{SOUT}$ = 1nF, $C_{OUT}$ = 3.3nF, INTV <sub>CC</sub> = 12V<br>$R_{TAO}$ = 44.2k<br>$R_{TAO}$ = 73.2k (Note 10)                                                                       |   | 150<br>214 | 196<br>295  | 250<br>376  | ns<br>ns |

| SOUT Driver (Synchronous Rectification Contro           | ol)                                                                                                                                                                                     |   |            |             |             |          |

| SOUT Rise Time                                          | C <sub>OUT</sub> = 1nF, INTV <sub>CC</sub> = 12V (Note 5)                                                                                                                               |   |            | 21          |             | ns       |

| SOUT Fall Time                                          | C <sub>OUT</sub> = 1nF, INTV <sub>CC</sub> = 12V (Note 5)                                                                                                                               |   |            | 19          |             | ns       |

| SOUT Low Level                                          |                                                                                                                                                                                         |   |            | 0.1         |             | V        |

| SOUT High Level                                         | INTV <sub>CC</sub> = 12V                                                                                                                                                                |   | 11.9       |             |             | V        |

| SOUT High Level in Shutdown                             | UVLO_V <sub>SEC</sub> = 0V, INTV <sub>CC</sub> = 8V, I <sub>SOUT</sub> = 1mA Out of the Pin                                                                                             |   | 7.8        |             |             | V        |

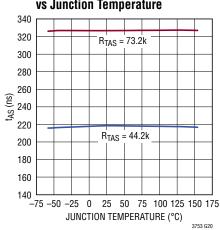

| AOUT Edge to SOUT (Fall): (t <sub>AS</sub> )            | $C_{AOUT} = C_{SOUT} = 1$ nF, INTV <sub>CC</sub> = 12V<br>$R_{TAS} = 44.2$ k (Note 11)<br>$R_{TAS} = 73.2$ k                                                                            |   | 168<br>253 | 218<br>328  | 268<br>403  | ns<br>ns |

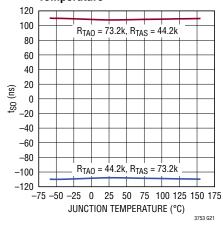

| SOUT (Fall) to OUT (Rise): $(t_{SO} = t_{AO} - t_{AS})$ | $C_{SOUT}$ = 1nF, $C_{OUT}$ = 3.3nF, INTV <sub>CC</sub> = 12V<br>R <sub>TAO</sub> = 73.2k, R <sub>TAS</sub> = 44.2k (Notes 9, 11)<br>R <sub>TAO</sub> = 44.2k, R <sub>TAS</sub> = 73.2k |   | 70<br>–70  | 110<br>–110 | 132<br>–132 | ns<br>ns |

## **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ . $V_{IN} = 12V$ , $UVLO_{VSEC} = 2.5V$ .

| PARAMETER                                                                                                                                                                                 | CONDITIONS                                                                                                                                                                                                                                                                                        | MIN                  | TYP                  | MAX                  | UNITS          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|----------------------|----------------------|----------------|

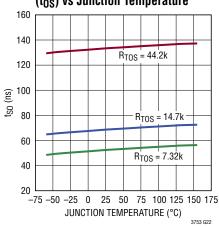

| OUT (Fall) to SOUT (Rise): (t <sub>OS</sub> )                                                                                                                                             | $C_{SOUT}$ = 1nF, $C_{OUT}$ = 3.3nF, INTV <sub>CC</sub> = 12V<br>$R_{TOS}$ = 14.7k<br>$R_{TOS}$ = 44.2k (Note 12)                                                                                                                                                                                 | 52<br>102            | 68<br>133            | 84<br>164            | ns<br>ns       |

| OUT Driver (Main Power Switch Control)                                                                                                                                                    |                                                                                                                                                                                                                                                                                                   |                      |                      |                      |                |

| OUT Rise Time                                                                                                                                                                             | $C_{OUT} = 3.3$ nF, INTV <sub>CC</sub> = 12V (Note 5)                                                                                                                                                                                                                                             |                      | 19                   |                      | ns             |

| OUT Fall Time                                                                                                                                                                             | C <sub>OUT</sub> = 3.3nF, INTV <sub>CC</sub> = 12V (Note 5)                                                                                                                                                                                                                                       |                      | 20                   |                      | ns             |

| OUT Low Level                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                   |                      | 0.1                  |                      | V              |

| OUT High Level                                                                                                                                                                            | INTV <sub>CC</sub> = 12V                                                                                                                                                                                                                                                                          | 11.9                 |                      |                      | V              |

| OUT Low Level in Shutdown                                                                                                                                                                 | UVLO_V <sub>SEC</sub> = 0V, INTV <sub>CC</sub> = 8V, I <sub>OUT</sub> = 1mA Into the Pin                                                                                                                                                                                                          |                      | 0.25                 |                      | V              |

| OUT (Volt-Sec) Max Duty Cycle Clamp  D <sub>VSEC</sub> (1 • System Input (Min)) × 100  D <sub>VSEC</sub> (2 • System Input (Min)) × 100  D <sub>VSEC</sub> (4 • System Input (Min)) × 100 | $\begin{aligned} R_T &= 22.6 \text{k, } R_{\text{IVSEC}} = 51.1 \text{k, FB} = 1 \text{V, SS1} = 2.7 \text{V} \\ \text{UVLO}\_\text{V}_{\text{SEC}} &= 1.25 \text{V} \\ \text{UVLO}\_\text{V}_{\text{SEC}} &= 2.50 \text{V} \\ \text{UVLO}\_\text{V}_{\text{SEC}} &= 5.00 \text{V} \end{aligned}$ | 68.5<br>34.3<br>17.5 | 72.5<br>36.5<br>18.6 | 76.2<br>38.7<br>19.7 | %<br>%<br>%    |

| OUT Minimum ON Time                                                                                                                                                                       | C <sub>OUT</sub> = 3.3nF, INTV <sub>CC</sub> = 12V (Note 7)<br>R <sub>TBLNK</sub> = 14.7k<br>R <sub>TBLNK</sub> = 73.2k (Note 14)                                                                                                                                                                 |                      | 325<br>454           |                      | ns<br>ns       |

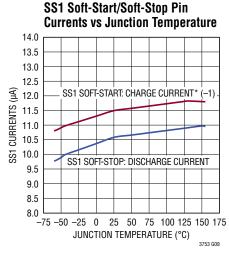

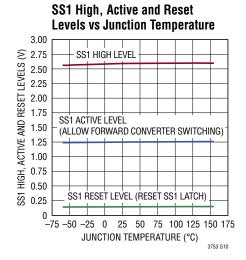

| SS1 Pin (Soft-Start: Frequency and D <sub>VSEC</sub> ) (S                                                                                                                                 | oft-Stop: COMP Pin, Frequency and D <sub>VSEC</sub> )                                                                                                                                                                                                                                             | '                    |                      |                      |                |

| SS1 Reset Threshold (V <sub>SS1(RTH)</sub> )                                                                                                                                              |                                                                                                                                                                                                                                                                                                   |                      | 150                  |                      | mV             |

| SS1 Active Threshold (V <sub>SS1(ACT)</sub> )                                                                                                                                             | (Allow Switching)                                                                                                                                                                                                                                                                                 |                      | 1.25                 |                      | V              |

| SS1 Charge Current (Soft-Start)                                                                                                                                                           | SS1 = 1.5V (Note 8)                                                                                                                                                                                                                                                                               | 7                    | 11.5                 | 16                   | μА             |

| SS1 Discharge Current (Soft-Stop)                                                                                                                                                         | SS1 = 1V, UVL0_V <sub>SEC</sub> = $V_{SYS\_UV} - 50$ mV                                                                                                                                                                                                                                           | 6.4                  | 10.5                 | 14.6                 | μА             |

| SS1 Discharge Current (Hard Stop) OC > OC Threshold INTV <sub>CC</sub> < INTV <sub>CC</sub> UVLO(-) OVLO > OVLO(+)                                                                        | SS1 = 1V                                                                                                                                                                                                                                                                                          |                      | 0.9<br>0.9<br>0.9    |                      | mA<br>mA<br>mA |

| SS2 Pin (Soft-Start: Comp Pin)                                                                                                                                                            |                                                                                                                                                                                                                                                                                                   | ,                    |                      |                      |                |

| SS2 Discharge Current                                                                                                                                                                     | SS1 < V <sub>SS(ACT)</sub> , SS2 = 2.5V                                                                                                                                                                                                                                                           |                      | 2.8                  |                      | mA             |

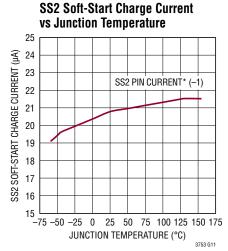

| SS2 Charge Current                                                                                                                                                                        | SS1 > V <sub>SS(ACT)</sub> , SS2 = 1.5V                                                                                                                                                                                                                                                           | 11                   | 21                   | 28                   | μА             |

**Note 1:** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

Note 2: The LT3753EFE is guaranteed to meet performance specifications from 0°C to 125°C junction temperature. Specifications over the -40°C to 125°C operating junction temperature range are assured by design, characterization and correlation with statistical process controls. The LT3753IFE is guaranteed to meet performance specifications from -40°C to 125°C junction temperature. The LT3753HFE is guaranteed to meet performance specifications from -40°C to 150°C junction temperature. The LT3753MPFE is tested and guaranteed to meet performance specifications from -55°C to 150°C junction temperature.

**Note 3:** For maximum operating ambient temperature, see the Thermal Calculations section in the Applications Information section.

**Note 4:** SYNC minimum and maximum thresholds are guaranteed by SYNC frequency range test using a clock input with guard banded SYNC levels of 0.7V low level and 1.7V high level.

**Note 5:** Rise and fall times are measured between 10% and 90% of gate driver supply voltage.

Note 6: Guaranteed by design.

**Note 7:** ON times are measured between rising and falling edges at 50% of gate driver supply voltage.

Note 8: Current flows out of pin.

**Note 9:** Guaranteed by correlation to R<sub>TAS</sub> = 73.2k test.

Note 10:  $t_{OA}$  timing guaranteed by design based on correlation to measured  $t_{AO}$  timing.

Note 11: Guaranteed by correlation to  $R_{TAO} = 44.2k$  test.

**Note 12:** Guaranteed by correlation to  $R_{TOS} = 14.7k$  test.

Note 13: A  $2\mu s$  one-shot of  $20\mu A$  from the  $UVLO\_V_{SEC}$  pin allows communication between ICs to begin shutdown (useful when stacking supplies for more power ( = inputs in parallel/outputs in series)). The current is tested in a static test mode. The  $2\mu s$  one-shot is guaranteed by design.

**Note 14:** Guaranteed by correlation to  $R_{TBLNK} = 14.7k$  test.

## TYPICAL PERFORMANCE CHARACTERISTICS $T_A = 25$ °C, unless otherwise noted.

0

25 50 75 100 125 150 175

JUNCTION TEMPERATURE (°C)

### TYPICAL PERFORMANCE CHARACTERISTICS $T_A = 25^{\circ}C$ , unless otherwise noted.

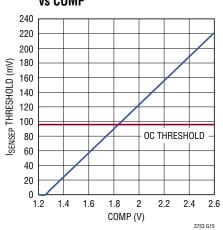

I<sub>SENSEP</sub> Maximum Threshold vs COMP

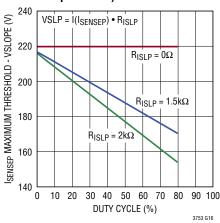

I<sub>SENSEP</sub> Maximum Threshold – VSLP vs Duty Cycle (Programming Slope Compensation)

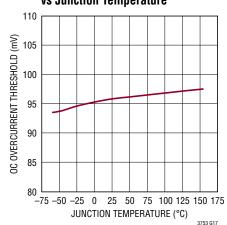

#### OC Overcurrent (Hiccup Mode) Threshold vs Junction Temperature

### TYPICAL PERFORMANCE CHARACTERISTICS $T_A = 25^{\circ}C$ , unless otherwise noted.

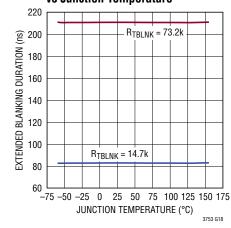

## Extended Blanking Duration vs Junction Temperature

# AOUT to OUT Delay ( $t_{AO}$ ) and OUT to AOUT Delay ( $t_{OA}$ ) vs Junction Temperature

## AOUT to SOUT Delay (t<sub>AS</sub>) vs Junction Temperature

# SOUT (Fall) to OUT (Rise) Delay $(t_{SO} = t_{AO} - t_{AS})$ vs Junction Temperature

## OUT (Fall) to SOUT (Rise) Delay (tos) vs Junction Temperature

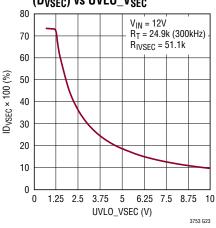

## OUT Maximum Duty Cycle Clamp (D<sub>VSEC</sub>) vs UVLO\_V<sub>SEC</sub>

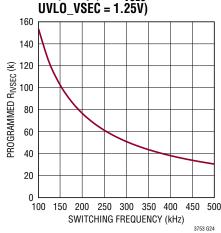

#### Required $R_{IVSEC}$ vs Switching Frequency (for $D_{VSEC} \times 100 = 72.5\%$ ,

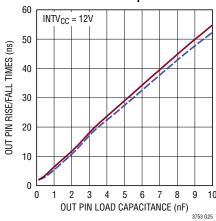

## OUT Pin Rise/Fall Times vs OUT Pin Load Capacitance

#### PIN FUNCTIONS

**TEST1 (Pin 1):** Connect to GND.

**NC (Pins 2, 15, 16, 34, 37):** No Connect Pins. These pins are not connected inside the IC. These pins should be left open.

**RT (Pin 3):** A resistor to ground programs switching frequency.

FB (Pin 4): Error Amplifier Inverting Input.

**COMP (Pin 5):** Error Amplifier Output. Allows various compensation networks for nonisolated applications.

**SYNC (Pin 6):** Allows synchronization of internal oscillator to an external clock. f<sub>SYNC</sub> equal to f<sub>OSC</sub> allowed.

**SS1 (Pin 7):** Capacitor controls soft-start/stop of switching frequency and volt-second clamp. During soft-stop it also controls the COMP pin.

**IVSEC (Pin 8):** Resistor Programs OUT Pin Maximum Duty Cycle Clamp ( $D_{VSEC}$ ). This clamp moves inversely proportional to system input voltage to provide a volt-second clamp.

**UVLO\_V**SEC (**Pin 9**): A resistor divider from system input allows switch maximum duty cycle to vary inversely proportional with system input. This volt-second clamp prevents transformer saturation for duty cycles above 50%. Resistor divider ratio programs undervoltage lockout (UVLO) threshold. A  $5\mu A$  pin current hysteresis allows programming of UVLO hysteresis. Pin below 0.4V reduces  $V_{IN}$  currents to microamps.

**OVLO (Pin 10):** A resistor divider from system input programs overvoltage lockout (OVLO) threshold. Fixed hysteresis included.

**T<sub>AO</sub>** (**Pin 11**): A resistor programs nonoverlap timing between AOUT rise and OUT rise control signals.

$T_{AS}$  (Pin 12): Resistors at  $T_{AO}$  and  $T_{AS}$  define delay between SOUT fall and OUT rise (=  $t_{AO} - t_{AS}$ ).

**T<sub>OS</sub>** (**Pin 13**): Resistor programs delay between OUT fall and SOUT rise.

**T<sub>BLNK</sub> (Pin 14):** Resistor programs extended blanking of I<sub>SENSEP</sub> and OC signals during MOSFET turn-on.

**SS2 (Pin 17):** Capacitor controls soft-start of COMP pin. Alternatively can connect to OPTO to communicate start of switching to secondary side. If unused, leave the pin open.

**GND (Pin 18):** Analog Signal Ground. Electrical connection exists inside the IC to the exposed pad (Pin 39).

**PGND** (Pins 19, 38, 39): The Power Grounds for the IC. The package has an exposed pad (Pin 39) underneath the IC which is the best path for heat out of the package. Pin 39 should be soldered to a continuous copper ground plane under the device to reduce die temperature and increase the power capability of the LT3753.

**I**<sub>SENSEN</sub> (**Pin 20**): Negative input for the current sense comparator. Kelvin connect to the sense resistor in the source of the power MOSFET.

**I**SENSEP (Pin 21): Positive input for the current sense comparator. Kelvin connect to the sense resistor in the source of the power MOSFET. A resistor in series with I<sub>SENSEP</sub> programs slope compensation.

**OC (Pin 22):** An accurate 96mV threshold, independent of duty cycle, for detection of primary side MOSFET overcurrent and trigger of hiccup mode. Connect directly to sense resistor in the source of the primary side MOSFET.

Missing Pins 23, 25, 27, 29, 31, 33, 35: Pins removed for high voltage spacings and improved reliability.

**OUT (Pin 24):** Drives the gate of an N-channel MOSFET between OV and INTV<sub>CC</sub>. Active pull-off exists in shutdown.

**INTV<sub>CC</sub> (Pin 26):** A linear regulator supply generated from  $V_{IN}$ . Supplies 10V for AOUT, SOUT and OUT gate drivers. INTV<sub>CC</sub> must be bypassed with a  $4.7\mu F$  capacitor to power ground. Can be externally driven by the housekeeping supply to remove power from within the IC.

$V_{IN}$  (Pin 28): Input Supply Pin. Bypass with  $1\mu$ F to ground.

**SOUT (Pin 30):** Sync signal for secondary side synchronous rectifier controller.

**AOUT (Pin 32):** Control signal for external active clamp switch.

TEST2 (Pin 36): Connect to GND.

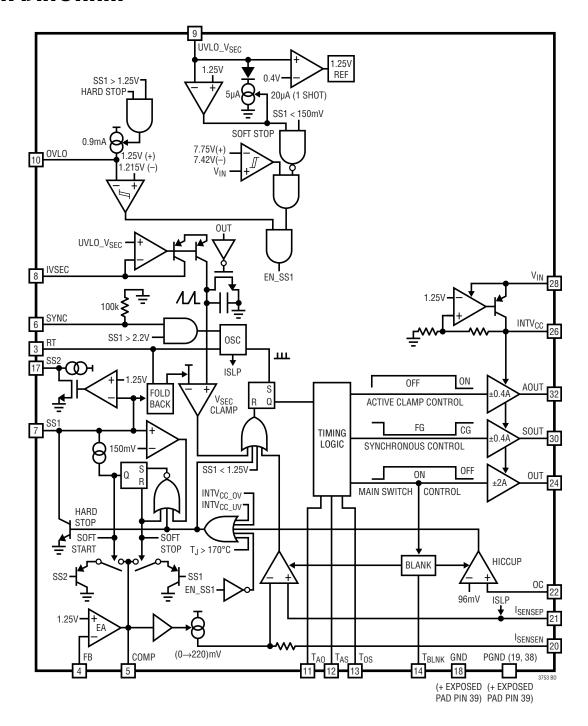

#### **BLOCK DIAGRAM**

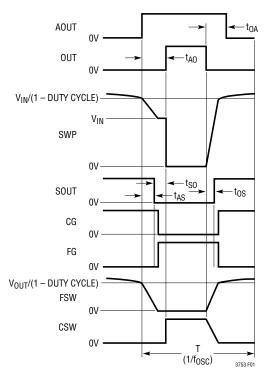

### TIMING DIAGRAMS

$t_{AO}$  Programmed by  $r_{TAO}$ ,  $t_{AS}$  Programmed by  $r_{TAS}$   $t_{OS}$  Programmed by  $r_{TOS}$ ,  $t_{OA}$  = 0.9 •  $t_{AO}$ ,  $t_{SO}$  =  $t_{AO}$  –  $t_{AS}$

Figure 1. Timing Diagram

Figure 2. Timing Reference Circuit

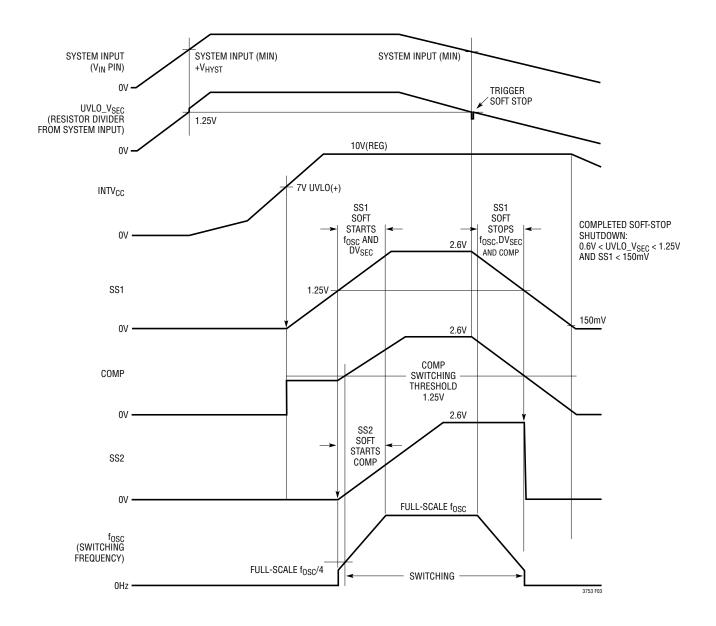

#### **TIMING DIAGRAMS**

Figure 3. Start-Up and Shutdown Timing Diagram

#### **OPERATION**

#### Introduction

The LT3753 is a primary side, current mode, PWM controller optimized for use in a synchronous forward converter with active clamp reset. The LT3753 allows  $V_{\text{IN}}$  pin operation between 8.5V and 100V. The LT3753 based forward converter is targeted for power levels up to 400W and is not intended for battery charger applications. For higher power levels the converter outputs can be stacked in series. Connecting UVLO\_V\_SEC pins, OVLO pins, SS1 pins and SS2 pins together allows blocks to react simultaneously to all fault modes and conditions.

The IC contains an accurate programmable volt-second clamp. When set above the natural duty cycle of the converter, it provides a duty cycle guardrail to limit primary switch reset voltage and prevent transformer saturation during load transients. The accuracy and excellent line regulation of the volt-second clamp provides V<sub>OUT</sub> regulation for open-loop conditions such as no opto-coupler, reference or error amplifier on the secondary side.

For applications not requiring isolation but requiring high step-down ratios, each IC contains a voltage error amplifier to allow a very simple nonisolated, fully regulated synchronous forward converter.

A range of protection features include programmable overcurrent (OC) hiccup mode, programmable system input undervoltage lockout (UVLO), programmable system input overvoltage lockout (OVLO) and built-in

thermal shutdown. Programmable slope compensation and switching frequency allow the use of a wide range of output inductor values and transformer sizes.

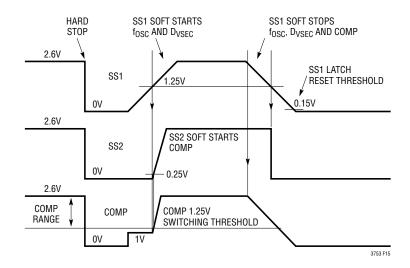

#### Part Start-Up

LT3753 start-up is best described by referring to the Block Diagram and to the start-up waveforms in Figure 3. For part start-up, system input voltage must be high enough to drive the UVLO\_V\_SEC pin above 1.25V and the V\_IN pin must be greater than 8.5V. An internal linear regulator is activated and provides a 10V INTV\_CC supply for all gate drivers. The SS1 pin of the forward controller is allowed to start charging when INTV\_CC reaches its 7V UVLO(+) threshold. When SS1 reaches 1.25V, the SS2 pin begins to charge, controlling COMP pin rise and the soft-start of output inductor peak current. The SS1 pin independently soft starts switching frequency and a volt-second clamp from 22% of their full-scale programmed values.

If secondary side control already exists for soft starting the converter output voltage then the SS2 pin can still be used to control initial inductor peak current rise. Simply programming the primary side SS2 soft-start faster than the secondary side allows the secondary side to take over. If SS2 is not needed for soft-start control, its pull-down strength and voltage rating also allow it to drive the input of an opto-coupler connected to  $INTV_{CC}$ . This allows the option of communicating to the secondary side that switching has begun.

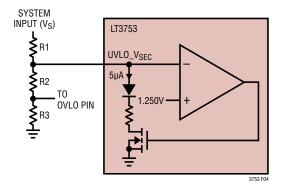

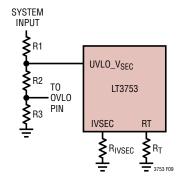

## Programming System Input Undervoltage Lockout (UVLO) Threshold and Hysteresis

The LT3753 has an accurate 1.25V shutdown threshold at the UVLO\_V<sub>SEC</sub> pin. This threshold can be used in conjunction with an external resistor divider to define the falling undervoltage lockout threshold (UVLO(–)) for the converter's system input voltage (V<sub>S</sub>) (Figure 4). A pin hysteresis current of  $5\mu A$  allows programming of the UVLO(+) threshold.

$V_S$  (UVLO(-)) [begin SOFT-STOP then shut down]

$$=1.25\left\lceil 1+\left(\frac{R1}{R2+R3}\right)\right\rceil$$

$$V_S$$

(UVLO(+)) [begin SOFT-START]

=  $V_S$  (UVLO(-)) + (5 $\mu$ A • R1)

It is important to note that the part enters soft-stop when the UVLO\_V\_SEC pin falls back below 1.25V. During soft-stop the converter continues to switch as it folds back switching frequency, volt-second clamp and COMP pin voltage. See Soft-Stop in the Applications Information section. When the SS2 pin is finally discharged below its 150mV reset threshold the forward converter is shut down.

Figure 4. Programming Undervoltage Lockout (UVLO)

#### **Soft-Stop Shutdown**

Soft-stop shutdown (similar to system undervoltage) can be commanded by an external control signal. A MOSFET with a diode (or diodes) in series with the drain should be used to pull down the UVLO\_V<sub>SEC</sub> pin below 1.25V but not below the micropower shutdown threshold of 0.6V(max). Typical  $V_{IN}$  quiescent current after soft-stop is 165µA.

#### Micropower Shutdown

If a micropower shutdown is required using an external control signal, an open-drain transistor can be directly connected to the UVLO\_V\_SEC pin. The LT3753 has a micropower shutdown threshold of typically 0.4V at the UVLO\_V\_SEC pin.  $V_{IN}$  quiescent current in micropower shutdown is  $20\mu A$ .

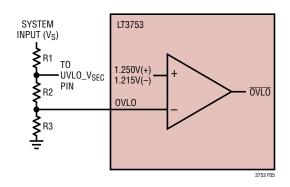

## Programming System Input Overvoltage Lockout (OVLO) Threshold

The LT3753 has an accurate 1.25V overvoltage shutdown threshold at the OVLO pin. This threshold can be used in conjunction with an external resistor divider to define the rising overvoltage lockout threshold (OVLO(+)) for the converter's system input voltage ( $V_S$ ) (Figure 5). When OVLO(+) is reached, the part stops switching immediately and a hard stop discharges the SS1 and SS2 pins. The falling threshold OVLO(–) is fixed internally at 1.215V and allows the part to restart in soft-start mode. A single resistor divider can be used from system input supply ( $V_S$ ) to define both the undervoltage and overvoltage thresholds for the system. Minimum value for R3 is 1k. If OVLO is unused, place a 10k resistor from OVLO pin to ground.

$V_S$  OVLO(+) [stop switching; HARD STOP]

$$=1.25\left[1+\left(\frac{R1+R2}{R3}\right)\right]$$

V<sub>S</sub> OVLO(-) [begin SOFT-START]

$$= V_S \ OVLO(+) \cdot \frac{1.215}{1.25}$$

Figure 5. Programming Overvoltage Lockout (OVLO)

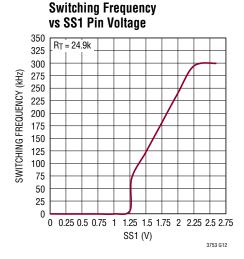

#### **Programming Switching Frequency**

The switching frequency for the LT3753 is programmed using a resistor,  $R_T$ , connected from analog ground (Pin 18) to the RT pin. Table 1 shows typical  $f_{OSC}$  vs  $R_T$  resistor values. The value for  $R_T$  is given by:

$$R_T = 8.39 \cdot X \cdot (1 + Y)$$

where.

$X = (10^9/f_{OSC}) - 365$

$Y = (300kHz - f_{OSC})/10^7 (f_{OSC} < 300kHz)$

$Y = (f_{OSC} - 300kHz)/10^7 (f_{OSC} > 300kHz)$

Example: For  $f_{OSC} = 200kHz$ ,

$R_T = 8.39 \cdot 4635 \cdot (1 + 0.01) = 39.28k \text{ (choose } 39.2k)$

The LT3753 includes frequency foldback at start-up (see Figure 3). In order to make sure that a SYNC input does not override frequency foldback during start-up, the SYNC function is ignored until SS1 pin reaches 2.2V.

Table 1.  $R_T$  vs Switching Frequency ( $f_{OSC}$ )

| SWITCHING FREQUENCY (kHz) | R <sub>T</sub> (kΩ) |

|---------------------------|---------------------|

| 100                       | 82.5                |

| 150                       | 53.6                |

| 200                       | 39.2                |

| 250                       | 30.9                |

| 300                       | 24.9                |

| 350                       | 21                  |

| 400                       | 18.2                |

| 450                       | 15.8                |

| 500                       | 14                  |

#### Synchronizing to an External Clock

The LT3753 internal oscillator can be synchronized to an external clock at the SYNC pin. SYNC pin high level should exceed 1.8V for at least 100ns and SYNC pin low level should fall below 0.6V for at least 100ns. The SYNC pin frequency should be set equal to or higher than the typical frequency programmed by the RT pin. An  $f_{SYNC}/f_{OSC}$  ratio of x (1.0 < x < 1.25) will reduce the externally programmed slope compensation by a factor of 1.2x. If required, the external resistor  $R_{ISLP}$  can be reprogrammed higher by a factor of 1.2x. (see Current Sensing and Programmable Slope Compensation).

The part injection locks the internal oscillator to every rising edge of the SYNC pin. If the SYNC input is removed at any time during normal operation the part will simply change switching frequency back to the oscillator frequency programmed by the  $R_{\text{\scriptsize T}}$  resistor. This injection lock method avoids the possible issues from a PLL method which can potentially cause a large drop in frequency if SYNC input is removed.

During soft-start the SYNC input is ignored until SS1 exceeds 2.2V. During soft-stop the SYNC input is completely ignored. If the SYNC input is to be used, recall that the programmable duty cycle clamp  $D_{VSEC}$  is dependent on the switching frequency of the part (see section Programming Duty Cycle Clamp).  $R_{IVSEC}$  should be reprogrammed by 1/x for an  $f_{SYNC}/f_{OSC}$  ratio of x.

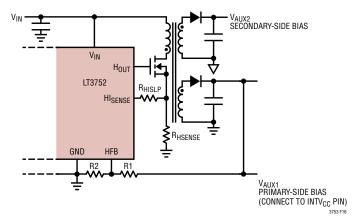

#### INTV<sub>CC</sub> Regulator Bypassing and Operation

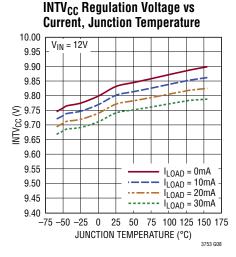

The INTV<sub>CC</sub> pin is the output of an internal linear regulator driven from V<sub>IN</sub> and provides a 10V supply for onboard gate drivers AOUT, SOUT and OUT. INTV<sub>CC</sub> should be bypassed with a  $4.7\mu F$  low ESR, X7R or X5R ceramic capacitor to power ground to ensure stability and to provide enough charge for the gate drivers.

The INTV $_{\text{CC}}$  regulator has a minimum 19mA output current limit. This current limit should be considered when choosing the switching frequency and capacitance loading on each gate driver. Average current load on the INTV $_{\text{CC}}$  pin for a single gate driver driving an external MOSFET is given as :

$I_{INTVCC} = f_{OSC} \cdot Q_G$

where:

f<sub>OSC</sub> = controller switching frequency

$Q_G$  = gate charge ( $V_{GS}$  = INT $V_{CC}$ )

While the INTV<sub>CC</sub> 19mA output current limit is sufficient for LT3753 applications, efficiency and internal power dissipation should also be considered. INTV<sub>CC</sub> can be externally overdriven by an auxiliary supply (see Generating Auxiliary Supplies in the Applications Information section) to improve efficiency, remove power dissipation from within the IC and provide more than 19mA output current capability. Any overdrive level should exceed the regulated INTV<sub>CC</sub> level but not exceed 16V.

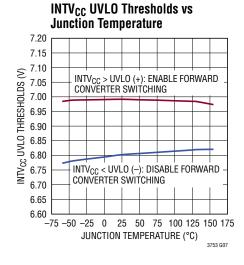

In the case of a short-circuit fault from INTV $_{CC}$  to ground, the IC reduces the INTV $_{CC}$  output current limit to typically 13mA. The INTV $_{CC}$  regulator has an undervoltage lockout rising threshold, UVLO(+), which prevents gate driver switching until INTV $_{CC}$  reaches 7V and maintains switching until INTV $_{CC}$  falls below a UVLO(–) threshold of 6.8V.

For V<sub>IN</sub> levels close to or below the INTV<sub>CC</sub> regulated level, the INTV<sub>CC</sub> linear regulator may enter dropout. The resulting lower INTV<sub>CC</sub> level will still allow gate driver switching as long as INTV<sub>CC</sub> remains above INTV<sub>CC</sub> UVLO(–) levels. See the Typical Performance Characteristics section for INTV<sub>CC</sub> performance vs V<sub>IN</sub> and load current.

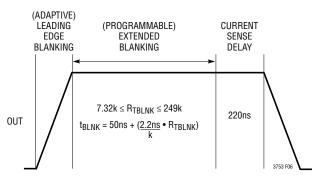

#### Adaptive Leading Edge Blanking Plus Programmable Extended Blanking

The LT3753 provides a  $\pm 2A$  gate driver at the OUT pin to control an external N-channel MOSFET for main power delivery in the forward converter (Figure 7). During gate rise time and sometime thereafter, noise can be generated in the current sensing resistor connected to the source of the MOSFET. This noise can potentially cause a false trip of sensing comparators resulting in early switch turn off and in some cases re-soft-start of the system. To prevent this, LT3753 provides adaptive leading edge blanking of both OC and  $I_{SENSEP}$  signals to allow a wide range of MOSFET  $I_{C}$  Ratings. In addition, a resistor  $I_{C}$  Ratings. In addition, a resistor  $I_{C}$  Ratings an extended blanking duration (Figure 6).

Figure 6. Adaptive Leading Edge Blanking Plus Programmable Extended Blanking

Figure 7. Current Sensing and Programmable Slope Compensation

Adaptive leading edge blanking occurs from the start of OUT rise and completes when OUT reaches within 1V of its maximum level. An extended blanking then occurs which is programmable using the R<sub>TBLNK</sub> resistor given by:

$$t_{BLNK} = 50 \text{ns} + \left(\frac{2.2 \text{ns}}{k} \cdot R_{TBLNK}\right),$$

$7.32k < R_{TBLNK} < 249k$

Adaptive leading edge blanking minimizes the value required for  $R_{TBLNK}$ . Increasing  $R_{TBLNK}$  further than required increases M1 minimum on time (Figure 7).

In addition, the critical volt-second clamp ( $D_{VSEC}$ ) is not blanked. Therefore, if  $D_{VSEC}$  decreases far enough (in soft start foldback and at maximum input voltage) M1 may turn off before blanking has completed. Since OC and  $I_{SENSEP}$  signals are only seen when M1 is on (and after blanking has completed),  $R_{TBLNK}$  value should be limited by:

$$(2.2ns/k)R_{TBLNK} < T_{VSEC(MIN)} - t_{ADAPTIVE} - 50ns$$

Rev. 0

where,

$T_{VSEC(MIN)} = 10^{9} (D_{VSEC(MAX)} / (fold.fosc))$

• (Input<sub>(MIN)</sub>/Input<sub>(MAX)</sub>)

fold = f<sub>OSC</sub> and D<sub>VSEC</sub> foldback ratio (for OUT pin)

$t_{ADAPTIVE} = OUT$  pin rise time to  $INTV_{CC} - 1V$

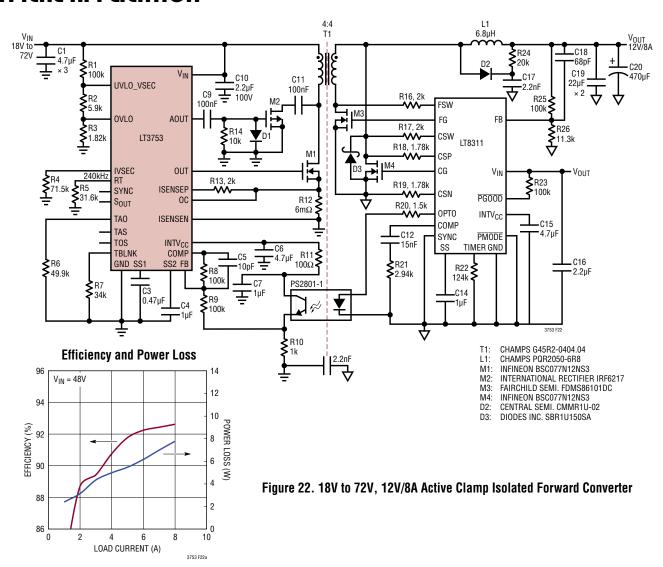

Example: For Figure 22 circuit,  $D_{VSEC(MAX)} = 0.77$ ,  $Input_{(MIN)/(MAX)} = 17.4V/74V$ , fold = 4,  $t_{ADAPTIVE} = 23$ ns and  $t_{OSC} = 240$ kHz,

$T_{VSEC(MIN)} = 10^9 (0.77/(4 \cdot 2.4 \cdot 10^5)) \cdot 17.4/74 = 188 \text{ns}$

$(2.2ns/1k)R_{TBI,NK} < 188 - 23 - 50$

R<sub>TBLNK</sub> < 52.5k (Actual Circuit Uses 34k)

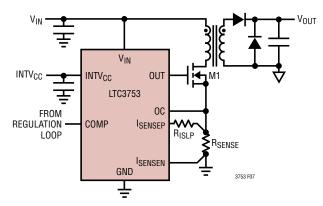

## **Current Sensing and Programmable Slope Compensation**

The LT3753 commands cycle-by-cycle peak current in the external switch and primary winding of the forward transformer by sensing voltage across a resistor connected in the source of the external n-channel MOSFET (Figure 7).

The sense voltage across  $R_{SENSE}$  is compared to a sense threshold at the  $I_{SENSEP}$  pin, controlled by COMP pin level. Two sense inputs,  $I_{SENSEP}$  and  $I_{SENSEN}$ , are provided to allow a Kelvin connection to  $R_{SENSE}$ . For operation in continuous mode and above 50% duty cycle, required slope compensation can be programmed by adding a resistor,  $R_{ISLP}$ , in series with the  $I_{SENSEP}$  pin. A ramped current always flows out of the  $I_{SENSE}$  pin. The current starts from 2 $\mu$ A at 0% duty cycle and linearly ramps to 33 $\mu$ A at 80% duty cycle. A good starting value for  $R_{ISLP}$  is 1.5 $k\Omega$  which gives a 41mV total drop in current comparator threshold at 65% duty cycle.

The COMP pin commands an  $I_{SENSEP}$  threshold between OmV and 220mV. The 220mV allows a large slope compensation voltage drop to exist in  $R_{ISLP}$  without effecting the programming of  $R_{SENSE}$  to set maximum operational currents in M1. An  $f_{SYNC}/f_{OSC}$  ratio of x (1.0 < x < 1.25) will reduce the externally programmed slope compensation by a factor of 1.2x. If required, the external resistor  $R_{ISLP}$  can be reprogrammed higher by a factor of 1.2x.

#### **Overcurrent: Hiccup Mode**

The LT3753 uses a precise 96mV sense threshold at the OC pin to detect excessive peak switch current (Figure 7). During an overload condition switching stops immediately and the SS1/SS2 pins are rapidly discharged. The absence of switching reduces the sense voltage at the OC pin, allowing SS1/SS2 pins to recharge and eventually attempt switching again. The part exists in this hiccup mode as long as the overcurrent condition exists. This protects the converter and reduces power dissipation in the components (see Hard Stop in the Applications Information section). The 96mV peak switch current threshold is independent of the voltage drop in  $R_{\rm ISI,P}$  used for slope compensation.

Output DC load current to trigger hiccup mode:

= I<sub>LOAD(OVERCURRENT)</sub>

$$= \left(\frac{N_{P}}{N_{S}} \bullet \frac{96mV}{R_{ISENSE}}\right) - \left(1/2 I_{RIPPLE(P-P)}\right)$$

where:

$N_P$  = forward transformer primary turns

$N_S$  = forward transformer secondary turns

$I_{RIPPLE(P-P)}$  = Output inductor peak-to-peak ripple current

R<sub>ISENSE</sub> should be programmed to allow maximum DC load current for the application plus enough margin during load transients to avoid overcurrent hiccup mode.

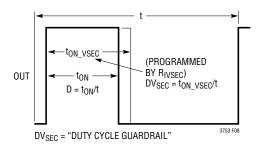

## Programming Maximum Duty Cycle Clamp: D<sub>VSEC</sub> (Volt-Second Clamp)

Unlike other converters which only provide a fixed maximum duty cycle clamp, the LT3753 provides an accurate programmable maximum duty cycle clamp ( $D_{VSEC}$ ) on the OUT pin which moves inversely with system input.  $D_{VSEC}$  provides a duty cycle guardrail to limit the volt-seconds-on product over the entire

natural duty cycle range (Figures 8 and 9). This limits the drain voltage required for complete transformer reset. A resistor  $R_{IVSEC}$  from the IVSEC pin to analog ground (Pin 18) programs  $D_{VSEC}$ .

D<sub>VSFC</sub> (OUT pin duty cycle clamp)

= 0.725 •

$$\frac{R_{IVSEC}}{51.1k}$$

•  $\frac{f_{OSC}}{300}$  •  $\frac{1.25}{UVLO_{VSEC}}$

where:

R<sub>IVSEC</sub> = programming resistor at IVSEC pin

$f_{OSC}$  = switching frequency (kHz)

UVLO\_V<sub>SEC</sub> = resistor divided system input voltage

$R_{IVSEC}$  can program any  $D_{VSEC}$  required at minimum system input.  $D_{VSEC}$  will then follow natural duty cycle as  $V_{IN}$  varies. Maximum programmable  $D_{VSEC}$  is typically 0.75 but may be further limited by the transformer design and voltage ratings of components connected to the drain of the primary side power MOSFET (SWP). See voltage calculations in the LO side and HI side active clamp topologies sections.

Figure 8. Volt-Second (D<sub>VSEC</sub>) Clamp

Figure 9. Programming D<sub>VSEC</sub>

If system input voltage falls below it's UVLO threshold the part will enter soft-stop with continued switching. The LT3753 includes an intelligent circuit which prevents  $D_{VSEC}$  from continuing to rise as system input voltage falls (see Soft-Stop). Without this, too large a  $D_{VSEC}$  would require extremely high reset voltages on the SWP node to properly reset the transformer. The UVLO\_V\_SEC pin maximum operational level is the lesser of  $V_{IN}-2V$  or 12.5V.

The LT3753 volt-second clamp architecture is superior to an external RC network connected from system input to trip an internal comparator threshold. The RC method suffers from external capacitor error, part-to-part mismatch between the RC time constant and the IC's switching period, the error of the internal comparator threshold and the nonlinearity of charging at low input voltages. The LT3753 uses the  $R_{IVSEC}$  resistor to define the charge current for an internal timer capacitor to set an OUT pin maximum on-time,  $t_{ON(VSEC)}$ . The voltage across  $R_{IVSEC}$  follows UVLO\_VSEC pin voltage (divided down from system input voltage). Hence,  $R_{IVSEC}$  current varies linearly with input supply. The LT3753 also trims out internal timing capacitor and comparator threshold errors to optimize part-to-part matching between  $t_{ON(VSEC)}$  and T.

## D<sub>VSEC</sub> Open Loop Control: No Opto-Coupler, Error Amplifier or Reference

The accuracy of the programmable volt-second clamp ( $D_{VSEC}$ ) safely controls  $V_{OUT}$  if open loop conditions exist such as no opto-coupler, error amplifier or reference on the secondary side.  $D_{VSEC}$  controls the output of the converter by controlling duty cycle inversely proportional to system input. If  $D_{VSEC}$  duty cycle guardrail is programmed X% above natural duty cycle,  $V_{OUT}$  will only increase by X% if a closed loop system breaks open. This volt-second clamp is operational over a 10:1 system input voltage range. See  $D_{VSEC}$  versus  $UVLO_{VSEC}$  pin voltage in the Typical Performance Characteristics section.

#### R<sub>IVSEC</sub>: Open Pin Detection Provides Safety

The LT3753 provides an open-detection safety feature for the  $R_{IVSEC}$  pin. If the  $R_{IVSEC}$  resistor goes open circuit the part immediately stops switching. This prevents the part from running without the volt-second clamp in place.

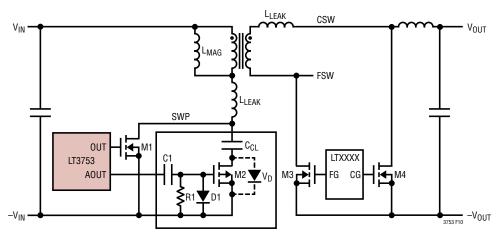

#### Transformer Reset: Active Clamp Technique

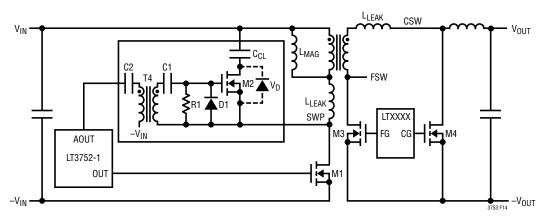

The LT3753 includes a  $\pm 0.4A$  gate driver at the AOUT pin to allow the use of an active clamp transformer reset technique (Figures 10, 14). The active clamp method improves efficiency and reduces voltage stress on the main power switch, M1. By switching in the active clamp capacitor only when needed, the capacitor does not lose its charge during M1 on-time. By allowing the active clamp capacitor,  $C_{CL}$ , to store the average voltage required to reset the transformer, the main power switch sees lower drain voltage.

In addition, the active clamp drain waveform on M1 (Figure 11) allows a self-driven architecture, whereby the drains of M3 and M4 drive the gates of M4 and M3 respectively, removing the need for a secondary-side synchronous MOSFET driver (Figure 21). In a self-driven architecture, the reset voltage level on M1,  $V_{OUT}$  level and duty cycle range (governed by system input range) must be considered to ensure the maximum  $V_{GS}$  rating of synchronous MOSFETs M3, M4 are not exceeded.

An imbalance of volt-seconds will cause magnetizing current to walk upwards or downwards until the active clamp capacitor is charged to the optimal voltage for proper transformer reset. The voltage rating of the capacitor will depend on whether the active clamp capacitor is actively switched to ground (Figure 10) or actively switched to system input (Figure 14). In an active clamp reset topology, volt-second balance requires:

$$V_{IN} \bullet D = (SWP - V_{IN}) \bullet (1 - D)$$

where:

$V_{IN}$  = Transformer input supply

$D = (V_{OUT}/V_{IN}) \cdot N =$ switch M1 duty cycle

$V_{OUT}$  = Output voltage (including the voltage drop contribution of M4 catch diode during M1 off)

$N = Transformer turns ratio = N_P/N_S$

SWP = M1 drain voltage

#### LO Side Active Clamp Topology (LT3753)

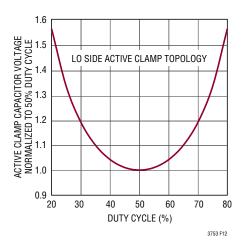

The steady-state active clamp capacitor voltage,  $V_{CCL}$ , required to reset the transformer in a LO side active clamp topology (Figure 10) can be approximated as the drain-to-source voltage ( $V_{DS}$ ) of switch M1, given by:

V<sub>CCL</sub> (LO side):

(a) Steady state:  $V_{CCL} = SWP = V_{DS}$

$$= \left(\frac{1}{1 - D}\right) \bullet V_{IN} = \frac{V_{IN}^2}{\left(V_{IN} - \left(V_{OUT} \bullet N\right)\right)}$$

#### (b) Transient:

During load transients, duty cycle and hence  $V_{CCL}$  may increase. Replace D with  $D_{VSEC}$  in the equation above to calculate transient  $V_{CCL}$  values. See the previous section Programming Duty Cycle Clamp— $D_{VSEC}$ . The  $D_{VSEC}$  guardrail can be programmed as close as 5% higher than D but may require a larger margin to improve transient response.

Figure 10. LO Side Active Clamp Topology

As shown in Figure 12, the maximum steady-state value for  $V_{CCL}$  may occur at minimum or maximum input voltage. Hence  $V_{CCL}$  should be calculated at both input voltage levels and the largest of the two calculations used. M1 drain should be rated for a voltage greater than the above steady-state  $V_{DS}$  calculation due to tolerances in duty cycle, load transients, voltage ripple on  $C_{CL}$  and leakage inductance spikes.  $C_{CL}$  should be rated higher due to the effect of voltage coefficient on capacitance value. A typical choice for  $C_{CL}$  is a good quality X7R capacitor. M2 should have a  $V_{DS}$  rating greater than  $V_{CCL}$  since the bottom plate of  $C_{CL}$  is  $-V_{CCL}$  during M1 on and M2 off. For high input voltage applications, the limited  $V_{DS}$  rating of available P-channel MOSFETs might require changing from a L0 side to HI side active clamp topology.

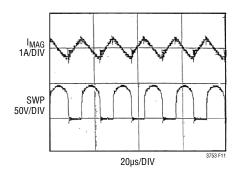

For the lo side active clamp topology in steady state, during M1 on time, magnetizing current ( $I_{MAG}$ ) increases from a negative value to a positive value (Figure 11). When M1 turns off, magnetizing current charges SWP until it reaches  $V_{CCL}$  plus the voltage drop of the M2 body diode. At this

Figure 11. Active Clamp Reset: Magnetizing Current and M1 Drain Voltage

Figure 12. LO Side V<sub>CCL</sub> vs Duty Cycle (Normalized to 50% Duty Cycle)

Figure 13. HI Side V<sub>CCL</sub> vs Duty Cycle (Normalized to 50% Duty Cycle)

Figure 14. HI Side Active Clamp Topology (Using LT3752-1)

moment the active clamp capacitor is passively switched in to ground (due to the forward conduction of M2 body diode) and the drain voltage increases at a slower rate due to the loading of  $C_{CL}$ . SWP above  $V_{IN}$  causes  $I_{MAG}$  to reduce from a positive value towards zero ( $dV_{SWP}/dT=0$ ). As  $I_{MAG}$  becomes negative it begins to discharge the SWP node. Switching in M2 before  $I_{MAG}$  reverses, actively connects the bottom plate of  $C_{CL}$  to ground and allows SWP to be discharged slowly. The resulting SWP waveform during M1 off-time appears as a square wave with a superimposed sinusoidal peak representing ripple voltage on  $C_{CL}$ .

The switch M2 experiences near zero voltage switching (ZVS) since only the body diode voltage drop appears across it at switch turn on.

#### HI Side Active Clamp Topology (LT3752-1)

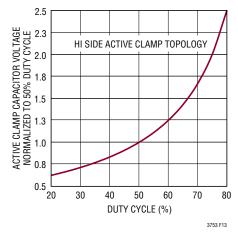

For high input voltage applications the  $V_{DS}$  rating of available P-channel MOSFETs might not be high enough to be used as the active clamp switch in the LO side active clamp topology (Figure 10). An N-channel approach using the HI side active clamp topology (Figure 14) should be used. (The LT3752-1 is ideal for the HI side active clamp topology). This topology requires a gate drive transformer or a simple gate drive opto-coupler to drive the N-channel MOSFET (M2) for switching in the active clamp capacitor from SWP to  $V_{IN}$ . The M1 drain voltage calculation is the same as in the LO side active clamp case and M1 should be rated in a similar manner. The voltage across the clamp capacitor in the HI side architecture, however, is lower by  $V_{IN}$  since it is referenced to  $V_{IN}$ .

The steady-state active clamp capacitor voltage  $V_{CCL}$  to reset the transformer in a HI side active clamp topology can be approximated by:

V<sub>CCL</sub> (HI side):

(a) Steady state:  $V_{CCL} = V_{RESET} = V_{DS} - V_{IN}$

$$= \left(\frac{\mathsf{D}}{\mathsf{1-D}}\right) \bullet \mathsf{V}_{\mathsf{IN}} = \mathsf{V}_{\mathsf{IN}} \bullet \mathsf{V}_{\mathsf{OUT}} \bullet \frac{\mathsf{N}}{\mathsf{V}_{\mathsf{IN}} - \left(\mathsf{V}_{\mathsf{OUT}} \bullet \mathsf{N}\right)}$$

(b) Transient:

During load transients, duty cycle and hence  $V_{CCL}$  may increase. Replace D with  $D_{VSEC}$  in the equation above to calculate transient  $V_{CCL}$  values.  $D_{VSEC}$  guardrail can be programmed as close as 6% higher than D but may require a larger margin to improve transient response. See the previous section Programming Duty Cycle Clamp— $D_{VSEC}$ .

$C_{CL}$  should be rated for a voltage higher than the above steady-state calculation due to tolerances in duty cycle, load transients, voltage ripple on  $C_{CL}$  and the effect of voltage coefficient on capacitance value. A typical choice for  $C_{CL}$  is a good quality (X7R) capacitor. When using a gate drive transformer to provide control of the active clamp switch (M2), the external components C1, C2, R1, D1 and T4 are required. T4 size will increase for lower programmed switching frequencies due to a minimum volt-second requirement. Alternatively, a simple gate driver opto-coupler can be used as a switch to control M2, for a smaller solution size.

#### **Active Clamp Capacitor Value and Voltage Ripple**

The active clamp capacitor value should be chosen based on the amount of voltage ripple which can be tolerated by components attached to SWP. Lower C<sub>CL</sub> values will create larger voltage ripple (increased drain voltage for the primary side power MOSFET) but will require less swing in magnetizing current to move the active clamp capacitor during duty cycle changes. Choosing too high a value for the active clamp capacitor (beyond what is needed to keep ripple voltage to an acceptable level) will require unnecessary additional flux swing during transient conditions. For systems with flux swing detection, too high a value for the active clamp capacitor will trigger the detection system early and degrade transient response.

Another factor to consider is the resonance between  $C_{CL}$  and the magnetizing inductance ( $L_{MAG}$ ) of the main transformer. An RC snubber ( $R_S$ ,  $C_S$ ) in parallel with  $C_{CL}$  will dampen

the sinusoidal ringing and limit the peak voltages at the primary side MOSFET drain during input/load transients. Check circuit performance to determine if the snubber is required. Component values can be approximated as:

$$C_{CL}$$

(active clamp capacitance) =  $\frac{10}{L_{MAG}} \cdot \left(\frac{(1-D_{MIN})}{2 \cdot \pi \cdot f_{OSC}}\right)^2$

where.

$$D_{MIN} = (V_{OUT}/V_{IN(MAX)}) \cdot N_P/N_S$$

and (if needed),

$C_S$  (snubber capacitance) = 6 •  $C_{CL}$

$R_S$  (snubber resistance) =  $(1/(1-D_{MAX})) \cdot \sqrt{(L_{MAG}/C_{CL})}$  where.

$$D_{MAX} = (V_{OUT}/V_{IN(MIN)}) \cdot N_P/N_S$$

Check the voltage ripple on SWP during steady-state operation.

C<sub>Cl</sub> voltage ripple can be estimated as:

$$V_{CCL(RIPPLE)} = V_{CCL} \cdot (1-D)^2/(8 \cdot C_{CL} \cdot L_{MAG} \cdot f_{OSC}^2)$$

where,

$$\mathsf{D} = (\mathsf{V}_\mathsf{OUT}/\mathsf{V}_\mathsf{IN}) \bullet (\mathsf{N}_\mathsf{P}/\mathsf{N}_\mathsf{S})$$

$V_{CCL} = V_{IN}/(1-D)$  (Lo side active clamp topology)

$V_{CCL} = D \cdot V_{IN}/(1-D)$  (Hi side active clamp topology)

Example : For  $V_{IN}$  = 36V,  $V_{OUT}$  = 12V,  $N_P/N_S$  = 2,  $V_{CCL}$  = 108V (Lo side active clamp topology),  $C_{CL}$  = 22nF,  $L_{MAG}$  = 100 $\mu$ H,  $f_{OSC}$  = 250kHz,  $V_{CCL(RIPPLE)}$  = 108(0.33)<sup>2</sup>/(8(22 • 10<sup>-9</sup>)(10<sup>-4</sup>)(2.5 • 10<sup>5</sup>)<sup>2</sup>) = 10.7V

The transformer is typically chosen to operate at a maximum flux density that is low enough to avoid excessive core losses. This also allows enough headroom during input and load transients to move the active clamp capacitor at a fast enough rate to keep up with duty cycle changes.

#### **Active Clamp MOSFET Selection**

The selection of active clamp MOSFET is determined by the maximum levels expected for the drain voltage and drain current. The active clamp switch (M2) in a either a lo side or hi side active clamp topology has the same BVdss requirements as the main N-channel power MOSFET. The current requirements are divided into two categories:

#### (A) Drain Current

This is typically less than the main N-channel power MOSFET because the active clamp MOSFET sees only magnetizing current, estimated as:

Peak

$$I_{MAG}$$

(steady state) = (1/2) • ( $N_P/N_S$ ) • ( $V_{OUT}/L_{MAG}$ ) • (1/ $f_{OSC}$ )

where.

L<sub>MAG</sub> = main transformer's magnetizing inductance

Example (LT3752) : For  $V_{OUT}$  =12V,  $N_P/N_S$  = 2,  $f_{OSC}$  = 250kHz and  $L_{MAG}$  = 100 $\mu$ H, Peak  $I_{MAG}$  = 0.48A.

This value should be doubled for safety margin due to variations in  $L_{MAG}$ ,  $f_{OSC}$  and transient conditions.

#### (B) Body Diode Current