# A 7-Bit Current DAC with SPI Interface

### FEATURES

ANALOG

±0.8% I<sub>DAC</sub> Positive Output Current Accuracy (Over Temp)

OWER BY

- ±1.5% I<sub>DAC</sub> Negative Output Current Accuracy (Over Temp)

- Input Voltage Range: 2.5V to 5.5V

- High Impedance at IDAC Output When Disabled

- Wide IDAC Operation Voltage (0.4V to 2.0V)

- 7-Bit Programmable DAC Output Current for DC/DC V<sub>OUT</sub> Control

- Wide Range IDAC Output Current: ±16µA to ±256µA

- Programmable Slew Rate: 500ns ~ 3ms per Bit

- Available in a 10-Lead (3mm × 2mm) DFN Package

### **APPLICATIONS**

- General Purpose Power Systems

- Telecom Systems

- Industrial Applications

### DESCRIPTION

The LTC<sup>®</sup>7106-1 is a precision, SPI controlled, bidirectional current digital-to-analog converter that adjusts the output voltage of any conventional V<sub>FB</sub> referenced regulator. The LTC7106-1 can work with the vast majority of power management controllers or regulators to enable digital control of the output voltage. Internal power-on reset circuitry keeps the DAC output current at zero (high impedance IDAC) until a valid write takes place.

Features include a range bit for easy interfacing to almost any impedance resistor divider, and an open-drain GPO output for controlling the Run or Enable pin of the DC/ DC regulator. For most applications, the current DAC error is significantly attenuated with proper design. See more detail about  $V_{OUT}$  accuracy in the Applications Information section of this data sheet. The LTC7106 shares the same current DAC, but is controlled by an I<sup>2</sup>C PMBus interface.

All registered trademarks and trademarks are the property of their respective owners.

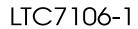

### TYPICAL APPLICATION

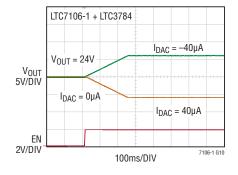

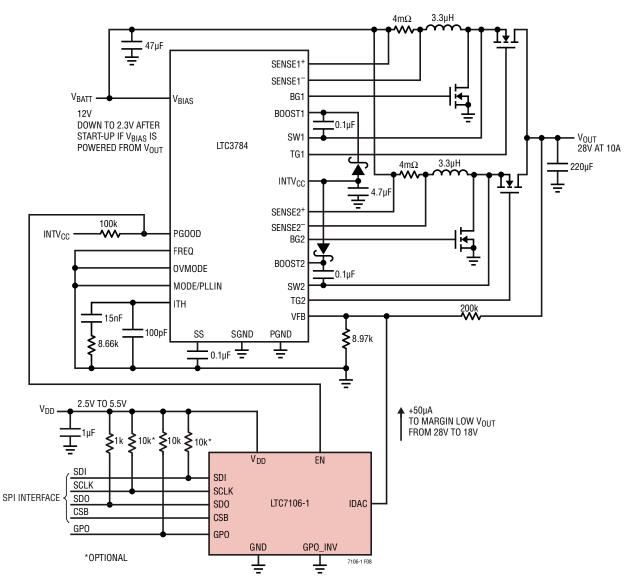

Using LTC7106-1 to Vary  $V_{\mbox{OUT}}$  of DC/DC Converter

#### Margin High and Margin Low

# ABSOLUTE MAXIMUM RATINGS

(Note 1)

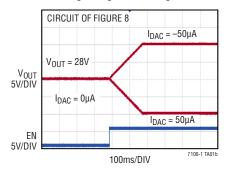

# PIN CONFIGURATION

# **ORDER INFORMATION**

| LEAD FREE FINISH  | TAPE AND REEL       | PART MARKING* | PACKAGE DESCRIPTION             | TEMPERATURE RANGE |

|-------------------|---------------------|---------------|---------------------------------|-------------------|

| LTC7106EDDB-1#PBF | LTC7106EDDB-1#TRPBF | LHCH          | 10-Lead (3mm × 2mm) Plastic DFN | -40°C to 125°C    |

| LTC7106IDDB-1#PBF | LTC7106IDDB-1#TRPBF | LHCH          | 10-Lead (3mm × 2mm) Plastic DFN | -40°C to 125°C    |

Consult ADI Marketing for parts specified with wider operating temperature ranges. \*The temperature grade is identified by a label on the shipping container. Tape and reel specifications. Some packages are available in 500 unit reels through designated sales channels with #TRMPBF suffix.

### **ELECTRICAL CHARACTERISTICS** The • denotes the specifications which apply over the specified operating

junction temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$  (Note 2),  $V_{DD} = 3.3V$ , unless otherwise specified.

| SYMBOL              | PARAMETER                      | CONDITIONS                                             |                                 |   | MIN    | ТҮР    | MAX    | UNITS |

|---------------------|--------------------------------|--------------------------------------------------------|---------------------------------|---|--------|--------|--------|-------|

| V <sub>DD</sub>     | Power Supply                   |                                                        |                                 |   | 2.5    |        | 5.5    | V     |

| Ι <sub>Q</sub>      | Supply Quiescent Current       | EN High                                                |                                 |   |        | 1.3    | 1.5    | mA    |

| V <sub>UVLO_R</sub> | Undervoltage Rising Threshold  | V <sub>DD</sub> Rising                                 |                                 |   | 2.35   |        | V      |       |

| V <sub>UVLO_F</sub> | Undervoltage Falling Threshold | V <sub>DD</sub> Falling                                |                                 |   | 2.15   |        | V      |       |

| V <sub>EN_R</sub>   | Enable Rising Threshold        | V <sub>EN</sub> Rising                                 |                                 |   |        | 1.35   | V      |       |

| V <sub>EN_F</sub>   | Enable Falling Threshold       | V <sub>EN</sub> Falling                                |                                 |   | 0.8    |        |        | V     |

| IDAC_OUT            |                                |                                                        |                                 |   |        |        |        |       |

| IDAC                | Accuracy                       | Full Scale Positive                                    | Range = Normal                  |   | 62.5   | 63.0   | 63.5   | μA    |

|                     |                                | $0.4 \le V_{IDAC} \le 2V$ (Note 3)                     | Range = Low                     | • | 15.50  | 15.75  | 16.00  | μA    |

|                     |                                |                                                        | Range = High                    | • | 246.7  | 252.0  | 255.3  | μA    |

|                     |                                | Full Scale Negative $0.4 \le V_{IDAC} \le 2V$ (Note 3) | Range = Normal<br>(0°C to 85°C) |   | -64.6  | -64.0  | -63.0  | μA    |

|                     |                                |                                                        | Range = Normal                  | • | -65    | -64.0  | -63    | μA    |

|                     |                                |                                                        | Range = Low                     | • | -16.4  | -16.0  | -15.6  | μA    |

|                     |                                |                                                        | Range = High                    | • | -263.5 | -256.0 | -249.5 | μA    |

| LSB                 |                                | $0.4 \le V_{IDAC} \le 2V$                              | Range = Normal                  |   |        | 1.0    |        | μA    |

|                     |                                |                                                        | Range = Low                     |   |        | 0.25   |        | μA    |

|                     |                                |                                                        | Range = High                    |   |        | 4.0    |        | μA    |

**ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes the specifications which apply over the specified operating junction temperature range, otherwise specifications are at T<sub>A</sub> = 25°C (Note 2), V<sub>DD</sub> = 3.3V, unless otherwise specified.

| INL                 |                             | $0.4 \le V_{IDAC} \le 2V$ | Range = Normal      | -1.0 |     | 1.0 | LSB |

|---------------------|-----------------------------|---------------------------|---------------------|------|-----|-----|-----|

|                     |                             |                           | Range = Low         | -1.5 |     | 1.5 | LSB |

|                     |                             |                           | Range = High        | -1.6 |     | 1.6 | LSB |

| DNL                 |                             | $0.4 \le V_{IDAC} \le 2V$ | Range = Normal      | -0.3 |     | 0.3 | LSB |

|                     |                             |                           | Range = Low         | -0.5 |     | 0.5 | LSB |

|                     |                             |                           | Range = High        | -0.8 |     | 0.8 | LSB |

| IHZ                 | High-Z Current              | $0.4 \le V_{IDAC} \le 2V$ | V <sub>EN</sub> = 0 |      |     | 20  | nA  |

| Digital Inpu        | t: SDI, SCLK, CSB, GPO_INV  |                           |                     |      |     |     |     |

| V <sub>IH</sub>     |                             |                           |                     |      |     | 1.4 | V   |

| V <sub>IL</sub>     |                             |                           |                     | 0.8  |     |     | V   |

| C <sub>PIN</sub>    | Input Capacitance           |                           |                     |      |     | 10  | pF  |

| Open-Drain          | Outputs: GPO, SDO           |                           |                     |      |     |     |     |

| SDO V <sub>OL</sub> | Output Low Voltage (Note 4) | I <sub>SINK</sub> = 3mA   |                     |      | 0.2 | 0.4 | V   |

| GPO V <sub>OL</sub> | Output Low Voltage          | I <sub>SINK</sub> = 2mA   |                     |      | 0.1 | 0.3 | V   |

### SPI INTERFACE TIMING CHARACTERISTICS

The • denotes the specifications which

apply over the specified operating junction temperature range, otherwise specifications are at T<sub>A</sub> = 25°C (Note 2), V<sub>DD</sub> = 3.3V, unless otherwise specified.

| SYMBOL           | PARAMETER              | CONDITIONS | MIN | ТҮР | MAX | UNITS |

|------------------|------------------------|------------|-----|-----|-----|-------|

| t <sub>CKH</sub> | SCLK High Time         |            | 95  | 100 | 105 | ns    |

| t <sub>CKL</sub> | SCLK Low Time          |            | 95  | 100 | 105 | ns    |

| t <sub>CSS</sub> | CSB Setup Time         |            | 15  |     |     | ns    |

| t <sub>CSH</sub> | CSB High Time          |            | 15  |     |     | ns    |

| t <sub>CS</sub>  | SDI to SCLK Setup Time |            | 15  |     |     | ns    |

| t <sub>CH</sub>  | SDI to SCLK Hold Time  |            | 20  |     |     | ns    |

| t <sub>DO</sub>  | SCLK to SDO Time       |            | 90  |     |     | ns    |

|                  | SCLK Duty Cycle        |            |     |     | ±5  | %     |

| f                | Frequency              |            |     |     | 5   | MHz   |

Note 1: Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

Note 2: The LTC7106-1 is tested under pulsed load conditions such that  $T_J \approx T_A$ . The LTC7106-1E is guaranteed to meet performance specifications from 0°C to 85°C. Specifications over the -40°C to 125°C operating junction temperature range are assured by design, characterization and correlation with statistical process controls. The LTC7106-11 is guaranteed over the –40°C to 125°C operating junction temperature range. High junction temperatures degrade operating lifetimes: operating lifetime is derated for junction temperatures greater than 125°C. Note that the maximum ambient temperature consistent with these specifications is determined by specific operating conditions in conjunction with board layout, the rated package thermal impedance and other environmental factors. T<sub>J</sub> is calculated from the ambient temperature  $T_A$  and power dissipation  $P_D$  according to the following formula:

$$T_J = T_A + (P_D \bullet 55^{\circ}C/W).$$

Note 3: IDAC is a bidirectional current DAC, controlled by 2's complementary logic. Under the setting of Range = Normal,  $I_{DAC}$  = 63µA for Code = 0111111 provides the maximum source current and  $I_{DAC} = -64\mu A$  for Code = 1000000 provides the maximum sink current. Max sink current generates the Highest  $V_{OUT}$ , while Max source current generates the lowest V<sub>OUT</sub>. See the Operation section for more details. Note 4:  $R_{DS(ON)}$  MAX is 125 $\Omega$

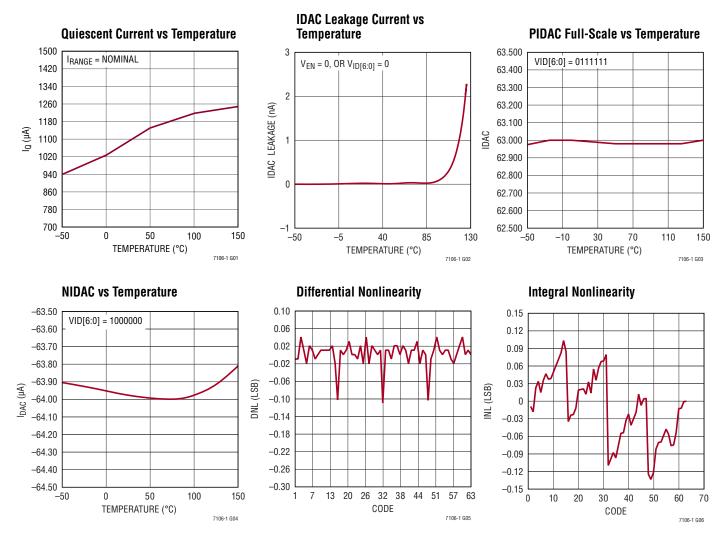

### TYPICAL PERFORMANCE CHARACTERISTICS

Range = Normal unless otherwise noted.

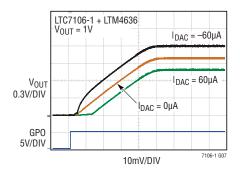

**Buck Start-Up with IDAC**

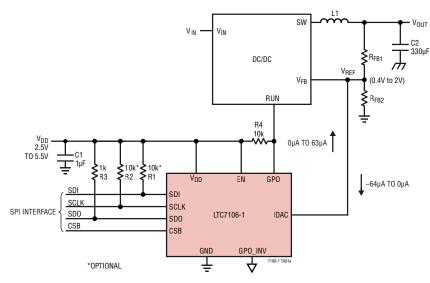

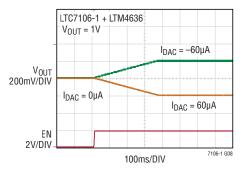

#### Margin High and Margin Low

$T_A = 25^{\circ}C, V_{DD} = 3.3V, V_{IDAC} = 1.0V,$

# **TYPICAL PERFORMANCE CHARACTERISTICS** $T_A = 25^{\circ}C$ , $V_{DD} = 3.3V$ , Range = Normal unless otherwise noted

otherwise noted.

Margin High and Margin Low

### PIN FUNCTIONS

$V_{DD}$  (Pin 3): Input Supply. Bypass this pin to GND with a capacitor (0.1µF to 1µF).

**IDAC (Pin 6):** Bidirectional Current DAC Output.

**EN (Pin 7):** DAC output current Enable. Current DAC output is in high impedance state when EN is Grounded. Do not leave EN floating.

SDI (Pin 1): Serial Bus Data Input.

SCLK (Pin 2): Serial Bus Clock Input.

**GPO (Pin 8):** Open-Drain Digital Output. A pull-up resistor to V<sub>DD</sub> is required.

**GPO\_INV (Pin 4):** Set to V<sub>DD</sub> to invert the GPO output pin. Otherwise set to GND.

GND (Pin 5): Ground.

**SDO (Pin 9):** Open-Drain Serial Bus Data Output. A pull-up resistor to V<sub>DD</sub> is required in the application.

CSB (Pin 10): Chip Select Active Low.

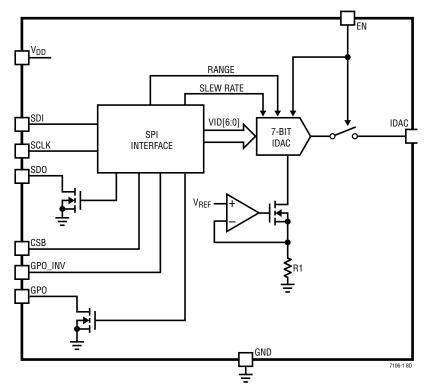

# **BLOCK DIAGRAM**

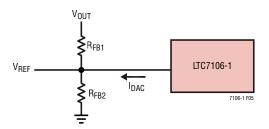

The LTC7106-1 is an SPI controlled 7-bit D/A converter current source. Through its SPI interface, the LTC7106-1 receives a 7-bit DAC code and converts this value to a bidirectional analog output current through the pin IDAC. By connecting IDAC to the feedback node of a voltage regulator,  $I_{DAC}$  can change the output voltage of the regulator with the equation:

$V_{OUT} = V_{REF} \bullet (1 + R_{FB1}/R_{FB2}) - I_{DAC} \bullet R_{FB1}$

where  $V_{REF}$  is the reference voltage of the voltage regulator.  $R_{FB1}$  and  $R_{FB2}$  are the resistor divider for the voltage regulator.  $I_{DAC}$  is the programmed bidirectional current shown in Table 2.

A typical application diagram is shown on the front page. Therefore, the traditional pure analog designed oriented PWM controller can be controlled by a digital interface.

This illustrates the flexibility of the LTC7106-1 providing a SPI interface to conventional analog DC/DC converters.

### (EN PIN)

The LTC7106-1's output is activated by the EN pin. It turns on/off the output device with threshold of 1.2V. When EN is low (<1.2V), IDAC is in high impedance (Hi-Z).

However, SPI interface as well as all the control circuits are still active when EN is low which means users can program the device and readback the internal register's value. The device will execute the commands of MFR\_ IOUT\_COMMAND, MFR\_IOUT\_MARGIN\_HIGH, MFR\_ IOUT\_MARGIN\_LOW after EN goes high.

### **SLEW RATE CONTROL**

To prevent abrupt changes in the D/A output current and subsequently the output voltage of the DC/DC regulator, an internal digital programmable slew rate control is included. The slew rate range can be programmed with a 6-bit register from  $0.5\mu$ s/step to 3.58ms/step with a default value of 3.58ms/step.

#### **CURRENT RANGE SETTING AND D/A PROGRAMMING**

The LTC7106-1 is a 7-bit bidirectional current DAC with a 1µA LSB as its default setting. The MSB determines the current direction. When MSB is 0, IDAC is sourcing current (reducing  $V_{OUT}$ ), which is positive current flowing out of the pin, and when MSB is 1,  $I_{DAC}$  is sinking current (increasing  $V_{OUT}$ ), which is negative current flowing into the pin. The LTC7106-1 also provides range high and range low options through its digital interface to change the LSB value to 4µA expanding the output current range and subsequently widening the programmable output voltage range. Alternately for higher resolution, the low range is provided with a LSB of 0.25µA. Users have additional flexibility of choosing the resistor divider ratio and resistor values to meet the output specification target. However, the design is most accurate using the nominal range which is the recommended setting. Table 1 lists the output current range and Table 2 lists the detailed DAC codes vs I<sub>DAC</sub> current.

#### Table 1. Output Current Range

| Range      | LSB (µA) | I <sub>MIN</sub> (μA) | Ι <sub>ΜΑΧ</sub> (μΑ) |  |  |

|------------|----------|-----------------------|-----------------------|--|--|

| Nominal    | 1        | -64                   | 63                    |  |  |

| Range High | 4        | -256                  | 252                   |  |  |

| Range Low  | 0.25     | -16                   | 15.75                 |  |  |

Table 2. IDAC Current and Corresponding DAC Codes

|     |     | DA  |     | DE  |     |     | lı      | dac (µA)      |              |     |     | DA  |     | DE  |     |     | l       | dac (µA)      |              |

|-----|-----|-----|-----|-----|-----|-----|---------|---------------|--------------|-----|-----|-----|-----|-----|-----|-----|---------|---------------|--------------|

| [6] | [5] | [4] | [3] | [2] | [1] | [0] | NOMINAL | RANGE<br>HIGH | RANGE<br>LOW | [6] | [5] | [4] | [3] | [2] | [1] | [0] | NOMINAL | RANGE<br>HIGH | RANGE<br>LOW |

| 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0       | 0             | 0            | 0   | 1   | 0   | 0   | 1   | 1   | 0   | 38      | 152           | 9.5          |

| 0   | 0   | 0   | 0   | 0   | 0   | 1   | 1       | 4             | 0.25         | 0   | 1   | 0   | 0   | 1   | 1   | 1   | 39      | 156           | 9.75         |

| 0   | 0   | 0   | 0   | 0   | 1   | 0   | 2       | 8             | 0.5          | 0   | 1   | 0   | 1   | 0   | 0   | 0   | 40      | 160           | 10           |

| 0   | 0   | 0   | 0   | 0   | 1   | 1   | 3       | 12            | 0.75         | 0   | 1   | 0   | 1   | 0   | 0   | 1   | 41      | 164           | 10.25        |

| 0   | 0   | 0   | 0   | 1   | 0   | 0   | 4       | 16            | 1            | 0   | 1   | 0   | 1   | 0   | 1   | 0   | 42      | 168           | 10.5         |

| 0   | 0   | 0   | 0   | 1   | 0   | 1   | 5       | 20            | 1.25         | 0   | 1   | 0   | 1   | 0   | 1   | 1   | 43      | 172           | 10.75        |

| 0   | 0   | 0   | 0   | 1   | 1   | 0   | 6       | 24            | 1.5          | 0   | 1   | 0   | 1   | 1   | 0   | 0   | 44      | 176           | 11           |

| 0   | 0   | 0   | 0   | 1   | 1   | 1   | 7       | 28            | 1.75         | 0   | 1   | 0   | 1   | 1   | 0   | 1   | 45      | 180           | 11.25        |

| 0   | 0   | 0   | 1   | 0   | 0   | 0   | 8       | 32            | 2            | 0   | 1   | 0   | 1   | 1   | 1   | 0   | 46      | 184           | 11.5         |

| 0   | 0   | 0   | 1   | 0   | 0   | 1   | 9       | 36            | 2.25         | 0   | 1   | 0   | 1   | 1   | 1   | 1   | 47      | 188           | 11.75        |

| 0   | 0   | 0   | 1   | 0   | 1   | 0   | 10      | 40            | 2.5          | 0   | 1   | 1   | 0   | 0   | 0   | 0   | 48      | 192           | 12           |

| 0   | 0   | 0   | 1   | 0   | 1   | 1   | 11      | 44            | 2.75         | 0   | 1   | 1   | 0   | 0   | 0   | 1   | 49      | 196           | 12.25        |

| 0   | 0   | 0   | 1   | 1   | 0   | 0   | 12      | 48            | 3            | 0   | 1   | 1   | 0   | 0   | 1   | 0   | 50      | 200           | 12.5         |

| 0   | 0   | 0   | 1   | 1   | 0   | 1   | 13      | 52            | 3.25         | 0   | 1   | 1   | 0   | 0   | 1   | 1   | 51      | 204           | 12.75        |

| 0   | 0   | 0   | 1   | 1   | 1   | 0   | 14      | 56            | 3.5          | 0   | 1   | 1   | 0   | 1   | 0   | 0   | 52      | 208           | 13           |

| 0   | 0   | 0   | 1   | 1   | 1   | 1   | 15      | 60            | 3.75         | 0   | 1   | 1   | 0   | 1   | 0   | 1   | 53      | 212           | 13.25        |

| 0   | 0   | 1   | 0   | 0   | 0   | 0   | 16      | 64            | 4            | 0   | 1   | 1   | 0   | 1   | 1   | 0   | 54      | 216           | 13.5         |

| 0   | 0   | 1   | 0   | 0   | 0   | 1   | 17      | 68            | 4.25         | 0   | 1   | 1   | 0   | 1   | 1   | 1   | 55      | 220           | 13.75        |

| 0   | 0   | 1   | 0   | 0   | 1   | 0   | 18      | 72            | 4.5          | 0   | 1   | 1   | 1   | 0   | 0   | 0   | 56      | 224           | 14           |

| 0   | 0   | 1   | 0   | 0   | 1   | 1   | 19      | 76            | 4.75         | 0   | 1   | 1   | 1   | 0   | 0   | 1   | 57      | 228           | 14.25        |

| 0   | 0   | 1   | 0   | 1   | 0   | 0   | 20      | 80            | 5            | 0   | 1   | 1   | 1   | 0   | 1   | 0   | 58      | 232           | 14.5         |

| 0   | 0   | 1   | 0   | 1   | 0   | 1   | 21      | 84            | 5.25         | 0   | 1   | 1   | 1   | 0   | 1   | 1   | 59      | 236           | 14.75        |

| 0   | 0   | 1   | 0   | 1   | 1   | 0   | 22      | 88            | 5.5          | 0   | 1   | 1   | 1   | 1   | 0   | 0   | 60      | 240           | 15           |

| 0   | 0   | 1   | 0   | 1   | 1   | 1   | 23      | 92            | 5.75         | 0   | 1   | 1   | 1   | 1   | 0   | 1   | 61      | 244           | 15.25        |

| 0   | 0   | 1   | 1   | 0   | 0   | 0   | 24      | 96            | 6            | 0   | 1   | 1   | 1   | 1   | 1   | 0   | 62      | 248           | 15.5         |

| 0   | 0   | 1   | 1   | 0   | 0   | 1   | 25      | 100           | 6.25         | 0   | 1   | 1   | 1   | 1   | 1   | 1   | 63      | 252           | 15.75        |

| 0   | 0   | 1   | 1   | 0   | 1   | 0   | 26      | 104           | 6.5          | 1   | 0   | 0   | 0   | 0   | 0   | 0   | -64     | -256          | -16          |

| 0   | 0   | 1   | 1   | 0   | 1   | 1   | 27      | 108           | 6.75         | 1   | 0   | 0   | 0   | 0   | 0   | 1   | -63     | -252          | -15.75       |

| 0   | 0   | 1   | 1   | 1   | 0   | 0   | 28      | 112           | 7            | 1   | 0   | 0   | 0   | 0   | 1   | 0   | -62     | -248          | -15.5        |

| 0   | 0   | 1   | 1   | 1   | 0   | 1   | 29      | 116           | 7.25         | 1   | 0   | 0   | 0   | 0   | 1   | 1   | -61     | -244          | -15.25       |

| 0   | 0   | 1   | 1   | 1   | 1   | 0   | 30      | 120           | 7.5          | 1   | 0   | 0   | 0   | 1   | 0   | 0   | -60     | -240          | -15          |

| 0   | 0   | 1   | 1   | 1   | 1   | 1   | 31      | 124           | 7.75         | 1   | 0   | 0   | 0   | 1   | 0   | 1   | -59     | -236          | -14.75       |

| 0   | 1   | 0   | 0   | 0   | 0   | 0   | 32      | 128           | 8            | 1   | 0   | 0   | 0   | 1   | 1   | 0   | -58     | -232          | -14.5        |

| 0   | 1   | 0   | 0   | 0   | 0   | 1   | 33      | 132           | 8.25         | 1   | 0   | 0   | 0   | 1   | 1   | 1   | -57     | -228          | -14.25       |

| 0   | 1   | 0   | 0   | 0   | 1   | 0   | 34      | 136           | 8.5          | 1   | 0   | 0   | 1   | 0   | 0   | 0   | -56     | -224          | -14          |

| 0   | 1   | 0   | 0   | 0   | 1   | 1   | 35      | 140           | 8.75         | 1   | 0   | 0   | 1   | 0   | 0   | 1   | -55     | -220          | -13.75       |

| 0   | 1   | 0   | 0   | 1   | 0   | 0   | 36      | 144           | 9            | 1   | 0   | 0   | 1   | 0   | 1   | 0   | -54     | -216          | -13.5        |

| 0   | 1   | 0   | 0   | 1   | 0   | 1   | 37      | 148           | 9.25         | 1   | 0   | 0   | 1   | 0   | 1   | 1   | -53     | -212          | -13.25       |

Table 2. IDAC Current and Corresponding DAC Codes (Continued)

|     |     | DA  | AC COI | DE  |     |     | ار      | DAC (µA)      |              |

|-----|-----|-----|--------|-----|-----|-----|---------|---------------|--------------|

| [6] | [5] | [4] | [3]    | [2] | [1] | [0] | NOMINAL | RANGE<br>High | RANGE<br>Low |

| 1   | 0   | 0   | 1      | 1   | 0   | 0   | -52     | -208          | -13          |

| 1   | 0   | 0   | 1      | 1   | 0   | 1   | -51     | -204          | -12.75       |

| 1   | 0   | 0   | 1      | 1   | 1   | 0   | -50     | -200          | -12.5        |

| 1   | 0   | 0   | 1      | 1   | 1   | 1   | -49     | -196          | -12.25       |

| 1   | 0   | 1   | 0      | 0   | 0   | 0   | -48     | -192          | -12          |

| 1   | 0   | 1   | 0      | 0   | 0   | 1   | -47     | -188          | -11.75       |

| 1   | 0   | 1   | 0      | 0   | 1   | 0   | -46     | -184          | -11.5        |

| 1   | 0   | 1   | 0      | 0   | 1   | 1   | -45     | -180          | -11.25       |

| 1   | 0   | 1   | 0      | 1   | 0   | 0   | -44     | -176          | -11          |

| 1   | 0   | 1   | 0      | 1   | 0   | 1   | -43     | -172          | -10.75       |

| 1   | 0   | 1   | 0      | 1   | 1   | 0   | -42     | -168          | -10.5        |

| 1   | 0   | 1   | 0      | 1   | 1   | 1   | -41     | -164          | -10.25       |

| 1   | 0   | 1   | 1      | 0   | 0   | 0   | -40     | -160          | -10          |

| 1   | 0   | 1   | 1      | 0   | 0   | 1   | -39     | -156          | -9.75        |

| 1   | 0   | 1   | 1      | 0   | 1   | 0   | -38     | -152          | -9.5         |

| 1   | 0   | 1   | 1      | 0   | 1   | 1   | -37     | -148          | -9.25        |

| 1   | 0   | 1   | 1      | 1   | 0   | 0   | -36     | -144          | -9           |

| 1   | 0   | 1   | 1      | 1   | 0   | 1   | -35     | -140          | -8.75        |

| 1   | 0   | 1   | 1      | 1   | 1   | 0   | -34     | -136          | -8.5         |

| 1   | 0   | 1   | 1      | 1   | 1   | 1   | -33     | -132          | -8.25        |

| 1   | 1   | 0   | 0      | 0   | 0   | 0   | -32     | -128          | -8           |

| 1   | 1   | 0   | 0      | 0   | 0   | 1   | -31     | -124          | -7.75        |

| 1   | 1   | 0   | 0      | 0   | 1   | 0   | -30     | -120          | -7.5         |

| 1   | 1   | 0   | 0      | 0   | 1   | 1   | -29     | -116          | -7.25        |

| 1   | 1   | 0   | 0      | 1   | 0   | 0   | -28     | -112          | -7           |

| 1   | 1   | 0   | 0      | 1   | 0   | 1   | -27     | -108          | -6.75        |

|     |     | DA  |     | DE  |     |     | I <sub>DAC</sub> (μA) |               |              |  |  |

|-----|-----|-----|-----|-----|-----|-----|-----------------------|---------------|--------------|--|--|

| [6] | [5] | [4] | [3] | [2] | [1] | [0] | NOMINAL               | RANGE<br>High | RANGE<br>Low |  |  |

| 1   | 1   | 0   | 0   | 1   | 1   | 0   | -26                   | -104          | -6.5         |  |  |

| 1   | 1   | 0   | 0   | 1   | 1   | 1   | -25                   | -100          | -6.25        |  |  |

| 1   | 1   | 0   | 1   | 0   | 0   | 0   | -24                   | -96           | -6           |  |  |

| 1   | 1   | 0   | 1   | 0   | 0   | 1   | -23                   | -92           | -5.75        |  |  |

| 1   | 1   | 0   | 1   | 0   | 1   | 0   | -22                   | -88           | -5.5         |  |  |

| 1   | 1   | 0   | 1   | 0   | 1   | 1   | -21                   | -84           | -5.25        |  |  |

| 1   | 1   | 0   | 1   | 1   | 0   | 0   | -20                   | -80           | -5           |  |  |

| 1   | 1   | 0   | 1   | 1   | 0   | 1   | -19                   | -76           | -4.75        |  |  |

| 1   | 1   | 0   | 1   | 1   | 1   | 0   | -18                   | -72           | -4.5         |  |  |

| 1   | 1   | 0   | 1   | 1   | 1   | 1   | -17                   | -68           | -4.25        |  |  |

| 1   | 1   | 1   | 0   | 0   | 0   | 0   | -16                   | -64           | -4           |  |  |

| 1   | 1   | 1   | 0   | 0   | 0   | 1   | -15                   | -60           | -3.75        |  |  |

| 1   | 1   | 1   | 0   | 0   | 1   | 0   | -14                   | -56           | -3.5         |  |  |

| 1   | 1   | 1   | 0   | 0   | 1   | 1   | -13                   | -52           | -3.25        |  |  |

| 1   | 1   | 1   | 0   | 1   | 0   | 0   | -12                   | -48           | -3           |  |  |

| 1   | 1   | 1   | 0   | 1   | 0   | 1   | -11                   | -44           | -2.75        |  |  |

| 1   | 1   | 1   | 0   | 1   | 1   | 0   | -10                   | -40           | -2.5         |  |  |

| 1   | 1   | 1   | 0   | 1   | 1   | 1   | -9                    | -36           | -2.25        |  |  |

| 1   | 1   | 1   | 1   | 0   | 0   | 0   | -8                    | -32           | -2           |  |  |

| 1   | 1   | 1   | 1   | 0   | 0   | 1   | -7                    | -28           | -1.75        |  |  |

| 1   | 1   | 1   | 1   | 0   | 1   | 0   | -6                    | -24           | -1.5         |  |  |

| 1   | 1   | 1   | 1   | 0   | 1   | 1   | -5                    | -20           | -1.25        |  |  |

| 1   | 1   | 1   | 1   | 1   | 0   | 0   | -4                    | -16           | -1           |  |  |

| 1   | 1   | 1   | 1   | 1   | 0   | 1   | -3                    | -12           | -0.75        |  |  |

| 1   | 1   | 1   | 1   | 1   | 1   | 0   | -2                    | -8            | -0.5         |  |  |

| 1   | 1   | 1   | 1   | 1   | 1   | 1   | -1                    | -4            | -0.25        |  |  |

9

### GPO

GPO is a general purpose open-drain output pin, which can be set by SPI command. It is designed to turn on/ off the DC/DC regulator by connecting GPO to the RUN pin of the regulator. Once GPO is set high, it stays high even if the EN pin goes low as long as the device is not power cycled.

### SPI SERIAL PORT

The LTC7106-1 SPI-compatible serial port provides chip control.

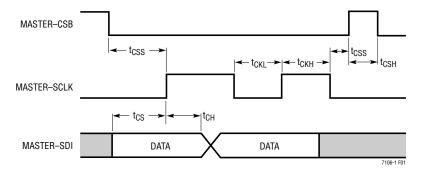

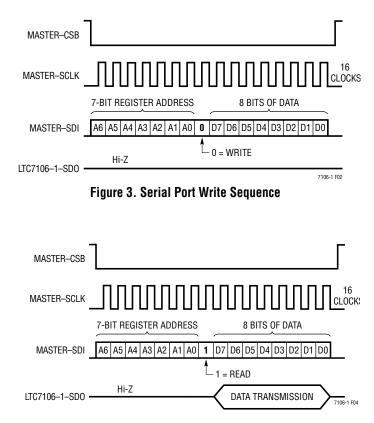

#### **Communication Sequence**

The serial bus is comprised of chip select active low (CSB), serial clock (SCLK), serial data input (SDI), serial data output (SDO) signals. Data transfers to the LTC7106-1 are

accomplished by the serial bus master device first taking CSB LOW, which enables the LTC7106-1's serial port. Input data applied on SDI is clocked on the rising edge of SCLK, with most significant bits transferred first. The communication burst is terminated by the serial bus master device returning CSB HIGH. See Figure 1 for details.

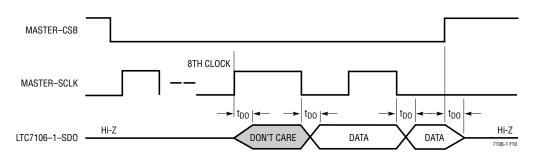

Data is read from the part during a communication burst using SDO. Read back may be multidrop (more than one LTC7106-1 connected in parallel on the serial bus), as SDO is set to a high impedance (Hi-Z) when CSB is HIGH or when data is not being read from the part.

#### **SINGLE BYTE TRANSFERS**

All data bursts are comprised of at least two bytes. The seven most significant bits (MSB) of the first byte are the register address, with a least significant bit (LSB) of 1 indicating a read from the part, and an LSB of 0 indicating

Figure 1. Serial Port Write Timing Diagram

Figure 2. Serial Port Read Timing Diagram

a write to the part. The subsequent byte, or bytes, is data from/to the specified register address. See Figure 3 for an example of a detailed write sequence, and Figure 4 for a read sequence. To terminate the first communication burst, CSB is taken HIGH.

Figure 4. Serial Port Read Sequence

# **REGISTER COMMAND DETAILS**

#### Table 3. Supported SPI Commands

| SPI CMD CODE<br>(7 BITS) | COMMAND NAME         | R/W TYPE | DATA<br>Bytes | DESCRIPTION                                                                                       |

|--------------------------|----------------------|----------|---------------|---------------------------------------------------------------------------------------------------|

| 0x01                     | OPERATION            | R/W      | 1             | Default is On: [7:0] = 0x80                                                                       |

| 0x38                     | STATUS_BYTE          | R/W      | 1             | Read Fault Status: CML, write 1 to reset                                                          |

| 0x62                     | MFR_CHIP_CTRL        | R/W      | 1             | [7:1] – Reserved, [0] = GPO enable                                                                |

| 0x64                     | MFR_DAC_CTRL         | R/W      | 1             | [7:6] = Current Range: 0.25μΑ, 1μΑ, 4μΑ<br>[5:0] = DAC Slew Rate Control: 0.5μs to 3580μs         |

| 0x65                     | MFR_IOUT_MARGIN_HIGH | R/W      | 1             | Same format as MFR_IOUT_COMMAND                                                                   |

| 0x66                     | MFR_IOUT_MAX         | R/W      | 1             | Clamped value that IDAC value cannot exceed<br>Default 7-bit value of 0x00 = cannot sink current  |

| 0x68                     | MFR_IOUT_COMMAND     | R/W      | 1             | I <sub>OUT</sub> Margining Command (2's comp)<br>[5:0] IDAC value, source: [6] = 0, sink: [6] = 1 |

| 0x6D                     | MFR_IOUT_MARGIN_LOW  | R/W      | 1             | Same format as MFR_IOUT_COMMAND                                                                   |

| 0x7D                     | MFR_RESET            | Write    | 1             | Reset to Power-On State (except for MFR_DAC_CTRL)<br>Write data is ignored                        |

#### MFR\_IOUT\_COMMAND

DAC output current command that is formatted as a 7-bit 2's complement value. When the operation register is set to 0x80, DAC takes the value stored in this register. Setting bit[6] to 0 sources the current from the IC and bit[6] to 1 sinks the current into the IC. Default value for this register is 0x00. The valid range of values are from 0x40 to 0x3F.

Do not attempt to write values outside of this range or undesired behavior may result.

#### MFR\_IOUT\_MARGIN\_HIGH

DAC margining register with the same format and rules as MFR\_IOUT\_COMMAND. The DAC value will take the value stored in this register when the operation register is set to margin high, 0xA8.

### MFR\_IOUT\_MARGIN\_LOW

DAC margining register with the same format and rules as MFR\_IOUT\_COMMAND. The DAC value will take the value stored in this register when the operation register is set to margin low, 0x98.

#### MFR\_IOUT\_MAX

Clamping value that DAC cannot exceed. The format is a 7-bit 2's complement value, the same as the margin registers. Therefore, the DAC value cannot be a smaller 2's complement value than what is stored in this register.

The 7-bit default value is 0x00 = cannot sink current.  $I_{\text{OUT}}$  cannot be set to a higher value unless this value is changed to a negative number, bit [7] = 1.

Setting this register to 0x40 allows the LTC7106-1 to sink the maximum current with no clamping.

# **REGISTER COMMAND DETAILS**

### MFR\_CHIP\_CTRL

This register is for general chip control and status. Please refer to Table 6 for each bit description.

### Bits Description

- [7:1] Reserved

- [0] GPO, General Purpose Output

0 = GPO Pulls Open Drain to GND

1 = Hi-Z on GPO

### MFR\_DAC\_CTRL

8-bit register to control the IDAC LSB current value and the timer count for the slew rate control. Default value = 0x40.

### Bits Description

[7:6] Selector Range for IDAC Step:

b'00 = 0.25µA/Step, Range Low

b'01 = 1.0µA/Step, Nominal

b'10 = 4.0µA/Step, Range High

- b'11 = Reserved

- [5:0] Selector for Time in µs/Step

Default Value 0x00 = Max = 3584µs/Step

See Table 4 for Allowable Values

Only a power cycle, POR, will reset this register to prevent unwanted immediate current changes in IDAC. MFR\_RESET will not reset this register.

In addition, IDAC must be at 0x00 to change the current range selector to prevent unwanted large swings in IDAC current. The time step selector, bits [5:0], can be changed at any time.

| Slew Rate Timer Clock (µs/Step) |        |        |       |        |         |  |  |  |  |

|---------------------------------|--------|--------|-------|--------|---------|--|--|--|--|

| [5:0]                           |        | [5:0]  |       | [5:0   | ]       |  |  |  |  |

| 000000                          | = 3584 | 010000 | = 16  | 100000 | = 256   |  |  |  |  |

| 000001                          | = 0.5  | 010001 | = 20  | 100001 | = 320   |  |  |  |  |

| 000010                          | = 1.0  | 010010 | = 24  | 100010 | = 384   |  |  |  |  |

| 000011                          | = 1.5  | 010011 | = 28  | 100011 | = 448   |  |  |  |  |

| 000100                          | = 2.0  | 010100 | = 32  | 100100 | = 512   |  |  |  |  |

| 000101                          | = 2.5  | 010101 | = 40  | 100101 | = 640   |  |  |  |  |

| 000110                          | = 3.0  | 010110 | = 48  | 100110 | = 768   |  |  |  |  |

| 000111                          | = 3.5  | 010111 | = 56  | 100111 | = 896   |  |  |  |  |

| 001000                          | = 4.0  | 011000 | = 64  | 101000 | = 1280* |  |  |  |  |

| 001001                          | = 5.0  | 011001 | = 80  | 101001 | = 1280  |  |  |  |  |

| 001010                          | = 6.0  | 011010 | = 96  | 101010 | = 1536  |  |  |  |  |

| 001011                          | = 7.0  | 011011 | = 112 | 101011 | = 1792  |  |  |  |  |

| 001100                          | = 8.0  | 011100 | = 128 | 101100 | = 2560* |  |  |  |  |

| 001101                          | = 10   | 011101 | = 160 | 101101 | = 2560  |  |  |  |  |

| 001110                          | = 12   | 011110 | = 192 | 101110 | = 3584* |  |  |  |  |

| 001111                          | = 14   | 011111 | = 224 | 101111 | = 3584  |  |  |  |  |

| *                               |        |        |       |        |         |  |  |  |  |

\* Duplicate Encoding

# **REGISTER COMMAND DETAILS**

### MFR\_RESET

This command provides a means by which the user can perform a reset of the LTC7106-1. All latched faults and register contents will be reset to a power-on condition by this command.  $V_{OUT}$  will remain in regulation but may change due to the reset of the margin registers.

This is a write-only command. The data byte is ignored.

### **OPERATION**

The OPERATION command is used to turn the unit on/off and for margining the output voltage.

The ON bit is automatically reset to ON after a master shutdown (EN), power cycle, or MFR\_RESET command.

The MARGIN\_LOW/HIGH bits command the I<sub>OUT</sub> reference to the offset value stored in either the MFR\_IOUT\_MARGIN\_HIGH or MFR\_IOUT\_MARGIN\_LOW.

This command has one data byte. It will accept one or two but ignores the second byte.

| Table 5. Supported | <b>OPERATION Command</b> | Register Values |

|--------------------|--------------------------|-----------------|

|                    | Of Elination Communia    | nogiotor vuluoo |

|                      | U     |  |

|----------------------|-------|--|

| ACTION               | VALUE |  |

| Turn Off Immediately | 0x00  |  |

| Turn On              | 0x80  |  |

| Margin Low           | 0x98  |  |

| Margin High          | 0xA8  |  |

### STATUS\_BYTE

The STATUS\_BYTE command returns a byte of information with a summary of the unit's fault condition.

See Table 6 for a list of the status bits that are supported and the conditions in which each bit is set.

Writing a "1" to a particular bit in the status byte will attempt to reset that fault in the status byte. If the fault is still present, the status byte bit will rmain asserted.

#### Table 6. Status Byte Bit Descriptions and Conditions

| BIT     | DESCRIPTION                        | CONDITION                      | CLEARABLE BY WRITING '1' TO BIT? |

|---------|------------------------------------|--------------------------------|----------------------------------|

| 0 (LSB) | None of the Above                  | MFR_VOUT_MAX Register Exceeded | Yes                              |

| 1       | Communication Failure              | Not Implemented                |                                  |

| 2       | Temperature Fault                  | Not Implemented                |                                  |

| 3       | V <sub>IN</sub> Undervoltage Fault | Not Implemented                |                                  |

| 4       | Output Overcurrent Fault           | Not Implemented                |                                  |

| 5       | Output Overvoltage Fault           | Not Implemented                |                                  |

| 6       | OFF                                | Not Implemented                |                                  |

| 7       | Busy                               | Not Implemented                |                                  |

### IDAC ACCURACY

The LTC7106-1 provides three ranges of  $I_{DAC}$  output current. However, only nominal range (LSB =  $\pm 1\mu$ A) is optimized with the highest accuracy. It is recommended that users design the resistor divider using the nominal range of the IDAC setting.

### TWO'S COMPLEMENTARY CODE

VID [6:0] of the LTC7106-1 is in the format of two's complementary. From Table 2, it is easy to program the register once the desired output current is known. For example, if output current is  $20\mu$ A, then set VID [6:0] = 0010100. If the output current is  $-20\mu$ A, then set VID [6:0] = 1101100 for the nominal I<sub>DAC</sub> setting.

### V<sub>OUT</sub> ACCURACY

When  $I_{DAC} = 0$ , define:

$$V_{OUT0} = V_{REF} \left[ 1 + \frac{R_{FB1}}{R_{FB2}} \right]$$

(1)

Referring to Figure 5, the output voltage is set according to:

$$V_{OUT} = V_{REF} \left[ 1 + \frac{R_{FB1}}{R_{FB2}} \right] - I_{DAC} \bullet R_{FB1}$$

(2)

Figure 5. Setting the Output Voltage Using the LTC7106-1

Define  $\Delta V_{OUT}$  as the  $V_{OUT}$  error caused by the  $I_{DAC}$  error  $\Delta I_{DAC}$ , then we can derive the following equation from equation (1) and (2):

$$\frac{\Delta V_{OUT}}{V_{OUT}} = \left(\frac{\Delta I_{DAC} / I_{DAC}}{Ratio - 1}\right)$$

(3)

Where:

$$Ratio = \frac{V_{OUTO}}{I_{DAC} \bullet R_{FB1}}$$

(4)

It is clear that when Ratio < 0 or Ratio  $\geq$  2, the  $V_{OUT}$  error can be attenuated from the  $I_{DAC}$  error:

$$\left|\frac{\Delta V_{OUT}}{V_{OUT}}\right| \le \left|\frac{\Delta I_{DAC}}{I_{DAC}}\right|$$

(5)

In the case of margin high,  $I_{DAC}$  < 0 so Ratio < 0. Therefore, the  $V_{OUT}$  error is always smaller than the  $I_{DAC}$  error by a factor of:

$$\frac{V_{OUTO}}{I_{DAC} \bullet R_{FB1}} - 1$$

(6)

In the case of margin low,  $I_{DAC}$  > 0. So the  $V_{OUT}$  error will only be attenuated when:

$$Ratio = \frac{V_{OUTO}}{I_{DAC} \bullet R_{FB1}} > 2$$

or  $I_{DAC} \bullet R_{FB1} < \frac{V_{OUTO}}{2}$  (7)

In other words, as long as  $V_{OUT}$  is margining low within 50% of the  $V_{OUT}$  default value,  $V_{OUT0}$ , the  $V_{OUT}$  error won't be larger than the  $I_{DAC}$  error.

### **DESIGN EXAMPLES**

The LTC7106-1 can work with almost all the power management controllers or regulators. Figure 6, Figure 7 and Figure 8 show three design examples using the LTC7106-1 to control the output voltage with a monolithic buck regulator, an  $\mu$ Module<sup>®</sup> and a boost controller.

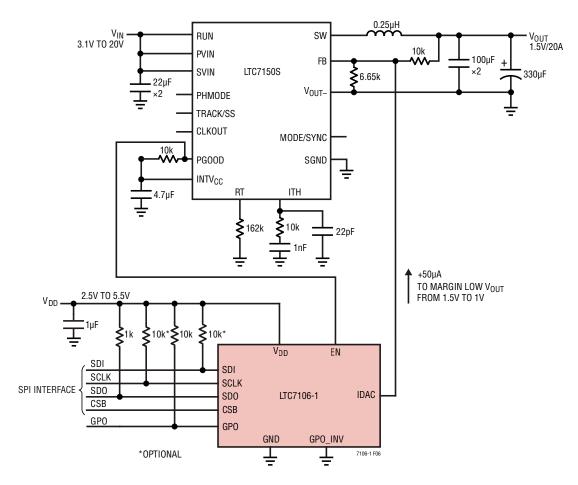

#### Case One

Assume that the LTC7150S, a monolithic buck regulator, provides a 1.5V output and requires to margin low  $V_{OUT}$  from 1.5V to 1.0V (see Figure 6). The  $V_{FB}$  is 0.6V and the voltage dividers are external. In order to achieve the best accuracy of the LTC7106-1, it is recommended to design  $I_{DAC}$  in nominal range. Also within certain current range (nominal, high or low), the larger the absolute  $I_{DAC}$

current amplitude is, the better accuracy the LTC7106-1 can achieve. So it is easy to choose  $R_{TOP} = 10k\Omega$  and  $R_{BOT} = 6.65k\Omega$ . Then  $I_{DAC} = (1.5V - 1.0V)/10k\Omega = + 50\mu A$ . Choose MFR\_CONTROL [6:5] = 00 (Range = Nominal) to set  $I_{DAC}$  LSB =1 $\mu$ A.

By looking in Table 2, choose DAC [6:0] = 0110010 to set the  $I_{DAC}$  = +50µA, which will margin  $V_{OUT}$  from 1.5V to 1.0V.

Figure 6. Using the LTC7106-1 to Margin Low Monolithic Buck Regulator LTC7150S Providing 1.5V to 1.0V at 20A

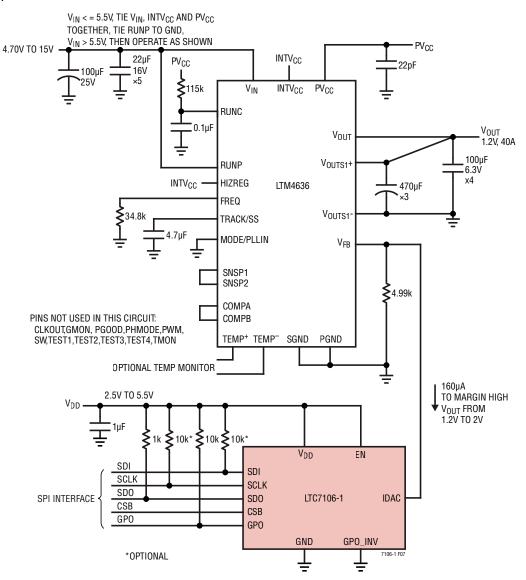

#### Case Two

In this case, the  $\mu$ Module LTM4636 provides a 1.2V output and requires to margin high V<sub>OUT</sub> from 1.2V to 2.0V (see Figure 7). The V<sub>FB</sub> of the LTM4636 is again 0.6V. However, the top voltage divider is internal (R<sub>TOP</sub> = 4.99k $\Omega$ ), so the R<sub>BOT</sub> is also fixed at 4.99k $\Omega$ . Then I<sub>DAC</sub> = (1.2V - 2.0V)/ 4.99k $\Omega$  = -160 $\mu$ A. So we have to choose MFR\_CONTROL [6:5] = 10 (Range = High) to set  $I_{DAC}$  LSB = 4µA.

From Table 3, choose DAC[6:0] = 1011000 to set the  $I_{DAC} = -160\mu A$ , which will margin  $V_{OUT}$  from 1.2V to 2.0V.

Figure 7. Using the LTC7106-1 to Margin High µModule LTM4636 Providing 1.2V to 2.0V at 40A

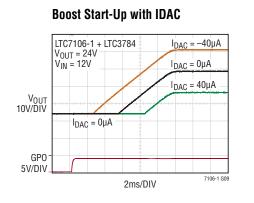

### Case Three

The LTC7106-1 can also work with boost converters. In this case, the LTC3784, a synchronous boost controller, provides a 2-phase 28V/10A output and requires to control  $V_{OUT}$  from 28V to 18V (see Figure 8). The VFB is 1.2V and the voltage dividers are external. Based on the same

design criteria in Case One, we can choose  $R_{TOP} = 200 k\Omega$ and  $R_{BOT} = 8.97 k\Omega$  for the best accuracy. Then  $I_{DAC} = (28V - 18V)/200 k\Omega = +50 \mu A$ . Choose MFR\_CONTROL [6:5] = 00 (Range Nominal) to set  $I_{DAC}$  LSB = 1 $\mu$ A. By looking in Table 2, choose DAC[6:0] = 0001110 to set the  $I_{DAC} = +50 \mu A$ , which will margin  $V_{OUT}$  from 28V to 18V.

Figure 8. Using the LTC7106-1 with a Boost Controller to Vary  $V_{\text{OUT}}$  from 28V to 18V

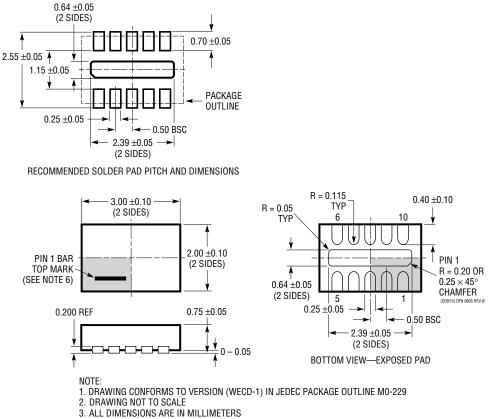

### PACKAGE DESCRIPTION

DDB Package 10-Lead Plastic DFN (3mm × 2mm) (Reference LTC DWG # 05-08-1722 Rev Ø)

4. DIMENSIONS OF EXPOSED PAD ON BOTTOM OF PACKAGE DO NOT INCLUDE

MOLD FLASH. MOLD FLASH, IF PRESENT, SHALL NOT EXCEED 0.15mm ON ANY SIDE 5. EXPOSED PAD SHALL BE SOLDER PLATED

6. SHADED AREA IS ONLY A REFERENCE FOR PIN 1 LOCATION ON THE TOP AND BOTTOM OF PACKAGE

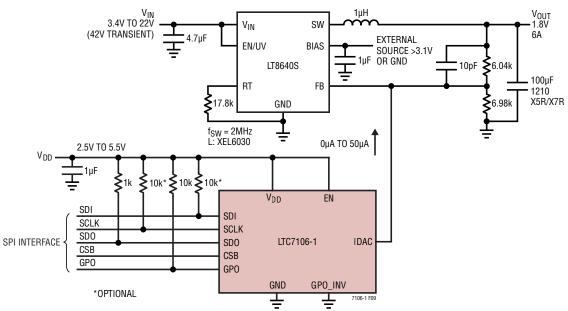

# TYPICAL APPLICATION

Figure 9. Margining a LT8640S from 1.8V to 1.5V at 6A

### **RELATED PARTS**

| PART NUMBER           | DESCRIPTION                                                                                         | COMMENTS                                                                                                                                                        |  |

|-----------------------|-----------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| LTC3605/LTC3605A      | 20V, 5A Synchronous Step-Down Regulator                                                             | 4V < V <sub>IN</sub> < 20V, 0.6V < V <sub>OUT</sub> < 20V, 96% Maximum Efficiency,<br>4mm × 4mm QFN-24 Package                                                  |  |

| LTC3626               | 20V, 2.5A Synchronous Step-Down Regulator with Current and Temperature Monitoring                   | 95% Efficiency, V <sub>IN</sub> : 3.6V to 20V, V <sub>OUT(MIN)</sub> = 0.6V, I <sub>Q</sub> = 300µA, ISD < 15µA, 3mm × 4mm QFN-20                               |  |

| LTC3636               | 20V, Dual 6A Synchronous Step-Down Regulator                                                        | 95% Efficiency, V <sub>IN</sub> : 3.1V to 17V, V <sub>OUT(MIN)</sub> = 0.6V, $I_Q < 8\mu A$ (Both Channels Enabled), ISD < 1 $\mu A$ , 3mm × 5mm QFN-24 Package |  |

| LTC3779               | 150V V <sub>IN</sub> and V <sub>OUT</sub> Synchronous 4-Switch Buck-Boost DC/DC Controller          | $4.5V \leq V_{IN} \leq$ 150V, Input or Output Average Current Loop, PLL, TSSOP-38 Package                                                                       |  |

| LTC3784               | Low I <sub>Q</sub> , Multiphase, Dual Channel Single Output<br>Synchronous Step-Up DC/DC Controller | 4.5V (Down to 2.5V After Start-Up) $\leq$ V <sub>IN</sub> $\leq$ 60V, V <sub>OUT</sub> Up to 60V, PLL Fixed Frequency 50kHz to 900kHz , I <sub>Q</sub> = 28µA   |  |

| LTC3807               | 38V, Low I <sub>Q</sub> , Synchronous Step-Down Controller with 24V Output Voltage Capability       | PLL Fixed Frequency 50kHz to 900kHz, $4V \le V_{IN} \le 38V$ , $0.8V \le V_{OUT} \le 24V$ , $I_Q = 50\mu A$                                                     |  |

| LTC3871               | 100V Bidirectional PolyPhase <sup>®</sup> Buck or Boost Controller                                  | Dynamic Regulation of $V_{\text{IN}}, V_{\text{OUT}}$ and Current, PLL, Current Monitor, 48-Lead LQPF Package                                                   |  |

| LTM <sup>®</sup> 4636 | 40A DC/DC µModule Step-Down Regulator                                                               | Complete 40A Switch Mode Power Supply, $4.75V \le V_{IN} \le 15V, 0.6V \le V_{OUT} \le 3.3V, 16mm \times 16mm \times 7.12mm$ BGA                                |  |

| LTC7150S              | 20V, 20A Synchronous Step-Down Regulator                                                            | 93% Efficiency, V <sub>IN</sub> : 3.1V to 20V, V <sub>OUT(MIN)</sub> = 0.6V, Output Remote<br>Sense, 42-Lead 6mm × 5mm × 1.3mm BGA Package                      |  |

| LT <sup>®</sup> 8640S | 42V, 6A Synchronous Step-Down Silent Switcher <sup>®</sup> 2                                        | $I_{Q} = 2.5 \mu A, V_{IN(MIN)} = 3.4 V, V_{OUT(MAX)} = 42 V, V_{OUT(MIN)} = 0$                                                                                 |  |

| LTC7106               | A 7-bit Current DAC with Digital PMBus Interface                                                    | $2.5V \le V_{DD} \le 5.5V$ , Wide I <sub>DAC</sub> , ±16µA to ±250µA                                                                                            |  |