# ANALOG DEVICES

# PLL/Multibit $\Sigma$ - $\Delta$ DAC

# AD1959

#### FEATURES

**5 V Stereo Audio DAC System** Accepts 16-Bit/20-Bit/24-Bit Data Supports 24 Bits, 192 kHz Sample Rate Accepts a Wide Range of Sample Rates Including: 32 kHz, 44.1 kHz, 48 kHz, 88.2 kHz, 96 kHz, and 192 kHz Multibit Sigma-Delta Modulator with Data Directed Scrambling **Single-Ended Output for Easy Application** -94 dB THD + N 108 dB SNR and Dynamic Range 75 dB Stopband Attenuation **Clickless Volume Control** Hardware and Software Controllable Clickless Mute Serial (SPI) Control for: Serial Mode, Number of Bits, Sample Rate, Volume, Mute, De-Emphasis and Output Phase Digital De-Emphasis Processing for 32 kHz, 44.1 kHz, and 48 kHz Sample Rates **Programmable Dual Fractional-N PLL Clock Generator** 27 MHz Master Clock Input/Oscillator **Generated System Clocks** SCLK0: 33.8688 MHz SCLK1: 384/256 fs (32 kHz/44.1 kHz/48 kHz/88.2 kHz/ 96 kHz)

SCLK2: 512 f<sub>S</sub> (32 kHz/44.1 kHz/48 kHz/88.2 kHz/ 96 kHz)/22.5792 MHz

Better than 100 ps RMS Clock Jitter

Flexible Serial Data Port with Right-Justified, Left-Justified, I<sup>2</sup>S-Compatible, and DSP Serial Port Modes

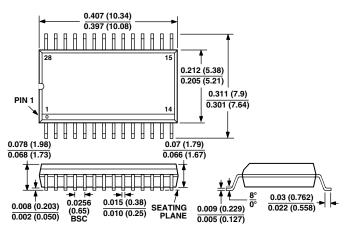

28-Lead SSOP Plastic Package

## APPLICATIONS

DVD, CD, Home Theater Systems, Automotive Audio Systems, Sampling Musical Keyboards, Digital Mixing Consoles, Digital Audio Effects Processors

#### PRODUCT OVERVIEW

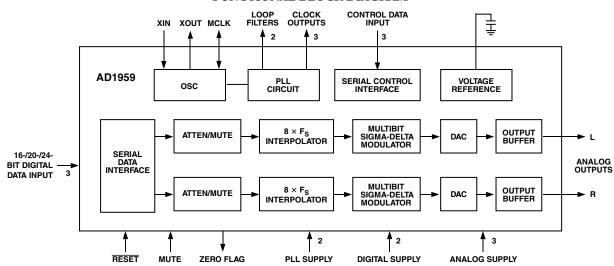

The AD1959 is a complete high-performance single-chip stereo digital audio playback system. It is comprised of a multibit sigmadelta modulator, digital interpolation filters, and analog output drive circuitry with an on-board dual PLL clock generator. Other features include an on-chip stereo attenuator and mute, programmed through an SPI-compatible serial control port. The AD1959 is fully compatible with all known DVD formats including 96 kHz and 192 kHz sample frequencies and 24 bits. It also is backwards-compatible by supporting 50  $\mu$ s/15  $\mu$ s digital de-emphasis for "redbook" compact discs, as well as de-emphasis at 32 kHz and 48 kHz sample rates.

The AD1959 has a simple but flexible serial data input port that allows for glueless interconnection to a variety of ADCs, DSP chips, AES/EBU receivers, and sample rate converters. The AD1959 can be configured in left-justified, I<sup>2</sup>S, right-justified, or DSP serial-port-compatible modes. It can support 16, 20, and 24 bits in all modes. The AD1959 accepts serial audio data in MSB first, two's-complement format, and operates from a single 5 V power supply. It is fabricated on a single monolithic integrated circuit and housed in a 28-lead SSOP package for operation over the temperature range  $-40^{\circ}$ C to  $+105^{\circ}$ C.

#### FUNCTIONAL BLOCK DIAGRAM

# REV.0

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781/329-4700 www.analog.com Fax: 781/326-8703 © Analog Devices, Inc., 2001

# AD1959-SPECIFICATIONS

# TEST CONDITIONS UNLESS OTHERWISE NOTED

| Supply Voltages (AVDD, DVDD) | ) 5.0 V            |

|------------------------------|--------------------|

| Ambient Temperature          | 25°C               |

| Input Clock                  | 12.288 MHz         |

| Input Signal                 | 996.11 Hz          |

|                              | -0.5 dB Full Scale |

| Input Sample Rate            | 48 kHz             |

| Measurement Bandwidth        | 20 Hz to 20 kHz    |

| Word Width                   | 20 Bits            |

| Load Capacitance             | 100 pF             |

| Load Impedance               | 47 kΩ              |

| Input Voltage HI             | 3.5 V              |

| Input Voltage LO             | 0.8 V              |

## ANALOG PERFORMANCE

|                                                                   | Min   | Тур         | Max       | Unit    |

|-------------------------------------------------------------------|-------|-------------|-----------|---------|

| Resolution                                                        |       | 24          |           | Bits    |

| Signal-to-Noise Ratio (20 Hz to 20 kHz)                           |       |             |           |         |

| No Filter (Stereo)                                                |       | 105         |           | dB      |

| With A-Weighted Filter (Stereo)                                   |       | 108         |           | dB      |

| Dynamic Range (20 Hz to 20 kHz, -60 dB Input)                     |       |             |           |         |

| No Filter (Stereo)                                                |       | 105         |           | dB      |

| With A-Weighted Filter (Stereo)                                   | 101   | 108         |           | dB      |

| Total Harmonic Distortion + Noise (Stereo)                        |       | -94         | -91       | dB      |

| PLL Performance                                                   |       |             |           |         |

| Master Clock Input Frequency                                      |       | 27          |           | MHz     |

| Generated System Clocks                                           |       |             |           |         |

| SCLK0                                                             |       | 33.8688     |           | MHz     |

| SCLK1                                                             |       | 12.288      |           | MHz     |

| SCLK2                                                             |       | 22.5792     |           | MHz     |

| Jitter (SCLK0 and SCLK1)                                          |       | 85          | 125       | ps rms  |

| Analog Outputs                                                    |       |             |           |         |

| Single-Ended Output Range (±Full Scale)                           |       | 3.17        |           | V p-p   |

| Output Capacitance at Each Output Pin                             |       |             | 2         | pF      |

| V <sub>REF</sub> (FILTR)                                          | 2.34  | 2.39        | 2.44      | V       |

| Gain Error                                                        | -5    | $\pm 2.0$   | +5        | %       |

| Interchannel Gain Mismatch                                        | -0.15 | $\pm 0.015$ | +0.15     | dB      |

| Gain Drift                                                        |       | 150         | 250       | ppm/°C  |

| DC Offset                                                         | -25   | -5          | +15       | mV      |

| Out-of-Band Energy $(0.5 \times f_8 \text{ to } 100 \text{ kHz})$ |       |             | -90       | dB      |

| Interchannel Crosstalk (EIAJ Method)                              |       | -120        |           | dB      |

| Interchannel Phase Deviation                                      |       | $\pm 0.1$   |           | Degrees |

| De-Emphasis Gain Error                                            |       |             | $\pm 0.1$ | dB      |

NOTES

Performance of right and left channels is identical (exclusive of the Interchannel Gain Mismatch and Interchannel Phase Deviation specifications). Specifications subject to change without notice.

## **DIGITAL I/O** (-40°C to +105°C)

|                                                                   | Min | Тур | Max | Unit |

|-------------------------------------------------------------------|-----|-----|-----|------|

| Input Voltage HI (V <sub>IH</sub> ) Except XIN                    | 2.2 |     |     | V    |

| Input Voltage HI (V <sub>IH</sub> ) XIN                           | 2.7 |     |     | V    |

| Input Voltage LO (V <sub>IL</sub> )                               |     |     | 0.8 | V    |

| Input Leakage ( $I_{IH}$ @ $V_{IH}$ = 2.4 V)                      |     |     | 10  | μA   |

| Input Leakage ( $I_{IL} @ V_{IL} = 0.8 \text{ V}$ )               |     |     | 10  | μA   |

| High Level Output Voltage ( $V_{OH}$ ) $I_{OH}$ = 1 mA            | 2.0 |     |     | V    |

| Low Level Output Voltage ( $V_{OL}$ ) $I_{OL}$ = 1 mA Except XOUT |     |     | 0.4 | V    |

| Low Level Output Voltage $(V_{OL}) I_{OL} = 1 \text{ mA XOUT}$    |     |     | 1.2 | V    |

| Input Capacitance                                                 |     |     | 20  | pF   |

Specifications subject to change without notice.

# **TEMPERATURE RANGE**

|                           | Min | Тур | Max   | Unit |

|---------------------------|-----|-----|-------|------|

| Specifications Guaranteed |     | 25  |       | °C   |

| Functionality Guaranteed  | -40 |     | +105* | °C   |

| Storage                   | -55 |     | +150  | °C   |

NOTES

\*105°C ambient guaranteed for a 4-layer board, two 1 oz. planes, two 2 oz. signal layers. Derate to 85°C for 2-layer board, 2 oz. layers. Specifications subject to change without notice.

#### POWER

|                             | Min  | Тур | Max  | Unit |

|-----------------------------|------|-----|------|------|

| Supplies                    |      |     |      |      |

| Voltage, Analog Digital PLL | 4.50 | 5   | 5.50 | V    |

| Analog Current              |      | 36  | 42   | mA   |

| Digital Current             |      | 28  | 34   | mA   |

| PLL Current                 |      | 27  | 32   | mA   |

| Dissipation                 |      |     |      |      |

| Operation – All Supplies    |      | 455 | 540  | mW   |

| Operation – Analog Supply   |      | 180 |      | mW   |

| Operation – Digital Supply  |      | 140 |      | mW   |

| Operation – PLL Supply      |      | 135 |      | mW   |

Specifications subject to change without notice.

# DIGITAL FILTER CHARACTERISTICS

| Sample Rate (kHz) | Pass Band (kHz)  | Stop Band (kHz)            | Stopband Attenuation (dB) | Pass-Band Ripple (dB)                                                 |

|-------------------|------------------|----------------------------|---------------------------|-----------------------------------------------------------------------|

| 44.1<br>48        | DC-20<br>DC-21.8 | 24.1–328.7<br>26.23–358.28 | 75<br>75                  | $\pm 0.0002$<br>$\pm 0.0002$                                          |

| 96                | DC-39.95         | 56.9-327.65                | 75                        | ±0.0005                                                               |

| 192               | DC-87.2          | 117-327.65                 | 60                        | 0/-0.04 (DC-21.8 kHz)<br>0/-0.5 (DC-65.4 kHz)<br>0/-1.5 (DC-87.2 kHz) |

Specifications subject to change without notice.

#### **GROUP DELAY**

| Chip Mode  | Group Delay Calculation                                                            | f <sub>S</sub> | Group Delay | Unit |

|------------|------------------------------------------------------------------------------------|----------------|-------------|------|

| INT8× Mode | $\begin{array}{c} 24.625/f_{\rm S} \\ 15.75/f_{\rm S} \\ 14/f_{\rm S} \end{array}$ | 48 kHz         | 513         | μs   |

| INT4× Mode |                                                                                    | 96 kHz         | 164         | μs   |

| INT2× Mode |                                                                                    | 192 kHz        | 72.91       | μs   |

Specifications subject to change without notice.

# **DIGITAL TIMING** (Guaranteed over $-40^{\circ}$ C to $+105^{\circ}$ C, AVDD = DVDD = 5.0 V ± 10%)

|                   |                                        | Min | Unit |

|-------------------|----------------------------------------|-----|------|

| t <sub>DMP</sub>  | MCLK Period (FMCLK = 256 × FLRCLK)     | 54  | ns   |

| t <sub>DML</sub>  | MCLK LO Pulsewidth (All Modes)         | 15  | ns   |

| t <sub>DMH</sub>  | MCLK HI Pulsewidth (All Modes)         | 10  | ns   |

| t <sub>DBH</sub>  | BCLK HI Pulsewidth                     | 7   | ns   |

| t <sub>DBL</sub>  | BCLK LO Pulsewidth                     | 12  | ns   |

| t <sub>DBP</sub>  | BCLK Period                            | 60  | ns   |

| t <sub>DLS</sub>  | LRCLK Setup                            | 20  | ns   |

| t <sub>DLH</sub>  | LRCLK Hold (DSP Serial Port Mode Only) | 20  | ns   |

| t <sub>DDS</sub>  | SDATA Setup                            | 15  | ns   |

| t <sub>DDH</sub>  | SDATA Hold                             | 10  | ns   |

| t <sub>RSTL</sub> | RST LO Pulsewidth                      | 15  | ns   |

Specifications subject to change without notice.

# AD1959

#### **ABSOLUTE MAXIMUM RATINGS\***

\*Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those listed in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. Only one absolute maximum rating may be applied at any one time.

#### CAUTION\_

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although the AD1959 features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high-energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

#### **ORDERING GUIDE**

PACKAGE CHARACTERISTICS

39.0°C/W Typ

109.0°C/W Typ (2-Layer Board)

$\theta_{IA}$  (Thermal Resistance) Junction-to-Ambient

$\theta_{IA}$  (Thermal Resistance) Junction-to-Ambient

$\theta_{IA}$  (Thermal Resistance) Junction-to-Case

78.58°C/W Typ (4-Layer Board-2 Signal, 2 Planes)

| Model                                     | Temperature                          | Package Description                                                                | Package Option              |

|-------------------------------------------|--------------------------------------|------------------------------------------------------------------------------------|-----------------------------|

| AD1959YRS<br>AD1959YRSRL<br>EVAL-AD1959EB | -40°C to +105 °C<br>-40°C to +105 °C | 28-Lead Small Outline Package<br>28-Lead Small Outline Package<br>Evaluation Board | RS-28<br>RS-28 on 13" Reels |

#### PIN CONFIGURATION

|          |                | 1  |       |

|----------|----------------|----|-------|

| CCLK 1   | •              | 28 | CDATA |

| CLATCH 2 |                | 27 | MUTE  |

| RESET 3  |                | 26 | ZERO  |

| LRCLK 4  |                | 25 | FILTB |

| BCLK 5   |                | 24 | AVDD  |

| SDATA 6  | AD1959         | 23 | OUTL  |

| DVDD 7   | TOP VIEW       | 22 | AGND1 |

| DGND 8   | (Not to Scale) | 21 | FLTR  |

| SCLK0 9  |                | 20 | OUTR  |

| MCLK 10  |                | 19 | AGND0 |

| XOUT 11  |                | 18 | LF1   |

| XIN 12   |                | 17 | LF0   |

| SCLK1 13 |                | 16 | PGND  |

| SCLK2 14 |                | 15 | PVDD  |

|          |                |    |       |

# PIN FUNCTION DESCRIPTIONS

| Pin | Input/Output | Mnemonic | Description                                                                                                                                                                |

|-----|--------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | I            | CCLK     | Control Clock Input for Control Data. Control input data must be valid on the rising edge of CCLK. CCLK may be continuous or gated.                                        |

| 2   | Ι            | CLATCH   | Latch Input for Control Data.                                                                                                                                              |

| 3   | I            | RESET    | Reset. The AD1959 is placed in a reset mode when this pin is held LO.<br>The serial control port registers are reset to their default values. Set HI for normal operation. |

| 4   | Ι            | LRCLK    | Left/Right Clock Input for Input Data. Must run continuously.                                                                                                              |

| 5   | Ι            | BCLK     | Bit Clock Input for Input Data. Need not run continuously; may be gated or used in a burst fashion.                                                                        |

| 6   | Ι            | SDATA    | Serial input, MSB first, containing two channels of 16/20/24 bits of two's-complement data per channel.                                                                    |

| 7   | Ι            | DVDD     | Digital Power Supply Connect to Digital 5 V Supply.                                                                                                                        |

| 8   | Ι            | DGND     | Digital Ground.                                                                                                                                                            |

| 9   | 0            | SCLK0    | 33.8688 MHz Clock Output.                                                                                                                                                  |

| 10  | I/O          | MCLK     | 27 MHz Master Clock Output/256 f <sub>S</sub> DAC Clock Input.                                                                                                             |

| 11  | 0            | XOUT     | 27 MHz Crystal Oscillator Output.                                                                                                                                          |

| 12  | Ι            | XIN      | 27 MHz Crystal Oscillator/External Clock Input.                                                                                                                            |

| 13  | 0            | SCLK1    | 256/384 f <sub>S</sub> Output.                                                                                                                                             |

| 14  | 0            | SCLK2    | 512 f <sub>S</sub> /22.5792 MHz Output.                                                                                                                                    |

| 15  |              | PVDD     | PLL Power Supply. Connect to PLL 5 V Supply.                                                                                                                               |

| 16  |              | PGND     | PLL Ground.                                                                                                                                                                |

| 17  |              | LF0      | PLL0 Loop Filter.                                                                                                                                                          |

| 18  |              | LF1      | PLL1 Loop Filter.                                                                                                                                                          |

| 19  |              | AGND0    | Analog Ground.                                                                                                                                                             |

| 20  | 0            | OUTR     | Right Channel Positive Line Level Analog Output.                                                                                                                           |

| 21  | 0            | FILTR    | Voltage Reference Filter Capacitor Connection. Bypass and decouple the voltage reference with parallel 10 $\mu$ F and 0.1 $\mu$ F capacitors to AGND.                      |

| 22  | Ι            | AGND1    | Analog Ground.                                                                                                                                                             |

| 23  | 0            | OUTL     | Left Channel Line Level Analog Output.                                                                                                                                     |

| 24  |              | AVDD     | Analog Power Supply. Connect to Analog 5 V Supply.                                                                                                                         |

| 25  |              | FILTB    | Filter Capacitor Connection, Connect 10 µF Capacitor to AGND.                                                                                                              |

| 26  | 0            | ZERO     | Zero Flag Output. This pin goes HI when both channels have zero signal input for more than 1024 L/R Clock Cycles.                                                          |

| 27  | I            | MUTE     | Mute. Assert HI to Mute Both Stereo Analog Outputs. Deassert LO for normal operation.                                                                                      |

| 28  | I            | CDATA    | Serial control input, MSB first, containing 16 bits of unsigned data per channel.                                                                                          |

# AD1959

# FUNCTIONAL DESCRIPTION DAC

The AD1959 has two DAC channels arranged as a stereo pair with single-ended analog outputs. Each channel has its own independently programmable attenuator, adjustable in 16384 linear steps. Digital inputs are supplied through a serial data input pin, SDATA, a frame clock, LRCLK and a bit clock, BLCK.

Each analog output pin sits at a dc level of  $V_{REF}$ , and swings  $\pm 1.585$  V for a 0 dB digital input signal. A single op amp third-order external low-pass filter is recommended to remove high-frequency noise present on the output pins. The output phase can be changed in an SPI control register to accommodate inverting and noninverting filters. Note that the use of op amps with low slew rate or low bandwidth may cause high frequency noise and tones to fold down into the audio band; care should be exercised in selecting these components.

The FILTD and FILTR pins should be bypassed by external capacitors to ground. The FILTD pin is used to reduce the noise of the internal DAC bias circuitry, thereby reducing the DAC output noise. The voltage at the  $V_{REF}$  pin, FILTR (~2.39 V) can be used to bias external op amps used to filter the output signals.

The DAC master clock frequency is 256 f<sub>S</sub> for the 32 kHz–48 kHz range. For the 96 kHz range this is 128 f<sub>S</sub>. It is supplied internally from the PLL clock system when MCLK mode is set to Output in the PLL Control Register. When the MCLK mode is changed to Input, it must be supplied from an external source connected to MCLK. The output from the 27 MHz PLL clock is disabled in this case.

# PLL Clock System

The PLL clock system operates from a 27 MHz master clock supplied by the on-board crystal oscillator or an external source connected to XIN. With the MCLK mode set to Output, the 27 MHz clock is buffered out to the MCLK pin. When set to Input, the MCLK is the 256  $f_S$  master clock input for the DAC. SCLK0 produces a 33.8688 MHz output, SCLK1 is intended to be used as a master audio clock and will be a multiple of the sample rate set in the PLL control register. It can be set to 256  $f_S$  or 384  $f_S$  using Bit 5 and to 512  $f_S$  or 768  $f_S$ , with Bit 4. SCLK2 can be set to a constant 22.5792 MHz (512 × 44.1 kHz) or 512  $f_S$  by Bit 3 of the PLL Control Register. Please note that SCLK2 is intended to operate a DSP and does not meet the jitter specifications stated under Analog Performance. All the generated clocks can be set to 1/2 their nominal rate by setting REF\_Div2, Bit 8 in the PLL Control Register.

## Reset

**RESET** will set the control registers to their default settings. The chip should be reset on power-up. After reset is deasserted, the part will come out of reset on the next rising LRCLK.

#### **Serial Control Port**

The AD1959 has an SPI-compatible control port to permit programming the internal control registers for the PLL and DAC. The DAC output levels may be independently programmed by means of an internal digital attenuator adjustable in 16384 linear steps.

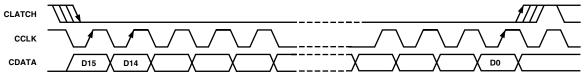

The SPI control port is a 3-wire serial control port. The format is similar to the Motorola SPI format except the input data word is 16 bits wide. Max serial bit clock frequency is 8 MHz and may be completely asynchronous to the PLL system or the DAC. Figure 1 shows the format of the SPI signal. Note that the CCLK can be gated or continuous, CLATCH should be low during the 16 active clocks.

Figure 1. Format of SPI Signal

#### POWER SUPPLY AND VOLTAGE REFERENCE

The AD1959 is designed for five-volt supplies. Separate power supply pins are provided for the analog, digital, and PLL sections. These pins should be bypassed with 100 nF ceramic chip capacitors, as close to the pins as possible, to minimize noise. A bulk aluminum electrolytic capacitor of at least  $22 \,\mu$ F should also be provided on the same PC board. For best performance it is recommended that the analog supply be separate from the digital and PLL supply. It is recommended that all supplies be isolated by ferrite beads in series with each supply. It is expected that the digital and PLL sections will be run from a common supply but isolated from one another. It is important that the analog supply be as clean as possible.

The internal voltage reference is brought out on Pin 21 (FILTR) and should be bypassed as close as possible to the chip with a

parallel combination of 10  $\mu$ F and 100 nF The reference voltage may be used to bias external op amps to the common-mode voltage of the analog output signal pins. The current drawn from the V<sub>REF</sub> pin should be limited to less than 50  $\mu$ A.

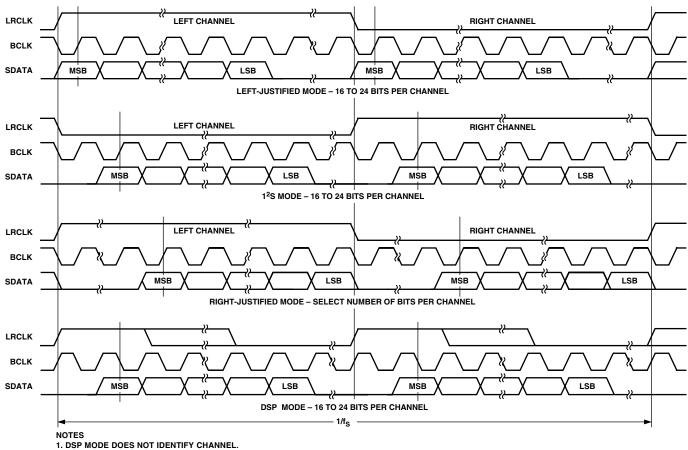

#### SERIAL DATA PORTS - DATA FORMAT

The DAC serial data input mode defaults to  $I^2S$ . By changing Bits 4 and 5 in the DAC control register, the mode can be changed to RJ, DSP, or LJ. The word width defaults to 24 bits but can be changed by programming Bits 8 and 9 in the DAC Control Register.

Figure 2 shows the serial mode formats.

2. LRCLK NORMALLY OPERATES AT  $f_{\rm S}$  except for DSP mode which is 2  $\times$   $f_{\rm S}.$

3. BCLK FREQUENCY IS NORMALLY 64 × LRCLK BUT MAY BE OPERATED IN BURST MODE.

Figure 2. Stereo Serial Modes

# AD1959

| Bit 11:10                                                                   | Bit 9:8                                                       | Bit 7                            | Bit 6                     | Bit 5:4                                                                           | Bit 3:2                                                  | Bit 1:0                 |

|-----------------------------------------------------------------------------|---------------------------------------------------------------|----------------------------------|---------------------------|-----------------------------------------------------------------------------------|----------------------------------------------------------|-------------------------|

| Interpolation<br>Factor                                                     | Serial Data<br>Width                                          | Output Phase                     | Soft Mute                 | Serial Data<br>Format                                                             | De-Emphasis<br>Filter                                    | SPI Register<br>Address |

| $00 = 8 \times *$<br>$01 = 4 \times$<br>$10 = 2 \times$<br>11 = Not Allowed | 00 = 24 Bits*<br>01 = 20 Bits<br>10 = 16 Bits<br>11 = 16 Bits | 0 = Noninverted*<br>1 = Inverted | 0 = No Mute*<br>1 = Muted | 00 = I <sup>2</sup> S*<br>00 = Right Justified<br>10 = DSP<br>11 = Left Justified | 00 = None*<br>01 = 44.1 kHz<br>10 =32 kHz<br>11 = 48 kHz | 01                      |

# Table I. DAC Control Register

\*Default Setting.

# Table II. DAC Volume Registers

| Bit 15:2                               | Bit 1:0                               |  |  |

|----------------------------------------|---------------------------------------|--|--|

| Volume                                 | SPI Register Address                  |  |  |

| 14 Bits, Unsigned<br>14 Bits, Unsigned | 00 = Left Volume<br>10 = Right Volume |  |  |

Default is full volume.

#### Table III. PLL Control Register

| Bit 11     | Bit 10     | Bit 9      | Bit 8          | Bit 7:6                 | Bit 5   | Bit 4              | Bit 3                              | Bit 2       | Bit 1:0  |

|------------|------------|------------|----------------|-------------------------|---------|--------------------|------------------------------------|-------------|----------|

| PLL2       | PLL1       | XTAL       | REF_Div2       |                         |         |                    |                                    |             | SPI      |

| Power-     | Power-     | Power-     | Power-         |                         | SCLK1   |                    | SCLK2                              | MCLK        | Register |

| Down       | Down       | Down       | Down           | $f_S$                   | Select  | Double             | Select                             | Mode        | Address  |

| $0 = On^*$ | 0 = On*    | $0 = On^*$ | $0 = No Div^*$ | $00 = 48 \text{ kHz}^*$ | 0 =256* | $0 = f_{s}^{*}$    | $0 = 512 \times 4.1 \text{ kHz}^*$ | 0 = Output* | 11       |

| 1 = Power- | 1 = Power- | 1 = Power- | 1 = Div by  2  | 01 = Not                | 1 =384  | $1 = 2 \times f_s$ | $1 = 512 \times f_s$               | 1 = Input   |          |

| Down       | Down       | Down       | -              | Allowed                 |         |                    |                                    | _           |          |

|            |            |            |                | 10 = 32 kHz             |         |                    |                                    |             |          |

|            |            |            |                | 11 = 44.1 kHz           |         |                    |                                    |             |          |

\*Default Setting.

# OUTLINE DIMENSIONS Dimensions shown in inches and (mm).

#### 28-Lead Small Outline Package (SSOP) (RS-28)

PRINTED IN U.S.A.