# Optical Evaluation Kit for the ADN2530 **Differential VCSEL Driver**

**EVAL-ADN2530**

#### **GENERAL DESCRIPTION**

This data sheet describes the optical evaluation kit for the ADN2530, a 10 Gbps active back-terminated, vertical-cavity surface-emitting laser (VCSEL) driver. The output stage's differential configuration combined with on-chip active backtermination ensures high quality eye diagrams at lower power consumption compared with traditional passive back-termination approaches. The complete ADN2530 specifications are available in the ADN2530 data sheet and need to be consulted in conjunction with this data sheet when using the evaluation board. The optical evaluation kit, EVAL-ADN2530-AOZ, consists of an evaluation board and an 850 nm, 10 Gbps VCSEL TOSA, AOC HFE6192-562. The evaluation kit EVAL-ADN2530-ANZ has the same evaluation board without a TOSA attached.

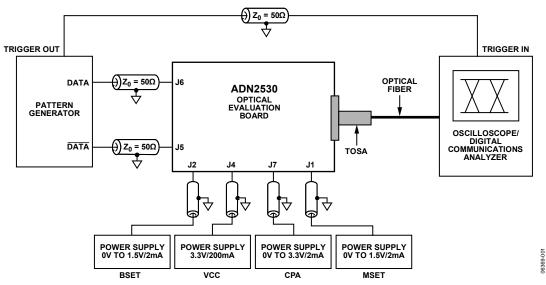

To evaluate the performance of the ADN2530, the board and the test setup must be configured as shown in Figure 1. A multimode fiber patch cord with appropriate connector for the TOSA end is required to connect the TOSA to the sampling scope/digital communications analyzer.

The power supply must be able to deliver 200 mA at 3.3 V. The amplitude of the data signal from pattern generator must be adjusted to within the ADN2530 data sheet specifications for data inputs, typically 1 V p-p differential (500 mV single-ended on DATAP and DATAN). The oscilloscope/digital communications analyzer must have an 850 nm optical channel that can accept and display properly the optical signals generated by the TOSA.

The co-axial cables used to connect the pattern generator to the evaluation board DATAP/DATAN inputs must be suitable for carrying 10 Gbps signals without significant reduction of rise/fall time or introduction of pattern jitter. They should also be a matched pair with a delay skew of  $\leq 2$  ps. An example of suitable cables is the 60 cm Lab-Flex® 160 cables with 2.4 mm connectors from Florida RF Labs®.

Figure 1. ADN2530 Optical Evaluation Board Test Setup

#### Rev. 0

Evaluation boards are only intended for device evaluation and not for production purposes Evaluation boards are supplied "as is" and without warranties of any kind, express, implied, or statutory including, but not limited to, any implied warranty of merchantability or fitness for a particular purpose. No license is granted by implication or otherwise under any patents or other intellectual property by application or use of evaluation boards. Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Analog Devices reserves the right to change devices or specifications at any time without notice. Trademarks and registered trademarks are the property of their respective owners. Evaluation boards are not authorized to be used in life support devices or systems.

## **TABLE OF CONTENTS**

| General Description                | . 1 |

|------------------------------------|-----|

| Revision History                   | . 2 |

| Evaluation Board Hardware          |     |

| Connectors                         |     |

|                                    |     |

| Terminals                          |     |

| Jumpers                            |     |

| Ouick Start for Optical Evaluation | . 3 |

| Using the Evaluation Board PCB Layout in an Optical Transmitter Design | 5  |

|------------------------------------------------------------------------|----|

| Evaluation Board Schematics and Artwork                                |    |

| Ordering Information                                                   | 10 |

| Bill of Materials                                                      | 10 |

| Ordering Guide                                                         | 10 |

| FSD Caution                                                            | 10 |

### **REVISION HISTORY**

12/07—Revision 0: Initial Version

### **EVALUATION BOARD HARDWARE**

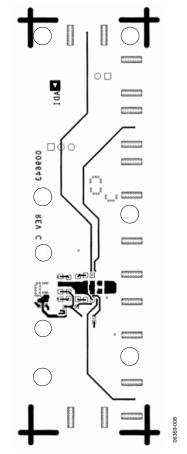

#### **CONNECTORS**

The ADN2530 is capable of delivering a 23 mA differential modulation current and 25 mA bias current. Applying dc voltages to the ADN2530 BSET and MSET pins sets the bias and modulation currents. The board is set up so that the outputs of the ADN2530 are ac-coupled to the TOSA. The board is fitted with connectors that allow the user to connect the evaluation board to the test setup. Table 1 describes the function of each connector on the board.

**Table 1. Connector Description**

| Tuble 1. Connector Description |                                                                                                                                                         |  |  |

|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Connector                      | Description                                                                                                                                             |  |  |

| J1                             | Allows the user to apply an external dc voltage source to control the differential modulation current provided by the ADN2530.                          |  |  |

| J2                             | Allows the user to apply an external dc voltage source to control the bias current provided by the ADN2530.                                             |  |  |

| J3                             | Automatic laser shutdown. Allows the user to enable/disable the bias and modulation currents by applying a low/high logic level (not greater than VCC). |  |  |

| J4                             | Power supply connector. The board supply voltage is 3.3 V with respect to GND.                                                                          |  |  |

| J5                             | Negative data input. A PECL/CML data signal should be applied.                                                                                          |  |  |

| J6                             | Positive data input. A PECL/CML data signal should be applied.                                                                                          |  |  |

| J7                             | Allows the user to apply an external DC voltage to the ADN2530 CPA pin to adjust the eye cross-point level.                                             |  |  |

| J8                             | $50 \Omega$ test transmission line.                                                                                                                     |  |  |

### **TERMINALS**

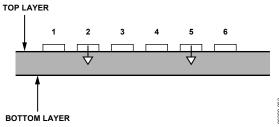

The evaluation board accommodates the terminal assignment of the AOC HFE6x92-562 TOSA flex.

Table 2. AOC HFE6x92-562 Terminal Function

| Terminal Number | Function   |

|-----------------|------------|

| 1               | PD Cathode |

| 2               | Ground     |

| 3               | LD Anode   |

| 4               | LD Cathode |

| 5               | Ground     |

| 6               | PD Anode   |

For additional optical eye diagram performance data and for information on optimizing the performance of the evaluation board for different TOSAs, contact a local Analog Devices, Inc. representative.

Figure 2. Pinout of TOSA Footprint on PCB (Looking Toward the Edge of the Board)

#### **JUMPERS**

Cross-point adjust and automatic laser shutdown can be configured to be driven by the voltages generated on the board or by external voltages as described in Table 3.

**Table 3. Jumper Configurations**

|        | Tuble 5. Jumper Configurations |                                                                                                                                                            |  |  |

|--------|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Jumper | Jumper<br>Setting              | Configuration Description                                                                                                                                  |  |  |

| P4     | Α                              | Enables the bias and differential modulation currents.                                                                                                     |  |  |

|        | В                              | Disables the bias and differential modulation currents.                                                                                                    |  |  |

|        | Removed                        | Allows the user to enable/disable the<br>bias and differential modulation<br>currents by applying a low/high logic<br>level to J3 from an external source. |  |  |

| P1     | Populated                      | Disable the cross-point adjust function.                                                                                                                   |  |  |

|        | Removed                        | Allow the user to adjust the output eye cross-point level using a dc voltage applied to J7.                                                                |  |  |

### **QUICK START FOR OPTICAL EVALUATION**

- If using evaluation kit EVAL-ADN2530-ANZ, solder a TOSA to the evaluation board following soldering guidelines in the TOSA data sheet.

- 2. If required, change the jumper settings to obtain the desired configuration using Table 3.

- 3. Connect the evaluation board to an oscilloscope, pattern generator, and power supplies as shown in Figure 1. A suitable pattern generator is the Anritsu MP1763B and a suitable oscilloscope is the Agilent 86100B with 86105C optical plug-in. Use coaxial cables for DATAP and DATAN of the type recommended in the General Description section.

- 4. Run any applicable user calibrations on the oscilloscope optical input.

- 5. Turn on the power supply (3.3 V) connected to J4. Check that the current drawn from the 3.3 V power supply is within the limits of the I<sub>SUPPLY</sub> specifications in the ADN2530 data sheet.

- 6. Increase the voltage applied to J2 starting from 0 V until the desired optical average power is obtained.

- 7. Increase the voltage applied to J1 starting from 0 V until the desired extinction ratio is obtained.

- 8. If cross-point adjust function is enabled, adjust the voltage applied to J7 until the desired output eye cross-point level is obtained.

- To prevent damage to the TOSA, it is advisable to gradually adjust the BSET and MSET voltages back to 0 V before turning off the power supplies.

### Using Evaluation Kit EVAL-ADN2530-AOZ

When using the evaluation kit, EVAL-ADN2530-AOZ, it is recommended that the kit be initially set up to reproduce the sample optical eye diagram that is included with the kit. This confirms that the test setup is configured correctly to produce a high quality optical eye diagram. The following steps should be followed to reproduce the sample optical eye diagram:

- 1. Set up the board following the recommendations in the Quick Start for Optical Evaluation section.

- Adjust the data rate and pattern to the settings used in the sample optical eye diagram and select the appropriate optical filter and wavelength on the oscilloscope.

- 3. Adjust the BSET, MSET, and CPA voltages to the settings used in the sample optical eye diagram.

- 4. Confirm that the VCC supply current (I<sub>CC</sub>) and the IBMON voltage at TP1 are close to the values reported in the sample optical eye diagram. If either of the values is significantly different, this indicates that there is a problem with the test setup, evaluation board, or TOSA, and this needs to be investigated.

- 5. Confirm that the real average power is close to the value reported in the sample optical eye diagram. The real average power is the average power as measured by the test equipment plus the measured attenuation of any optical attenuators in the optical signal path. If the value is significantly different, this indicates that there is a problem with the test setup, evaluation board, or TOSA, and this needs to be investigated. Less significant differences can sometimes be attributed to some of the following:

- Dirt in the fiber connectors, optical attenuators, or oscilloscope optical input can cause errors in average power.

- Optical coupling can be quite variable at the TOSA because there is no latching mechanism for the fiber connector. Ensuring that the connector is fully inserted and rotating the connector can eliminate small discrepancies in real average power.

- Calibration differences between the oscilloscope in the test setup and the oscilloscope used to measure the sample optical eye diagram can cause small discrepancies in measured average power.

- 6. Confirm that the extinction ratio is close to the value reported in the sample optical eye diagram. If the value is significantly different, this indicates that there is a problem with the test setup, evaluation board, or TOSA, and this needs to be investigated. Because the extinction ratio is a sensitive measurement, small discrepancies can be attributed to using different oscilloscope or optical plug-in models or even different optical plug-ins of the same model.

- 7. Select the same eye mask and mask Y-alignment method as used in the sample optical eye diagram.

- 8. Select the same number of waveforms for the eye diagram capture as used in the sample optical eye diagram.

- 9. Confirm that the average mask margin is close to the value reported in the sample optical eye diagram. If the value is significantly different, this indicates that there is a problem with the test setup, evaluation board, or TOSA, and this needs to be investigated. Differences can be attributed to some of the following:

- A poor quality differential electrical eye diagram at

the output of the coaxial cables from the pattern

generator results in a poor optical eye diagram.

Measuring the electrical eye diagram on these signals

confirms or eliminates this possibility. Delay skew

>2 ps between the DATAP and DATAN signals is one

example of a degraded input signal that leads to a

degraded optical eye diagram.

- Small discrepancies can be attributed to using different oscilloscope or optical plug-in models or even different optical plug-ins of the same model. Different optical plug-in models have different bandwidths, noise, and time-base jitter and this can affect eye mask margin. Different optical plug-ins of the same model can have different frequency responses in the optical filter that is within the allowed tolerance and this can affect eye mask margin.

- If an optical attenuator is required to keep the eye diagram within the oscilloscope range, an attenuation value should be chosen that keeps the optical signal in the upper end of the oscilloscope range. Otherwise, the effect of oscilloscope noise on the eye mask margin is increased.

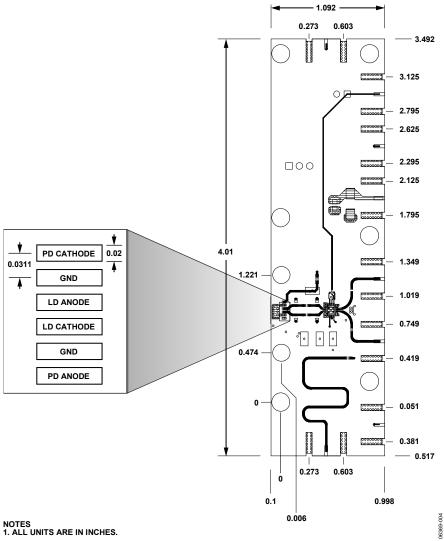

# USING THE EVALUATION BOARD PCB LAYOUT IN AN OPTICAL TRANSMITTER DESIGN

The evaluation kit PCB is fabricated using FR4 (NELCO N4000-6, 170 Tg) with 12 mil dielectric thickness between the top-side signal and ground layers. When using the evaluation board PCB layout as a guide when designing an optical transmitter it is recommended that the same dielectric material and thickness be used and the PCB layout associated with the ADN2530, the ac-coupling components, and the TOSA be copied exactly. This includes features such as component pad positions and sizes, track widths and lengths, via sizes, and positions. These features

affect the high frequency performance in ways that are difficult to predict, therefore changing them increases the risk of losing some mask margin performance. Following this recommendation gives the highest likelihood that eye diagram performance measured on the evaluation board is reproduced in the optical transmitter (ignoring any performance loss contributed by retiming or other circuitry that precedes the ADN2530). It is possible that changing the PCB dielectric material or making small changes to the PCB layout causes negligible degradation in the performance or even improves the performance, but this is difficult to predict.

Figure 3. Evaluation Board Outline

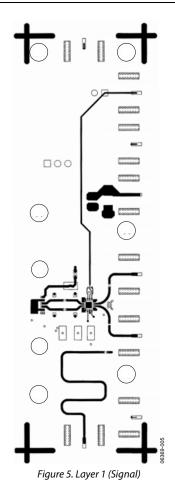

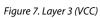

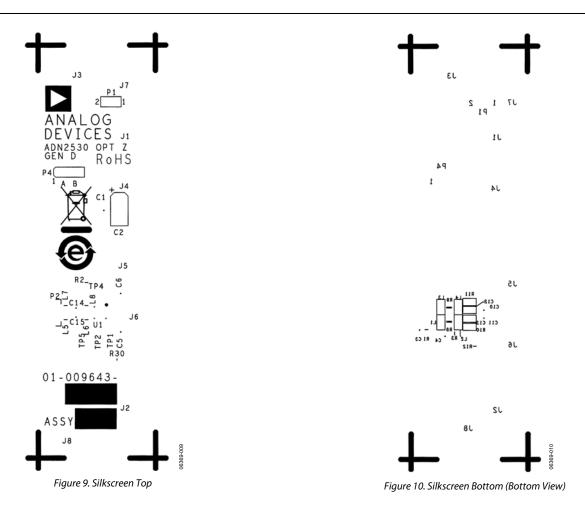

# **EVALUATION BOARD SCHEMATICS AND ARTWORK**

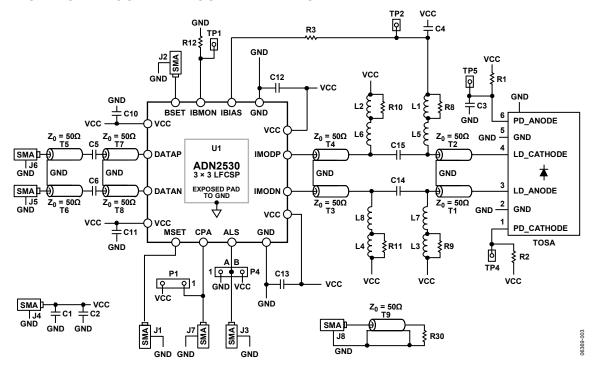

Figure 4. Schematic of Generation C Evaluation Board

Figure 6. Layer 2 (GND)

Figure 8. Layer 4 (Signal)

### ORDERING INFORMATION

### **BILL OF MATERIALS**

### Table 4.

| Qty | Reference Designator           | Description                                        | Supplier/Part Number   |

|-----|--------------------------------|----------------------------------------------------|------------------------|

| 2   | R2, R3                         | 0 Ω, 0402 size resistor                            |                        |

| 1   | R1                             | $0 \Omega$ , 0402 size resistor; not populated     |                        |

| 2   | R10, R11                       | 300 Ω, 0603 size resistor                          |                        |

| 2   | R8, R9                         | $300 \Omega$ , 0603 size resistor                  |                        |

| 1   | R12                            | 750 Ω, 0 603 size 0.1% resistor                    |                        |

| 2   | C5, C6                         | 10 nF, 0402, X7R, ceramic capacitor                |                        |

| 1   | C4                             | 100 nF, 0402, X7R, ceramic capacitor               |                        |

| 2   | P1, P4                         | Jumper and header                                  |                        |

| 8   | J1, J2, J3, J4, J5, J6, J7, J8 | Side launch SMA connector                          |                        |

| 2   | C14, C15                       | 100 nF, 0402, ceramic capacitor                    | Phycomp 2238 787 19849 |

| 4   | C10, C11, C12, C13             | 100 nF, 0402, X7R ceramic capacitor                |                        |

| 1   | C1                             | 10 nF, 0603, X7R, ceramic capacitor                |                        |

| 1   | C3                             | 10 nF, 0402, X7R, ceramic capacitor; not populated |                        |

| 1   | C2                             | 10 μF, Case-C tantalum capacitor                   |                        |

| 4   | L5, L6, L7, L8                 | 0402 size chip ferrite bead                        | Murata BLM15HG102      |

| 4   | L1, L2, L3, L4                 | 82 μH, 0805 size inductor                          | Murata LQH2MCN820K     |

| 1   | R30                            | $50 \Omega$ , not populated                        |                        |

| 1   | U1                             | ADN2530 differential VCSEL driver                  |                        |

| 1   | TOSA (EVAL-ADN2530-AOZ only)   | AOC HFE6192-562, 10 Gbps VCSEL                     |                        |

### **ORDERING GUIDE**

| Model                         | Description                                              |

|-------------------------------|----------------------------------------------------------|

| EVAL-ADN2530-AOZ <sup>1</sup> | Optical Evaluation Board with a VCSEL Laser Populated    |

| EVAL-ADN2530-ANZ <sup>1</sup> | Optical Evaluation Board Without a VCSEL Laser Populated |

<sup>&</sup>lt;sup>1</sup> Z = RoHS Compliant Part.

### **ESD CAUTION**

**ESD (electrostatic discharge) sensitive device.**Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

**NOTES**

| EV | ΔΙ | _ \D | וח | 17 | 53 | N |

|----|----|------|----|----|----|---|

| LV | ML | м    | υı | 12 | JJ | u |

NOTES