# Analog Devices Welcomes Hittite Microwave Corporation

NO CONTENT ON THE ATTACHED DOCUMENT HAS CHANGED

www.analog.com

www.hittite.com

## THIS PAGE INTENTIONALLY LEFT BLANK

#### Typical Applications

The HMC952LP5GE is ideal for:

- Point-to-Point Radios

- Point-to-Multi-Point Radios

- SATCOM

#### **Features**

+35 dBm Pout @ 27% PAE

High P1dB Output Power: +34 dBm

High Gain: 33 dB

High Output IP3: +43 dBm

Supply Voltage: Vdd = +6V @ 1400 mA

50 Ohm Matched Input/Output

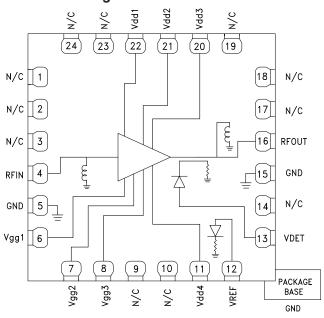

#### **Functional Diagram**

#### **General Description**

The HMC952LP5GE is a four-stage GaAs pHEMT MMIC Medium Power Amplifier with a temperature compensated on-chip power detector which operates between 9 and 14 GHz. The amplifier provides 33 dB of gain and +35 dBm of saturated output power at 27% PAE from a +6V supply. With up to +43 dBm IP3 the HMC952LP5GE is ideal for linear applications such as point-to-point and point-to-multi-point radios or SATCOM applications demanding +35 dBm of efficient saturated output power. The RF I/Os are internally matched to 50 Ohms.

### Electrical Specifications, $T_A = +25^{\circ}$ C, Vdd1, Vdd2, Vdd3, Vdd4 = +6V, Idd = 1400 mA [1]

| Parameter                                    | Min.   | Тур. | Max. | Min.    | Тур. | Max. | Units  |

|----------------------------------------------|--------|------|------|---------|------|------|--------|

| Frequency Range                              | 9 - 10 |      |      | 10 - 14 |      |      | GHz    |

| Gain [2]                                     | 30     | 33   |      | 30      | 33   |      | dB     |

| Gain Variation Over Temperature              |        | 0.05 |      |         | 0.05 |      | dB/ °C |

| Input Return Loss                            |        | 12   |      |         | 15   |      | dB     |

| Output Return Loss                           |        | 9    |      |         | 12   |      | dB     |

| Output Power for 1 dB Compression (P1dB) [2] | 30.5   | 33   |      | 31.5    | 34   |      | dBm    |

| Saturated Output Power (Psat) [2]            |        | 34.5 |      |         | 35   |      | dBm    |

| Output Third Order Intercept (IP3) [2] [3]   |        | 42   |      |         | 43   |      | dBm    |

| Total Supply Current                         |        | 1400 |      |         | 1400 |      | mA     |

<sup>[1]</sup> Adjust Vgg between -2 to 0V to achieve Idd = 1400 mA typical.

<sup>[2]</sup> Board loss subtracted out.

<sup>[3]</sup> Measurement taken at Pout / tone = +20 dBm.

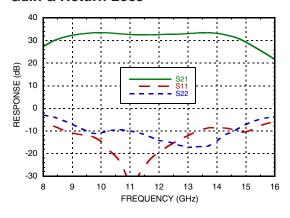

#### Gain & Return Loss

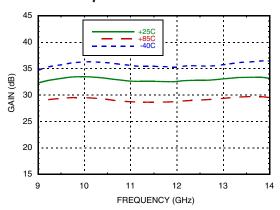

#### Gain vs. Temperature

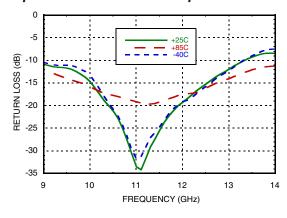

#### Input Return Loss vs. Temperature

#### **Output Return Loss vs. Temperature**

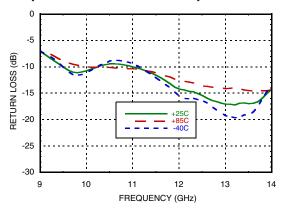

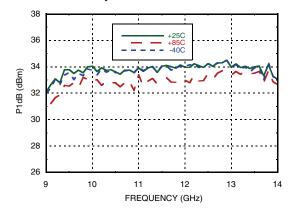

#### P1dB vs. Temperature

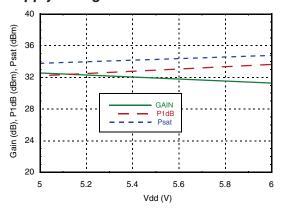

#### P1dB vs Supply Voltage

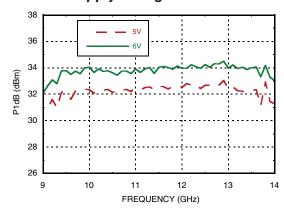

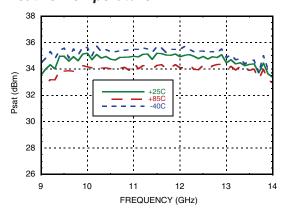

#### Psat vs. Temperature

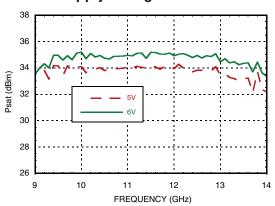

#### Psat vs. Supply Voltage

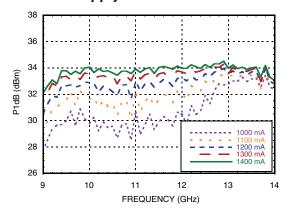

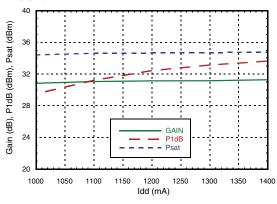

#### P1dB vs. Supply Current

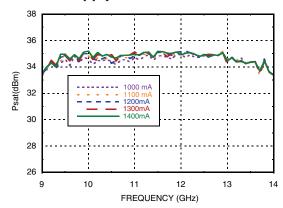

Psat vs. Supply Current

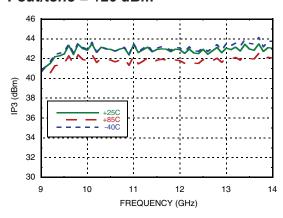

# Output IP3 vs. Temperature, Pout/tone = +20 dBm

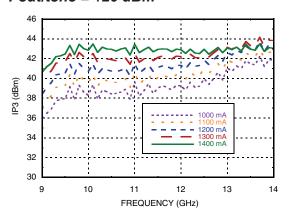

Output IP3 vs. Supply Current, Pout/tone = +20 dBm

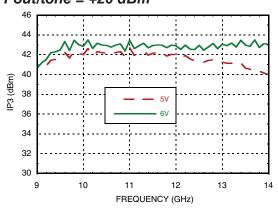

Output IP3 vs. Supply Voltage, Pout/tone = +20 dBm

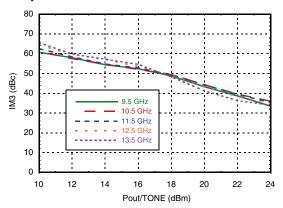

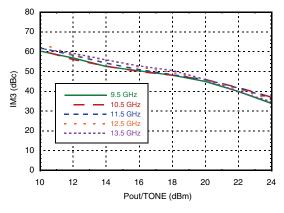

Output IM3 @ Vdd = +5V

#### Output IM3 @ Vdd = +6V

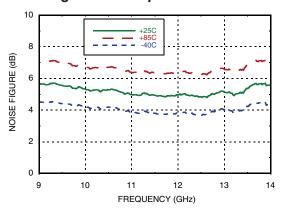

#### Noise Figure vs. Temperature

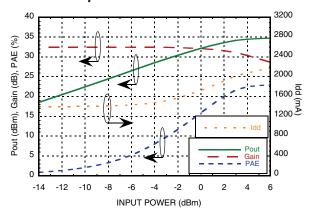

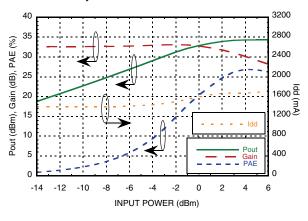

#### Power Compression @ 9.5 GHz

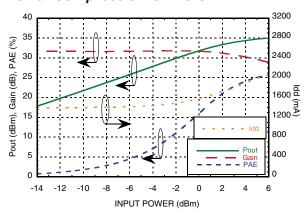

#### **Power Compression @ 11.5 GHz**

#### Power Compression @ 13.5 GHz

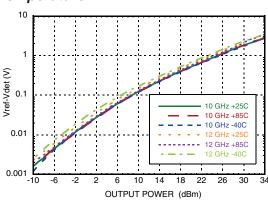

#### Detector Voltage vs. Frequency & Temperature

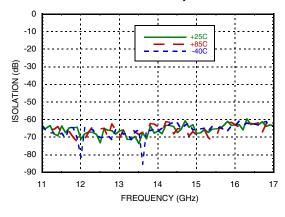

#### Reverse Isolation vs. Temperature

Gain & Power vs. Supply Current @ 11.5 GHz

#### Gain & Power vs. Supply Voltage @ 11.5 GHz

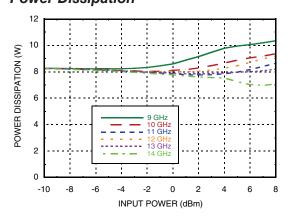

#### **Power Dissipation**

#### **Absolute Maximum Ratings**

| Drain Bias Voltage (Vdd)                                      | +8 Vdc               |

|---------------------------------------------------------------|----------------------|

| Gate Bias Voltage (Vgg)                                       | -3 - 0 Vdc           |

| RF Input Power (RFIN)                                         | +24 dBm              |

| Channel Temperature                                           | 150 °C               |

| Continuous Pdiss (T= 85 °C)<br>(derate 137 mW/°C above 85 °C) | 8.9 W                |

| Thermal Resistance (channel to die bottom)                    | 7.3 °C/W             |

| Storage Temperature                                           | -65 to 150°C         |

| Operating Temperature                                         | -55 to 85 °C         |

| ESD Sensitivity (HBM)                                         | Class 0, Passed 150V |

#### Typical Supply Current vs. Vdd

| Vdd (V) | ldd (mA) |  |  |

|---------|----------|--|--|

| +5      | 1400     |  |  |

| +6      | 1400     |  |  |

Adjust Vgg1 to achieve Idd = 1400 mA

ELECTROSTATIC SENSITIVE DEVICE OBSERVE HANDLING PRECAUTIONS

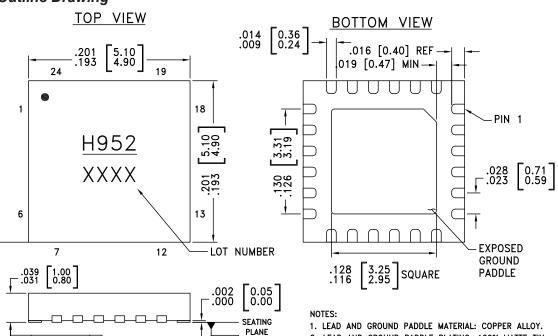

#### **Outline Drawing**

- 2. LEAD AND GROUND PADDLE PLATING: 100% MATTE TIN.

- 3. DIMENSIONS ARE IN INCHES [MILLIMETERS].

- 4. LEAD SPACING TOLERANCE IS NON-CUMULATIVE.

- 5. PAD BURR LENGTH SHALL BE 0.15mm MAX. PAD BURR HEIGHT SHALL BE 0.25mm MAX.

- 6. PACKAGE WARP SHALL NOT EXCEED 0.05mm

- ALL GROUND LEADS AND GROUND PADDLE MUST BE SOLDERED TO PCB RF GROUND.

#### Package Information

○ .003[0.08] C

| Part Number Package Body Material |             | Lead Finish                                        | MSL Rating [2] | Package Marking [1] |              |

|-----------------------------------|-------------|----------------------------------------------------|----------------|---------------------|--------------|

|                                   | HMC952LP5GE | RoHS-compliant Low Stress Injection Molded Plastic | 100% matte Sn  | MSL3                | H952<br>XXXX |

<sup>[1] 4-</sup>Digit lot number XXXX

<sup>[2]</sup> Max peak reflow temperature of 260 °C

#### **Pin Descriptions**

| Pin Number                          | Function                  | Description                                                                                                                               | Interface Schematic                            |  |

|-------------------------------------|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|--|

| 1-3, 9, 10,<br>14, 17-19,<br>23, 24 | N/C                       | These pins are not connected internally, however all data shown herein was measured with these pins connected to RF/DC ground externally. |                                                |  |

| 4                                   | RFIN                      | This pin is DC coupled and matched to 50 Ohms.                                                                                            | RFIN O                                         |  |

| 5, 15                               | GND                       | These pins and package bottom must be connected to RF/DC ground.                                                                          | GND                                            |  |

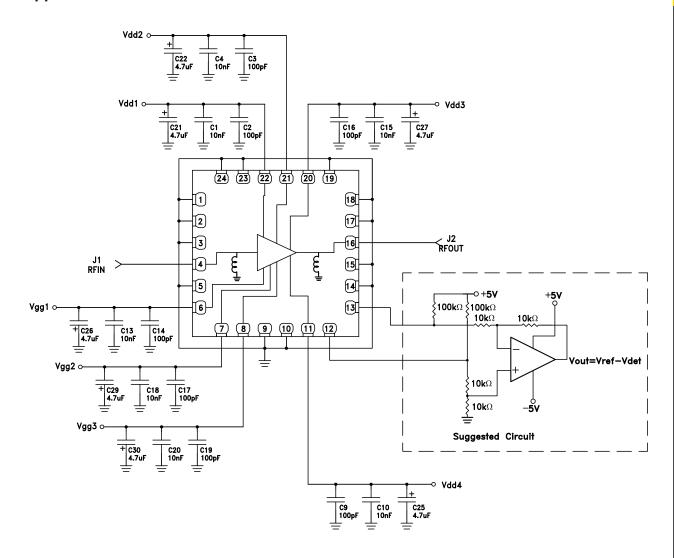

| 6-8                                 | Vgg1, Vgg2,<br>Vgg3       | Gate control for amplifier External bypass capacitors of 100pF, 10nF and 4.7uF are required.                                              | Vgg1-3                                         |  |

| 11, 20-22                           | Vdd4, Vdd3, Vdd2,<br>Vdd1 | Drain bias voltage for amplifier. external bypass capacitors of 100pF, 10nF and 4.7uF are required.                                       | Vdd1−4<br>———————————————————————————————————— |  |

| 12                                  | Vref                      | DC bias of diode biased through external resistor , used for temperature compensation of Vdet. See application circuit.                   |                                                |  |

| 13                                  | Vdet                      | DC voltage representing RF output power rectified by diode which is biased through an external resistor. See application circut.          |                                                |  |

| 16                                  | RFOUT                     | This pin is DC coupled and matched to 50 Ohms                                                                                             | ─────────────────────────────────────          |  |

#### **Application Circuit**

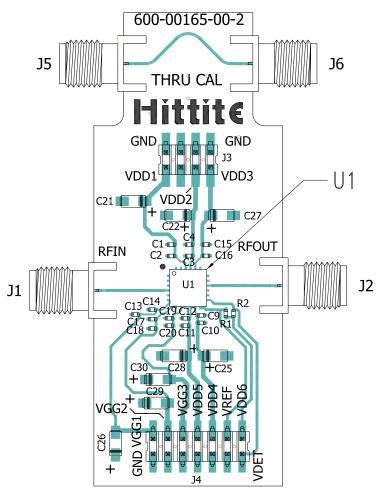

#### **Evaluation PCB**

#### List of Materials for Evaluation PCB EVAL01-HMC952LP5GE [1]

| Item                                       | Description                 |

|--------------------------------------------|-----------------------------|

| J1, J2, J5, J6                             | K Connector SRI             |

| J3, J4                                     | DC Pin                      |

| C2, C3, C9, C12,<br>C14, C16, C17,<br>C19  | 100 pF Capacitor, 0402 Pkg. |

| C1, C4, C10, C11,<br>C13, C15, C18,<br>C20 | 10 nF Capacitor, 0402 Pkg.  |

| C21, C22, C25<br>- C30                     | 4.7uF Capacitor, Case A.    |

| U1                                         | HMC952LP5GE Power Amplifier |

| PCB                                        | 600-00163-00 Evaluation PCB |

[1] Reference this number when ordering complete evaluation PCB

[2] Circuit Board Material: Rogers 4350 or Arlon FR4

The circuit board used in the application should use RF circuit design techniques. Signal lines should have 50 Ohm impedance while the package ground leads and exposed paddle should be connected directly to the ground plane similar to that shown. A sufficient number of via holes should be used to connect the top and bottom ground planes. The evaluation circuit board shown is available from Hittite upon request.

Notes: