## Wideband, Low Noise Amplifier, Single Positive Supply, 0.01 GHz to 26.5 GHz

### **Data Sheet**

#### **FEATURES**

#### Single positive supply

Low noise figure: 2.5 dB typical from 0.01 GHz to 14 GHz High gain: 17.5 dB typical from 0.01 GHz to 14 GHz OP1dB: 13.5 dBm typical from 0.01 GHz to 20 GHz High OIP3: 26 dBm typical from 0.01 GHz to 14 GHz RoHS-compliant, 4 mm × 4 mm, 24-lead LFCSP

#### **APPLICATIONS**

Test instrumentation Military Communications

## ADL9005

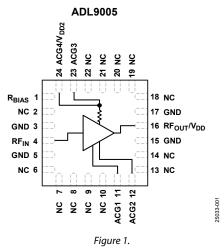

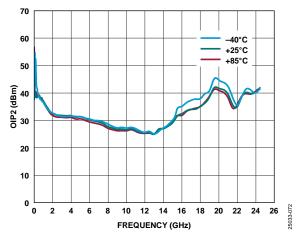

#### FUNCTIONAL BLOCK DIAGRAM

#### **GENERAL DESCRIPTION**

The ADL9005 is a gallium arsenide (GaAs), monolithic microwave integrated circuit (MMIC), pseudomorphic high electron mobility transistor (pHEMT), wideband, LNA that operates from 0.01 to 26.5 GHz. The ADL9005 provides a typical gain of 17.5 dB from 0.01 GHz to 14 GHz with a positive gain slope from 14 GHz to 20 GHz, a 13.5 dBm typical output power at 1 dB compression (OP1dB) from 0.01 GHz to 20 GHz, a 2.5 dB typical noise figure from 0.01 GHz to 14 GHz, and a typical output third-order intercept (OIP3) of 26 dBm from 0.01 GHz to 14 GHz, requiring only 80 mA from a 5 V supply voltage. The saturated output power (P<sub>SAT</sub>) of up to 16 dBm enables the LNA to function as a local oscillator (LO) driver for many of Analog Devices, Inc., balanced, inphase/quadrature (I/Q) or image rejection mixers. The ADL9005 also features inputs and outputs (I/Os) that are internally matched to 50  $\Omega$ , making it ideal for surface-mounted technology (SMT)-based, high capacity microwave radio applications.

The ADL9005 is housed in a RoHS-compliant, 4 mm  $\times$  4 mm, LFCSP.

Multifunction pin names may be referenced by their relevant function only.

#### Rev. 0

#### Document Feedback

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.Tel: 781.329.4700©2021 Analog Devices, Inc. All rights reserved.Technical Supportwww.analog.com

## **TABLE OF CONTENTS**

| Features                              |

|---------------------------------------|

| Applications 1                        |

| Functional Block Diagram 1            |

| General Description                   |

| Revision History 2                    |

| Specifications                        |

| 0.01 GHz to 14 GHz                    |

| 14 GHz to 20 GHz                      |

| 20 GHz to 26.5 GHz                    |

| DC Specifications 4                   |

| Absolute Maximum Ratings 5            |

| Thermal Resistance                    |

| Electrostatic Discharge (ESD) Ratings |

| ESD Caution                           |

| Pin Configuration and Function Descriptions6             |

|----------------------------------------------------------|

| Interface Schematics7                                    |

| Typical Performance Characteristics8                     |

| Biasing Through the ACG4/V <sub>DD2</sub> Pin18          |

| Theory of Operation 19                                   |

| Applications Information                                 |

| Basic Connections                                        |

| Biasing the ADL9005 by Using the LTM8020 21              |

| Providing Drain Bias                                     |

| Providing Drain Bias Through the ACG4/V $_{\rm DD2}$ Pin |

| Power-Up and Power-Down Sequencing                       |

| Outline Dimensions                                       |

| Ordering Guide 24                                        |

### **REVISION HISTORY**

2/2021—Revision 0: Initial Version

### **SPECIFICATIONS**

#### 0.01 GHz TO 14 GHz

Drain voltage ( $V_{DD}$ ) = 5 V, bias voltage ( $V_{BIAS}$ ) = 5 V, total current ( $I_{DQ}$ ) = 80 mA,  $R_{BIAS}$  = 300  $\Omega$ , and  $T_A$  = 25°C, unless otherwise noted.

| Table 1.                        |      |        |     |       |                                                                  |

|---------------------------------|------|--------|-----|-------|------------------------------------------------------------------|

| Parameter                       | Min  | Тур    | Max | Unit  | Test Conditions/Comments                                         |

| FREQUENCY RANGE                 | 0.01 |        | 14  | GHz   |                                                                  |

| GAIN                            | 15.5 | 17.5   |     | dB    |                                                                  |

| Gain Variation Over Temperature |      | 0.0077 |     | dB/°C |                                                                  |

| RETURN LOSS                     |      |        |     |       |                                                                  |

| Input                           |      | 15     |     | dB    |                                                                  |

| Output                          |      | 14     |     | dB    |                                                                  |

| OUTPUT                          |      |        |     |       |                                                                  |

| OP1dB                           | 11.5 | 13.5   |     | dBm   |                                                                  |

| P <sub>SAT</sub>                |      | 16     |     | dBm   |                                                                  |

| OIP3                            |      | 26     |     | dBm   | Measurement taken at output power ( $P_{OUT}$ ) per tone = 0 dBm |

| NOISE FIGURE                    |      | 2.5    |     | dB    |                                                                  |

#### 14 GHz TO 20 GHz

$V_{\text{DD}}$  = 5 V,  $V_{\text{BIAS}}$  = 5 V,  $I_{\text{DQ}}$  = 80 mA,  $R_{\text{BIAS}}$  = 300  $\Omega,$  and  $T_{\text{A}}$  = 25°C, unless otherwise noted.

#### Table 2.

| Parameter                       | Min  | Тур    | Max | Unit  | Test Conditions/Comments                        |

|---------------------------------|------|--------|-----|-------|-------------------------------------------------|

| FREQUENCY RANGE                 | 14   |        | 20  | GHz   |                                                 |

| GAIN                            | 16.5 | 18.5   |     | dB    |                                                 |

| Gain Variation Over Temperature |      | 0.0127 |     | dB/°C |                                                 |

| RETURN LOSS                     |      |        |     |       |                                                 |

| Input                           |      | 15     |     | dB    |                                                 |

| Output                          |      | 14     |     | dB    |                                                 |

| OUTPUT                          |      |        |     |       |                                                 |

| OP1dB                           | 11   | 13.5   |     | dBm   |                                                 |

| P <sub>SAT</sub>                |      | 15     |     | dBm   |                                                 |

| OIP3                            |      | 25     |     | dBm   | Measurement taken at $P_{OUT}$ per tone = 0 dBm |

| NOISE FIGURE                    |      | 3      |     | dB    |                                                 |

#### 20 GHz TO 26.5 GHz

$V_{\text{DD}}$  = 5 V,  $V_{\text{BIAS}}$  = 5 V,  $I_{\text{DQ}}$  = 80 mA,  $R_{\text{BIAS}}$  = 300  $\Omega,$  and  $T_{\text{A}}$  = 25°C, unless otherwise noted.

#### Table 3.

| Parameter                       | Min | Тур    | Мах  | Unit  | Test Conditions/Comments                        |

|---------------------------------|-----|--------|------|-------|-------------------------------------------------|

| FREQUENCY RANGE                 | 20  |        | 26.5 | GHz   |                                                 |

| GAIN                            | 17  | 19     |      | dB    |                                                 |

| Gain Variation Over Temperature |     | 0.0214 |      | dB/°C |                                                 |

| RETURN LOSS                     |     |        |      |       |                                                 |

| Input                           |     | 15     |      | dB    |                                                 |

| Output                          |     | 14     |      | dB    |                                                 |

| OUTPUT                          |     |        |      |       |                                                 |

| OP1dB                           | 8.5 | 11.5   |      | dBm   |                                                 |

| P <sub>SAT</sub>                |     | 14     |      | dBm   |                                                 |

| OIP3                            |     | 22     |      | dBm   | Measurement taken at $P_{OUT}$ per tone = 0 dBm |

| NOISE FIGURE                    |     | 4      |      | dB    |                                                 |

#### **DC SPECIFICATIONS**

#### Table 4. Parameter Min Мах Unit Тур $V_{\text{DD}}$ 3 5 6 ۷ CURRENT 80 Idq mΑ $Amplifier (I_{DQ\_AMP})$ 73.6 mΑ RBIAS (IDQ\_BIAS) 6.4 mΑ

### **ABSOLUTE MAXIMUM RATINGS**

#### Table 5.

| Parameter                                                                                            | Rating          |

|------------------------------------------------------------------------------------------------------|-----------------|

| V <sub>DD</sub>                                                                                      | 7 V             |

| RF <sub>IN</sub> Power                                                                               | 22 dBm          |

| Continuous Power Dissipation ( $P_{DISS}$ ),<br>T <sub>A</sub> = 85°C (Derate 12.5 mW/°C Above 85°C) | 1.125 W         |

| Temperature                                                                                          |                 |

| Peak Reflow, Moisture Sensitivity Level (MSL) <sup>1</sup>                                           | 260°C           |

| Junction to Maintain 1,000,000 Hour<br>Meant Time to Failure (MTTF)                                  | 175°C           |

| Nominal Junction ( $T_A = 85^{\circ}C$ , $V_{DD} = 5 V$ ,<br>$I_{DQ} = 80 \text{ mA}$ )              | 117°C           |

| Storage Range                                                                                        | −65°C to +150°C |

| Operating Range                                                                                      | –40°C to +85°C  |

<sup>1</sup> See the Ordering Guide for more information.

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

#### THERMAL RESISTANCE

Thermal performance is directly linked to printed circuit board (PCB) design and operating environment. Careful attention to PCB thermal design is required.

$\theta_{\text{JC}}$  is the junction to case thermal resistance.

#### Table 6. Thermal Resistance

| Package  | θις | Unit |

|----------|-----|------|

| CP-24-15 | 80  | °C/W |

#### **ELECTROSTATIC DISCHARGE (ESD) RATINGS**

The following ESD information is provided for handling of ESD sensitive devices in an ESD protected area only.

Human body model (HBM) per ANSI/ESDA/JEDEC JS-001.

#### ESD Ratings for ADL9005

#### Table 7. ADL9005, 24-Lead LFCSP

| ESD Model | Withstand Threshold (V) | Class |

|-----------|-------------------------|-------|

| HBM       | ±250                    | 1A    |

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

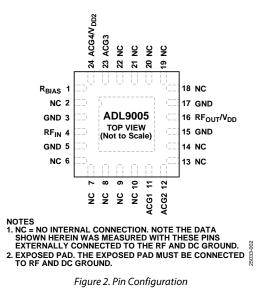

### **PIN CONFIGURATION AND FUNCTION DESCRIPTIONS**

#### **Table 8. Pin Function Descriptions**

| Pin No.                      | Mnemonic                           | Description                                                                                                                                                                                                                                |  |  |  |

|------------------------------|------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1                            | Rbias                              | Current Mirror Bias Resistor Pin. Use the $R_{BIAS}$ pin to set the $I_{DQ}$ by connecting an external bias resistor as defined in Table 9. Refer to Figure 74 for the bias resistor connection. See Figure 3 for the interface schematic. |  |  |  |

| 2, 6 to 10, 13, 14, 18 to 22 | NC                                 | No Internal Connection. Note the data shown herein was measured with these pins externally connected to the RF and dc ground.                                                                                                              |  |  |  |

| 3, 5, 15, 17                 | GND                                | Ground. The GND pins must be connected to RF and dc ground. See Figure 4 for the interface schematic.                                                                                                                                      |  |  |  |

| 4                            | RF <sub>IN</sub>                   | RF Input. The RF <sub>IN</sub> pin is dc-coupled and matched to 50 Ω. See Figure 5 for the interface schematic.                                                                                                                            |  |  |  |

| 11                           | ACG1                               | AC Grounding 1. A capacitor is required on the ACG1 pin to provide low frequency decoupling.<br>Refer to Figure 74 for the capacitor value. See Figure 5 for the interface schematic.                                                      |  |  |  |

| 12                           | ACG2                               | AC Grounding 2. A capacitor is required on the ACG2 pin to provide low frequency decoupling.<br>Refer to Figure 74 for the capacitor value. See Figure 5 for the interface schematic.                                                      |  |  |  |

| 16                           | RF <sub>OUT</sub> /V <sub>DD</sub> | RF Output (RF <sub>OUT</sub> )/Drain Voltage for Amplifier (V <sub>DD</sub> ). The RF <sub>OUT</sub> /V <sub>DD</sub> pin is dc-coupled and matched to 50 $\Omega$ . See Figure 6 for the interface schematic.                             |  |  |  |

| 23                           | ACG3                               | AC Grounding 3. A capacitor is required on the ACG3 pin to provide low frequency decoupling.<br>Refer to Figure 74 for the capacitor value. See Figure 6 for the interface schematic.                                                      |  |  |  |

| 24                           | ACG4/V <sub>DD2</sub>              | AC Grounding 4 (ACG4). A capacitor is required on the ACG4 pin to provide low frequency decoupling. Refer to Figure 74 for the capacitor value. See Figure 6 for the interface schematic.                                                  |  |  |  |

|                              |                                    | Optional Drain Voltage for the Amplifier that Requires a Higher Voltage ( $V_{DD2}$ ). Do not use the $V_{DD2}$ pin simultaneously with $RF_{OUT}/V_{DD}$ . See Figure 6 for the interface schematic.                                      |  |  |  |

|                              | EPAD                               | Exposed Pad. The exposed pad must be connected to RF and dc ground.                                                                                                                                                                        |  |  |  |

#### **INTERFACE SCHEMATICS**

Figure 3. RBIAS Interface Schematic

Figure 5. RF<sub>IN</sub>, ACG1, and ACG2 Interface Schematic

Figure 6. RFout/VDD, ACG3, and ACG4/VDD2 Interface Schematic

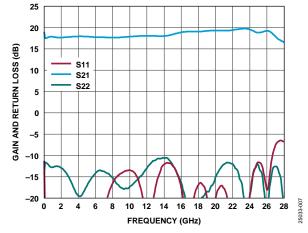

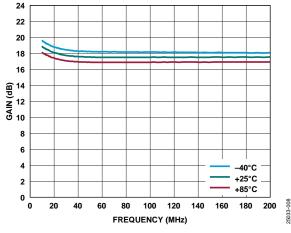

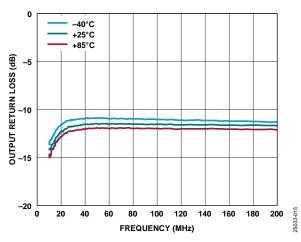

### **TYPICAL PERFORMANCE CHARACTERISTICS**

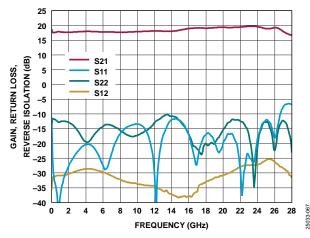

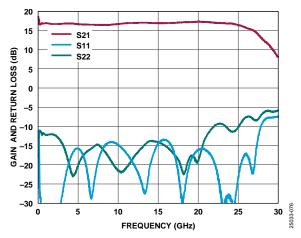

Figure 7. Gain and Return Loss vs. Frequency, 0.01 GHz to 28 GHz,  $V_{DD} = 5 V$ ,  $V_{BIAS} = 5 V$ ,  $I_{DQ} = 80 \text{ mA}$ ,  $R_{BIAS} = 300 \Omega$  (S22 Is the Output Return Loss, S11 Is the Input Return Loss, and S21 Is the Gain)

Figure 8. Gain vs. Frequency for Various Temperatures, 10 MHz to 200 MHz,  $V_{DD} = 5 V$ ,  $V_{BIAS} = 5 V$ ,  $I_{DQ} = 80 mA$ ,  $R_{BIAS} = 300 \Omega$

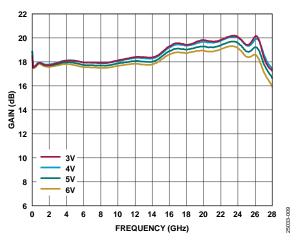

Figure 9. Gain vs. Frequency for Various  $V_{DD}$ ,  $I_{DQ} = 80$  mA, 0.01 GHz to 28 GHz

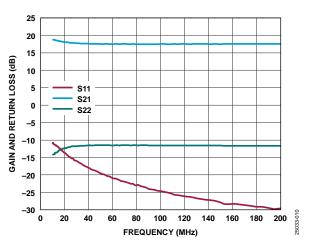

Figure 10. Gain and Return Loss vs. Frequency, 10 MHz to 200 MHz,  $V_{\text{DD}}$  = 5 V,  $V_{\text{BIAS}}$  = 5 V,  $I_{\text{DQ}}$  = 80 mA,  $R_{\text{BIAS}}$  = 300  $\Omega$

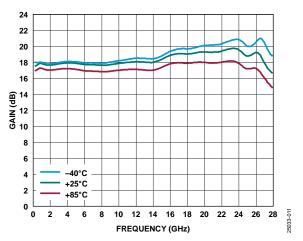

Figure 11. Gain vs. Frequency for Various Temperatures, 0.2 GHz to 28 GHz,  $V_{DD} = 5 V$ ,  $V_{BIAS} = 5 V$ ,  $I_{DQ} = 80 \text{ mA}$ ,  $R_{BIAS} = 300 \Omega$

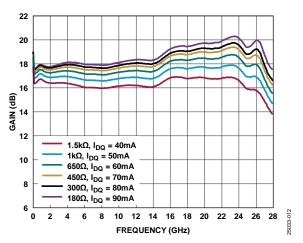

Figure 12. Gain vs. Frequency for Various Bias Resistor Values and  $I_{DQ}$ 10 MHz to 28 GHz,  $V_{DD} = 5 V$

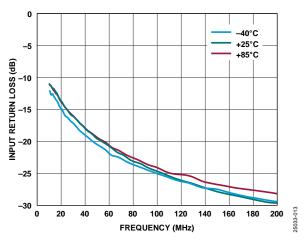

Figure 13. Input Return Loss vs. Frequency for Various Temperatures, 10 MHz to 200 MHz, V\_{DD} = 5 V, V\_{BIAS} = 5 V, I\_{DQ} = 80 mA, R\_{BIAS} = 300 \Omega

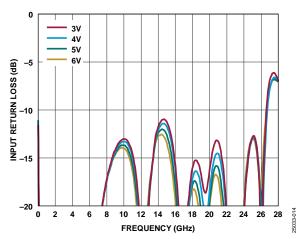

Figure 14. Input Return Loss vs Frequency for Various  $V_{DD}$ ,  $I_{DQ} = 80$  mA, 0.01 GHz to 28 GHz

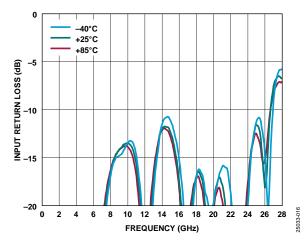

Figure 16. Input Return Loss vs. Frequency for Various Temperatures, 0.2 GHz to 28 GHz,  $V_{DD}$  = 5 V,  $V_{BIAS}$  = 5 V,  $I_{DQ}$  = 80 mA,  $R_{BIAS}$  = 300  $\Omega$

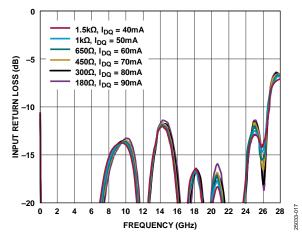

Figure 17. Input Return Loss vs. Frequency for Various Bias Resistor Values and  $I_{DQ}$  0.01 GHz to 28 GHz,  $V_{DD}$  = 5 V

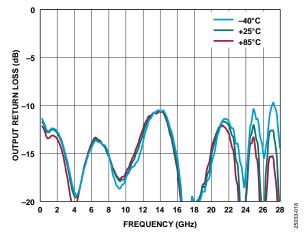

Figure 18. Output Return Loss vs. Frequency for Various Temperatures, 0.2 GHz to 28 GHz,  $V_{DD} = 5 V$ ,  $V_{BIAS} = 5 V$ ,  $I_{DQ} = 80 \text{ mA}$ ,  $R_{BIAS} = 300 \Omega$

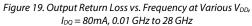

Figure 20. Reverse Isolation (S12) vs. Frequency for Various Temperatures, 10 MHz to 200 MHz,  $V_{DD}$  = 5 V,  $V_{BIAS}$  = 5 V,  $I_{DQ}$  = 80 mA,  $R_{BIAS}$  = 300  $\Omega$

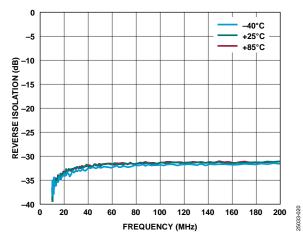

Figure 21. Reverse Isolation vs. Frequency for Various  $V_{DD}$ ,  $I_{DQ} = 80$  mA, 0.01 GHz to 28 GHz

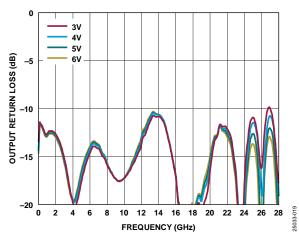

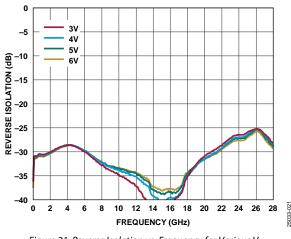

Figure 22. Output Return Loss vs. Frequency for Various Bias Resistor Values and I<sub>DO</sub>, 0.01 GHz to 28 GHz, V<sub>DD</sub> = 5 V

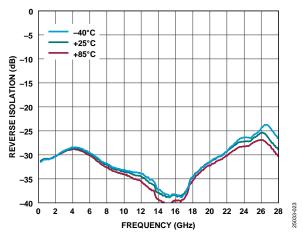

Figure 23. Reverse Isolation vs. Frequency for Various Temperatures, 0.2 GHz to 28 GHz,  $V_{DD} = 5 V$ ,  $V_{BIAS} = 5 V$ ,  $I_{DQ} = 80 \text{ mA}$ ,  $R_{BIAS} = 300 \Omega$

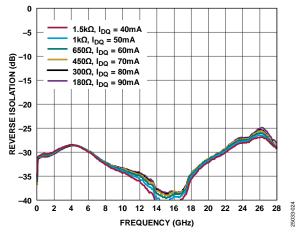

Figure 24. Reverse Isolation vs. Frequency for Various Bias Resistor Values and  $I_{DQ}$ , 0.01 GHz to 28 GHz,  $V_{DD} = 5 V$

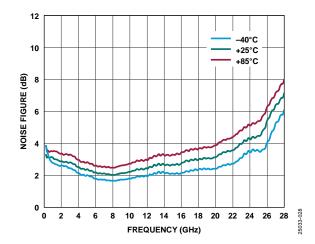

Figure 25. Noise Figure vs. Frequency for Various Temperatures, 10 MHz to 200 MHz,  $V_{DD} = 5 V$ ,  $V_{BIAS} = 5 V$ ,  $I_{DQ} = 80 \text{ mA}$ ,  $R_{BIAS} = 300 \Omega$

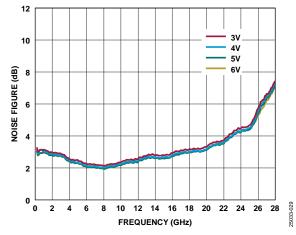

Figure 26. Noise Figure vs. Frequency for Various  $V_{DD}$ ,  $I_{DQ} = 80$  mA, 10 MHz to 200 MHz

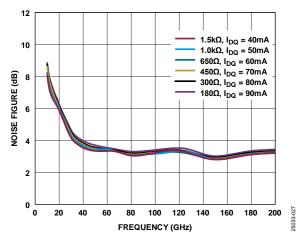

Figure 27. Noise Figure vs. Frequency for Various Bias Resistor Values and  $I_{DQ}$ , 10 MHz to 200 MHz,  $V_{DD} = 5 V$ ,  $V_{BIAS} = 5 V$

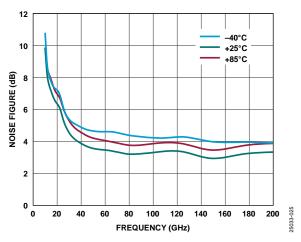

Figure 28. Noise Figure vs. Frequency for Various Temperatures, 0.2 GHz to 28 GHz,  $V_{DD} = 5 V$ ,  $V_{BIAS} = 5 V I_{DQ} = 80 \text{ mA}$ ,  $R_{BIAS} = 300 \Omega$

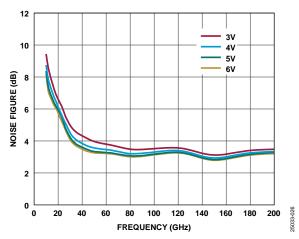

Figure 29. Noise Figure vs. Frequency for Various  $V_{DD}$ ,  $I_{DQ} = 80$  mA, 0.2 GHz to 28 GHz

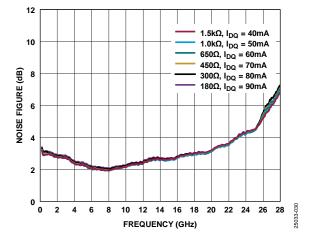

Figure 30. Noise Figure vs. Frequency for Various Bias Resistor Values and  $I_{DQ}$ , 0.2 GHz to 28 GHz,  $V_{DD} = 5 V$ ,  $V_{BIAS} = 5 V$

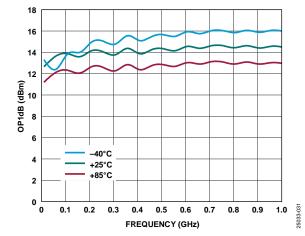

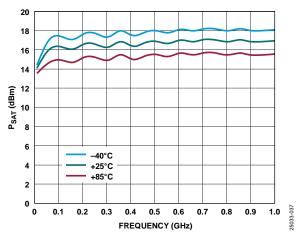

Figure 31. OP1dB vs. Frequency for Various Temperatures, 0.01 GHz to 1 GHz,  $V_{DD} = 5 V$ ,  $V_{BIAS} = 5 V$ ,  $I_{DQ} = 80 \text{ mA}$ ,  $R_{BIAS} = 300 \Omega$

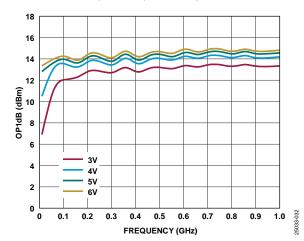

Figure 32. OP1dB vs. Frequency for Various Supply Voltages,  $I_{DQ} = 80$  mA, 0.01 GHz to 1 GHz

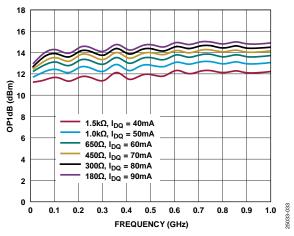

Figure 33. OP1dB vs. Frequency for Various Bias Resistor Values and  $I_{DQ}$ , 0.01 GHz to 1 GHz,  $V_{DD} = 5 V$ ,  $V_{BIAS} = 5 V$

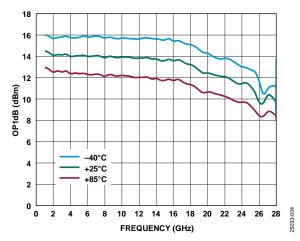

Figure 34. OP1dB vs. Frequency for Various Temperatures, 1 GHz to 28 GHz,  $V_{DD} = 5 V$ ,  $V_{BIAS} = 5 V$ ,  $I_{DQ} = 80 \text{ mA}$ ,  $R_{BIAS} = 300 \Omega$

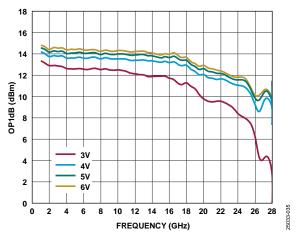

Figure 35. OP1dB vs. Frequency for Various Supply Voltages,  $I_{DQ}$  = 80 mA, 1 GHz to 28 GHz

Figure 36. OP1dB vs. Frequency for Various Bias Resistor Values and  $I_{DQ_{r}}$ 1 GHz to 28 GHz,  $V_{DD} = 5 V$ ,  $V_{BIAS} = 5 V$

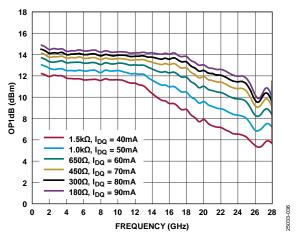

Figure 37. P<sub>SAT</sub> vs. Frequency for Various Temperatures, 0.01 GHz to 1 GHz,  $V_{DD}$  = 5 V,  $V_{BIAS}$  = 5 V,  $I_{DQ}$  = 80 mA,  $R_{BIAS}$  = 300  $\Omega$

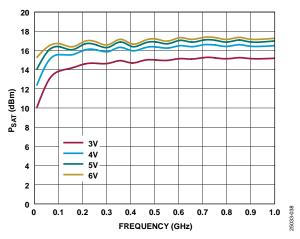

Figure 38. P<sub>SAT</sub> vs. Frequency for Various V<sub>DD</sub>, I<sub>DQ</sub> = 80 mA, 0.01 GHz to 1 GHz

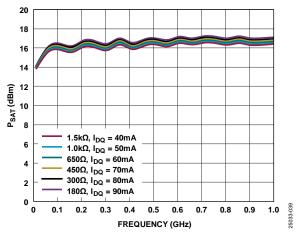

Figure 39.  $P_{SAT}$  vs. Frequency for Various Bias Resistor Values and  $I_{DQ}$ , 0.01 GHz to 1 GHz,  $V_{DD} = 5 V$ ,  $V_{BIAS} = 5 V$

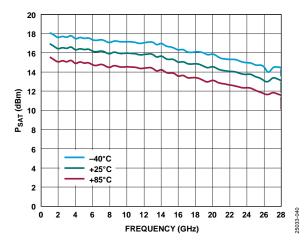

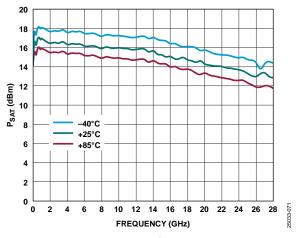

Figure 40.  $P_{SAT}$  vs. Frequency for Various Temperatures, 1 GHz to 28 GHz,  $V_{DD} = 5 V$ ,  $V_{BIAS} = 5 V$ ,  $I_{DQ} = 80 \text{ mA}$ ,  $R_{BIAS} = 300 \Omega$

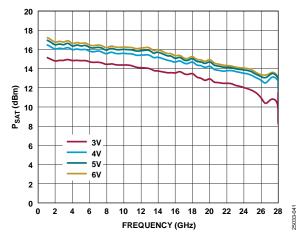

Figure 41.  $P_{SAT}$  vs. Frequency for Various  $V_{DD}$ ,  $I_{DQ} = 80$  mA, 1 GHz to 28 GHz

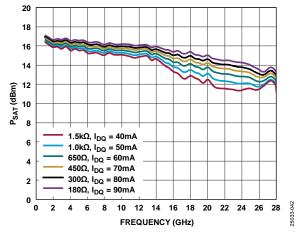

Figure 42.  $P_{SAT}$  vs. Frequency for Various Bias Resistor Values and  $I_{DQ_r}$ 1 GHz to 28 GHz,  $V_{DD} = 5 V$ ,  $V_{BIAS} = 5 V$

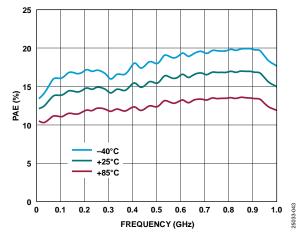

Figure 43. Power Added Efficiency (PAE) vs. Frequency for Various Temperatures, 0.01 GHz to 1 GHz,  $V_{DD} = 5 V$ ,  $V_{BIAS} = 5 V$ ,  $I_{DQ} = 80 \text{ mA}$ ,  $R_{BIAS} = 300 \Omega$

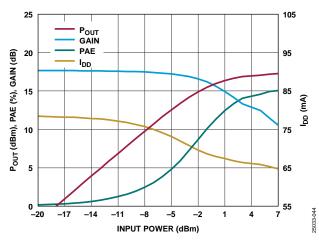

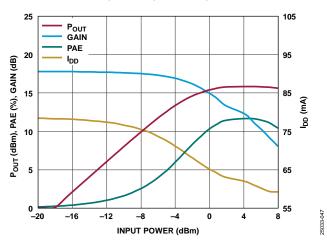

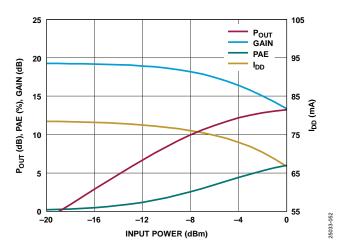

Figure 44. P<sub>OUT</sub>, PAE, Gain, and Drain Current ( $I_{DD}$ ) vs. Input Power, Power Compression at 1 GHz, V<sub>DD</sub> = 5 V, V<sub>BIAS</sub> = 5 V, R<sub>BIAS</sub> = 300  $\Omega$

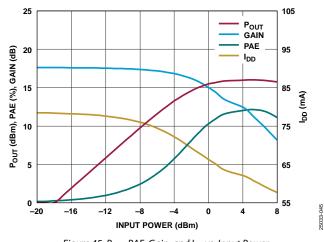

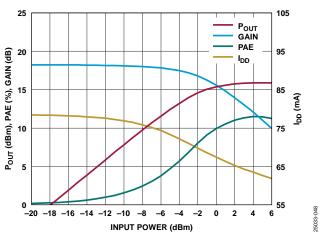

Figure 45.  $P_{OUT}$ , PAE, Gain, and  $I_{DD}$  vs. Input Power, Power Compression at 8 GHz,  $V_{DD} = 5$  V,  $V_{BIAS} = 5$  V,  $R_{BIAS} = 300 \Omega$

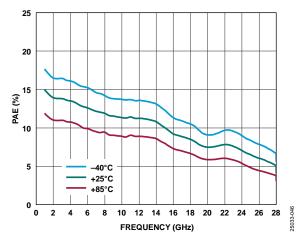

Figure 46. PAE vs. Frequency for Various Temperatures, 1 GHz to 28 GHz,  $V_{DD} = 5 V$ ,  $V_{BIAS} = 5 V$ ,  $I_{DQ} = 80 \text{ mA}$ ,  $R_{BIAS} = 300 \Omega$

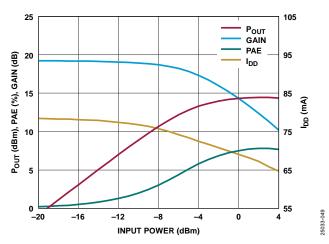

Figure 47.  $P_{OUT_r}$  PAE, Gain, and  $I_{DD}$  vs. Input Power, Power Compression at 10 GHz,  $V_{DD} = 5 V$ ,  $V_{BIAS} = 5 V$ ,  $R_{BIAS} = 300 \Omega$

Figure 48.  $P_{OUT}$ , PAE, Gain, and  $I_{DD}$  vs. Input Power, Power Compression at 14 GHz,  $V_{DD} = 5 V$ ,  $V_{BIAS} = 5 V$ ,  $R_{BIAS} = 300 \Omega$

Figure 49.  $P_{OUT}$ , PAE, Gain, and  $I_{DD}$  vs. Input Power, Power Compression at 20 GHz,  $V_{DD} = 5 V$ ,  $V_{BIAS} = 5 V$ ,  $R_{BIAS} = 300 \Omega$

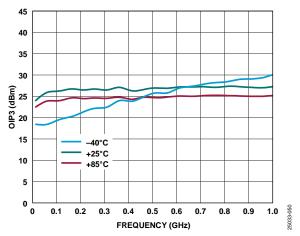

Figure 50. OIP3 vs. Frequency for Various Temperatures, 0.01 GHz to 1 GHz,  $V_{DD}$  = 5 V,  $V_{BIAS}$  = 5 V,  $I_{DQ}$  = 80 mA,  $R_{BIAS}$  = 300  $\Omega$

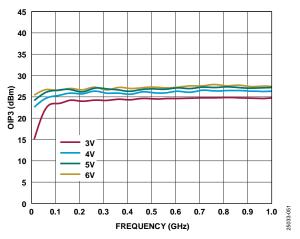

Figure 51. OIP3 vs. Frequency for Various  $V_{DD}$ ,  $I_{DQ} = 80$  mA, 0.01 GHz to 1 GHz

Figure 52.  $P_{OUT}$ , PAE, Gain, and  $I_{DD}$  vs. Input Power, Power Compression at 26 GHz,  $V_{DD}$  = 5 V,  $V_{BIAS}$  = 5 V,  $R_{BIAS}$  = 300  $\Omega$

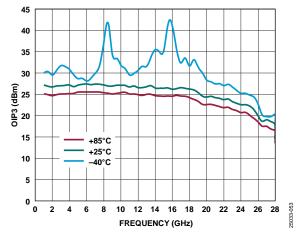

Figure 53. OIP3 vs. Frequency for Various Temperatures, 1 GHz to 28 GHz,  $V_{DD}$  = 5 V,  $V_{BIAS}$  = 5 V,  $I_{DQ}$  = 80 mA,  $R_{BIAS}$  = 300  $\Omega$

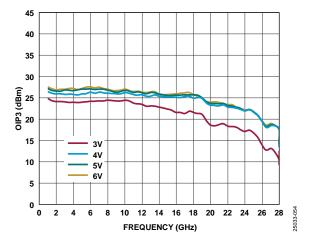

Figure 54. OIP3 vs. Frequency for Various  $V_{DD}$ ,  $I_{DQ} = 80$  mA, 1 GHz to 28 GHz

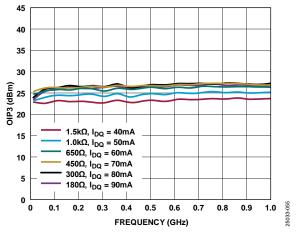

Figure 55. OIP3 vs. Frequency for Various Bias Resistor Values and  $I_{DQr}$ 0.01 GHz to 1 GHz,  $V_{DD} = 5 V$ ,  $V_{BIAS} = 5 V$

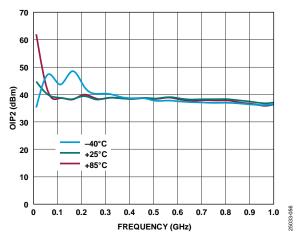

Figure 56. OIP2 vs. Frequency for Various Temperatures, 0.01 GHz to 1 GHz,  $V_{DD}$  = 5 V,  $V_{BIAS}$  = 5 V,  $I_{DQ}$  = 80 mA,  $R_{BIAS}$  = 300  $\Omega$

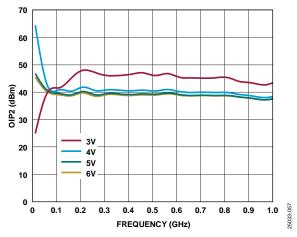

Figure 57. OIP2 vs. Frequency for Various  $V_{DD}$ ,  $I_{DQ} = 80$  mA, 0.01 GHz to 1 GHz

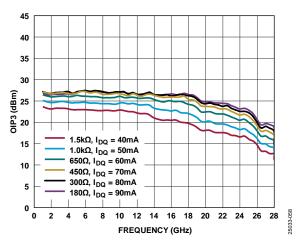

Figure 58. OIP3 vs. Frequency for Various Bias Resistor Values and  $I_{DQ}$ , 1 GHz to 28 GHz,  $V_{DD} = 5 V$ ,  $V_{BIAS} = 5 V$

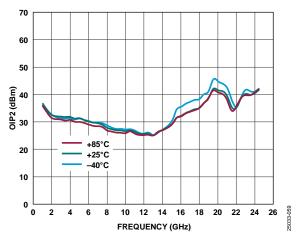

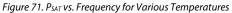

Figure 59. OIP2 vs. Frequency for Various Temperatures, 1 GHz to 24.5 GHz,  $V_{DD}$  = 5 V,  $V_{BIAS}$  = 5 V,  $I_{DQ}$  = 80 mA,  $R_{BIAS}$  = 300  $\Omega$

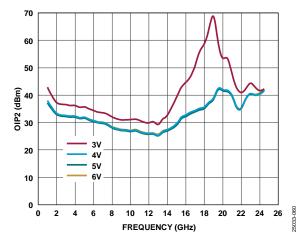

Figure 60. OIP2 vs. Frequency for Various  $V_{DD}$ ,  $I_{DQ} = 80$  mA, 1 GHz to 24.5 GHz

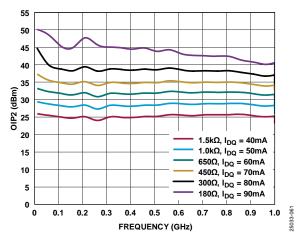

Figure 61. OIP2 vs. Frequency for Various Bias Resistor Values and  $I_{DQ}$ ,  $0.01 \text{ GHz to } 1 \text{ GHz}, V_{DD} = 5 \text{ V}, V_{BIAS} = 5 \text{ V}$

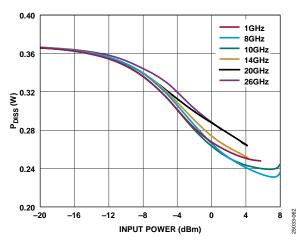

Figure 62. P<sub>DISS</sub> vs. Input Power at Various Frequencies,  $T_A = 85$  °C,  $V_{DD} = 5$  V,  $V_{BIAS} = 5 V, I_{DQ} = 80 mA$

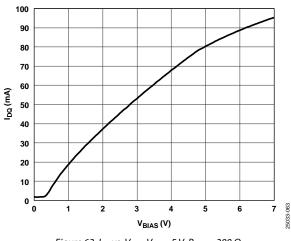

Figure 63.  $I_{DQ}$  vs.  $V_{BIAS}$ ,  $V_{DD} = 5 V$ ,  $R_{BIAS} = 300 \Omega$

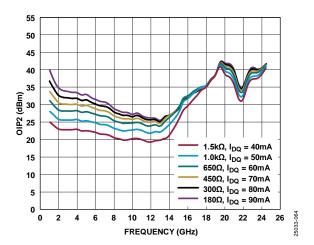

Figure 64. OIP2 vs. Frequency for Various Bias Resistor Values and  $I_{DQ}$ , 1 GHz to 24.5 GHz,  $V_{DD} = 5 V$ ,  $V_{BIAS} = 5 V$

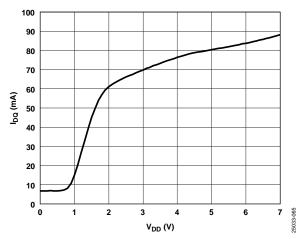

Figure 65.  $I_{DQ}$  vs.  $V_{DD}$ ,  $V_{BIAS} = 5 V$ ,  $R_{BIAS} = 300 \Omega$

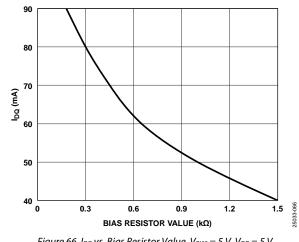

Figure 66.  $I_{DQ}$  vs. Bias Resistor Value,  $V_{BIAS} = 5 V$ ,  $V_{DD} = 5 V$

#### **BIASING THROUGH THE ACG4/V<sub>DD2</sub> PIN**

$V_{DD2} = 8.5 \text{ V}, V_{BIAS} = 5 \text{ V}, I_{DQ} = 80 \text{ mA}, R_{BIAS} = 300 \Omega$ , and frequency range = 0.01 GHz to 28 GHz.

Figure 67. Gain, Return Loss, and Reverse Isolation vs. Frequency

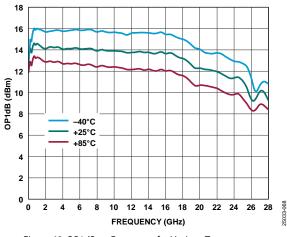

Figure 68. OP1dB vs. Frequency for Various Temperatures

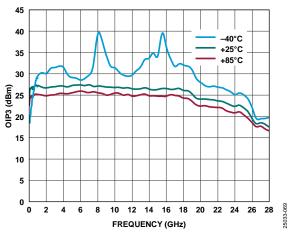

Figure 69. OIP3 vs. Frequency for Various Temperatures

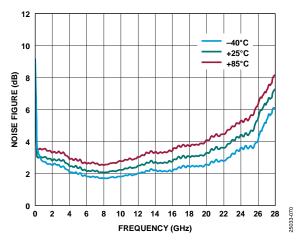

Figure 70. Noise Figure vs. Frequency for Various Temperatures

Figure 72. OIP2 vs. Frequency for Various Temperatures

### **THEORY OF OPERATION**

The ADL9005 is a GaAs, MMIC, pHEMT, wideband LNA. A simplified block diagram is shown in Figure 73. The RF<sub>IN</sub> and RF<sub>OUT</sub> pins are dc-coupled and matched to 50  $\Omega$ .

The ADL9005 operates from a single positive supply.  $I_{DQ}$  is set by connecting a resistor between the  $R_{BIAS}$  pin and the external supply voltage. The drain bias voltage is normally provided via an external bias tee. However, the drain bias voltage can also be resistively biased by connecting the ACG4/V<sub>DD2</sub> pin to an external supply.

Figure 73. Simplified Block Diagram

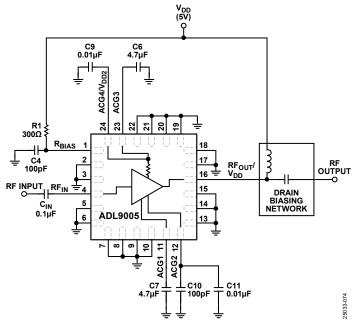

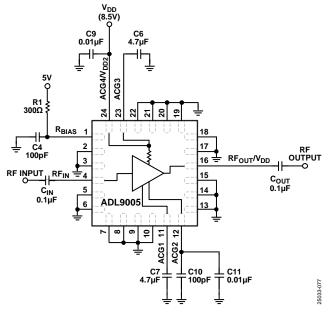

### APPLICATIONS INFORMATION BASIC CONNECTIONS

The basic connections for operating the ADL9005 are shown in Figure 74. Connect the recommended capacitor values to the ac ground pins (ACG1, ACG2, ACG3, and ACG4) as shown in Figure 74. The bias current is set by connecting a resistor between  $R_{BIAS}$  and  $V_{DD}$ . When using 5 V  $V_{DD}$ , a resistor value of 300  $\Omega$  is recommended to achieve an  $I_{DQ}$  of 80 mA. Table 9 shows the resulting  $I_{DQ}$  for the various  $R_{BIAS}$  values where the resistor is tied to 5 V. Decouple the  $R_{BIAS}$  pin with a 100 pF capacitor as shown in Figure 74.

Refer to ADL9005-EVALZ user guide (UG-1859) for the recommended part numbers of the manufacturers for all the external components required to operate the ADL9005.

#### Table 9. Recommended Bias Resistor Values

| R <sub>BIAS</sub> (Ω) | I <sub>DQ</sub> (mA) | I <sub>DQ_AMP</sub> (mA) | I <sub>DQ_BIAS</sub> (mA) |

|-----------------------|----------------------|--------------------------|---------------------------|

| 180                   | 90                   | 82.3                     | 7.7                       |

| 300                   | 80                   | 73.6                     | 6.4                       |

| 450                   | 70                   | 64.8                     | 5.2                       |

| 650                   | 60                   | 55.8                     | 4.2                       |

| 1000                  | 50                   | 46.8                     | 3.2                       |

| 1500                  | 40                   | 37.4                     | 2.6                       |

Figure 74. Typical Application Circuit

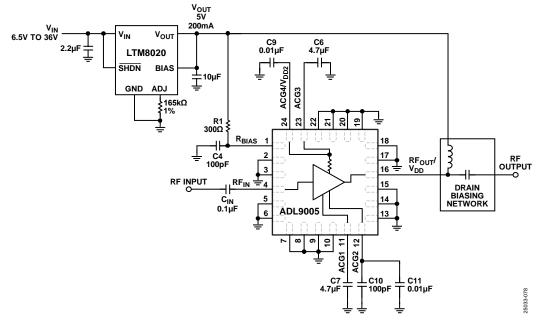

#### BIASING THE ADL9005 BY USING THE LTM8020

The LTM8020,  $\mu$ Module<sup>\*</sup> regulator is suitable for the ADL9005 due to its compact size and wide input voltage range of 4 V to 36 V while maintaining high efficiency and output noise below the maximum allowable ripple of the ADL9005 due to its high power supply modulation ratio.

The ADL9005 can be powered by using a well regulated power source. The LTM8020 is a complete 200 mA, dc to dc, step-down power supply that provides a single 5 V supply to  $V_{DD}$  through a bias tee on R<sub>BIAS</sub>. The recommended input voltage (V<sub>IN</sub>) for the LTM8020 is from 6.5 V to 36 V to achieve a 5 V output voltage (V<sub>OUT</sub>).

Figure 75 shows the application circuit for ADL9005 using the LTM8020 regulator.

Figure 75. Application Circuit for the ADL9005 Using the LTM8020 Regulator

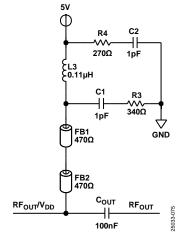

The ADL9005 was characterized using a connectorized wideband bias tee (Marki Microwave BT2-0040). In practice, the drain bias must be provided by a board mountable component. Drain biasing for a wideband amplifier, such as the ADL9005, is traditionally provided by connecting a wideband conical inductor between  $RF_{OUT}/V_{DD}$  and the 5 V power supply, as shown in Figure 74. Conical inductors are fragile and physically large. Figure 76 shows an alternative biasing circuit that uses 0402 sized, surfacemount components. The gain, input return loss, and output return loss over frequency are shown in Figure 77.

Figure 76. Surface-Mounted Bias Tee Schematic

Figure 77. Gain and Return Loss vs. Frequency Using the Surface-Mount Bias Tee

The circuit consists of ferrite beads (FB1 and FB2), an ac coupling capacitor ( $C_{OUT}$ ), an inductor (L3), de-Q resistors (R3 and R4), and bypass capacitors (C1 and C2).

The R3, R4, C1, and C2 decoupling components are used to reduce the RF coupling and to filter out power supply noise. R3 and R4 are de-Q resistors that can reduce frequency glitches caused by interactions between the PCB and the decoupling capacitors.

FB2 is critical to achieving high frequency operation. Optimal performance is achieved when FB2 touches down on the RF trace directly. FB1 is also a critical component that must be placed as close as possible to FB2 because a longer trace adds increased inductance and capacitance. FB1 mitigates resonances caused by the interaction between FB2 and the PCB.

The L3 inductor is only needed if operation at below 100 MHz is required. Otherwise, omit L3.

Table 10 lists the part numbers of the manufacturers and values used in the surface-mounted bias tee circuit shown in Figure 76.

Further details on design of surface-mount bias tee circuits can be found in Application Note AN-2061.

| Component | Value   | Manufacturer                | Part Number        |

|-----------|---------|-----------------------------|--------------------|

| FB1, FB2  | 470 Ω   | Murata                      | BLM15GG471SN1D     |

| L3        | 0.11 μH | Coilcraft                   | 0805LS-111X_E_     |

| Соит      | 100 nF  | American Technical Ceramics | ATC 560L           |

| R3        | 340 Ω   | Panasonic                   | ERA-2AEB3400X      |

| C1, C2    | 1 pF    | Murata                      | GJM1555C1H1R0CB01D |

| R4        | 270 Ω   | Panasonic                   | ERJ-2GEJ271X       |

# PROVIDING DRAIN BIAS THROUGH THE ACG4/V<sub>DD2</sub> PIN

An alternative way to bias the ADL9005 is through the ACG4/V<sub>DD2</sub> pin (Pin 24), which is shown in Figure 78. Because of the voltage drop across the internal bias resistor, a higher V<sub>DD</sub> is required. If a 300  $\Omega$  bias resistor (R1) is used and connected to the 5 V power supply, which results in a total current of 80 mA, a V<sub>DD</sub> of 8.5 V is recommended. R1 can also be connected to the V<sub>DD</sub> of 8.5 V. In this case, to set I<sub>DQ</sub> to 80 mA, use an R1 value of 850  $\Omega$  on R<sub>BIAS</sub>. The performance of this circuit is summarized in Figure 67 to Figure 72.

Figure 78. Providing Resistive Drain Bias Through the ACG4/ $V_{DD2}$  Pin

#### POWER-UP AND POWER-DOWN SEQUENCING

Apply the RF input signal after the main supply voltage and the voltage driving  $R_{BIAS}$  (R1 in Figure 74 and Figure 78) and remove the RF input signal before the main supply voltage and the voltage on  $R_{BIAS}$  are turned off. The voltage on  $R_{BIAS}$  can either be applied simultaneously with  $V_{DD}$  or after  $V_{DD}$  is applied.

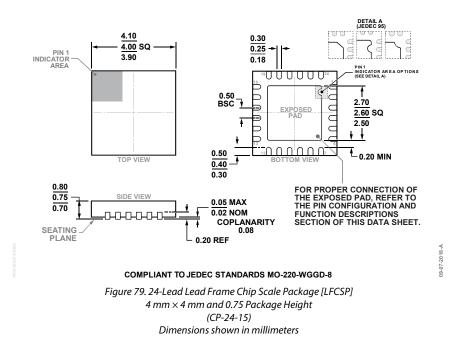

### **OUTLINE DIMENSIONS**

#### **ORDERING GUIDE**

| Model <sup>1, 2</sup> | Temperature Range | MSL Rating <sup>3</sup> | Package Description <sup>4</sup>              | Package Option |

|-----------------------|-------------------|-------------------------|-----------------------------------------------|----------------|

| ADL9005ACPZN          | -40°C to +85°C    | MSL3                    | 24-Lead Lead Frame Chip Scale Package [LFCSP] | CP-24-15       |

| ADL9005ACPZN-R7       | -40°C to +85°C    | MSL3                    | 24-Lead Lead Frame Chip Scale Package [LFCSP] | CP-24-15       |

| ADL9005-EVALZ         |                   |                         | Evaluation Board                              |                |

$^{1}$  Z = RoHS Compliant Part.

<sup>2</sup> When ordering the evaluation board only, reference the model number, ADL9005-EVALZ.

<sup>3</sup> See the Absolute Maximum Ratings section for additional information.

<sup>4</sup> The lead finish of the ADL9005ACPZN and ADL9005ACPZN-R7 is nickel palladium gold (NiPdAu).

©2021 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners. D25033-2/21(0)

www.analog.com