# EVAL-ADuM4221EBZ User Guide

One Technology Way • P.O. Box 9106 • Norwood, MA 02062-9106, U.S.A. • Tel: 781.329.4700 • Fax: 781.461.3113 • www.analog.com

## Evaluating the ADuM4221 Isolated, Half Bridge Gate Driver with Adjustable Dead Time, 4 A Output

#### **FEATURES**

Adjustable dead time

Output voltage range to 35 V

Screw terminals for easy connectivity

Pad placement for external series gate resistors

Pad placement for capacitive load testing

Supports TO-220 or TO-252 IGBTs or MOSFETs

Bootstrap option

Jumper placement for easy half bridge setup

#### **EVALUATION KIT CONTENTS**

EVAL-ADuM4221EBZ evaluation board

#### **EQUIPMENT NEEDED**

Suggested test equipment

Primary side power supply: 0 V to 6.5 V at 100 mA

2 secondary side supplies: 0 V to 35 V at 250 mA

Square wave generator: 0 V to 5 V

#### **GENERAL DESCRIPTION**

The EVAL-ADuM4221EBZ supports the ADuM4221 half bridge gate driver that employs Analog Devices, Inc., iCoupler\* technology to provide independent and isolated high-side and low-side outputs. The EVAL-ADuM4221EBZ is populated with the ADuM4221, which has  $V_{IA}$  and  $V_{IB}$  inputs and dead time control. The EVAL-ADuM4221EBZ supplies jumpers and screw

terminals to configure different drive conditions. The EVAL-ADuM4221EBZ operates with square waves and dc values on the  $V_{\rm IA},\,V_{\rm IB},$  and DISABLE pins.

The ADuM4221 operates with an input supply ranging from 2.5 V to 6.5 V, providing compatibility with lower voltage systems. Logic level voltages at the input pins control the  $V_{OA}$  and  $V_{OB}$  outputs. The driver has a DISABLE input pin that, if held high, shuts the device off regardless of the input on the channels. In addition to basic overlap protection, the dead time (DT) pin on the primary side allows an adjustable dead time between the  $V_{OA}$  and  $V_{OB}$  output transitions.

The ADuM4221 provides operation with voltages of up to 35 V on the secondary side. The EVAL-ADuM4221EBZ has a provision for the high-side supply to be bootstrapped to the low-side supply. The EVAL-ADuM4221EBZ facilitates testing of the propagation delay, drive strength, dead time operation, and input logic of the device. Because the EVAL-ADuM4221EBZ has footprints for insulated gate bipolar transistors (IGBTs) and metal-oxide semiconductor field effect transistors (MOSFETs) in TO-220 and TO-252 packages, the ADuM4221 can be evaluated with many different power devices.

For complete information about the ADuM4221, refer to the ADuM4221 data sheet in conjunction with this user guide when using the EVAL-ADuM4221EBZ.

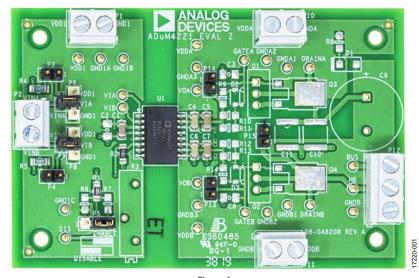

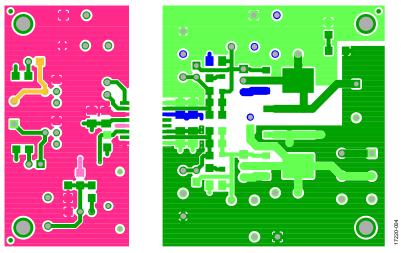

#### **EVAL-ADUM4221EBZ PHOTOGRAPH**

Figure 1.

PLEASE SEE THE LAST PAGE FOR AN IMPORTANT WARNING AND LEGAL TERMS AND CONDITIONS.

## UG-1442

## **EVAL-ADuM4221EBZ** User Guide

### **TABLE OF CONTENTS**

| Features                    | 1 |

|-----------------------------|---|

| Evaluation Kit Contents     | 1 |

| Equipment Needed            | 1 |

| General Description         | 1 |

| EVAL-ADuM4221EBZ Photograph |   |

| Revision History            | 2 |

| EVAL-ADuM4221EBZ Hardware   |   |

| Initial Configuration       | 3 |

| Pad Layout for the Device Under Test (DUT)         | 3 |

|----------------------------------------------------|---|

| Setting Up the EVAL-ADuM4221EBZ                    |   |

| Power Connections                                  | 4 |

| Input/Output Connections                           | 4 |

| Bootstrapping V <sub>DDB</sub> to V <sub>DDA</sub> | 4 |

| Evaluation Board Schematic and Artwork             | 5 |

| Ordering Information                               | 6 |

| Pill of Matarials                                  |   |

#### **REVISION HISTORY**

7/2020—Revision 0: Initial Version

## EVAL-ADUM4221EBZ HARDWARE INITIAL CONFIGURATION

In stock configuration (see Figure 1), the EVAL-ADuM4221EBZ is set up for testing the basic gate driver functionality under a no load condition. Either screw terminals or test pins can be used for the input, output, and signal connections to the board. The R9 to R14 resistors are not populated. These locations of the series external resistors serve as the charging and discharging paths of the device being driven. R9 to R11 are for the high-side output, and R12 to R14 are for the low-side output. However, before initial use, it is recommended to complete certain steps to prepare the EVAL-ADuM4221EBZ for operation.

#### PAD LAYOUT FOR THE DEVICE UNDER TEST (DUT)

The EVAL-ADuM4221EBZ provides placement for supporting components to facilitate evaluation of the gate driver. The available pad placements are as follows:

- U1 is the footprint for the ADuM4221.

- C1, C4, and C6 are 0.1 μF bypass capacitors, C5 and C7 are 10 μF bypass capacitors, and C2 (not populated) is 1 μF, in a surface-mount device (SMD), Size 1206 package.

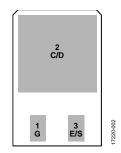

- Q1 and Q2 can be populated with TO-220 package MOSFETs or IGBTs, and Q3 and Q4 with TO-252 package MOSFETs or IGBTs (see Figure 2). In Figure 2, C/D is collector/drain, G is gate, and E/S is emitter/source.

- R9 to R14 are gate resistors that control the slew rate of the outputs, and can be populated with Size 1206, SMD resistors in the 1  $\Omega$  to 10  $\Omega$  range.

- C3 and C8 capacitor pad placements provide land patterns for placing a capacitor load to simulate gate capacitance.

- D1 and R8 can be populated for using a bootstrap supply for the high-side driver.

- R3 (not populated) is a variable resistor up to 500 kΩ.

Figure 2. IGBT/MOSFET Footprint

#### **SETTING UP THE EVAL-ADUM4221EBZ**

It is recommended to use Size 1206, surface-mount, external gate resistors with values between approximately 1  $\Omega$  and 10  $\Omega$ , depending on the required drive strength for the load being driven. Diode D2 and Diode D3 are not populated but can be used for providing a different turn on and turn off path. An IGBT or MOSFET can be placed in the provided Q1 or Q3 and Q2 or Q4 landing patterns. Jumpers P13 and P14 allow shorting across the series external resistors on the low side and the high

side, respectively, to observe overshoot or allow the user to probe the voltage to quantify peak currents.

A 10 k $\Omega$  dead time resistor is placed at R2, but it can be replaced with any value in the range of 10 k $\Omega$  to 500 k $\Omega$  to provide a corresponding dead time between the high-side and the low-side outputs of the ADuM4221. Potentiometer R3 (not populated) can be used instead of R2 for faster dead time adjustment.

The combination of Resistor R4 and Jumper P3 allows the user to terminate a high-side logic input with a 50  $\Omega$  load, and the combination of Resistor R5 and Jumper P4 allows a similar provision for the low-side logic input. R4 and R5 are not required, and, if not connected through the jumpers, the EVAL-ADuM4221EBZ accepts high impedance, generator signals from an external source.

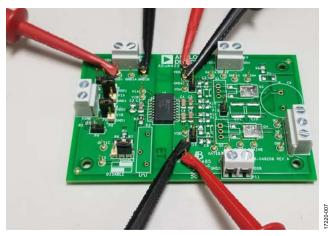

A jumper on P6 allows the user to easily connect  $V_{IA}$  to  $V_{DD1}$  or  $GND_1$ , and a jumper on P8 allows the user to tie  $V_{IB}$  to  $V_{DD1}$  or  $GND_1$  (see Figure 3).

Figure 3. Example of P6 and P8 Configured to Connect Inputs to DC Values

Screw terminals are the preferred method to connect the logic level inputs on the EVAL-ADuM4221EBZ because this method provides added flexibility for making connections to the input pins of the device.

Placing a Jumper between P6 and P7 connects  $V_{\rm IA}$  to an external input voltage signal (labeled VINA) on the EVAL-ADuM4221EBZ. Similarly, a jumper between P8 and P9 allows corresponding connections for  $V_{\rm IB}$  to VINB (see Figure 1). The VIA and VIB test pins directly connect to the input pins of the device under test (DUT) and eliminate the need to use the screw terminals or any combination of jumpers when the device is driven by an external signal. The user can choose to utilize either a direct pin connection or the screw terminal method to make the connection. However, when the test pins are used to connect to an external source, care must be taken to ensure that there is no jumper on P6 and on P8, which connects to dc values. Connection between P6 and P7 and between P8 and P9 can still be made if termination is required in combination with placing the jumpers on P3 and on P4.

#### **POWER CONNECTIONS**

Follow these steps to connect the EVAL-ADuM4221EBZ to a power supply (see Figure 4):

- 1. Connect the input  $V_{\rm DD1}$  supply (2.5 V to 6.5 V) with the positive terminal to the  $V_{\rm DD1}$  pin and ground to the GND<sub>1</sub> pin.

- 2. Connect the  $V_{DDB}$  supply (4.5 V to 35 V) with the positive terminal to the  $V_{DDB}$  pin and ground to the  $GND_B$  pin.

- 3. Connect the  $V_{DDA}$  supply (4.5 V to 35 V) with the positive terminal to the  $V_{DDA}$  pin and ground to the GND<sub>A</sub> pin.

Figure 4. Power Supply Connections

$GND_1$ ,  $GND_A$ , and  $GND_B$  are all isolated from each other. The high-side IGBT emitter/MOSFET source is connected to  $GND_A$ , and low-side IGBT emitter/MOSFET source is tied to  $GND_B$ .

#### INPUT/OUTPUT CONNECTIONS

The  $V_{IA}$  and  $V_{IB}$  pins are logic level inputs compatible with 3.3 V and 5 V systems. If using a screw terminal, connect  $V_{IA}$  to VINA by connecting P7 and Pin 2 (center pin) of P6 with a jumper or by using the VIA test pin. Similarly, connect  $V_{IB}$  to VINB by connecting P9 and Pin 2 (center pin) of P8 with a jumper or by using the VIB test pin. Only one of the outputs is high at any given time due to the built-in overlap protection and the default dead time is about 62 ns with a 10 k $\Omega$  resistor at R2.

In stock configuration, the P5 header jumper connects Pin 2 and Pin 3 (two pins on the right side) to enable operation of the

device outputs. Connecting Pin 1 and Pin 2 of P5 disables the device. The disable function can be controlled externally by connection to the disable (DIS) test pin. R6 and R7 can be used as pull-up and pull-down resistors, respectively, for the disable input.

The half bridge output (HB) test pin on the EVAL-ADuM4221EBZ is the Q2/Q4 collector/drain node. If the device is used in the half bridge configuration, the Q1/Q3 emitter/source can be connected to HB with a jumper across P15. The bus voltage (BUS) test pin on the EVAL-ADuM4221EBZ connects to the drain of the high-side Q1 and Q3 MOSFET/IGBT. It is recommended to use a 100  $\mu F$  electrolytic capacitor for C9 and 2.2  $\mu F$  ceramic capacitors for C10 and C11.

The EVAL-ADuM4221EBZ comes with screw terminals for both the input and output connections. These terminals facilitate connection options but are not ideal for recording transient measurements to assess the ADuM4221 performance. Using the output screw terminals as the sensing node often results in overshoot during measurement. When conducting measurements on the load, whether through the IGBT, MOSFET, or load capacitor, small loop measurements are recommended for optimal results. Thus, use the output screw terminals only for connection of the external load.

#### **BOOTSTRAPPING VDDB TO VDDA**

To use a single supply on the secondary side in a bootstrap setup, populate the bootstrap diode, D1, and Resistor R8 with a value typically in the 1  $\Omega$  to 20  $\Omega$  range. In this setup, both outputs of the ADuM4221 can be powered by the  $V_{\text{DDB}}$  supply when a half bridge is configured with Q1 and Q2 or Q3 and Q4. When the switch node (GNDA) is low, C4 and C5 are charged through the forward-biased bootstrapping diode. When the switch node rises to the bridge voltage, the diode becomes reverse biased, and because of the charge on C4 and C5, VDDA to GND<sub>A</sub> almost equals V<sub>DDB</sub>, accounting for the forward drop of the diode. For bootstrapping to work, Q1 and Q2 or Q3 and Q4 must be populated instead of the load capacitors, C3 and C8, and a jumper must be placed on P15. To supply C4 and C5 with the charge required to drive the Q1 or Q3 gate, the switching frequency must be sufficiently high, and the duty cycle must be limited.

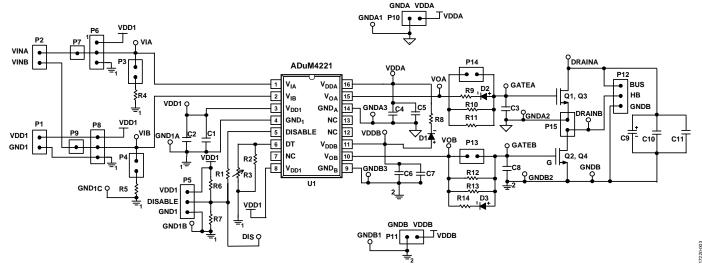

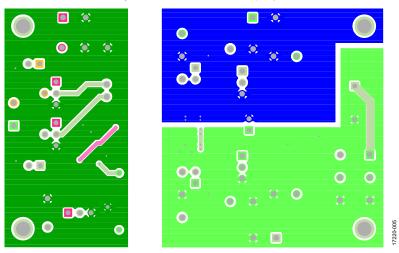

### **EVALUATION BOARD SCHEMATIC AND ARTWORK**

Figure 5. Schematic of the EVAL-ADuM4221EBZ

Figure 6. EVAL-ADuM4221EBZ Top Layer

Figure 7. EVAL-ADuM4221EBZ Bottom Layer

### ORDERING INFORMATION

#### **BILL OF MATERIALS**

#### Table 1 Rill of Materials

| Table 1. Dill of Materials |                                                               |

|----------------------------|---------------------------------------------------------------|

| Reference Designator       | Description                                                   |

| U1                         | ADuM4221, RI-16-2                                             |

| R1                         | Resistor, 1 k $\Omega$ , 1206                                 |

| R2                         | Resistor, 10 k $\Omega$ , 1206                                |

| R4, R5                     | Resistor, 50 Ω, 1206                                          |

| C1, C4, C6                 | Capacitor, 0.1 μF, 10%, 1206                                  |

| C5, C7                     | Capacitor, 10 μF, 10%, 1206                                   |

| D1                         | Diode, not installed, DO214AC package                         |

| D2, D3                     | Diode, not installed, SOD123FL package                        |

| R3                         | Resistor, not installed, 0.190 in. $\times$ 0.750 in. package |

| R6 to R14                  | Resistor, not installed, 1206                                 |

| C2, C3, C8,                | Capacitor, not installed, 1206                                |

| C9                         | Capacitor, not installed, 0.630 in. diameter                  |

| C10, C11                   | Capacitor, not installed, 2220                                |

| Q1, Q2                     | IGBT or MOSFET, not installed, TO-220                         |

| Q3, Q4                     | IGBT or MOSFET, not installed, TO-252                         |

#### ESD Caution

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

#### Legal Terms and Conditions

By using the evaluation board discussed herein (together with any tools, components documentation or support materials, the "Evaluation Board"), you are agreeing to be bound by the terms and conditions set forth below ("Agreement") unless you have purchased the Evaluation Board, in which case the Analog Devices Standard Terms and Conditions of Sale shall govern. Do not use the Evaluation Board until you have read and agreed to the Agreement, Your use of the Evaluation Board shall signify your acceptance of the Agreement. This Agreement is made by and between you ("Customer") and Analog Devices, Inc. ("ADI"), with its principal place of business at One Technology Way, Norwood, MA 02062, USA. Subject to the terms and conditions of the Agreement, ADI hereby grants to Customer a free, limited, personal, temporary, non-exclusive, non-sublicensable, non-transferable license to use the Evaluation Board FOR EVALUATION PURPOSES ONLY. Customer understands and agrees that the Evaluation Board is provided for the sole and exclusive purpose referenced above, and agrees not to use the Evaluation Board for any other purpose. Furthermore, the license granted is expressly made subject to the following additional limitations: Customer shall not (i) rent, lease, display, sell, transfer, assign, sublicense, or distribute the Evaluation Board; and (ii) permit any Third Party to access the Evaluation Board. As used herein, the term "Third Party" includes any entity other than ADI, Customer, their employees, affiliates and in-house consultants. The Evaluation Board is NOT sold to Customer, all rights not expressly granted herein, including ownership of the Evaluation Board, are reserved by ADI. CONFIDENTIALITY. This Agreement and the Evaluation Board shall all be considered the confidential and proprietary information of ADI. Customer may not disclose or transfer any portion of the Evaluation Board to any other party for any reason. Upon discontinuation of use of the Evaluation Board or termination of this Agreement, Customer agrees to promptly return the Evaluation Board to ADI. ADDITIONAL RESTRICTIONS. Customer may not disassemble, decompile or reverse engineer chips on the Evaluation Board. Customer shall inform ADI of any occurred damages or any modifications or alterations it makes to the Evaluation Board, including but not limited to soldering or any other activity that affects the material content of the Evaluation Board. Modifications to the Evaluation Board must comply with applicable law, including but not limited to the RoHS Directive. TERMINATION. ADI may terminate this Agreement at any time upon giving written notice to Customer. Customer agrees to return to ADI the Evaluation Board at that time. LIMITATION OF LIABILITY. THE EVALUATION BOARD PROVIDED HEREUNDER IS PROVIDED "AS IS" AND ADI MAKES NO WARRANTIES OR REPRESENTATIONS OF ANY KIND WITH RESPECT TO IT. ADI SPECIFICALLY DISCLAIMS ANY REPRESENTATIONS, ENDORSEMENTS, GUARANTEES, OR WARRANTIES, EXPRESS OR IMPLIED, RELATED TO THE EVALUATION BOARD INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, TITLE, FITNESS FOR A PARTICULAR PURPOSE OR NONINFRINGEMENT OF INTELLECTUAL PROPERTY RIGHTS. IN NO EVENT WILL ADI AND ITS LICENSORS BE LIABLE FOR ANY INCIDENTAL, SPECIAL, INDIRECT, OR CONSEQUENTIAL DAMAGES RESULTING FROM CUSTOMER'S POSSESSION OR USE OF THE EVALUATION BOARD, INCLUDING BUT NOT LIMITED TO LOST PROFITS, DELAY COSTS, LABOR COSTS OR LOSS OF GOODWILL. ADI'S TOTAL LIABILITY FROM ANY AND ALL CAUSES SHALL BE LIMITED TO THE AMOUNT OF ONE HUNDRED US DOLLARS (\$100.00). EXPORT. Customer agrees that it will not directly or indirectly export the Evaluation Board to another country, and that it will comply with all applicable United States federal laws and regulations relating to exports. GOVERNING LAW. This Agreement shall be governed by and construed in accordance with the substantive laws of the Commonwealth of Massachusetts (excluding conflict of law rules). Any legal action regarding this Agreement will be heard in the state or federal courts having jurisdiction in Suffolk County, Massachusetts, and Customer hereby submits to the personal jurisdiction and venue of such courts. The United Nations Convention on Contracts for the International Sale of Goods shall not apply to this Agreement and is expressly disclaimed.

©2020 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners.

UG17220-7/20(0)

www.analog.com