# **DEMO MANUAL DC1741B**

# LTC4370 Two-Supply Diode-OR Current Balancing Controller

### DESCRIPTION

Demonstration circuit DC1741B features the LTC®4370, a two supply diode-OR current sharing controller in a typical 2.9V to 18V, 16A sharing application.

The maximum MOSFET voltage drop  $V_{FR} = V_{IN} - OUT$  is set with an external resistor, up to 600mV. A fast gate turn-on reduces the load voltage droop during supply switchover. If the input supply fails or is shorted, a fast turn-off minimizes the transient reverse current.

Disabling the load sharing function turns the LTC4370 into a dual ideal diode controller.

Two enable input pins,  $\overline{\text{EN1}}$  and  $\overline{\text{EN2}}$ , allow enabling and disabling each rail's MOSFET individually while the MOSFETs' inherent diodes create diode-OR connection

when the MOSFETs are disabled. The LTC4370 provides a rich set of features to support shared current diode-ORed applications including:

- · Load Sharing Between Two Supplies

- Elimination of the Need for Active Control of Input Supplies

- Elimination of "Share Bus"

- Reverse Current Blocking

- Elimination of Shoot-Through Current During Start-Up or Faults

### Design files for this circuit board are available.

All registered trademarks and trademarks are the property of their respective owners.

## **PERFORMANCE SUMMARY** Specifications are at T<sub>A</sub> = 25°C

| SYMBOL                | PARAMETER                                                                                                    | CONDITIONS                                                                                                                                        | MIN               | TYP                | MAX                   | UNITS        |

|-----------------------|--------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|--------------------|-----------------------|--------------|

| V <sub>IN</sub>       | V <sub>IN1</sub> and V <sub>IN2</sub> Input Voltage Operating<br>Range                                       | With External V <sub>CC</sub> Supply                                                                                                              | 2.9<br>0          |                    | 18<br>V <sub>CC</sub> | V            |

| V <sub>CC(EXT)</sub>  | V <sub>CC</sub> External Supply Operating Range                                                              | $V_{IN1}, V_{IN2} \leq V_{CC}$                                                                                                                    | 2.9               |                    | 6.0                   | V            |

| V <sub>CC(REG)</sub>  | V <sub>CC</sub> Regulated Voltage                                                                            |                                                                                                                                                   | 4.5               | 5                  | 5.5                   | V            |

| V <sub>EA(OS)</sub>   | Error Amplifier Input Offset                                                                                 |                                                                                                                                                   |                   | 0                  | ±2                    | mV           |

| gm(EA)                | Error Amplifier Gain                                                                                         |                                                                                                                                                   |                   | 150                |                       | μS           |

| $V_{FR}$              | Forward Regulation Voltage (V <sub>IN</sub> – V <sub>OUT</sub> )                                             | $V_{IN} = 1.2V, V_{CC} = 5V$<br>$V_{IN} = 12V$                                                                                                    | 2<br>2            | 12<br>25           | 25<br>50              | mV<br>mV     |

| $\Delta V_{GATE}$     | MOSFET Gate Drive (GATE-V <sub>IN</sub> )                                                                    | $V_{FWD} = 0.2V; I = 0, -1\mu A;$ Highest $V_{IN} = 12V$<br>$V_{FWD} = 0.2V; I = 0, -1\mu A;$ Highest $V_{IN} = 2.9V$                             | 10<br>4.5         | 12<br>7            | 14<br>9               | V            |

| I <sub>GATE</sub>     | GATE1, GATE2 Fast Pull-Up Current<br>GATE1, GATE2 Fast Down-Up Current<br>GATE1, GATE2 Off Pull-Down Current | $V_{PWD}$ = 0.4V, $\Delta V_{GATE}$ = 0V, CPO = 17V<br>$V_{PWD}$ = -2V, $\Delta V_{GATE}$ = 5V,<br>Corresponding EN =1V, $\Delta V_{GATE}$ = 2.5V | -0.9<br>0.9<br>65 | -1.4<br>1.4<br>110 | -1.9<br>1.9<br>160    | Α<br>Α<br>μΑ |

| V <sub>EN(TH)</sub>   | EN1, EN2 Threshold Voltage                                                                                   | EN Falling                                                                                                                                        | 580               | 600                | 620                   | mV           |

| $\Delta V_{GATE(ON)}$ | MOSFET On-Detect Threshold<br>(GATE-V <sub>IN</sub> )                                                        | FETON Transitions High                                                                                                                            | 0.28              | 0.7                | 1.1                   | V            |

| I <sub>OUT</sub>      | Maximum Continuous Load Current                                                                              | Sharing active, limited by SUM90N04-3m3P-E3 Dissipation                                                                                           |                   |                    | 16.6                  | A            |

### **OPERATING PRINCIPLES**

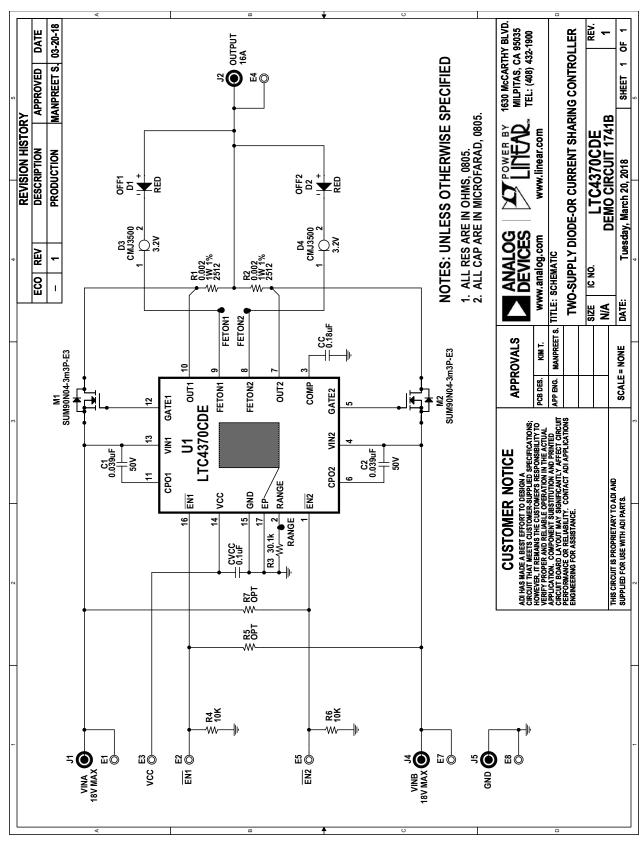

The LTC4370 controls N-channel MOSFETs, M1 and M2, to share the load between two input rails. The error amplifier compares OUT1 and OUT2, and controls servo amplifiers which regulate the MOSFET forward voltage drop to  $V_{FR}$ . Combined action of the error amplifier and servo amplifiers forces OUT1 and OUT2 to be equal and as a result the rail currents are equal. The board RANGE resistor R3 = 30.1k defines the maximum regulation voltage range as 265mV to 375mV.

The board is assembled with SUM90N04-3m3P-E3 N-channel MOSFETs, which in a single channel application has current capability up to 20A. In the load share mode, the installed components guarantee continuous proper load sharing up to 16.6A total load. For a short test time of 3 to 5 seconds, it is possible to double this load.

Two LEDs, OFF1 and OFF2, indicate the MOSFETs' status. Each LED lights up when the gate voltage is less than 0.7V above  $V_{\text{IN}}$ .

Pay special attention to the power supply features used with the LTC4370.

This controller may not work properly with supplies utilizing synchronized rectification in the output stage unless the internal circuit of the supply has the ability to limit negative current or to block it completely. Exercise caution when using the controller with this type of supply unless it is determined that it contains the required circuitry.

## **QUICK START PROCEDURE**

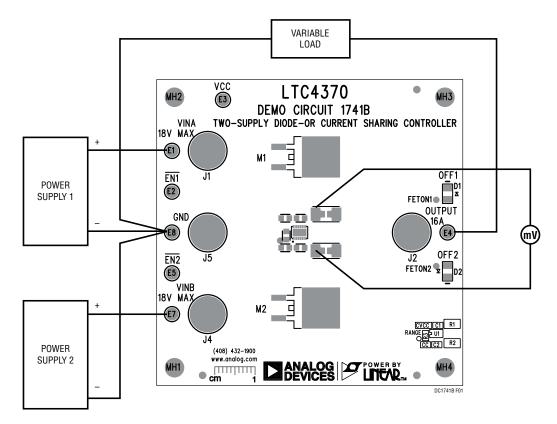

Demonstration circuit DC1741B is easy to set up to evaluate the performance of the LTC4370. Refer to Figure 1 for proper measurement equipment setup for load share observation.

- 1. Turn both supplies on. Adjust two 5V supplies' outputs to a 215mV difference, which equals the minimum  $\Delta V_{\rm IN(MIN)}$  load share breakpoint (265mV–50mV). Load the LTC4370 output with minimal current so that both supplies contribute current to the common load. Increase load up to 35A and observe the LTC4370 operation mode with accurate load sharing. It is easy to estimate load share accuracy by measuring a voltage between two sense resistors. Since the MOSFETs will be dissipating excessive power, limit this measurement to 3 to 5 seconds when at the 35A level.

- 2. Reduce the load current to a total of 7.5A. Adjust the two 5V supplies' outputs to a voltage difference of 373 mV, which equals the maximum  $\Delta V_{IN(MAX)}$  load share breakpoint (375mV-2mV). As the difference between power supplies output is greater than the maximum voltage regulation, the LTC4370 channel with the higher voltage will provide most of the current. Increase the voltage until all of the current is provided by the higher voltage supply. This is the point at which the MOSFET of the higher voltage channel MOSFET is fully enhanced while the MOSFET of the lower channel voltage is completely cut off. Observe that the LED of the lower supply is illuminated.

Figure 1. Load Share Performance Measurement

# DEMO MANUAL DC1741B

# **PARTS LIST**

| ITEM                        | QTY | REFERENCE                  | PART DESCRIPTION                               | MANUFACTURER/PART NUMBER            |  |  |  |

|-----------------------------|-----|----------------------------|------------------------------------------------|-------------------------------------|--|--|--|

| Required Circuit Components |     |                            |                                                |                                     |  |  |  |

| 1                           | 1   | CC                         | Cap., X7R, 0.18µF, 25V, 10%, 0805              | AVX, 08053C184KAT2A                 |  |  |  |

| 2                           | 1   | CV <sub>CC</sub>           | Cap., X7R, 0.1µF, 50V, 10%, 0805               | AVX, 08055C104KAT2A                 |  |  |  |

| 3                           | 2   | C1, C2                     | Cap., X7R, 0.039µF, 50V, 10%, 0805             | AVX, 08055C393KAT2A                 |  |  |  |

| 4                           | 2   | D1, D2                     | LED, RED                                       | Panasonic, LN1251C-TR               |  |  |  |

| 5                           | 2   | D3, D4                     | Current Limiting Diode, 3.2V, SOD-80           | Central Semi. Corp. CMJ3500         |  |  |  |

| 6                           | 7   | E1, E2, E3, E4, E5, E7, E8 | Turret, Testpoint 0.063"                       | Mill-Max, 2308-2-00-80-00-00-07-0   |  |  |  |

| 7                           | 4   | J1, J2, J4, J5             | Connector, Banana Jack                         | Keystone, 575-4                     |  |  |  |

| 8                           | 2   | M1, M2                     | MOSFET N-Channel, 30V, D2PAK                   | Vishay, SUM90N04-3m3P-E3            |  |  |  |

| 9                           | 2   | R1, R2                     | Res., WSL 0.002 1W, 1%, 2512                   | Vishay, WSL25122L000FEA             |  |  |  |

| 10                          | 1   | R3                         | Res., Chip 30.1k, 0.1W 1%, 0805                | Vishay, CRCW080530K1FKEA            |  |  |  |

| 11                          | 2   | R4, R6                     | Res., Chip 10k, 0.1W, 5%, 0805                 | Vishay, CRCW080510K0JNEA            |  |  |  |

| 12                          | 0   | R5, R7                     | Res., 0805                                     | OPT                                 |  |  |  |

| 13                          | 1   | U1                         | I.C., Diode-OR Load Share Cont., DFN16DE-4 × 3 | Linear Technology Corp., LTC4370CDE |  |  |  |

### SCHEMATIC DIAGRAM

### DEMO MANUAL DC1741B

#### **ESD Caution**

ESD (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

### **Legal Terms and Conditions**

By using the evaluation board discussed herein (together with any tools, components documentation or support materials, the "Evaluation Board"), you are agreeing to be bound by the terms and conditions set forth below ("Agreement") unless you have purchased the Evaluation Board shall signify your acceptance of the Agreement is made by and between you ("Customer") and Analog Devices, Inc. ("ADI"), with its principal place of business at One Technology Way, Norwood, MA 02062, USA. Subject to the terms and conditions of the Agreement, ADI hereby grants to Customer a free, limited, personal, temporary, non-exclusive, non-sublicensable, non-transferable license to use the Evaluation Board For EVALUATION PURPOSES ONLY. Customer understands and agrees that the Evaluation Board is provided for the sole and exclusive purpose referenced above, and agrees not to use the Evaluation Board for any other purpose. Furthermore, the license granted is expressly made subject to the following additional limitations: Customer shall not (i) rent, lease, display, sell, transfer, assign, sublicense, or distribute the Evaluation Board. As used herein, including ownership of the Evaluation Board, as used herein, including ownership of the Evaluation Board, and in-house consultants. The Evaluation Board is considered the conflidential and proprietary information of ADI. Customer may not disclose or transfer any portion of the Evaluation Board to any other party for any reason. Upon discontinuation of use of the Evaluation Board or termination of this Agreement, Customer agrees to promptly return the Evaluation Board to ADI. ADDITIONAL RESTRICTIONS. Customer may not disassemble, decompile or reverse engineer chips on the Evaluation Board. Customer agrees to promptly return the Evaluation Board to ADI. ADDITIONAL RESTRICTIONS. Customer may not disassemble, decompile or reverse engineer chips on the Evaluation Board. Customer agrees to promptly return the Evaluation Board to ADI. ADDITIONAL RESTRICTIONS. Customer may not disassemble, decomp

Rev. A