# Dual Smart Battery System Manager

## **FEATURES**

- SMBus Charger/Selector for Two Smart Batteries\*

- Voltage and Current Accuracy within 0.2% of Value Reported by Battery

- Simplifies Construction of "Smart Battery System Manager"

- Includes All SMBus Charger V1.1 Safety Features

- Supports Autonomous Operation without a Host

- Allows Both Batteries to Discharge Simultaneously into Single Load with Low Loss (Ideal Diode)

- SMBus Switching for Dual Batteries with Alarm Monitoring for Charging Battery at All Times

- Pin Programmable Limits for Maximum Charge Current and Voltage Improve Safety

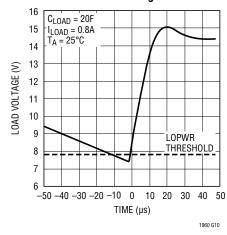

- Fast Autonomous PowerPath™ Switching (<10µs)</p>

- Low Loss Simultaneous Charging of Two Batteries

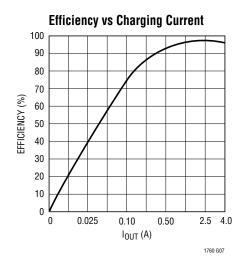

- >95% Efficient Synchronous Buck Charger

- AC Adapter Current Limiting\* Maximizes Charge Rate

- SMBus Accelerator Improves SMBus Timing\*\*

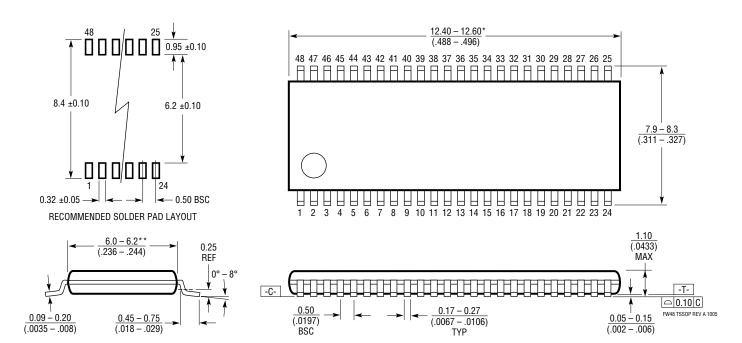

- Available in 48-Lead TSSOP Package

# **APPLICATIONS**

- Portable Computers and Instruments

- Standalone Dual Smart Battery Chargers

- Battery Backup Systems

# DESCRIPTION

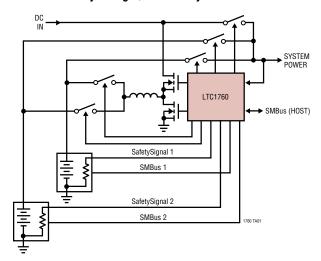

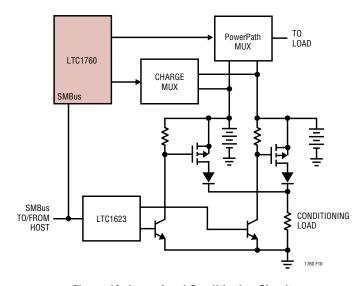

The LTC®1760 Smart Battery System Manager is a highly-integrated SMBus Level 3 battery charger and selector intended for products using dual smart batteries. Three SMBus interfaces allow the LTC1760 to servo to the internal voltage and currents measured by the batteries while allowing an SMBus Host device to monitor either battery's status. Charging accuracy is determined by the battery's internal voltage and current measurements, typically better than ±0.2%.

A proprietary PowerPath architecture supports simultaneous charging or discharging of both batteries. Typical battery run times are extended by up to 10%, while charging times are reduced by up to 50%. The LTC1760 automatically switches between power sources in less than 10µs to prevent power interruption upon battery or wall adapter removal.

The LTC1760 implements all elements of a version 1.1 "Smart Battery System Manager" except for the generation of composite battery information. An internal multiplexer cleanly switches the SMBus Host to either of the two attached Smart Batteries without generating partial messages to batteries or SMBus Host. Thermistors on both batteries are automatically monitored for temperature and disconnection information (SafetySignal).

7, LT, LTC, LTM, Linear Technology and the Linear logo are registered trademarks and PowerPath is a trademark of Analog Devices, Inc. All other trademarks are the property of their respective owners. Protected by U.S. Patents including \*5723970 \*\*6650174.

# TYPICAL APPLICATION

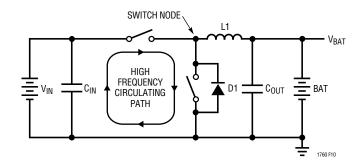

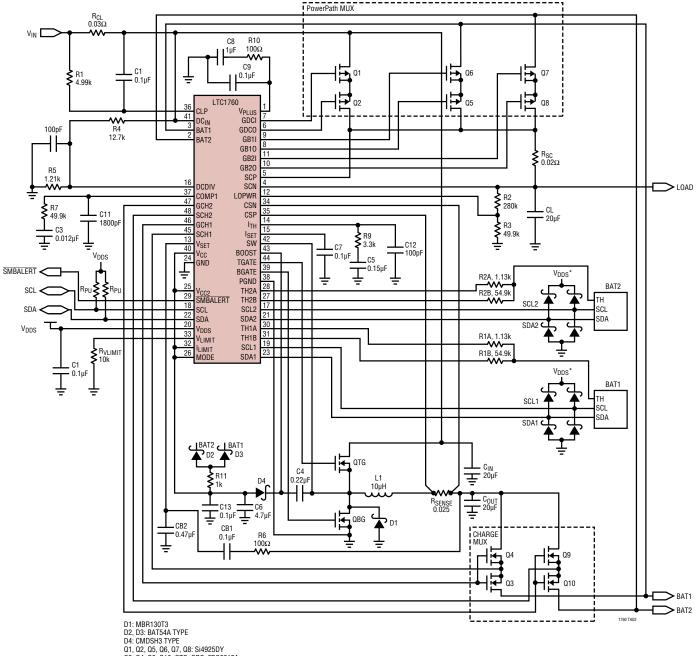

**Dual Battery Charger/Selector System Architecture**

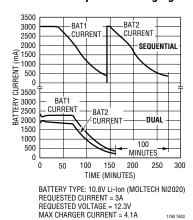

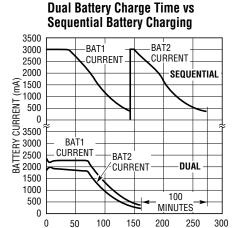

#### **Dual vs Sequential Charging**

# **ABSOLUTE MAXIMUM RATINGS**

#### (Note 1)

| DCIN, SCP, SCN, CLP,                      |

|-------------------------------------------|

| V <sub>PLUS</sub> , SW to GND0.3V to 32V  |

| SCH1, SCH2 to GND0.3V to 28V              |

| BOOST to GND0.3V to 37V                   |

| CSP, CSN, BAT1, BAT2 to GND0.3V to 28V    |

| LOPWR, DCDIV to GND0.3V to 10V            |

| $V_{CC2}$ , $V_{DDS}$ to GND0.3V to 7V    |

| SDA1, SDA2, SDA, SCL1,                    |

| SCL2, SCL, SMBALERT to GND0.3V to 7V      |

| MODE to GND $-0.3V$ to $V_{CC2} + 0.3V$   |

| COMP1 to GND0.3V to 5V                    |

| Maximum DC Current Into Pin               |

| SDA1, SDA2, SDA, SCL1, SCL2, SCL ±3mA     |

| TH1A, TH2A –5mA                           |

| TH1B, TH2B –102μA                         |

| Operating Junction Temperature Range      |

| (Note 6)40°C to 125°C                     |

| Storage Temperature65°C to 150°C          |

| Lead Temperature (Soldering, 10 sec)300°C |

# PIN CONFIGURATION

# ORDER INFORMATION

(http://www.linear.com/product/LTC1760#orderinfo)

| LEAD FREE FINISH | TAPE AND REEL    | PART MARKING | PACKAGE DESCRIPTION   | TEMPERATURE RANGE |

|------------------|------------------|--------------|-----------------------|-------------------|

| LTC1760CFW#PBF   | LTC1760CFW#TRPBF | LTC1760CFW   | 48-Lead Plastic TSSOP | 0°C to 85°C       |

| LTC1760IFW#PBF   | LTC1760IFW#TRPBF | LTC1760IFW   | 48-Lead Plastic TSSOP | -40°C to 125°C    |

Consult LTC Marketing for parts specified with wider operating temperature ranges.

Consult LTC Marketing for information on non-standard lead based finish parts.

For more information on lead free part marking, go to: http://www.linear.com/leadfree/

For more information on tape and reel specifications, go to: http://www.linear.com/tapeandreel/. Some packages are available in 500 unit reels through designated sales channels with #TRMPBF suffix.

**ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes the specifications which apply over the full operating junction temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$  (Note 6).  $V_{DCIN} = 20V$ ,  $V_{BAT1} = 12V$ ,  $V_{BAT2} = 12V$ ,  $V_{VDDS} = 3.3V$ ,  $V_{VCC2} = 5.2V$  unless otherwise noted.

| SYMBOL                                                                        | PARAMETER                                                                                                                                                    | CONDITIONS                                                                                                                                                                                                                                                                                                        |   | MIN                  | TYP                      | MAX                     | UNITS                |

|-------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|----------------------|--------------------------|-------------------------|----------------------|

| Supply an                                                                     | d Reference                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                   |   | <u>I</u>             |                          |                         |                      |

|                                                                               | DCIN Operating Range                                                                                                                                         | DCIN Selected                                                                                                                                                                                                                                                                                                     |   | 6                    |                          | 28                      | V                    |

| I <sub>CH0</sub><br>I <sub>CH1</sub>                                          | DCIN Operating Current                                                                                                                                       | Not Charging (DCIN Selected) (Note 10)<br>Charging (DCIN Selected) (Note 10)                                                                                                                                                                                                                                      |   |                      | 1<br>1.3                 | 1.5<br>2                | mA<br>mA             |

| I <sub>VCC2_AC1</sub>                                                         | V <sub>CC2</sub> Operating Current                                                                                                                           | AC Present (Note 11)<br>AC Not Present (Note 11)                                                                                                                                                                                                                                                                  |   |                      | 0.75<br>75               | 1<br>100                | mA<br>μA             |

|                                                                               | Battery Operating Voltage Range                                                                                                                              | Battery Selected, PowerPath Function<br>Battery Selected, Charging Function (Note 2)                                                                                                                                                                                                                              |   | 6<br>0               |                          | 28<br>28                | V                    |

| I <sub>BAT</sub>                                                              | Battery Drain Current                                                                                                                                        | Battery Selected, Not Charging, V <sub>DCIN</sub> = 0V (Note 10)                                                                                                                                                                                                                                                  |   |                      | 175                      |                         | μA                   |

| V <sub>FDC</sub><br>V <sub>FB1</sub><br>V <sub>FB2</sub><br>V <sub>FSCN</sub> | V <sub>PLUS</sub> Diodes Forward Voltage:<br>DCIN to V <sub>PLUS</sub><br>BAT1 to V <sub>PLUS</sub><br>BAT2 to V <sub>PLUS</sub><br>SCN to V <sub>PLUS</sub> | I <sub>VCC</sub> = 10mA<br>I <sub>VCC</sub> = 0mA<br>I <sub>VCC</sub> = 0mA<br>I <sub>VCC</sub> = 0mA                                                                                                                                                                                                             |   |                      | 0.8<br>0.7<br>0.7<br>0.7 |                         | V<br>V<br>V          |

| UVL0                                                                          | Undervoltage Lockout Threshold                                                                                                                               | V <sub>PLUS</sub> Ramping Down, Measured at V <sub>PLUS</sub> to GND                                                                                                                                                                                                                                              | • | 3                    |                          | 5                       | V                    |

| V <sub>VCC</sub>                                                              | V <sub>CC</sub> Regulator Output Voltage                                                                                                                     |                                                                                                                                                                                                                                                                                                                   | • | 4.9                  | 5.2                      | 5.5                     | V                    |

| $\overline{V_{LDR}}$                                                          | V <sub>CC</sub> Load Regulation                                                                                                                              | No External Connection Beyond Applications Shown<br>Herein                                                                                                                                                                                                                                                        |   |                      | 0.2                      | 1                       | %                    |

| Switching                                                                     | Regulator                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                   | , |                      |                          |                         |                      |

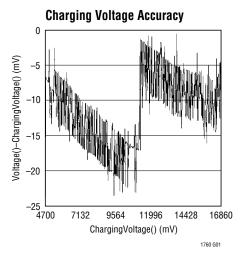

| V <sub>TOL</sub>                                                              | Voltage Accuracy                                                                                                                                             | With Respect to Voltage Reported by Battery V <sub>CHMIN</sub> < Requested Voltage < V <sub>LIMIT</sub>                                                                                                                                                                                                           | • | -32                  |                          | 32                      | mV                   |

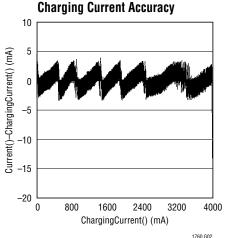

| I <sub>TOL</sub>                                                              | Current Accuracy                                                                                                                                             | With Respect to Current Reported by Battery  4mV/R <sub>SENSE</sub> < Requested Current < I <sub>LIMIT</sub> (Min) (Note 12)  R <sub>ILIMIT</sub> = 0 (Short to GND)  R <sub>ILIMIT</sub> = 10k ±1%  R <sub>ILIMIT</sub> = 33k ±1%  R <sub>ILIMIT</sub> = Open (or Short I <sub>LIMIT</sub> to V <sub>CC2</sub> ) | • | -2<br>-4<br>-8<br>-8 |                          | 2<br>4<br>8<br>8        | mA<br>mA<br>mA<br>mA |

| f <sub>OSC</sub>                                                              | Regulator Switching Frequency                                                                                                                                |                                                                                                                                                                                                                                                                                                                   |   | 255                  | 300                      | 345                     | kHz                  |

| $f_{DO}$                                                                      | Regulator Switching Frequency in Low Dropout Mode                                                                                                            | Duty Cycle ≥99%                                                                                                                                                                                                                                                                                                   |   | 20                   | 25                       |                         | kHz                  |

| DC <sub>MAX</sub>                                                             | Regulator Maximum Duty Cycle                                                                                                                                 |                                                                                                                                                                                                                                                                                                                   |   | 99                   | 99.5                     |                         | %                    |

| I <sub>MAX</sub>                                                              | Maximum Current Sense Threshold                                                                                                                              | V <sub>ITH</sub> = 2.2V                                                                                                                                                                                                                                                                                           |   | 140                  | 155                      | 190                     | mV                   |

| I <sub>SNS</sub>                                                              | CA1 Input Bias Current                                                                                                                                       | V <sub>CSP</sub> = V <sub>CSN</sub> > 5V                                                                                                                                                                                                                                                                          |   |                      | 150                      |                         | μA                   |

| CMSL                                                                          | CA1 Input Common Mode Low                                                                                                                                    |                                                                                                                                                                                                                                                                                                                   |   | 0                    |                          |                         | V                    |

| CMSH                                                                          | CA1 Input Common Mode High                                                                                                                                   |                                                                                                                                                                                                                                                                                                                   |   |                      |                          | V <sub>DCIN</sub> - 0.2 | V                    |

| V <sub>CL1</sub>                                                              | CL1 Turn-On Threshold                                                                                                                                        | C-Grade (Note 6)<br>I-Grade (Note 6)                                                                                                                                                                                                                                                                              | • | 95<br>94<br>90       | 100<br>100<br>100        | 105<br>108<br>108       | mV<br>mV<br>mV       |

| TG t <sub>r</sub>                                                             | TGATE Transition Time:<br>TGATE Rise Time<br>TGATE Fall Time                                                                                                 | C <sub>LOAD</sub> = 3300pF, 10% to 90%<br>C <sub>LOAD</sub> = 3300pF, 10% to 90%                                                                                                                                                                                                                                  |   |                      | 50<br>50                 | 90<br>90                | ns<br>ns             |

| BG t <sub>r</sub><br>BG t <sub>f</sub>                                        | BGATE Transition Time<br>BGATE Rise Time<br>BGATE Fall Time                                                                                                  | C <sub>LOAD</sub> = 3300pF, 10% to 90%<br>C <sub>LOAD</sub> = 3300pF, 10% to 90%                                                                                                                                                                                                                                  |   |                      | 50<br>40                 | 90<br>80                | ns<br>ns             |

**ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes the specifications which apply over the full operating junction temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$  (Note 6).  $V_{DCIN} = 20V$ ,  $V_{BAT1} = 12V$ ,  $V_{BAT2} = 12V$ ,  $V_{VDDS} = 3.3V$ ,  $V_{VCC2} = 5.2V$  unless otherwise noted.

| SYMBOL                               | PARAMETER                                                                 | CONDITIONS                                                                                                                                                                                                                                                                                            |   | MIN                             | TYP                                      | MAX                             | UNITS                |

|--------------------------------------|---------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---------------------------------|------------------------------------------|---------------------------------|----------------------|

| Trip Point                           | s                                                                         |                                                                                                                                                                                                                                                                                                       |   |                                 |                                          |                                 |                      |

| V <sub>TR</sub>                      | DCDIV/LOPWR Threshold                                                     | V <sub>DCDIV</sub> or V <sub>LOPWR</sub> Falling<br>C-Grade (Note 6)<br>I-Grade (Note 6)                                                                                                                                                                                                              | • | 1.166<br>1.162                  | 1.19<br>1.19                             | 1.215<br>1.215                  | V                    |

| V <sub>THYS</sub>                    | DCDIV/LOPWR Hysteresis Voltage                                            | V <sub>DCDIV</sub> or V <sub>LOPWR</sub> Rising                                                                                                                                                                                                                                                       |   |                                 | 30                                       |                                 | mV                   |

| I <sub>BVT</sub>                     | DCDIV/LOPWR Input Bias Current                                            | V <sub>DCDIV</sub> or V <sub>LOPWR</sub> = 1.19V                                                                                                                                                                                                                                                      |   |                                 | 20                                       | 200                             | nA                   |

| V <sub>TSC</sub>                     | Short-Circuit Comparator Threshold                                        | $V_{SCP} - V_{SCN}, V_{CC} \ge 5V$<br>C-Grade (Note 6)<br>I-Grade (Note 6)                                                                                                                                                                                                                            | • | 90<br>88                        | 100<br>100                               | 115<br>115                      | mV<br>mV             |

| $V_{FTO}$                            | Fast PowerPath Turn-Off Threshold                                         | V <sub>DCDIV</sub> Rising from V <sub>CC</sub>                                                                                                                                                                                                                                                        |   | 6                               | 7                                        | 7.9                             | V                    |

| V <sub>OVSD</sub>                    | Overvoltage Shutdown Threshold as a Percent of Programmed Charger Voltage | V <sub>SET</sub> Rising from 0.8V until TGATE and BGATE<br>Stop Switching                                                                                                                                                                                                                             |   |                                 | 107                                      |                                 | %                    |

| DACs                                 | _                                                                         |                                                                                                                                                                                                                                                                                                       |   |                                 |                                          |                                 |                      |

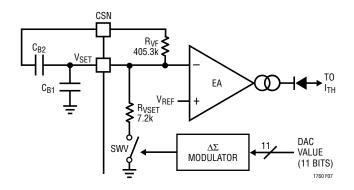

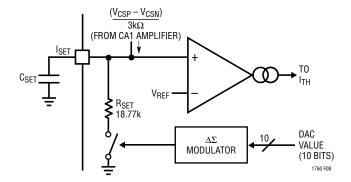

| I <sub>RES</sub>                     | I <sub>DAC</sub> Resolution                                               | Guaranteed Monotonic                                                                                                                                                                                                                                                                                  |   | 10                              |                                          |                                 | Bits                 |

| t <sub>IP</sub><br>t <sub>ILOW</sub> | I <sub>DAC</sub> Pulse Period:<br>Normal Mode<br>Wake-Up Mode             |                                                                                                                                                                                                                                                                                                       |   | 6                               | 10<br>50                                 | 15                              | μs<br>ms             |

|                                      | Charging Current Granularity                                              | R <sub>ILIMIT</sub> = 0 (Short I <sub>LIMIT</sub> to GND) R <sub>ILIMIT</sub> = 10k ±1% R <sub>ILIMIT</sub> = 33k ±1% R <sub>ILIMIT</sub> = Open (or Short I <sub>LIMIT</sub> to V <sub>CC2</sub> )                                                                                                   |   |                                 | 1<br>2<br>4<br>4                         |                                 | mA<br>mA<br>mA<br>mA |

| I <sub>WAKE_UP</sub>                 | Wake-Up Charging Current (Note 5)                                         |                                                                                                                                                                                                                                                                                                       |   | 60                              | 80                                       | 100                             | mA                   |

| I <sub>LIMIT</sub>                   | Charging Current Limit                                                    | C-Grade (Note 6) R <sub>ILIMIT</sub> = 0 (Short I <sub>LIMIT</sub> to GND) R <sub>ILIMIT</sub> = 10k ±1% R <sub>ILIMIT</sub> = 33k ±1% R <sub>ILIMIT</sub> = Open (or Short I <sub>LIMIT</sub> to V <sub>CC2</sub> )                                                                                  | • | 980<br>1960<br>2490<br>3920     | 1000<br>2000<br>3000<br>4000             | 1070<br>2140<br>3210<br>4280    | mA<br>mA<br>mA<br>mA |

|                                      |                                                                           | I-Grade (Note 6)  R <sub>ILIMIT</sub> = 0 (Short I <sub>LIMIT</sub> to GND)  R <sub>ILIMIT</sub> = 10k ±1%  R <sub>ILIMIT</sub> = 33k ±1%  R <sub>ILIMIT</sub> = Open (or Short I <sub>LIMIT</sub> to V <sub>CC2</sub> )                                                                              | • | 930<br>1870<br>2380<br>3750     | 1000<br>2000<br>3000<br>4000             | 1110<br>2220<br>3320<br>4430    | mA<br>mA<br>mA       |

| V <sub>RES</sub>                     | V <sub>DAC</sub> Resolution                                               | Guaranteed Monotonic (5V < V <sub>BAT</sub> < 25V)                                                                                                                                                                                                                                                    |   | 11                              |                                          |                                 | Bits                 |

| V <sub>STEP</sub>                    | V <sub>DAC</sub> Granularity                                              |                                                                                                                                                                                                                                                                                                       |   |                                 | 16                                       |                                 | mV                   |

| V <sub>LIMIT</sub>                   | Charging Voltage Limit<br>(Note 7)                                        | $ \begin{aligned} &R_{VLIMIT} = 0 \text{ (Short } V_{LIMIT} \text{ to GND)} \\ &R_{VLIMIT} = 10 \text{k} \pm 1\% \\ &R_{VLIMIT} = 33 \text{k} \pm 1\% \\ &R_{VLIMIT} = 100 \text{k} \pm 1\% \\ &R_{VLIMIT} = 0 \text{pen (or Short } V_{LIMIT} \text{ to } V_{CC2} \text{ )(Note 13)} \end{aligned} $ | • | 8400<br>12608<br>16832<br>21024 | 8432<br>12640<br>16864<br>21056<br>32768 | 8464<br>12672<br>16896<br>21088 | mV<br>mV<br>mV<br>mV |

| Charge M                             | UX Switches                                                               |                                                                                                                                                                                                                                                                                                       |   |                                 |                                          |                                 |                      |

| tonc                                 | GCH1/GCH2 Turn-On Time                                                    | V <sub>GCHX</sub> - V <sub>SCHX</sub> > 3V, C <sub>LOAD</sub> = 3000pF                                                                                                                                                                                                                                |   |                                 | 5                                        | 10                              | ms                   |

| t <sub>OFFC</sub>                    | GCH1/GCH2 Turn-Off Time                                                   | $V_{GCHX} - V_{SCHX} < 1V$ , from Time of $V_{CSN} < V_{BATX} - 30$ mV, $C_{LOAD} = 3000$ pF                                                                                                                                                                                                          |   |                                 | 15                                       |                                 | μs                   |

| V <sub>CON</sub>                     | CH Gate Clamp Voltage<br>GCH1<br>GCH2                                     | $ \begin{aligned} I_{LOAD} &= 1 \mu A \\ V_{GCH1} &= V_{SCH1} \\ V_{GCH2} &= V_{SCH2} \end{aligned} $                                                                                                                                                                                                 |   | 5<br>5                          | 5.8<br>5.8                               | 7<br>7                          | V<br>V               |

**ELECTRICAL CHARACTERISTICS** The • denotes the specifications which apply over the full operating junction temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$  (Note 6).  $V_{DCIN} = 20V$ ,  $V_{BAT1} = 12V$ ,  $V_{BAT2} = 12V$ ,  $V_{VDDS} = 3.3V$ ,  $V_{VCC2} = 5.2V$  unless otherwise noted.

| SYMBOL                                       | PARAMETER                                                              | CONDITIONS                                                                                                                                                                                                                                        |   | MIN                  | TYP                  | MAX                  | UNITS       |

|----------------------------------------------|------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|----------------------|----------------------|----------------------|-------------|

| V <sub>COFF</sub>                            | CH Gate Off Voltage<br>GCH1<br>GCH2                                    | I <sub>LOAD</sub> =10μA<br>V <sub>GCH1</sub> - V <sub>SCH1</sub><br>V <sub>GCH2</sub> - V <sub>SCH2</sub>                                                                                                                                         |   | -0.8<br>-0.8         | -0.4<br>-0.4         | 0                    | V           |

| V <sub>TOC</sub>                             | CH Switch Reverse Turn-Off Voltage                                     | $V_{BATX} - V_{CSN}$ , $5V \le V_{BATX} \le 28V$<br>C-Grade (Note 6)<br>I-Grade (Note 6)                                                                                                                                                          | • | 5<br>2               | 20<br>20             | 40<br>40             | mV<br>mV    |

| $\overline{V_{FC}}$                          | CH Switch Forward Regulation Voltage                                   | $V_{CSN} - V_{BATX}$ , $5V \le V_{BATX} \le 28V$                                                                                                                                                                                                  | • | 15                   | 35                   | 60                   | mV          |

| I <sub>OC(SRC)</sub>                         | GCH1/GCH2 Active Regulation:<br>Max Source Current<br>Max Sink Current | V <sub>GCHX</sub> – V <sub>SCHX</sub> = 1.5V                                                                                                                                                                                                      |   |                      | -2<br>2              |                      | μΑ<br>μΑ    |

| V <sub>CHMIN</sub>                           | BATX Voltage Below Which<br>Charging is Inhibited                      | (Note 14)                                                                                                                                                                                                                                         |   | 3.5                  |                      | 4.7                  | V           |

| PowerPat                                     | h Switches                                                             |                                                                                                                                                                                                                                                   | • |                      |                      |                      |             |

| t <sub>DLY</sub>                             | Blanking Period after UVLO Trip                                        | Switches Held Off                                                                                                                                                                                                                                 |   |                      | 250                  |                      | ms          |

| t <sub>PPB</sub>                             | Blanking Period after LOPWR Trip                                       | Switches in 3-Diode Mode                                                                                                                                                                                                                          |   |                      | 1                    |                      | sec         |

| t <sub>ONPO</sub>                            | GB10/GB20/GDC0 Turn-On Time                                            | V <sub>GS</sub> < -3V, from Time of Battery/DC<br>Removal, or LOPWR Indication, C <sub>LOAD</sub> = 3000pF                                                                                                                                        | • |                      | 5                    | 10                   | μѕ          |

| t <sub>OFFPO</sub>                           | GB10/GB20/GDC0 Turn-Off Time                                           | V <sub>GS</sub> > -1V, from Time of Battery/DC<br>Removal, or LOPWR Indication, C <sub>LOAD</sub> = 3000pF                                                                                                                                        | • |                      | 3                    | 7                    | μѕ          |

| V <sub>PONO</sub>                            | Output Gate Clamp Voltage<br>GB10<br>GB20<br>GDC0                      | I <sub>LOAD</sub> = 1μA<br>Highest (V <sub>BAT1</sub> or V <sub>SCP</sub> ) – V <sub>GB10</sub><br>Highest (V <sub>BAT2</sub> or V <sub>SCP</sub> ) – V <sub>GB20</sub><br>Highest (V <sub>DCIN</sub> or V <sub>SCP</sub> ) – V <sub>GDC0</sub>   |   | 4.75<br>4.75<br>4.75 | 6.25<br>6.25<br>6.25 | 7<br>7<br>7          | V<br>V<br>V |

| V <sub>POFFO</sub>                           | Output Gate Off Voltage<br>GB10<br>GB20<br>GDC0                        | I <sub>LOAD</sub> = -25µA<br>Highest (V <sub>BAT1</sub> or V <sub>SCP</sub> ) - V <sub>GB10</sub><br>Highest (V <sub>BAT2</sub> or V <sub>SCP</sub> ) - V <sub>GB20</sub><br>Highest (V <sub>DCIN</sub> or V <sub>SCP</sub> ) - V <sub>GDC0</sub> |   |                      | 0.18<br>0.18<br>0.18 | 0.25<br>0.25<br>0.25 | V<br>V<br>V |

| V <sub>TOP</sub>                             | PowerPath Switch Reverse<br>Turn-Off Voltage                           | V <sub>SCP</sub> − V <sub>BATX</sub> or V <sub>SCP</sub> − V <sub>DCIN</sub><br>6V ≤ V <sub>SCP</sub> ≤ 28V<br>C-Grade (Note 6)<br>I-Grade (Note 6)                                                                                               | • | 5<br>2               | 20<br>20             | 60<br>60             | mV<br>mV    |

| $\overline{V_{FP}}$                          | PowerPath Switch Forward<br>Regulation Voltage                         | $V_{BATX} - V_{SCP}$ or $V_{DCIN} - V_{SCP}$<br>6V $\leq V_{SCP} \leq 28V$                                                                                                                                                                        | • | 0                    | 25                   | 50                   | mV          |

| I <sub>OP(SRC)</sub><br>I <sub>OP(SNK)</sub> | GDCI/GB1I/GB2I Active Regulation:<br>Source Current<br>Sink Current    | (Note 3)                                                                                                                                                                                                                                          |   |                      | –4<br>75             |                      | μΑ<br>μΑ    |

| t <sub>ONPI</sub>                            | Gate B1I/B2I/DCI Turn-On Time                                          | V <sub>GS</sub> < -3V, C <sub>LOAD</sub> = 3000pF (Note 4)                                                                                                                                                                                        |   |                      | 300                  |                      | μs          |

| t <sub>OFFPI</sub>                           | Gate B1I/B2I/DCI Turn-Off Time                                         | $V_{GS} > -1V$ , $C_{LOAD} = 3000pF$ (Note 4)                                                                                                                                                                                                     |   |                      | 10                   |                      | μs          |

| V <sub>PONI</sub>                            | Input Gate Clamp Voltage<br>GB1I<br>GB2I<br>GDCI                       | I <sub>LOAD</sub> = 1µA<br>Highest (V <sub>BAT1</sub> or V <sub>SCP</sub> ) – V <sub>GB11</sub><br>Highest (V <sub>BAT2</sub> or V <sub>SCP</sub> ) – V <sub>GB21</sub><br>Highest (V <sub>DCIN</sub> or V <sub>SCP</sub> ) – V <sub>GDCI</sub>   |   | 4.75<br>4.75<br>4.75 | 6.7<br>6.7<br>6.7    | 7.5<br>7.5<br>7.5    | V<br>V<br>V |

| V <sub>POFFI</sub>                           | Input Gate Off Voltage<br>GB1I<br>GB2I<br>GDCI                         | I <sub>LOAD</sub> = -25µA<br>Highest (V <sub>BAT1</sub> or V <sub>SCP</sub> ) - V <sub>GB11</sub><br>Highest (V <sub>BAT2</sub> or V <sub>SCP</sub> ) - V <sub>GB21</sub><br>Highest (V <sub>DCIN</sub> or V <sub>SCP</sub> ) - V <sub>GDC1</sub> |   |                      | 0.18<br>0.18<br>0.18 | 0.25<br>0.25<br>0.25 | V<br>V<br>V |

**ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes the specifications which apply over the full operating junction temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$  (Note 6).  $V_{DCIN} = 20V$ ,  $V_{BAT1} = 12V$ ,  $V_{BAT2} = 12V$ ,  $V_{VDDS} = 3.3V$ ,  $V_{VCC2} = 5.2V$  unless otherwise noted.

| SYMBOL               | PARAMETER                                                                                                                                         | CONDITIONS                                                                                                                                                                  |   | MIN            | TYP    | MAX                     | UNITS        |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|----------------|--------|-------------------------|--------------|

| Thermisto            | or                                                                                                                                                |                                                                                                                                                                             |   |                |        |                         |              |

|                      | Thermistor Trip<br>COLD-RANGE to OVER-RANGE                                                                                                       | $C_{LOAD(MAX)} = 300 pF \text{ (Note 9)}$<br>$R1A = R2A = 1130\Omega \pm 1\%$<br>$R1B = R2B = 54900\Omega \pm 1\%$                                                          | • | 95             | 100    | 105                     | kΩ           |

|                      | Thermistor Trip IDEAL-RANGE to COLD-RANGE                                                                                                         | $C_{LOAD(MAX)} = 300 pF \text{ (Note 9)}$<br>R1A = R2A = 1130 $\Omega$ ±1%<br>R1B = R2B = 54900 $\Omega$ ±1%                                                                | • | 28.5           | 30     | 32.5                    | kΩ           |

|                      | Thermistor Trip<br>HOT-RANGE to IDEAL-RANGE                                                                                                       | $C_{LOAD(MAX)} = 300 pF \text{ (Note 9)}$<br>$R1A = R2A = 1130\Omega \pm 1\%$<br>$R1B = R2B = 54900\Omega \pm 1\%$<br>C-Grade (Note 6)<br>I-Grade (Note 6)                  | • | 2.85<br>2.83   | 3<br>3 | 3.15<br>3.15            | kΩ<br>kΩ     |

|                      | Thermistor Trip<br>UNDER-RANGE to HOT-RANGE                                                                                                       | $C_{LOAD(MAX)} = 300 pF \text{ (Note 9)}$<br>$R1A = R2A = 1130\Omega \pm 1\%$<br>$R1B = R2B = 54900\Omega \pm 1\%$                                                          | • | 425            | 500    | 575                     | Ω            |

| Logic Lev            | els                                                                                                                                               |                                                                                                                                                                             |   |                |        |                         |              |

|                      | SCL/SCL1/SCL2/SDA/SDA1/<br>SDA2 Input Low Voltage (V <sub>IL</sub> )                                                                              |                                                                                                                                                                             | • |                |        | 0.8                     | V            |

|                      | SCL/SCL1/SCL2/SDA/SDA1/<br>SDA2 Input High Voltage (V <sub>IH</sub> )                                                                             |                                                                                                                                                                             | • | 2.1            |        |                         | V            |

|                      | SCL/SCL1/SCL2/SDA/SDA1/<br>SDA2 Input Leakage Current                                                                                             | $V_{SDA}$ , $V_{SCL}$ , $V_{SDA1}$ , $V_{SCL1}$ , $V_{SDA2}$ , $V_{SCL2} = 0.8V$                                                                                            | • | <del>-</del> 5 |        | 5                       | μА           |

|                      | SCL/SCL1/SCL2/SDA/SDA1/<br>SDA2 Input Leakage Current                                                                                             | $ \begin{array}{c} V_{SDA},  V_{SCL},  V_{SDA1},  V_{SCL1},  V_{SDA2}, \\ V_{SCL2} = 2.1 V \end{array} $                                                                    | • | <del>-</del> 5 |        | 5                       | μА           |

| I <sub>PULLUP</sub>  | SCL1/SDA1/SCL2/SDA2 Pull-Up<br>Current When Not Connected to<br>SMBus Host                                                                        | $V_{SCL1}$ , $V_{SDA1}$ , $V_{SCL2}$ , $V_{SDA2}$ = 0.4V $V_{VCC2}$ = 4.85V and 5.55V (Current is Through Internal Series Resistor and Schottky to $V_{CC2}$ )              |   | 165            | 220    | 350                     | μА           |

|                      | SCL1/SDA1/SCL2/SDA2<br>Series Impedance to Host SMBus                                                                                             | $V_{SDA1}$ , $V_{SCL1}$ , $V_{SDA2}$ , $V_{SCL2} = 0.8V$                                                                                                                    | • |                |        | 300                     | Ω            |

|                      | SCL/SDA Output Low Voltage (V <sub>OL</sub> ).<br>LTC1760 Driving the Pin                                                                         | I <sub>PULLUP</sub> = 350μA                                                                                                                                                 | • |                |        | 0.4                     | V            |

|                      | SCL1/SDA1/SCL2/SDA2 Pullup<br>Output Low Voltage (V <sub>OL</sub> ).<br>LTC1760 Driving the Pin with Battery<br>SMBus not Connected to Host SMBus | I <sub>PULLUP</sub> Internal to LTC1760                                                                                                                                     | • |                |        | 0.4                     | V            |

|                      | SCL1/SDA1/SCL2/SDA2<br>Output Low Voltage (V <sub>OL</sub> ).<br>LTC1760 Driving the Pin with Battery<br>SMBus Connected to Host SMBus            | I <sub>PULLUP</sub> = 350μA on Host Side                                                                                                                                    | • |                |        | 0.4                     | V            |

|                      | SCL/SCL1/SCL2/SDA/SDA1/ SDA2/<br>SMBALERT Power Down Leakage                                                                                      | $\begin{aligned} &V_{VCC2} = 0V, \ V_{VDDS} = 0V, \\ &V_{SCL}, \ V_{SCL1}, \ V_{SCL2}, \ V_{SDA}, \\ &V_{SDA1}, \ V_{SDA2}, \ V_{\overline{SMBALERT}} = 5.5V \end{aligned}$ | • |                |        | 2                       | μА           |

|                      | SMBALERT Output Low Voltage (V <sub>OL</sub> )                                                                                                    | I <sub>PULLUP</sub> = 500μA                                                                                                                                                 | • |                |        | 0.4                     | V            |

|                      | SMBALERT Output Pull-Up Current                                                                                                                   | V <sub>SMBALERT</sub> = 0.4V                                                                                                                                                |   | 3.5            | 10     | 17.5                    | μA           |

| V <sub>IL_VDDS</sub> | V <sub>DDS</sub> Input Low Voltage (V <sub>IL</sub> )                                                                                             |                                                                                                                                                                             | • | 0.0            |        | 1.5                     | V            |

| V <sub>IH_VDDS</sub> | V <sub>DDS</sub> Input High Voltage (V <sub>IH</sub> ) V <sub>DDS</sub> Operating Voltage V <sub>DDS</sub> Operating Current                      | $V_{SCL}$ , $V_{SDA} = V_{VDDS}$ , $V_{VDDS} = 5V$                                                                                                                          |   | 2.6<br>3       |        | 5.5<br>18               | V<br>V<br>μA |

| V <sub>IL_MODE</sub> | MODE Input Low Voltage (V <sub>IL</sub> )                                                                                                         | V <sub>VCC2</sub> = 4.85V                                                                                                                                                   | • |                |        | V <sub>VCC2</sub> • 0.3 | V            |

**ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes the specifications which apply over the full operating junction temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$  (Note 6).  $V_{DCIN} = 20V$ ,  $V_{BAT1} = 12V$ ,  $V_{BAT2} = 12V$ ,  $V_{VDDS} = 3.3V$ ,  $V_{VCC2} = 5.2V$  unless otherwise noted.

| SYMBOL                | PARAMETER                                                                                                                                      | CONDITIONS                                                         |   | MIN                     | TYP | MAX  | UNITS |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|---|-------------------------|-----|------|-------|

| V <sub>IH_MODE</sub>  | MODE Input High Voltage (V <sub>IH</sub> )                                                                                                     | V <sub>VCC2</sub> = 4.85V                                          | • | V <sub>VCC2</sub> • 0.7 |     |      | V     |

|                       | MODE Input Current (I <sub>IH</sub> )                                                                                                          | MODE = V <sub>VCC2</sub> • 0.7V, V <sub>VCC2</sub> = 4.85V         | • | -1                      |     | 1    | μA    |

|                       | MODE Input Current (I <sub>IL</sub> )                                                                                                          | MODE = V <sub>VCC2</sub> • 0.3V, V <sub>VCC2</sub> = 4.85V         | • | -1                      |     | 1    | μA    |

| Charger Ti            | iming                                                                                                                                          |                                                                    |   |                         |     |      |       |

| t <sub>TIMEOUT</sub>  | Timeout for Wake-Up Charging and Controlled Charging                                                                                           |                                                                    | • | 140                     | 175 | 210  | sec   |

| t <sub>QUERY</sub>    | Sampling Rate Used by the LTC1760 to Update Charging Parameters                                                                                |                                                                    |   |                         | 1   |      | sec   |

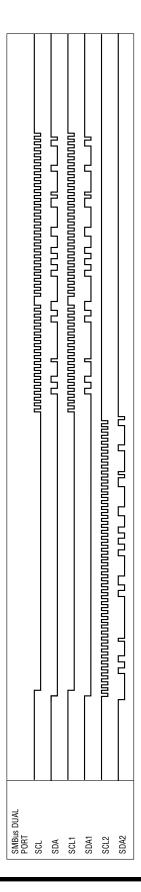

| SMBus Tir             | ming                                                                                                                                           |                                                                    |   |                         |     |      |       |

|                       | SCL Serial-Clock High Period(t <sub>HIGH</sub> )                                                                                               | At I <sub>PULLUP</sub> = 350μA, C <sub>LOAD</sub> = 150pF (Note 8) | • | 4                       |     |      | μs    |

|                       | SCL Serial-Clock Low Period (t <sub>LOW</sub> )                                                                                                | At I <sub>PULLUP</sub> = 350μA, C <sub>LOAD</sub> = 150pF (Note 8) | • | 4.7                     |     |      | μs    |

|                       | SDA/SCL Rise Time (t <sub>r</sub> )                                                                                                            | C <sub>LOAD</sub> = 150pF, RPU = 9.31k (Note 8)                    | • |                         |     | 1000 | ns    |

|                       | SDA/SCL Fall Time (t <sub>f</sub> )                                                                                                            | C <sub>LOAD</sub> = 150pF, RPU = 9.31k (Note 8)                    | • |                         |     | 300  | ns    |

|                       | SMBus Accelerator Trip Voltage Range                                                                                                           |                                                                    | • | 0.8                     |     | 1.42 | V     |

|                       | Start-Condition Setup Time (t <sub>SU:STA</sub> )                                                                                              |                                                                    | • | 4.7                     |     |      | μs    |

|                       | Start-Condition Hold Time (t <sub>HD:STA</sub> )                                                                                               |                                                                    | • | 4                       |     |      | μs    |

|                       | SDA to SCL Rising-Edge<br>Setup Time (t <sub>SU:DAT</sub> )                                                                                    |                                                                    | • | 250                     |     |      | ns    |

|                       | SDA to SCL Falling-Edge Hold Time,<br>Slave Clocking in Data (t <sub>HD:DAT</sub> )                                                            |                                                                    | • | 300                     |     |      | ns    |

| t <sub>TIMEOUT_</sub> | The LTC1760 will Release the SMBus<br>and Terminate the Current Master or<br>Slave Command if the Command is not<br>Completed Before this Time |                                                                    | • | 25                      |     | 35   | ms    |

**Note 1:** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

**Note 2:** Battery voltage must be adequate to drive gates of PowerPath P-channel FET switches. This does not affect charging voltage of the battery, which can be zero volts during wake-up charging.

**Note 3:** DCIN, BAT1, BAT2 are held at 12V and GDCI, GB1I, GB2I are forced to 10.5V. SCP is set at 12V to measure source current at GDCI, GB1I and GB2I. SCP is set at 11.9V to measure sink current at GDCI, GB1I and GB2I.

**Note 4:** Extrapolated from testing with  $C_L = 50 pF$ .

**Note 5:** Accuracy dependent upon external sense resistor and compensation components.

**Note 6:** The LTC1760 is tested under pulsed load conditions such that  $T_J \approx T_A$ . The LTC1760C is guaranteed to meet specifications from 0°C to 70°C junction temperature. Specifications over the -40°C to 85°C operating junction temperature range are assured by design, characterization and correlation with statistical process controls. The LTC1760I is guaranteed over the -40°C to 125°C operating junction temperature range.

**Note 7:** Charger servos to the value reported by a Voltage() query. This is the internal cell voltage measured by the battery electronics and may be

lower than the terminal voltage. Refer to "Operation Section 3.7" for more information.

**Note 8:**  $C_{LOAD}$  is the combined capacitance on the host's SMBus connection and the selected battery's SMBus connection.

**Note 9:** C<sub>LOAD\_MAX</sub> is the maximum allowed combined capacitance on THxA, THxB and the battery's SafetySignalx connections.

Note 10: Does not include current supplied by  $V_{CC}$  to  $V_{CC2}$  (I\_{VCC2\\_AC1} or I\_vCC2\_AC0)

**Note 11:** Measured with thermistors not present,  $R_{VLIMIT}$  and  $R_{ILIMIT}$  removed and  $\overline{SMBALERT}$  = 1. See Applications Information section: "Calculating IC Operating Current" for example on how to calculate total IC operating current.

**Note 12:** Requested currents below 44mV/R<sub>SENSE</sub> may not servo correctly due to charger offsets. The charging current for requested currents below 4mV/R<sub>SENSE</sub> will be between 4mV/R<sub>SENSE</sub> and (Requested Current – 8mA). Refer to Applications Information: "Setting Charger Output Current Limit" for values of R<sub>SENSE</sub>.

**Note 13:** This limit is greater than the absolute maximum for the charger. Therefore, there is no effective limitation for the voltage when this option is selected.

Note 14: Does not apply to Wake-Up Mode.

# TYPICAL PERFORMANCE CHARACTERISTICS

BATTERY TYPE: 10.8V Li-Ion (MOLTECH NI2020) REQUESTED CURRENT = 3A REQUESTED VOLTAGE = 12.3V MAX CHARGER CURRENT = 4.1A

TIME (MINUTES)

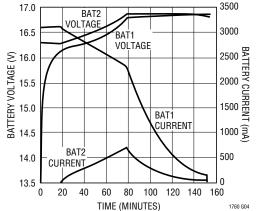

#### Dual Charging Batteries with Different Charge State

BAT1 INITIAL CAPACITY = 0% BAT2 INITIAL CAPACITY = 90% PROGRAMMED CHARGER CURRENT = 3A PROGRAMMED CHARGER VOLTAGE = 16.8V

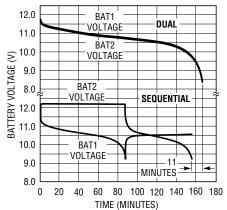

#### Dual Battery Discharge Time vs Sequential Battery Discharge (Li-lon)

BATTERY TYPE: 10.8V Li-lon (MOLTECH NI2020) LOAD CURRENT = 3A 1760 GO

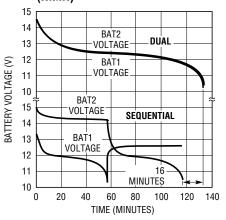

#### Dual Battery Dischage Time vs Sequential Battery Discharge (NiMH)

BATTERY TYPE: 12V NIMH (MOLTECH NJ1020) LOAD: 33W 1760 G06

# TYPICAL PERFORMANCE CHARACTERISTICS

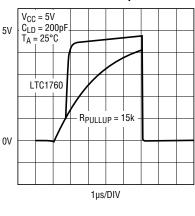

#### PowerPath Switching 1 and 2

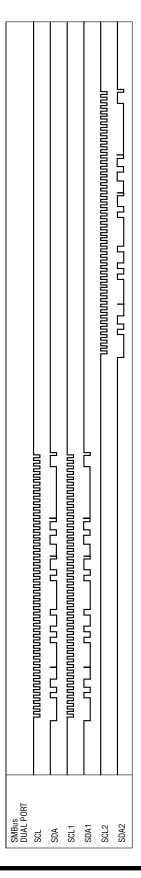

#### **SMBus Accelerator Operation**

1760 G11

# PIN FUNCTIONS

#### Input Power Related

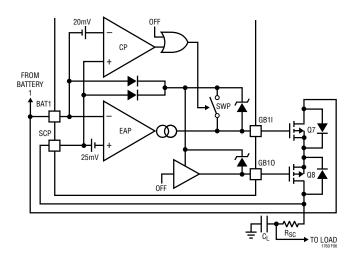

**SCN (Pin 4):** PowerPath Current Sensing Negative Input. This pin should be connected directly to the "bottom" (output side) of the sense resistor, R<sub>SC</sub>, in series with the three PowerPath switch pairs, for detecting short-circuit current events. Also powers the LTC1760 internal circuitry when all other sources are absent.

**SCP (Pin 5):** PowerPath Current Sensing Positive Input. This pin should be connected directly to the "top" (switch

side) of the sense resistor,  $R_{SC}$ , in series with the three PowerPath switch pairs, for detecting short-circuit current events.

**GDCO (Pin 6):** DCIN Output Switch Gate Drive. Together with GDCI, this pin drives the gate of the P-channel switch in series with the DCIN input switch.

**GDCI (Pin 7):** DCIN Input Switch Gate Drive. Together with GDCO, this pin drives the gate of the P-channel switch connected to the DCIN input.

# PIN FUNCTIONS

**GB10 (Pin 8):** BAT1 Output Switch Gate Drive. Together with GB1I, this pin drives the gate of the P-channel switch in series with the BAT1 input switch.

**GB11 (Pin 9):** BAT1 Input Switch Gate Drive. Together with GB10, this pin drives the gate of the P-channel switch connected to the BAT1 input.

**GB20 (Pin 10):** BAT2 Output Switch Gate Drive. Together with GB2I, this pin drives the gate of the P-channel switch in series with the BAT2 input switch.

**GB21 (Pin 11):** BAT2 Input Switch Gate Drive. Together with GB2O, this pin drives the gate of the P-channel switch connected to the BAT2 input.

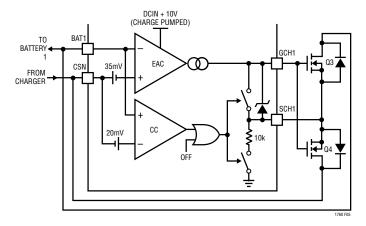

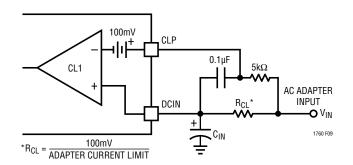

**CLP (Pin 36):** The Positive Input to the Supply Current Limiting Amplifier CL1. The threshold is set at 100mV above the voltage at the DCIN pin. When used to limit supply current, a filter is needed to filter out the switching noise.

#### **Battery Charging Related**

$V_{SET}$  (Pin 13): The Tap Point of a Programmable Resistor Divider which Provides Battery Voltage Feedback to the Charger. A capacitor from CSN to  $V_{SET}$  and from  $V_{SET}$  to GND provide necessary compensation and filtering for the voltage loop.

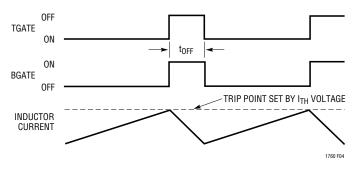

$I_{TH}$  (Pin 14): The Control Signal of the Inner Loop of the Current Mode PWM. Higher  $I_{TH}$  voltage corresponds to higher charging current in normal operation. A capacitor of at least 0.1μF to GND filters out PWM ripple. Typical full-scale output current is 30μA. Nominal voltage range for this pin is 0V to 2.4V.

**I<sub>SET</sub>** (**Pin 15**): A capacitor from I<sub>SET</sub> to GND is required to filter higher frequency components from the delta-sigma I<sub>DAC</sub>.

$I_{LIMIT}$  (Pin 32): An external resistor ( $R_{ILIMIT}$ ) is connected between this pin and GND. The value of the external resistor programs the range and resolution of the programmed charger current.

**V<sub>LIMIT</sub> (Pin 33):** An external resistor (R<sub>VLIMIT</sub>) is connected between this pin and GND. The value of the external resistor programs the range and resolution of the voltage DAC.

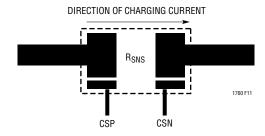

**CSN (Pin 34):** Current Amplifier CA1 Input. Connect this to the common output of the charger MUX switches.

**CSP (Pin 35):** Current Amplifier CA1 Input. This pin and the CSN pin measure the voltage across the charge current sense resistor,  $R_{SENSE}$ , to provide the instantaneous current signals required for both peak and average current mode operation.

**COMP1 (Pin 37):** The Compensation Node for the Amplifier CL1. A capacitor is required from this pin to GND if input current amplifier CL1 is used. At input adapter current limit, this node rises to 1V. By forcing COMP1 to GND, amplifier CL1 will be defeated (no adapter current limit). COMP1 can source  $10\mu A$ .

**BGATE (Pin 39):** Drives the gate of the bottom external MOSFET of the battery charger buck converter.

**SW (Pin 42):** PWM Switch Node. Connected to the source of the top external MOSFET. Used as reference for top gate driver.

**BOOST (Pin 43):** Supply to Topside Floating Driver. The bootstrap capacitor is returned to this pin. Voltage swing at this pin is from a diode drop below  $V_{CC}$  to (DCIN +  $V_{CC}$ ).

**TGATE (Pin 44):** Drives the gate of the top external MOSFET of the battery charger buck converter.

SCH1 (Pin 45), SCH2 (Pin 48): Charger MUX N-Channel Switch Source Returns. These two pins are connected to the sources of the back-to-back switch pairs Q3/Q4 and Q9/Q10 (see Typical Applications). A small pull-down current source returns these nodes to 0V when the switches are turned off.

**GCH1 (Pin 46), GCH2 (Pin 47):** Charger MUX N-Channel Switch Gate Drives. These two pins drive the gates of the back-to-back switch pairs, Q3/Q4 and Q9/Q10, between the charger output and the two batteries (see Typical Applications).

#### **External Power Supply Pins**

**V<sub>PLUS</sub>** (**Pin 1**): Supply. The V<sub>PLUS</sub> pin is connected via four internal diodes to the DCIN, SCN, BAT1, and BAT2 pins. Bypass this pin with a  $0.1\mu F$  capacitor and a  $1\mu F$  capacitor (see Typical Applications for complete circuit).

**BAT1 (Pin 3), BAT2 (Pin 2):** These two pins are the inputs from the two batteries for power to the LTC1760.

# PIN FUNCTIONS

**LOPWR (Pin 12):** LOPWR Comparator Input from SCN External Resistor Divider to GND. If the voltage at LOPWR pin is lower than the LOPWR comparator threshold, then system power has failed and power is autonomously switched to a higher voltage source, if available.

**DCDIV** (**Pin 16**): External DC Source Comparator Input from DCIN External Resistor Divider to GND. If the voltage at DCDIV pin is above the DCDIV comparator threshold, then the AC\_PRESENT bit is set and the wall adapter power is considered to be adequate to charge the batteries. If DCDIV rises more than 1.8V above  $V_{CC}$ , then all of the power path switches are latched off until all power is removed. A capacitor from DCDIV to GND is recommended to prevent noise-induced false emergency turn-off conditions from being detected. Refer to "Section 8.3" and "Typical Application".

**DCIN (Pin 41):** Supply. External DC power source. A  $0.1\mu F$  bypass capacitor must be connected to this pin as close as possible. No series resistance is allowed, since the adapter current limit comparator input is also this pin.

## Internal Power Supply Pins

**V<sub>DDS</sub>** (**Pin 20**): Power Supply for SMBus Accelerators. Also used in conjunction with MODE pin to modify the LTC1760 operating mode.

GND (Pin 24): Ground for Low Power Circuitry.

$V_{CC2}$  (Pin 25): Power Supply is used Primarily to Power Internal Logic Circuitry. Must be connected to  $V_{CC}$ .

**PGND (Pin 38):** High Current Ground Return for BGATE Driver.

$V_{CC}$  (Pin 40): Internal Regulator Output. Bypass this output with at least a  $2\mu F$  to  $4.7\mu F$  capacitor. Do not use this regulator output to supply external circuitry except as shown in the application circuit.

#### SBS Interface Pins

**SCL2 (Pin 17):** SMBus Clock Signal to Smart Battery 2. Do not connect to an external pull-up. The LTC1760 connects this pin to an internal pull-up (I<sub>PULLUP</sub>) when required.

**SCL (Pin 18):** SMBus Clock Signal to SMBus Host. Also used to determine flashing rate for stand-alone charge indi-

cators. Requires an external pullup to V<sub>DDS</sub> (normal SMBus operating mode). Connected to internal SMBus accelerator.

**SCL1 (Pin 19):** SMBus Clock Signal to Smart Battery 1. Do not connect to an external pull-up. The LTC1760 connects this pin to an internal pull-up (I<sub>PULLUP</sub>) when required.

**SDA2 (Pin 21):** SMBus Data Signal to Smart Battery 2. Do not connect to an external pull-up. The LTC1760 connects this pin to an internal pull-up ( $I_{PULLUP}$ ) when required.

**SDA (Pin 22):** SMBus Data Signal to SMBus Host. Also used to indicate charging status of Battery 2. Requires an external pullup to  $V_{DDS}$ . Connected to internal SMBus accelerator.

**SDA1 (Pin 23):** SMBus Data Signal to Smart Battery 1. Do not connect to an external pull-up. The LTC1760 connects this pin to an internal pull-up (I<sub>PULLUP</sub>) when required.

**MODE (Pin 26):** Used in conjunction with  $V_{DDS}$  to allow SCL, SDA and  $\overline{SMBALERT}$  to indicate charging status. May also be used as a hardware charge inhibit.

**TH2B (Pin 27):** Thermistor Force/Sense Connection to Smart Battery 2 SafetySignal. Connect to Battery 2 thermistor through resistor network shown in "Typical Application."

**TH2A (Pin 28):** Thermistor Force/Sense Connection to Smart Battery 2 SafetySignal. Connect to Battery 2 thermistor through resistor network shown in "Typical Application."

**SMBALERT** (**Pin 29**): Active Low Interrupt Pin. Signals SMBus Host that there has been a change of status in battery or AC presence. Open drain with weak current source pull-up to  $V_{CC2}$  (with Schottky to allow it to be pulled to 5V externally). Also used to indicate charging status of Battery 1.

**TH1A (Pin 30):** Thermistor Force/Sense Connection to Smart Battery 1 SafetySignal. Connect to Battery 1 thermistor through resistor network shown in "Typical Application."

**TH1B (Pin 31):** Thermistor Force/Sense Connection to Smart Battery 1 SafetySignal. Connect to Battery 1 thermistor through resistor network shown in "Typical Application."

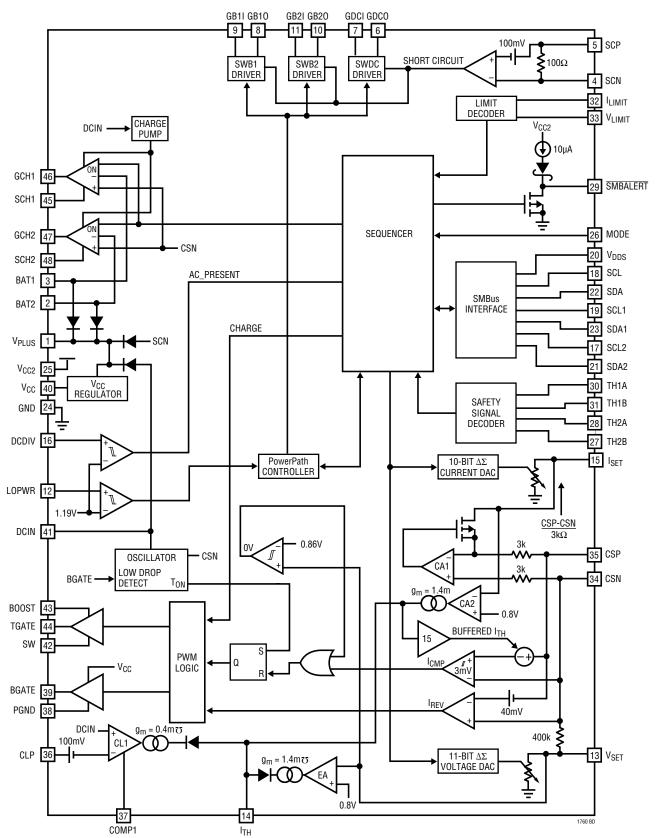

# **BLOCK DIAGRAM**

# TABLE OF CONTENTS (For Operation Section)

|   | Overview                                                               |       |          |

|---|------------------------------------------------------------------------|-------|----------|

| 2 | The SMBus Interface                                                    |       |          |

|   | 2.1 SMBus Interface Overview                                           |       |          |

|   | 2.3 Description of Supported SMBus Functions                           | . 17  | 7        |

|   | 2.3.1 BatterySystemState() (0×01)                                      |       |          |

|   | 2.3.2 BatterySystemStateCont() (0×02)                                  | 18    | 3        |

|   | 2.3.3 BatterySystemInfo() (0×04)                                       |       |          |

|   | 2.3.4 LTC() (0×3C)                                                     |       |          |

|   | 2.3.5 BatteryMode() (0×03)                                             |       |          |

|   | 2.3.6 Voltage() (0×09)                                                 |       |          |

|   |                                                                        |       |          |

|   | 2.3.7 Current() (0×0A)                                                 |       |          |

|   | 2.3.8 ChargingCurrent() (0×14)                                         |       |          |

|   | 2.3.9 ChargingVoltage() (0×15)                                         |       |          |

|   | 2.3.10 AlarmWarning() (0×16)                                           |       |          |

|   | 2.3.11 AlertResponse()                                                 |       |          |

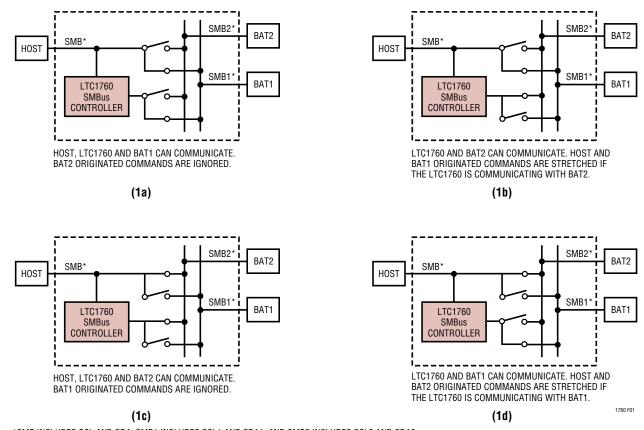

|   | 2.4 SMBus Dual Port Operation                                          |       |          |

|   | 2.5 LTC1760 SMBus Controller Operation                                 |       |          |

|   | 2.6 LTC1760 SMBALERT Operation                                         |       |          |

| 3 | Charging Algorithm Overview                                            | . 26  | j        |

|   | 3.1 Wake-Up Charging Initiation                                        | . 26  | ì        |

|   | 3.2 Wake-Up Charging Termination                                       | . 26  | ò        |

|   | 3.3 Wake-Up Charging Current and Voltage Limits                        |       |          |

|   | 3.4 Controlled Charging Initiation                                     | . 27  | 7        |

|   | 3.5 Controlled Charging Termination                                    | 27    | 7        |

|   | 3.6 Controlled Charging Current Programming                            |       |          |

|   | 3.6.1 Current Limits When Charging A Single Battery                    |       |          |

|   | 3.6.2 Current Limits When Charging Two Batteries (TURBO Mode Disabled) |       |          |

|   | 3.6.3 Current Limits When Charging Two Batteries (TURBO Mode Enabled)  | . Z0  | )<br>\   |

|   | 5.0.5 Currented Chessing Voltage Deservations                          | . ZIJ | <i>)</i> |

| , | 3.7 Controlled Charging Voltage Programming                            | . 29  | ,        |

| 4 | System Power Management Algorithm and Battery Calibration              | . 29  | ,        |

|   | 4.1 Turning Off System Power                                           | . 29  | ,        |

|   | 4.2 Power-By Algorithm When No Battery is Being Calibrated             | . 29  | )        |

|   | 4.3 Power-By Algorithm When a Battery is Being Calibrated              | . 30  | )        |

|   | 4.4 Power-By Reporting                                                 |       |          |

| 5 | Battery Calibration (Conditioning)                                     | . 30  | )        |

|   | 5.1 Selecting a Battery to be Calibrated                               |       |          |

|   | 5.2 Initiating Calibration of Selected Battery                         | . 31  | ı        |

|   | 5.3 Terminating Calibration of Selected Battery                        | . 31  | ĺ        |

| 6 | MODE Pin Operation                                                     |       |          |

|   | 6.1 Standalone Charge Indication                                       |       |          |

|   | 6.2 Hardware Charge Inhibit                                            | . 32  | )        |

|   | 6.3 Charging When SCL And SDA Are Low.                                 |       |          |

|   | 6.4 Charging With an SMBus Host                                        |       |          |

| 7 | Battery Charger Controller                                             |       |          |

| 1 | 7.1 Charge MUX Switches                                                |       |          |

|   |                                                                        |       |          |

| 0 | 7.2 Dual Charging                                                      |       |          |

| Ŏ | PowerPath Controller                                                   |       |          |

|   | 8.1 Autonomous PowerPath Switching                                     |       |          |

|   | 8.2 Short-Circuit Protection                                           |       |          |

|   | 8.3 Emergency Turn-Off                                                 |       |          |

|   | 8.4 Power-Up Strategy                                                  | . 34  | į        |

|   | The Voltage DAC Block                                                  |       |          |

|   | The Current DAC Block                                                  |       |          |

# **OPERATION** (Refer to Block Diagram and Typical Application Figure)

#### 1 Overview