# Configurable, High *g, i*MEMS Accelerometer

Data Sheet ADXL180

#### **FEATURES**

Wide sensor range: 50 g to 500 g

Adjustable filter bandwidth: 100 Hz to 800 Hz

Configurable communication protocol

2-wire, current mode bus interface

Selectable sensor data resolution: 8 bit or 10 bit

Continuous auto-zero

Fully differential sensor and interface circuitry

High resistance to EMI/RFI

Sensor self-test

5.0 V to 14.5 V operation

8 bits of user-defined OTP memory

32-bit electronic serial number

Dual device per bus option

#### **APPLICATIONS**

**Crash sensing**

#### **GENERAL DESCRIPTION**

The ADXL180 *i*MEMS\* accelerometer is a configurable, single axis, integrated satellite sensor that enables low cost solutions for front and side impact airbag applications. Acceleration data is sent to the control module via a digital 2-wire current loop interface bus. The communication protocol is programmable for compatibility with various automotive interface bus standards.

The sensor g range is configurable to provide full-scale ranges from  $\pm 50~g$  to  $\pm 500~g$ . The sensor signal third-order, low-pass Bessel filter bandwidth is configurable at 100 Hz, 200 Hz, 400 Hz, and 800 Hz.

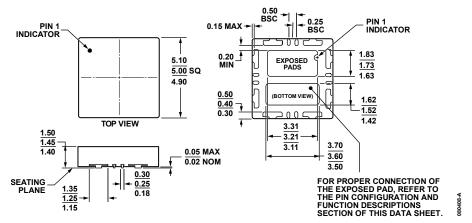

The 10-bit analog-to-digital converter (ADC) allows either 8-bit or 10-bit acceleration data to be transmitted to the control module. Each part has a unique electronic serial number. The device is rated for operation from  $-40^{\circ}$ C to  $+125^{\circ}$ C and is available in a 5 mm  $\times$  5 mm LFCSP package.

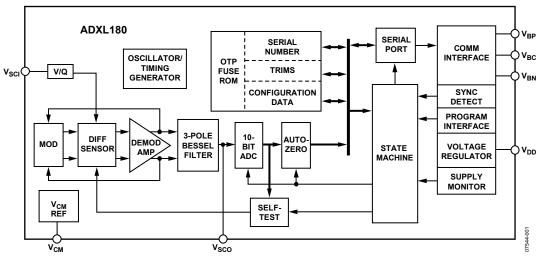

#### **FUNCTIONAL BLOCK DIAGRAM**

Figure 1.

Data Sheet

## **ADXL180**

## **TABLE OF CONTENTS**

| Features 1                                                 | Phase 2: Mode Description                                     | 30 |

|------------------------------------------------------------|---------------------------------------------------------------|----|

| Applications1                                              | Phase 3: Self-Test Diagnostic                                 | 37 |

| General Description1                                       | Phase 4: Auto-Zero Initialization4                            | 40 |

| Functional Block Diagram1                                  | Phase 5: Normal Operation4                                    | 40 |

| Revision History                                           | Signal Range and Filtering4                                   | 41 |

| Specifications4                                            | Transfer Function Overview4                                   | 41 |

| Absolute Maximum Ratings7                                  | Range4                                                        | 41 |

| ESD Caution                                                | Three-Pole Bessel Filter4                                     | 41 |

| Pin Configuration and Function Descriptions8               | Auto-Zero Operation4                                          | 41 |

| Terminology9                                               | Error Detection                                               | 43 |

| Theory of Operation10                                      | Overview4                                                     | 43 |

| Overview10                                                 | Parity Error Due to Communications Protocol Configuration     |    |

| Acceleration Sensor                                        | Bit Error                                                     |    |

| Signal Processing11                                        | Self-Test Error                                               | 44 |

| Digital Communications State Machine11                     | Offset Error/Offset Drift Monitoring4                         | 44 |

| 2-Wire Current Modulated Interface11                       | Voltage Regulator Monitor Reset Operation 4                   |    |

| Synchronous Operation and Dual Device Bus11                | Test and Diagnostic Tools                                     | 45 |

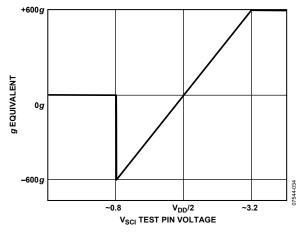

| Programmed Memory and Configurability11                    | V <sub>SCI</sub> Signal Chain Input Test Pin4                 | 45 |

| Physical Interface13                                       | V <sub>SCO</sub> Analog Signal Chain Output Test Pin 4        | 45 |

| Application Circuit13                                      | Configuration Specification                                   | 46 |

| Current Modulation13                                       | Overview4                                                     | 46 |

| Manchester Data Encoding14                                 | Configuration Mode Transmit Communications Protocol 4         | 47 |

| Operation at Low V <sub>BP</sub> or Low V <sub>DD</sub> 14 | Configuration Mode Command (Receive) Communications           |    |

| Operation at High V <sub>DD</sub> 14                       | Protocol                                                      |    |

| Communications Timing and Bus Topologies15                 | Configuration Mode Communications Handshaking 4               |    |

| Data Transmission15                                        | Configuration and User Data Registers                         |    |

| Asynchronous Communication16                               | Configuration Mode Exit                                       | 50 |

| Synchronous Communication17                                | Serial Number and Manufacturer Identification Data Registers5 | 50 |

| Synchronous Communication Mode—Dual Device 19              | Programming the Configuration and User Data Registers 5       |    |

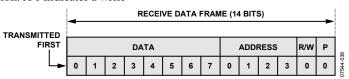

| Data Frame Definition23                                    | OTP Programming Conditions and Considerations 5               |    |

| Data Frame Transmission Format23                           | Configuration/User Register OTP Parity                        |    |

| Data Frame Configuration Options23                         | Configuration Mode Error Reporting                            |    |

| Acceleration Data Coding25                                 | Configuration Register Reference                              |    |

| State Vector Coding26                                      | UD[7:0] User Data Bits                                        |    |

| State Vector Descriptions26                                | UD8 Configuration Bit                                         |    |

| Transmission Error Detection Options27                     | BDE                                                           |    |

| Application Layer: Communication Protocol State Machine 28 | SCOE                                                          |    |

| ADXL180 State Machine28                                    | FDLY                                                          |    |

| Phase 1: Power-on-Reset Initialization28                   | ADME5                                                         |    |

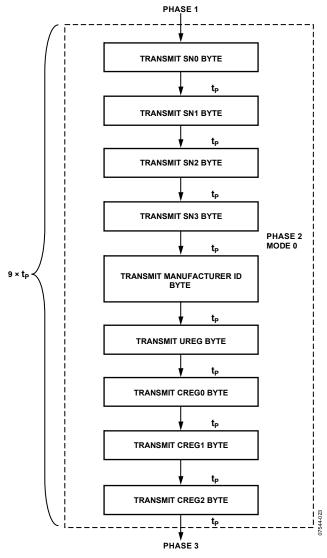

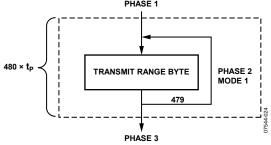

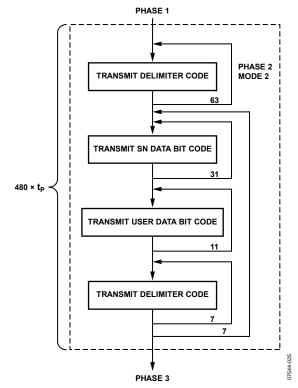

| Phase 2: Device Data Transmission28                        | STI                                                           |    |

|                                                            | 5-11                                                          |    |

| FC[1:0]                                                                       | 53 |

|-------------------------------------------------------------------------------|----|

| RG[2:0]                                                                       | 53 |

| MD[1:0]                                                                       | 54 |

| SYEN                                                                          | 55 |

| AZE                                                                           | 55 |

| ERC                                                                           | 55 |

| DAT                                                                           | 55 |

|                                                                               |    |

| REVISION HISTORY                                                              |    |

| KEVISION HISTORT                                                              |    |

| 1/2018—Rev. A to Rev. B                                                       |    |

|                                                                               | 28 |

| 1/2018—Rev. A to Rev. B                                                       |    |

| 1/2018—Rev. A to Rev. B Updated Outline Dimensions                            |    |

| 1/2018—Rev. A to Rev. B Updated Outline Dimensions Change to Ordering Guide   | 58 |

| 1/2018—Rev. A to Rev. B  Updated Outline Dimensions  Change to Ordering Guide | 58 |

| 1/2018—Rev. A to Rev. B  Updated Outline Dimensions                           |    |

| 1/2018—Rev. A to Rev. B  Updated Outline Dimensions  Change to Ordering Guide | 15 |

| 1/2018—Rev. A to Rev. B  Updated Outline Dimensions                           |    |

| 1/2018—Rev. A to Rev. B  Updated Outline Dimensions                           |    |

8/2008—Revision 0: Initial Version

| δVD                 | 33 |

|---------------------|----|

| CUPAR and CUPRG     | 55 |

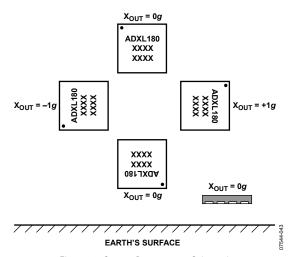

| Axis of Sensitivity | 56 |

| Branding            | 57 |

| Outline Dimensions  | 58 |

| Ordering Guide      | 58 |

## **SPECIFICATIONS**

$T_A = -40$ °C to +125°C,  $V_{BP} - V_{BN} = 5.0$  V to 14.5 V,  $f_{LP} = 400$  Hz, acceleration = 0 g, unless otherwise noted.

Table 1.

| Parameter <sup>1</sup>             | Symbol   | Min            | Тур         | Max        | Unit           | Test Conditions/Comments             |

|------------------------------------|----------|----------------|-------------|------------|----------------|--------------------------------------|

| SENSOR                             |          |                |             |            |                |                                      |

| Scale Factor                       |          |                |             |            |                | Measurement frequency: 100 Hz        |

| 50 <i>g</i> Range                  |          |                |             |            |                | See Table 37                         |

| 8-Bit Data                         |          | 0.465          | 0.50        | 0.535      | g/LSB          |                                      |

| 10-Bit Data                        |          | 0.116          | 0.1250      | 0.134      | g/LSB          |                                      |

| 100 <i>g</i> Range                 |          |                |             |            |                |                                      |

| 8-Bit Data                         |          | 0.930          | 1.00        | 1.070      | g/LSB          |                                      |

| 10-Bit Data                        |          | 0.233          | 0.2500      | 0.268      | g/LSB          |                                      |

| 150 <i>g</i> Range                 |          |                |             |            |                |                                      |

| 8-Bit Data                         |          | 1.395          | 1.50        | 1.605      | g/LSB          |                                      |

| 10-Bit Data                        |          | 0.349          | 0.3750      | 0.401      | g/LSB          |                                      |

| 200 <i>g</i> Range                 |          |                |             |            |                |                                      |

| 8-Bit Data                         |          | 1.860          | 2.00        | 2.140      | g/LSB          |                                      |

| 10-Bit Data                        |          | 0.465          | 0.5000      | 0.535      | g/LSB          |                                      |

| 250 <i>g</i> Range                 |          |                |             |            |                |                                      |

| 8-Bit Data                         |          | 2.325          | 2.50        | 2.675      | g/LSB          |                                      |

| 10-Bit Data                        |          | 0.581          | 0.625       | 0.669      | g/LSB          |                                      |

| 350 <i>g</i> Range                 |          | 0.00.          | 0.025       | 0.002      | 9, 200         |                                      |

| 8-bit Data                         |          | 3.255          | 3.50        | 3.745      | g/LSB          |                                      |

| 10-bit Data                        |          | 0.830          | 0.8925      | 0.955      | g/LSB          |                                      |

| 500 <i>g</i> Range                 |          | 0.030          | 0.0723      | 0.733      | 9/130          |                                      |

| 8-Bit Data                         |          | 4.650          | 5.00        | 5.350      | g/LSB          |                                      |

| 10-Bit Data                        |          | 1.163          | 1.2500      | 1.338      | g/LSB<br>g/LSB |                                      |

| Offset                             |          | 1.103          | 1.2300      | 1.550      | g/L3b          | All ranges, auto-zero disabled       |

| 8-Bit Data                         |          | -12            |             | +11        | LSB            | All fallges, auto-zelo disabled      |

| 10-Bit Data                        |          | -12<br>-48     |             | +11<br>+47 | LSB            |                                      |

|                                    |          | <del>-40</del> |             | +47        | LOD            | E0 a rango                           |

| Noise (Peak-to-Peak)<br>8-Bit Data |          |                |             | 2          | LSB            | 50 <i>g</i> range<br>10 Hz to 400 Hz |

|                                    |          |                | 2           | 2          |                |                                      |

| 10-Bit Data                        |          |                | 2           | 3          | LSB            | 10 Hz to 400 Hz                      |

| Self Test                          |          | 20             | 25          | 20         |                |                                      |

| Amplitude                          |          | 20             | 25          | 30         | g              | CT T                                 |

| Internal Self-Test Limit           |          | 20             |             | 30         | g              | STI enabled, see Table 35            |

| Nonlinearity                       |          | _              | 0.2         | 2          | %              | Of full-scale range                  |

| Cross-Axis Sensitivity             |          | <b>-</b> 5     |             | +5         | %              |                                      |

| Resonant Frequency                 |          |                | 12.8        |            | kHz            |                                      |

| Q                                  |          |                | 1.5         |            |                |                                      |

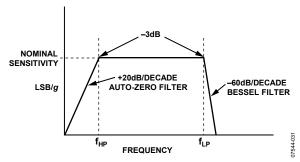

| LOW-PASS FILTER                    |          |                |             |            |                |                                      |

| Frequency Response                 |          |                | Third-order |            |                |                                      |

| Daga Dagad                         | _        |                | Bessel      |            |                | Drague manable con Table 20          |

| Pass Band                          | $f_{LP}$ | 670            | 000         | 000        |                | Programmable, see Table 38           |

| -3 dB Frequency                    |          | 670            | 800         | 880        | Hz             |                                      |

| –3 dB Frequency                    |          | 335            | 400         | 440        | Hz             |                                      |

| –3 dB Frequency                    |          | 167.5          | 200         | 220        | Hz             |                                      |

| –3 dB Frequency                    |          | 83.75          | 100         | 110        | Hz             |                                      |

| AUTO-ZERO                          |          |                |             |            |                |                                      |

| Update Rate                        |          |                |             |            |                |                                      |

| Slow Mode                          |          |                | 5.0         |            | sec/LSB        | 10-bit LSB                           |

| Fast Mode                          |          |                | 0.5         |            | sec/LSB        | 10-bit LSB                           |

| Parameter <sup>1</sup>                                 | Symbol                  | Min  | Тур        | Max  | Unit             | Test Conditions/Comments                                        |

|--------------------------------------------------------|-------------------------|------|------------|------|------------------|-----------------------------------------------------------------|

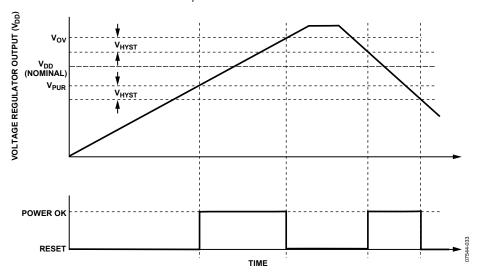

| REGULATOR VOLTAGE MONITOR                              |                         |      |            |      |                  |                                                                 |

| Regulator Operating Voltage                            | $V_{DD}$                |      | 4.20       |      | ٧                |                                                                 |

| Power-Up Reset Voltage                                 | $V_{PUR}$               | 3.77 | 4.0        | 4.23 | ٧                | See Figure 33                                                   |

| Overvoltage Level                                      | Vov                     | 4.7  | 4.95       | 5.3  | ٧                | See Figure 33                                                   |

| Reset Hysteresis Voltage                               | V <sub>HYST</sub>       |      | 0.12       |      | ٧                | _                                                               |

| COMMUNICATIONS INTERFACE                               |                         |      |            |      |                  |                                                                 |

| Quiescent (Idle) Current                               | I <sub>LDLE</sub>       | 5    | 6          | 7.7  | mA               |                                                                 |

| Modulation Current                                     | I <sub>MOD</sub>        | 23   | 25         | 30   | mA               |                                                                 |

| Signal Current                                         | Isig                    | 28   | 31         | 37.7 | mA               | I <sub>SIG</sub> = I <sub>IDLE</sub> + I <sub>MOD</sub>         |

| Autodelay Detect Current                               | I <sub>DET</sub>        | 18   | 22         | 26   | mA               | Total including IDLE                                            |

| Data Bit Period <sup>2</sup>                           | t <sub>B</sub>          |      | 8          |      | μs               | $t_B = 8 \times t_{CLK}$                                        |

| Data Bit Duty Cycle                                    | D <sub>DC</sub>         | 45   | 50         | 53   | %                | $D_{DC} = t_A/t_B$ , see Figure 7                               |

| Data Bit Rise/Fall                                     |                         |      |            |      |                  | See Figure 7                                                    |

| Fall Time                                              | t <sub>R</sub>          | 400  |            | 1000 | ns               | _                                                               |

| Rise Time                                              | t <sub>F</sub>          | 350  |            | 1000 | ns               |                                                                 |

| Encoding                                               |                         |      | Manchester |      |                  | See Figure 8                                                    |

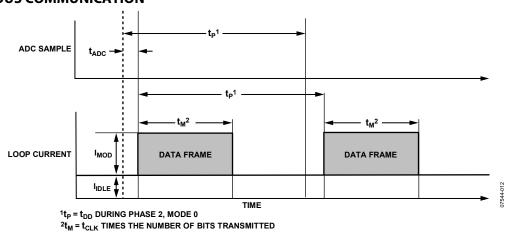

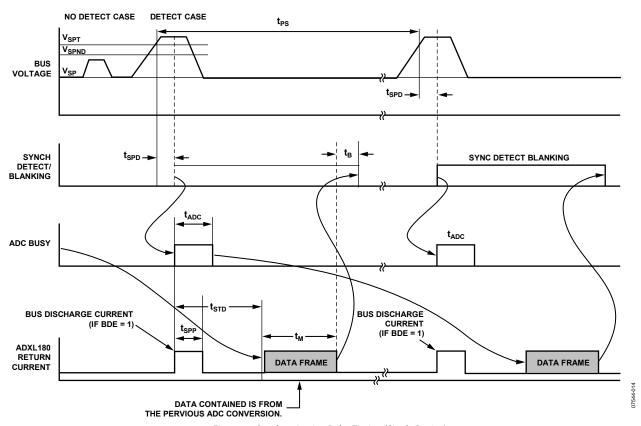

| ADC Conversion Time <sup>2</sup>                       | t <sub>ADC</sub>        |      | 35         |      | μs               | See Figure 12                                                   |

| Error Checking (Selectable)                            |                         |      |            |      |                  | _                                                               |

| Number of CRC Bits                                     |                         |      | 3          |      |                  | $x^3 + x^1 + x^0$                                               |

| Number of Parity Bits                                  |                         |      | 1          |      |                  | Even                                                            |

| Synchronization Pulse Detect                           |                         |      |            |      |                  |                                                                 |

| No Detect Limit                                        | V <sub>SPND</sub>       |      |            | 3.0  | ٧                |                                                                 |

| Detect Threshold                                       | V <sub>SPT</sub>        | 3.5  |            |      | ٧                | $V_{BP} - V_{BN} + V_{SPT} \le 14.5 \text{ V}$ ; see Figure 14  |

| Threshold Hysteresis                                   |                         |      | 0.1        |      | ٧                | _                                                               |

| Synchronization Pulse Detect<br>Time                   | <b>t</b> <sub>SPD</sub> |      | 8          |      | t <sub>CLK</sub> | See Figure 14                                                   |

| Synchronization Pulse<br>Discharge (Pull-Down)<br>Time | <b>t</b> <sub>SPP</sub> |      | 40         |      | <b>t</b> clk     | See Figure 14                                                   |

| Synchronization Mode<br>Transmission Delay             | t <sub>STD</sub>        |      | 63         |      | t <sub>CLK</sub> | See Figure 14                                                   |

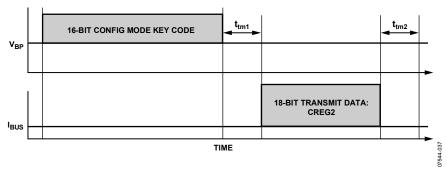

| Configuration Mode Receive<br>Communications Interface |                         |      |            |      |                  | All @ 25°C only; $V_{BP} - V_{BN} + V_{CT} \le 12.25 \text{ V}$ |

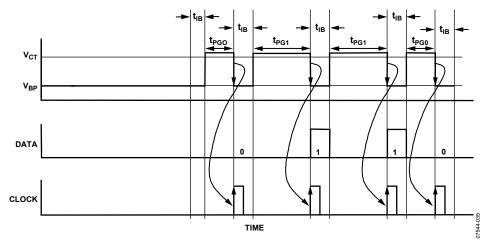

| Detect Threshold                                       | V <sub>CT</sub>         | 5.25 |            |      | V                | See Figure 35                                                   |

| Threshold Hysteresis                                   |                         |      | 0.1        |      | V                |                                                                 |

| Interbit Time                                          | t <sub>IB</sub>         | 250  |            |      | t <sub>CLK</sub> | See Figure 35                                                   |

| Data 0 Pulse Width                                     | t <sub>PG0</sub>        | 40   |            | 55   | t <sub>CLK</sub> | See Figure 35                                                   |

| Data 1 Pulse Width                                     | t <sub>PG1</sub>        | 80   |            |      | t <sub>CLK</sub> | See Figure 35                                                   |

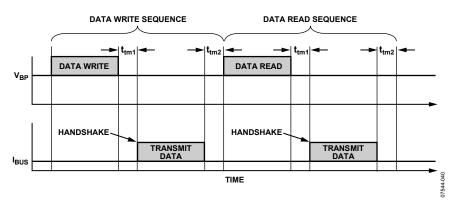

| Configuration Mode<br>Response Time                    | t <sub>TM1</sub>        |      | 24         |      | μs               | See Figure 35                                                   |

| Configuration Mode Write<br>Delay Time                 | t <sub>TM2</sub>        |      | 50         |      | μs               | See Figure 35                                                   |

| V <sub>BP</sub> During Fuse<br>Programming             | V <sub>BPF</sub>        | 7.5  |            |      | V                | Compliant up to the maximum operating voltage                   |

| V <sub>BP</sub> Current During Fuse<br>Programming     | I <sub>FP</sub>         |      |            | 15   | mA               | Maximum drawn by the part                                       |

| Parameter <sup>1</sup>                      | Symbol                  | Min  | Тур                      | Max  | Unit | Test Conditions/Comments                                                                                                    |

|---------------------------------------------|-------------------------|------|--------------------------|------|------|-----------------------------------------------------------------------------------------------------------------------------|

| ASYNCHRONOUS MODE TIMING <sup>2</sup>       |                         |      |                          |      |      |                                                                                                                             |

| Message Transmission Period                 |                         |      |                          |      |      |                                                                                                                             |

| Phase 2, Mode 0                             | t <sub>PM0</sub>        |      | 456                      |      | μs   | ADIFX compatible                                                                                                            |

| All Other Phases and Modes                  | t₽                      |      | 228                      |      | μs   |                                                                                                                             |

| Initialization State (Phase 1)              | tı                      |      | 100                      |      | ms   |                                                                                                                             |

| Device Data State (Phase 2)                 |                         |      |                          |      | ms   |                                                                                                                             |

| Mode 0                                      | t <sub>DD0</sub>        |      | 4.10                     |      | ms   |                                                                                                                             |

| Mode 1                                      | t <sub>DD1</sub>        |      | 109                      |      | ms   |                                                                                                                             |

| Mode 2                                      | t <sub>DD2</sub>        |      | 109                      |      | ms   |                                                                                                                             |

| Mode 3                                      | t <sub>DD3</sub>        |      | 117                      |      | ms   |                                                                                                                             |

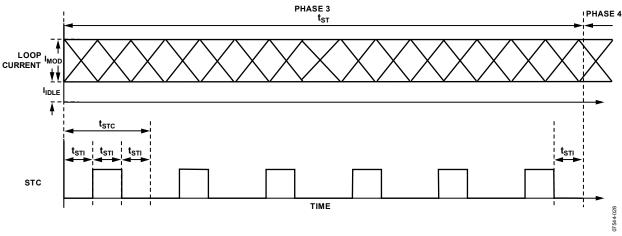

| Self-Test State (Phase 3)                   |                         |      |                          |      |      |                                                                                                                             |

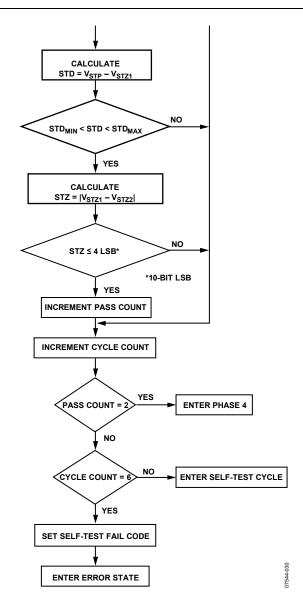

| Self-Test Time <sup>3</sup>                 | t <sub>ST</sub>         |      | 394                      |      | ms   | See Figure 28                                                                                                               |

| Self-Test Interval                          | t <sub>STI</sub>        |      | 21.9                     |      | ms   | See Figure 28                                                                                                               |

| Self-Test Cycle                             | <b>t</b> <sub>STC</sub> |      | 65.7                     |      | ms   | See Figure 28                                                                                                               |

| Auto-Zero Initialization State              | t <sub>AZ</sub>         |      | 14.94                    |      | sec  |                                                                                                                             |

| (Phase 4)                                   |                         |      |                          |      |      |                                                                                                                             |

| SYNCHRONOUS MODE TIMING <sup>4</sup>        |                         |      |                          |      |      |                                                                                                                             |

| Message Transmission Period                 | t <sub>PS</sub>         |      | N/A                      |      |      | Determined by sync pulse, See Figure 14,                                                                                    |

| Initialization State 1 (Dhasa 1)            | _                       |      | 100                      |      |      | $minimum t_{PS} = t_{SPD} + t_{STD} + t_{M} + t_{B}$                                                                        |

| Initialization State 1 (Phase 1)            | t <sub>i</sub>          |      | 100                      |      | ms   |                                                                                                                             |

| Device Data State (Phase 2)                 |                         |      | 0                        |      | ms   |                                                                                                                             |

| Mode 0                                      | t <sub>DD0s</sub>       |      | $9 \times t_{PS}$        |      | ms   |                                                                                                                             |

| Mode 1                                      | t <sub>DD1s</sub>       |      | 480 × t <sub>PS</sub>    |      | ms   |                                                                                                                             |

| Mode 2                                      | t <sub>DD2s</sub>       |      | $480 \times t_{PS}$      |      | ms   |                                                                                                                             |

| Mode 3                                      | t <sub>DD3s</sub>       |      | $512 \times t_{PS}$      |      | ms   |                                                                                                                             |

| Self-Test State (Phase 3)                   |                         |      |                          |      |      |                                                                                                                             |

| Self-Test Time <sup>3</sup>                 | <b>t</b> sts            |      | 1728 × t <sub>PS</sub>   |      | ms   |                                                                                                                             |

| Self-Test Interval                          | t <sub>STIS</sub>       |      | $96 \times t_{PS}$       |      | ms   |                                                                                                                             |

| Self-Test Cycle                             | t <sub>STCS</sub>       |      | 288 × t <sub>PS</sub>    |      | ms   |                                                                                                                             |

| Auto-Zero Initialization State<br>(Phase 4) | t <sub>AZs</sub>        |      | 65,535 × t <sub>PS</sub> |      | sec  |                                                                                                                             |

| CLOCK                                       |                         |      |                          |      |      |                                                                                                                             |

| Period <sup>2</sup>                         | <b>t</b> <sub>CLK</sub> | 1.05 | 1.0                      | 0.95 | μs   | $f_{CLK} = 1/t_{CLK}$                                                                                                       |

| PSRR                                        |                         |      | <1                       |      | LSB  | 8-bit LSB; test conditions: $V_{BP} - V_{BN} = 7.00 \text{ V}$ , $V_{AC} = 500 \text{ mV} \text{ p-p}$ , 100 kHz to 1.1 MHz |

| POWER SUPPLY HOLDUP TIME                    |                         |      | 500                      |      | ns   | $@I_{BUS} = I_{SIG}$                                                                                                        |

| THERMAL RESISTANCE, JUNCTION TO CASE        | $\theta_{JC}$           |      | 30                       |      | °C/W |                                                                                                                             |

<sup>&</sup>lt;sup>1</sup> All parameters are specified using the application circuit shown in Figure 6. C<sub>B</sub> = 10 nF, C<sub>VDD</sub> = 100 nF.

<sup>2</sup> All timing is driven from the on-chip master clock.

<sup>3</sup> t<sub>ST</sub> and t<sub>STS</sub> are the times for six self-test cycles. This is the maximum number of cycles in the internal self-test mode.

<sup>4</sup> Transmission timing is defined by the internal system clock in asynchronous mode and by the synchronization pulse period in synchronous mode.

## **ABSOLUTE MAXIMUM RATINGS**

Table 2.

| Parameter                                                   | Rating                                           |

|-------------------------------------------------------------|--------------------------------------------------|

| Supply Voltage (V <sub>BP</sub> – V <sub>BN</sub> )         | -0.3 V to +21 V                                  |

| Voltage at Any Pin with Respect to $V_{BN}$ Except $V_{BP}$ | $-0.3 \text{ V to V}_{DD} + 0.3 \text{ V}$       |

| Storage Temperature Range                                   | −55°C to +150°C                                  |

| Soldering Temperature                                       | 255°C                                            |

| Operating Temperature Range                                 | −40°C to +125°C                                  |

| ESD All Pins                                                | 1.5 kV HBM                                       |

| Latch-Up Current                                            | 100 mA                                           |

| Mechanical Shock                                            |                                                  |

| Unpowered                                                   | ±4000 g (0.5 ms, half sine)                      |

| Powered                                                     | ±2000 g (0.5 ms, half sine);<br>-0.3 V to +7.0 V |

| Drop Test (onto Concrete)1                                  | 1.2 m                                            |

| Thermal Gradient                                            | ±20°C/minute                                     |

$<sup>^1</sup>$  Soldered to FR4 coupon printed circuit board (PCB) at the dimensions of 25.4 mm  $\times$  25 mm. During test, the PCB is fastened to a support with 46 g mass, equivalent to a typical satellite module PCB.

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

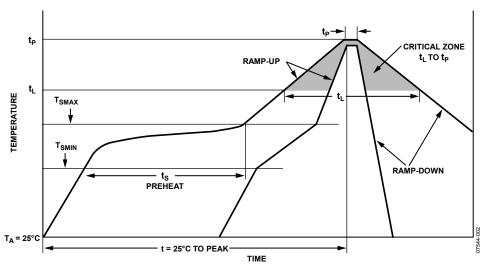

Figure 2. ADXL180 Pb-Free Solder Profile

**Table 3. ADXL Solder Profile Parameters**

| Profile Feature                                                                      | Small Body Pb-Free Assemblies |

|--------------------------------------------------------------------------------------|-------------------------------|

| Average Ramp-Up Rate (T <sub>L</sub> to T <sub>P</sub> )                             | 3°C/second maximum            |

| Preheat Temperature Min (T <sub>S</sub> min) to Temperature Max (T <sub>S</sub> max) | 150°C to 200°C                |

| Time (min to max) (ts)                                                               | 60 sec to 180 sec             |

| $T_S$ max to $T_L$ Ramp-Up Rate                                                      | 3°C/second maximum            |

| Time Maintained Above Temperature (T <sub>L</sub> )                                  | 217°C                         |

| Time (t <sub>L</sub> )                                                               | 60 sec to 150 sec             |

| Peak Temperature (T <sub>P</sub> )                                                   | 260°C +5/-5°C                 |

| Time Within 5°C of Actual Peak Temperature (t <sub>P</sub> )                         | 20 sec to 40 sec              |

| Ramp-Down Rate                                                                       | 6°C/sec maximum               |

| Time 25°C to Peak Temperature                                                        | 8 minutes maximum             |

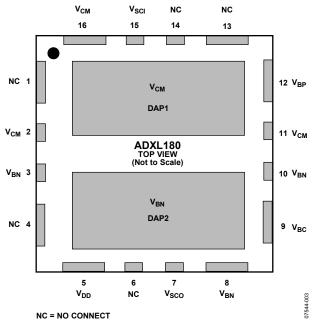

## PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 3. Pin Configuration

**Table 4. Pin Function Descriptions**

| Pin No. | Mnemonic         | Description                                                                                               |

|---------|------------------|-----------------------------------------------------------------------------------------------------------|

| 1       | NC               | Reserved for Analog Devices, Inc., Use Only. V <sub>BN</sub> or do not connect.                           |

| 2       | $V_{CM}$         | Reserved for Analog Devices Use Only. Do not connect.                                                     |

| 3       | $V_{BN}$         | Negative Bus Voltage.                                                                                     |

| 4       | NC               | Reserved for Analog Devices Use Only. V <sub>BN</sub> or do not connect.                                  |

| 5       | $V_{DD}$         | Voltage Regulator Bypass Capacitor.                                                                       |

| 6       | NC               | Reserved for Analog Devices Use Only. V <sub>BN</sub> or do not connect.                                  |

| 7       | V <sub>sco</sub> | Reserved for Analog Devices Use Only. Do not connect.                                                     |

| 8       | $V_{BN}$         | Negative Bus Voltage.                                                                                     |

| 9       | $V_{BC}$         | Daisy-Chain Connection. Daisy-chain connection to V <sub>BP</sub> of the second device or do not connect. |

| 10      | $V_{BN}$         | Negative Bus Voltage.                                                                                     |

| 11      | $V_{CM}$         | Reserved for Analog Devices Use Only. Do not connect.                                                     |

| 12      | $V_{BP}$         | Positive Bus Voltage.                                                                                     |

| 13      | NC               | Reserved for Analog Devices Use Only. V <sub>BN</sub> or do not connect.                                  |

| 14      | NC               | Reserved for Analog Devices Use Only. V <sub>BN</sub> or no connect                                       |

| 15      | $V_{SCI}$        | Analog Signal Chain Input. V <sub>BN</sub> when not in use.                                               |

| 16      | $V_{CM}$         | Reserved for Analog Devices Use Only. Do not connect.                                                     |

| DAP1    | $V_{CM}$         | Exposed Pad: Reserved for Analog Devices Use Only. Do not connect.                                        |

| DAP2    | $V_{BN}$         | Exposed Pad: Negative Bus Voltage.                                                                        |

#### **TERMINOLOGY**

#### Full-Scale Range (FSR)

The full-scale range of a device, also referred to as the dynamic range, is the maximum and minimum *g* level that reports on the output following the internal filtering. As a reference, there is usually a trade-off in increased sensitivity and resolution for decreased full-scale range, and vice versa.

#### Noise

Device noise is the noise content between 10 Hz and 400 Hz, as noted in the Specifications Table 1. Device noise can be measured by performing an FFT on the digital output and measuring the noise content between the specified frequency limits.

#### Sensitivity

The sensitivity of a device is the amount of output change per input change. In this device, it is most usually referred to in units of LSB/g.

#### **Scale Factor**

The scale factor is the amount of input change per output change. In this device, it is most usually referred to in units of *g*/LSB.

#### Offset

Offset is the low frequency component of the output signal that is not due to changes in input acceleration. Slow moving effects, such as temperature changes and self-heating during start up, may affect offset, but the time scale for these effects is beyond that of a typical shock or crash event.

#### Auto-Zero

Auto-zero is an offset compensation technique intended to reduce the long term offset drift effects of temperature and aging. This technique is designed to limit interaction with true acceleration signals. For more information, see Figure 32.

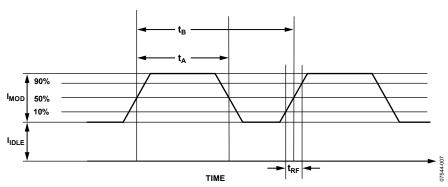

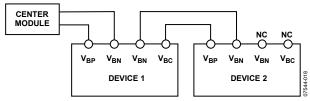

#### Rise/Fall Times

The device rise time is defined as the amount of time necessary for the Manchester encoded signal ( $I_{\text{MOD}}$ ) to transition from 10% to 90% of its final value ( $I_{\text{SIG}}$ ). Device fall time is the amount of time required for the  $I_{\text{MOD}}$  signal to fall from 90% of  $I_{\text{SIG}}$  to within 10% of  $I_{\text{IDLE}}$ .

#### **Idle Current**

Idle current is the current of the device when at rest, waiting for a synchronization pulse, or in between current modulation.

#### **Modulation Current**

Modulation current is the amount of current that the ADXL180 device pulls from the bus when communicating. For more information, see Figure 7.

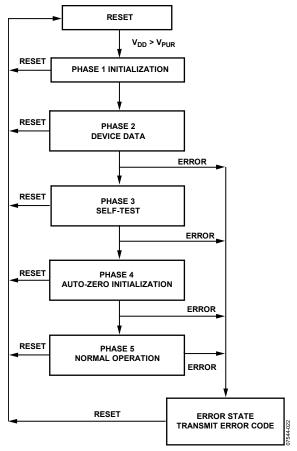

#### Phase

A phase is a stage in the ADXL180 state machine. For more information, see Figure 22.

#### Mode

Mode refers to the selection of the Phase 2 method of device data communication. The ADXL180 is configurable into four unique operating modes.

#### CRC

A cyclic redundancy check (CRC) is calculated from a set of data and then transmitted alongside that data. If the calculation technique is defined and known to the receiving device, the receiver can then check whether the CRC bits match the data. If they do not match, a transmission error has occurred.

#### Parity

Parity is defined by the count of 1s in a binary string of data. If this count is even, then the data is determined to have even parity. Often a bit is used, such as the CUPAR, in a configuration register that is defined in such a way as to establish a particular parity in the register to detect single bit changes during the life of the device. This is possible because a single bit change changes parity and a monitor circuit can detect this. Similarly, a parity bit can be added in a data transmission to detect single bit errors if the parity of communication is preestablished for the transmit and receive systems.

## THEORY OF OPERATION OVERVIEW

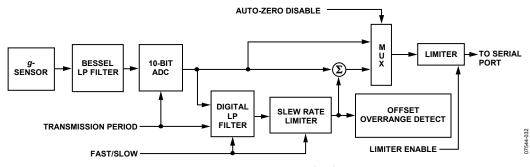

The ADXL180 is a complete satellite system, including acceleration sensor, data filtering, digital protocol functionality, and a 2-wire, high-voltage, current-modulated bus interface communications port.

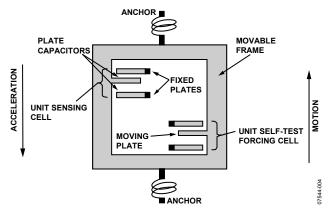

#### **ACCELERATION SENSOR**

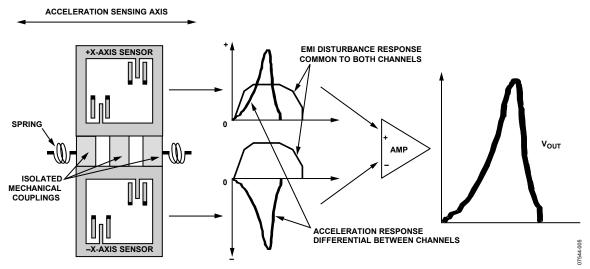

The ADXL180 provides a fully differential sensor structure and circuit path. This device uses electrical feedback with zero force feedback. Figure 4 is a simplified view of one of the differential sensor elements. Each sensor includes several differential capacitor unit cells. Each cell is composed of fixed plates attached to the substrate and movable plates attached to the frame. Displacement of the frame changes the differential capacitance, which the onchip circuitry measures.

Complementary signals drive the fixed capacitor plates. The relative phasing between the two halves of the differential

sensor is such that the displacement signal is differential between the two measurement channels. Using the fully differential sensor and an antiphase clocking scheme helps reject electrical environmental noise (see Figure 5).

The ADXL180 acceleration sensor uses two electrically isolated, mechanically coupled sensors to measure acceleration as shown in Figure 5. The clock phasing of the readout is such that the electrical signal due to acceleration is differential between the channels and environmental disturbances couple in as a common-mode signal. The following differential amplifier can then extract the acceleration signal while suppressing the environmental noise.

Electrical feedback adjusts the amplitudes of the fixed capacitor plates' drive signals such that the ac signal on the moving plates is zero. The feedback signal is linearly proportional to the applied acceleration. This feedback technique ensures that there is no net electrostatic force applied to the sensor.

Figure 4. Simplified View of ADXL180 Sensor Under Acceleration

Figure 5. Differential Acceleration Sensing

#### SIGNAL PROCESSING

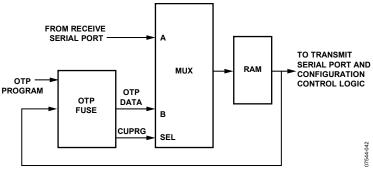

The ADXL180 contains an on-board set of signal processing blocks both prior to and after ADC conversion. The first stage is a fully differential, switched capacitor, low-pass, three-pole Bessel filter. Range scaling is also handled in one of the filter blocks, enabling 50 g to 500 g range capability. At this point, an analog output test signal (V<sub>SCO</sub>) is available to the user in a diagnostic mode. The signal then converts by a 10-bit rail-to-rail SAR ADC. In the digital section, an auto-zero routine is available to the user as part of the state machine in addition to error detection features such as offset drift detection.

#### **DIGITAL COMMUNICATIONS STATE MACHINE**

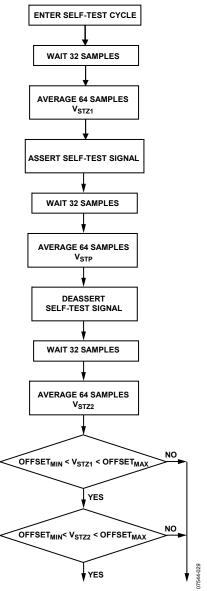

The ADXL180 digital state machine is based on a Core 5 phase state machine implemented in high density CMOS. This state machine handles the sequential states of

- Phase 1. Initialization.

- Phase 2. Device data transmission, including individual serial number and user-programmed data.

- Phase 3. Self-diagnostic, including automatic full electromechanical self-test with internal error detection available.

- Phase 4. Auto-zero initialization, if selected. During this phase, acceleration data is already available.

- Phase 5. Normal acceleration data transmission.

#### 2-WIRE CURRENT MODULATED INTERFACE

The data that is generated during these five phases is transmitted using a 2-wire high voltage communication port. This allows the device to be powered by a fixed supply voltage, and communicate back to the system or ECU electronics by modulating current. Current modulated messages are encoded using Manchester encoding.

Table 5. Factory Programmed and User-Programmed Memory

## SYNCHRONOUS OPERATION AND DUAL DEVICE BUS

In a point-to-point bus topology, the ADXL180 supports asynchronous transmission of data to the receive device every 228  $\mu s$ , controlled by the on-board state machine. A synchronous option is also available, allowing two devices to be on the same bus using time division multiplexing where each device transmits its data during a known time slot.

Synchronization is achieved by voltage modulated synchronization pulses, configuring the ADXL180 device into a synchronous mode, and establishing data frame time slots. The high voltage communication port registers valid synchronization pulses and enables message-by-message advancement of the state machine rather than asynchronous timed regular data transmission.

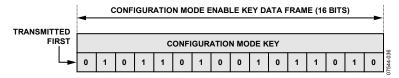

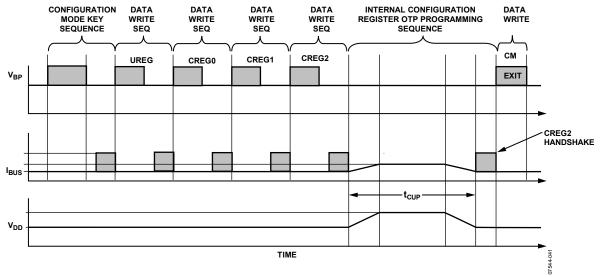

## PROGRAMMED MEMORY AND CONFIGURABILITY Factory-Programmed Serial Number and Manufacturer Information

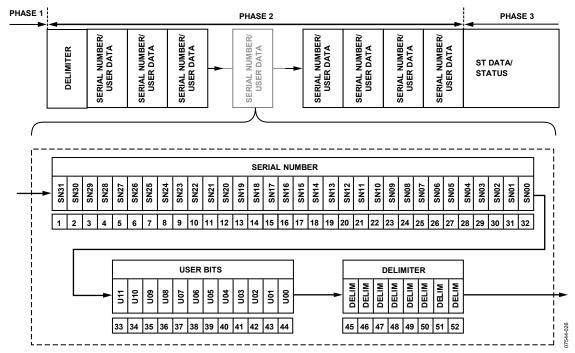

The ADXL180 includes a 32-bit factory-programmed serial number, as shown in Table 5. This serial number transmits during Phase 2 of startup for all devices to enable robust quality tracking of individual devices, and it is field readable. In addition, this data includes revision information and manufacturer identification in case multiple devices used within a single application are from different manufacturers or generations of parts.

#### **User-Programmable Data Register**

The ADXL180 gives the user an 8-bit register of user-programmable data, which is transmitted during Phase 2 of the state machine. In addition, the UD8 bit, a ninth user-available bit, is transmitted separately during Phase 2 and can be used for various purposes, such as orientation definition or module type.

|                      | Configuration Mode | Configuration Mode | MSB   |       |       |       |       |        |        | LSB    |

|----------------------|--------------------|--------------------|-------|-------|-------|-------|-------|--------|--------|--------|

| <b>Programmed By</b> | Register Address   | Register Name      | D7    | D6    | D5    | D4    | D3    | D2     | D1     | D0     |

| User                 | 0000b              | UREG               | UD7   | UD6   | UD5   | UD4   | UD3   | UD2    | UD1    | UD0    |

|                      | 0001b              | CREG0              | UD8   | BDE   | MD1   | MD0   | FDLY  | DLY2   | DLY1   | DLY0   |

|                      | 0010b              | CREG1              | STI   | AZE   | SYEN  | ADME  | ERC   | SVD    | DAT    | MAN    |

|                      | 0011b              | CREG2              | CUPRG | CUPAR | SCOE  | FC1   | FC0   | RG2    | RG1    | RG0    |

| Factory              | 1011b              | SN0                | SNB7  | SNB6  | SNB5  | SNB4  | SNB3  | SNB2   | SNB1   | SNB0   |

|                      | 1100b              | SN1                | SNB15 | SNB14 | SNB13 | SNB12 | SNB11 | SNB10  | SNB9   | SNB8   |

|                      | 1101b              | SN2                | SNB23 | SNB22 | SNB21 | SNB20 | SNB19 | SNB18  | SNB17  | SNB16  |

|                      | 1110b              | SN3                | SNB31 | SNB30 | SNB29 | SNB28 | SNB27 | SNB26  | SNB25  | SNB24  |

|                      | 1111b              | MFGID              | SNPRG | SNPAR | REV2  | REV1  | REV0  | MFGID2 | MFGID1 | MFGID0 |

#### **User-Programmed Configuration**

At each of these previously described points in the system, the ADXL180 is highly configurable for different applications. The organization and configurable items are briefly described in this section but are covered in depth in the remainder of this data sheet.

#### Physical Layer (ISO Layer 1)

The bus interface hardware definition including the phase of Manchester encoding and synchronization pulse enable/disable.

#### Data Link Layer (ISO Layer 2)

The specifics of the data frame format including the data width (8-bit or 10-bit data), state vector (enable/disable), and error detection (parity or CRC).

#### Application Layer (ISO Layer 7)

The serial number and configuration data transmission mode and self-test (internal self-test pass/fail discrimination or external self-test data evaluation).

Other signal processing related aspects of the function of the ADXL180 can also be configured as follows:

- Sensor scale factor (range)

- Signal chain low-pass filter bandwidth

- Auto-zero: enable/disable

- User-defined data in the user data register

## PHYSICAL INTERFACE

#### **APPLICATION CIRCUIT**

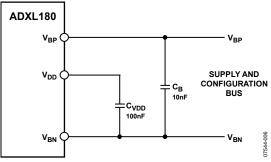

A typical application circuit is shown in Figure 6. The two capacitors shown in Figure 6 are typically ceramic, X7R, multilayer SMT capacitors. Maximum recommended values of ESR and ESL are 250 m $\Omega$  and 2 nH, respectively. Capacitor tolerances of  $\pm 10\%$  are recommended.

#### **CURRENT MODULATION**

When the ADXL180 device is powered on, it uses current modulation to transmit data. Normally, the device pulls  $I_{\rm IDLE}$  current. When modulating, an additional current of  $I_{\rm MOD}$  is pulled from the sensor bus. See Figure 7.

Figure 6. Application Circuit

Figure 7. Communication Current Modulation Timing

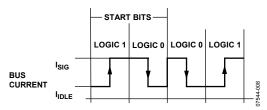

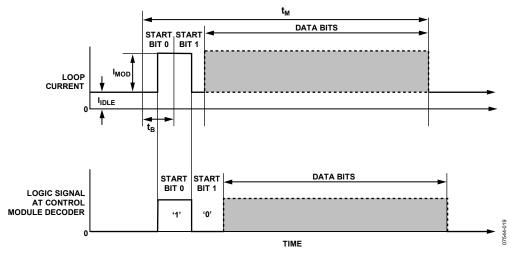

#### MANCHESTER DATA ENCODING

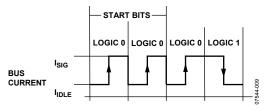

To encode data within the current modulation, the ADXL180 uses Manchester encoding. Manchester encoding works on the principle of transitions representing binary 1s and 0s, as shown in Figure 8. Manchester encoding uses a set of predefined start bits to transmit the clocking within each message, see Figure 9. The pattern of the start bits allows the receiver to synchronize itself to the bit stream. These start bits are user selectable.

Figure 8. Manchester-1, Start Bits and Phase

Figure 9. Manchester-2, Bit Coding

**Table 6. MAN Options**

| MAN | Manchester<br>Coding      | Start<br>Bits | Logic 0      | Logic 1      |

|-----|---------------------------|---------------|--------------|--------------|

| 0   | Manchester-1<br>(Default) | 1, 0          | Falling edge | Rising edge  |

| 1   | Manchester-2              | 0, 0          | Rising edge  | Falling edge |

The phase of the Manchester encoded data can be selected via a bit in the configuration registers. See Figure 8 and Figure 9 for details. The configuration bit that sets the phase of the Manchester encoder also sets the value of the two start bits. The start bits are 1, 0 for Manchester-1 and 0, 0 for Manchester-2. For phase and start bit information, see Table 6.

### OPERATION AT LOW $V_{BP}$ OR LOW $V_{DD}$

The ADXL180 monitors its internal regulator voltage to ensure proper operation. If the bus voltage drops, or the internal regulator voltage drops below the  $V_{\text{PUR}}$  reset threshold, the device resets. See the Voltage Regulator Monitor Reset Operation section.

#### **OPERATION AT HIGH VDD**

If the regulator pin detects a high voltage, such as from a short or leakage condition, the ADXL180 detects an error. See the Voltage Regulator Monitor Reset Operation section for more details.

## COMMUNICATIONS TIMING AND BUS TOPOLOGIES

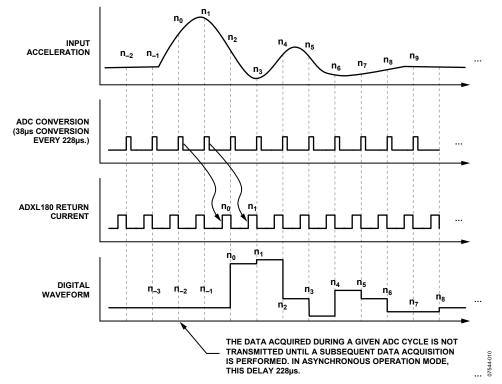

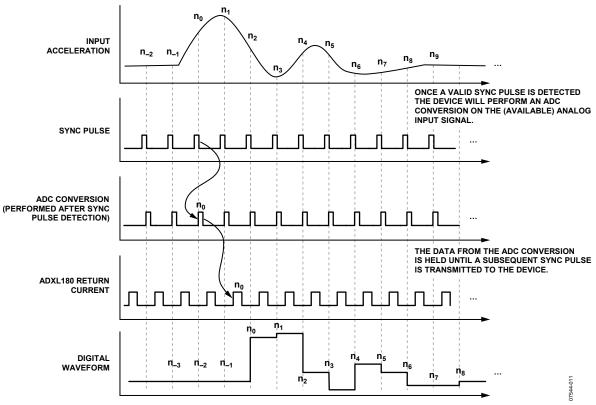

#### **DATA TRANSMISSION**

The analog data (available to the user by enabling the  $V_{\text{SCO}}$  output) is sampled every 228  $\mu s$  when the device is configured to run asynchronously. In synchronous operation, an ADC conversion is triggered upon the detection of a valid sync pulse. In both cases, the data is held until a subsequent ADC conversion is performed. This results in an additional time delay of either 228  $\mu s$  or one sync pulse period from the

sampling of the analog data to when it is transmitted via manchester encoded data. Analog-to-digital conversions are performed prior to the device entering run-time mode (Phase 5) thereby ensuring that the data from the ADC is never in an unknown state. This holds true upon receipt of the first sync pulse in run-time mode (Phase 5).

Figure 10. Asynchronous Data Transmission (Timing Not To Scale)

Figure 11. Synchronous Data Transmission (Timing Not To Scale)

#### **ASYNCHRONOUS COMMUNICATION**

Figure 12. Asynchronous Mode Data Transmission Timing

The ADXL180 data transmissions in their default mode run asynchronous to the control module. In this mode, the ADXL180 timing is entirely based on the internal clock of the device. After the initialization phases are complete, the ADXL180 begins to transmit sensor data every 228 µs. The device transmits sensor data until the supply voltage falls below the required minimum operating level. If an internal error is detected, the device transmits the appropriate error code until the supply voltage falls below the required minimum operating level.

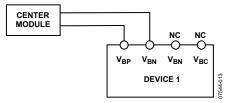

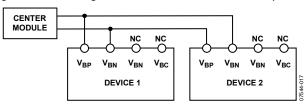

#### Asynchronous Single Device Point-to-Point Topology

A single device is wired in the point-to-point configuration as shown in Figure 13. This configuration must be used in asynchronous mode. Do not use two asynchronous devices on one bus because communications errors are very likely to occur.

Figure 13. Asynchronous Point-To-Point Topology

#### SYNCHRONOUS COMMUNICATION

The ADXL180 data transmission can be synchronized to the control module. This synchronization is accomplished by the control module generating a synchronization pulse to the ADXL180. The synchronization pulse is a voltage pulse that is superimposed on the supply voltage by the center module. Figure 14 shows the synchronization pulse timing. Upon detecting a synchronization pulse, the ADXL180 transmits its data.

#### **Configuring the ADXL180 for Synchronous Operation**

Table 7. Sync Enable (SYEN) Options

| SYEN | Definition                                                                                                                                                                                                       |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0    | Synchronization pulse disabled. The device transmits data every 228 µs based on the internal clock of the device. Data is transmitted according to an internal state machine sequence when powered on (default). |

| 1    | Synchronization pulse enabled. The device requires a synchronization pulse to sample and transmit data. Data transmission is in accordance with the internal state machine of the device.                        |

The user-defined SYEN bit determines whether the device is used in synchronous operation or remains asynchronous. SYEN, as shown in Table 7, must be set to SYEN = 1 to enable synchronous operation.

#### **Synchronization Pulse Detection**

The ADXL180 uses a digital integration method to validate the synchronization pulse. The ADXL180 detects the supply voltage ( $V_{BP}$ ) rising above the level of  $V_{SPT}$ . The state of the level detection circuit controls the count direction of an up-down counter. The counter is clocked every 1  $\mu$ s. The counter is incremented if the ADXL180 detects a level exceeding  $V_{SPT}$ . The counter is decremented if the ADXL180 detects a level below  $V_{SPND}$ . Operation is not defined between these thresholds. If the synchronization

pulse is fully below  $V_{SPND}$ , the pulse is rejected and not detected. The counter saturates at zero. The synchronization pulse is considered valid on the next clock after the counter is incremented to seven counts. The counter is gated off (blanked) after a valid synchronization pulse is detected. Once the sync pulse has been recognized as valid, a command is issued to start the acceleration data analog-to-digital conversion. The ADC does not run continuously in synchronous mode.

The synchronization pulse detector is reenabled after t<sub>B</sub>, which is an idle bit transmission following the last data frame bit (see the Data Frame Definition section). At this point, the device is ready to receive the next sync pulse.

If the application requires or uses a pulse of nonuniform shape, such as, for example, rising above  $V_{SPT}$  and subsequently toggling such that it falls below  $V_{SPT}$  one or more times before  $t_{SPD}$ , consult Analog Devices, Inc., applications support for further information on application specific pulse recognition.

Note, this counter means that when an invalid length sync pulse of less than seven counts is followed less than seven counts later by a subsequent sync pulse, detection may occur when the counter is incremented further by less than seven counts by the second pulse.

#### **Bus Discharge Enable**

Table 8. Bus Discharge Enable

| BD | ÞΕ | Definition                                        |

|----|----|---------------------------------------------------|

| 0  |    | Bus discharge disabled (default).                 |

| 1  |    | Bus discharge enabled. Only active when SYEN = 1. |

The bus discharge enable (BDE) bit in the configuration registers can be set to aid in the discharge of the bus voltage after a synchronization pulse is detected. If the BDE bit is set, the ADXL180 changes the bus current ( $I_{BUS}$ ) level from  $I_{IDLE}$  to  $I_{SIG}$  once a valid synchronization pulse is detected. The control module then sets the voltage on the bus to the nominal operating level. The bus capacitance is discharged by the ADXL180 device. The current level of  $I_{SIG}$  acts as an active pull-down current to return the  $V_{BP}$  voltage to the nominal supply voltage. The pull-down current pulse can also be used as a handshake with the control module acting as an acknowledgement of the synchronization pulse.

Figure 14. Synchronization Pulse Timing (Single Device)

#### Synchronous Single Device Point-to-Point Topology

A single device is wired in the point-to-point configuration as shown in Figure 15. The standard use of this configuration is with no delay devices. It is possible to use this topology with fixed delay devices as well, such as if line noise reduction after a sync pulse transmission is desired.

Figure 15. Single Device—Synchronous Communication

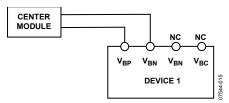

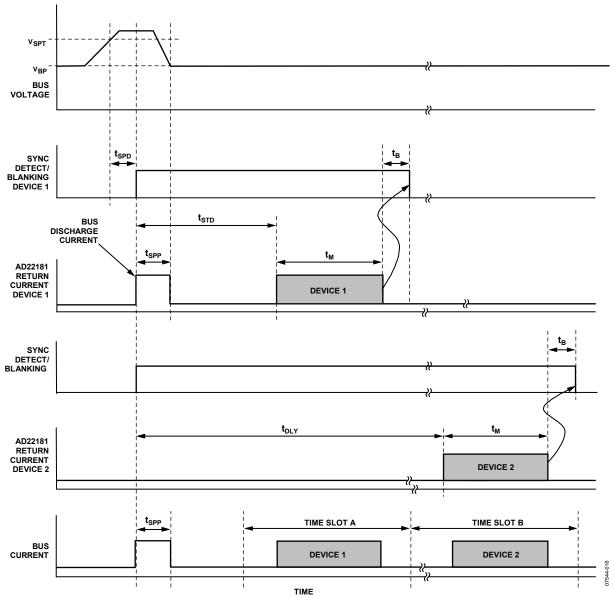

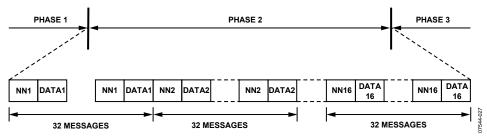

## SYNCHRONOUS COMMUNICATION MODE—DUAL DEVICE

The ADXL180 can be used in a dual device synchronous communication mode. This mode allows a maximum of two

ADXL180 devices to share a single pair of wires from the control module for power and communications. This is accomplished using time division multiplexing where each device transmits its data during a known time slot. The time slot used by each device is determined by the delay time from detection of a synchronization pulse to the beginning of data transmission. The data transmission delay time is selectable in the configuration registers. The following discussion uses the convention that the first time slot is named Time Slot A and the second time slot is named Time Slot B (see Figure 16). The two ADXL180 devices can be wired in either a parallel or series mode as described in the following sections. If a synchronization pulse is not detected, no data is sent. This is true for all initialization phases and normal run-time operation. Note that the minimum synchronization pulse period is

$$t_{SPD} + t_{DLY} + t_M + t_B$$

Figure 16. Synchronization Pulse Timing (Dual Device)

#### **Configuring Synchronous Operation**

#### **Delay Selection**

As shown in Table 9, the user can select the data timing of the second device to establish the predefined data slots. This allows for the fastest possible sampling, if required, and Table 9 shows the number of data frame bits the first device may transmit to ensure no overlap. To further reduce device interference from line or system circuit effects, use higher FDLY amounts than the minimum.

Table 9. Data Transmission Delay Codes

| DLY2 | DLY1 | DLY0 | Delay Time<br>(t <sub>DLY</sub> ) | Maximum First Data<br>Frame Bits |

|------|------|------|-----------------------------------|----------------------------------|

| 0    | 0    | 0    | 205 μs                            | 11                               |

| 0    | 0    | 1    | 213 μs                            | 12                               |

| 0    | 1    | 0    | 221 μs                            | 13                               |

| 0    | 1    | 1    | 229 μs                            | 14                               |

| 1    | 0    | 0    | 237 μs                            | 15                               |

| 1    | 0    | 1    | 245 μs                            | 16                               |

| 1    | 1    | 0    | 253 μs                            | 17                               |

| 1    | 1    | 1    | 261 μs                            | 18                               |

#### **Fixed Delay Mode**

Fixed delay mode establishes which device transmits in the second time slot. FDLY requires that either (but not both) of the two devices on the bus have the FDLY bit programmed to enable the data frame transmission delay time. The device with the FDLY bit set is named Device 2. Device 2 delays its data transmission by the amount of time programmed into the configuration register via Bit DLY2, Bit DLY1, and Bit DLY0. After receiving a valid synchronization pulse, only Device 1, without the FDLY bit set, sinks  $I_{SIG}$  as an active bus pull-down current (if the BDE bit is set) to return the  $V_{BP}$  voltage to the nominal supply voltage.

Table 10. Fixed Delay Mode

| FDLY | Definition                                                        |

|------|-------------------------------------------------------------------|

| 0    | Fixed delay mode disabled (default).                              |

| 1    | Fixed delay mode enabled. Device transmits data in the            |

|      | time slot delayed by t <sub>DLY</sub> as defined by DLY2 to DLY0. |

Caution: do not set Device 2 using Time Slot B as BDE = 1. Only Device 1 should draw  $I_{SIG}$  as an active pull-down when the BDE bit is set. It is good practice to never have BDE = 1 and FDLY = 1 in the same device.

#### **Autodelay Mode**

Table 11. Autodelay Mode Enable (ADME) Options

| ADME | Definition                                                                                                                                        |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| 0    | Autodelay mode is disabled. The part does not check for a second device on the line and does not pull any extra current during startup (default). |

| 1    | Autodelay mode detection is enabled. Pull down IDET for 6 ms at power up.                                                                         |

The autodelay mode allows two identically configured devices to be wired in a series configuration. The two devices automatically configure the two node network upon power up. The configuration bit (ADME) must be set to enable the autodelay mode. A device with the ADME bit set sinks a bus current of  $I_{DET}$  for 6 ms upon power up.

The first device in the series configuration (Device 2) detects the presence of the other device in the series (Device 1) by sensing the  $I_{DET}$  current passing though itself from Pin  $V_{BP}$  to Pin  $V_{BC}$  during the first 6 ms of the power-up initialization Phase 1. If the current draw of Device 1 is present, Device 2 delays its data transmission by the amount of time programmed into the configuration register via Bit DLY2, Bit DLY1, and Bit DLY0. Therefore, Device 2 transmits its data during Time Slot B. The data transmission delay time of Device 2 is usually selected based on the number of bits in the data frame. After receiving a valid synchronization pulse, only Device 1 sinks  $I_{SIG}$  as an active pull-down current (if the BDE bit is set) to return the  $V_{BP}$  voltage to the nominal supply voltage. Device 2 (using Time Slot B) never sinks  $I_{SIG}$  as an active pull-down even if the BDE bit is set.

In a single device network, the unit that would be called Device 1 is not present. Therefore, the single device detects no current draw through the  $V_{\text{BC}}$  pin during the power-on initialization. In this case, the single device transmits data during Time Slot A. This allows a device programmed with a nonminimum delay time to be used as either Device 1 or Device 2 in a series configuration or as a single device.

The autodelay mode detect function samples the state of the autodelay detect sense circuit every 500  $\mu$ s during the first 6 ms of Phase 1. A total of four consecutive samples must be valid to place the device in the autodelay mode.

Caution: do not send an additional valid sync pulse during the blanking period,  $t_{STD}$  or  $t_B$ , for either device, because it incurs the risk of the signal being misinterpreted and a change in message response timing.

#### **Dual Device Synchronous Parallel Topology**

The two devices are wired in a parallel configuration as shown in Figure 17. This configuration must be run in the fixed delay mode.

Figure 17. Dual Device—Parallel Configuration

#### **Dual Device Synchronous Series Topology**

The two devices are wired in a series configuration as shown in Figure 18. The series configuration can be configured to run in either of two modes: fixed delay or autodelay. These modes are configured using the FDLY and ADME bits in the configuration registers.

Figure 18. Dual Device—Series Configuration

## DATA FRAME DEFINITION

#### **DATA FRAME TRANSMISSION FORMAT**

Figure 19. Data Message Timing (Manchester-1, Bit Coding)

A data frame starts with two start bits. The value of these two bits is determined by the Manchester encoding mode select bit. See the Manchester Data Encoding section. Figure 19 shows the basic format and timing of the data frame. A 1-bit idle time is an implicit stop bit at the end of a data frame.

#### **DATA FRAME CONFIGURATION OPTIONS**

Figure 20 diagrams the protocol data frame construction options. The data frame can be broken into four specific fields as follows:

Start bits—two start bits are always transmitted at the start

of the data frame. These bits are used to synchronize the

center module decoder with the Manchester encoded signal.

- Error checking—a single parity bit or a 3-bit CRC code can be selected.

- State vector—identifies the type of data in the data field. It can be disabled. When it is disabled, it is not transmitted.

- Data—the device data and sensor data can be transmitted in either 8-bit or 10-bit mode.

Depending on the settings of the configuration register bits (ERC, SVD, and DAT), the data frame can be from 11 bits to 18 bits in length. Figure 20 shows the formats of the available data frames. Note that the error checking field is transmitted first when the CRC is selected but transmitted last when parity is selected. See Figure 20 for specific examples of full protocol configurations.

| CRI | EG BIT NA | ME  | ] _      | —ТЕ        | RANS | мітт | ED FI | RST  |       |     |       |       |     |       |       |     |   |   |   |           |

|-----|-----------|-----|----------|------------|------|------|-------|------|-------|-----|-------|-------|-----|-------|-------|-----|---|---|---|-----------|

| ERC | SVD       | DAT | <u>↓</u> |            |      |      |       |      |       |     |       |       |     |       |       |     |   |   |   |           |

|     |           |     |          | ART<br>TS  |      | CRC  |       |      | ECTO  |     |       |       |     | 1     | 0-BIT | DAT | Ά |   |   |           |

| 0   | 0         | 0   | 0        | 1          | 0    | 1    | 2     | 0    | 1     | 2   | 0     | 1     | 2   | 3     | 4     | 5   | 6 | 7 | 8 | 9         |

|     |           |     |          | ART<br>ITS |      | CRC  |       |      | STAT  |     |       |       |     | B-BIT | DAT   | A   |   |   |   |           |

| 0   | 0         | 1   | 0        | 1          | 0    | 1    | 2     | 0    | 1     | 2   | 0     | 1     | 2   | 3     | 4     | 5   | 6 | 7 |   |           |

|     |           |     |          | ART        |      | CRC  |       |      |       |     | 1     | 0-BIT | DAT | 'A    |       |     |   |   |   |           |

| 0   | 1         | 0   | 0        | 1          | 0    | 1    | 2     | 0    | 1     | 2   | 3     | 4     | 5   | 6     | 7     | 8   | 9 |   |   |           |

|     |           |     |          | ART        |      | CRC  |       |      |       | 8   | B-BIT | DATA  | Δ.  |       |       | ]   |   |   |   |           |

| 0   | 1         | 1   | 0        | 1          | 0    | 1    | 2     | 0    | 1     | 2   | 3     | 4     | 5   | 6     | 7     |     |   |   |   |           |

|     |           |     |          | ART        |      | STAT |       |      |       |     | 1     | 0-BIT | DAT | ·A    |       |     |   | Р |   |           |

| 1   | 0         | 0   | 0        | 1          | 0    | 1    | 2     | 0    | 1     | 2   | 3     | 4     | 5   | 6     | 7     | 8   | 9 | 0 |   |           |

|     |           |     |          | ART        |      | STAT |       |      |       | 8   | B-BIT | DAT   | Α.  |       |       | Р   |   |   |   |           |

| 1   | 0         | 1   | 0        | 1          | 0    | 1    | 2     | 0    | 1     | 2   | 3     | 4     | 5   | 6     | 7     | 0   |   |   |   |           |

|     |           |     |          | ART        |      |      |       | 1    | 0-RIT | DAT | Δ     |       |     |       | Р     |     |   |   |   |           |

| 1   | 1         | 0   | 0<br>0   | 1          | 0    | 1    | 2     | 3    | 4     | 5   | 6     | 7     | 8   | 9     | 0     |     |   |   |   |           |

|     |           | I   | 1 67     | ADT        |      |      |       |      |       |     |       |       |     | 1     |       | ı   |   |   |   |           |

|     |           |     |          | ART<br>TS  |      |      | 8     | -BIT | DATA  |     |       |       | Р   |       |       |     |   |   |   | -020      |

| 1   | 1         | 1   | 0        | 1          | 0    | 1    | 2     | 3    | 4     | 5   | 6     | 7     | 0   |       |       |     |   |   |   | 07544-020 |

Figure 20. Data Frame Formats

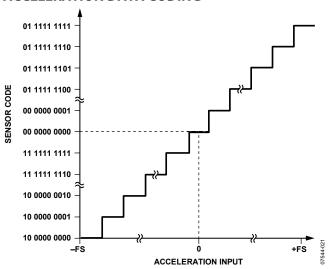

#### **ACCELERATION DATA CODING**

Figure 21. 10-Bit ADC Transfer Characteristic

**Table 12. DAT Data Bit Options**

| TWO I I I I I I WW DIE OF FIRM |                                                                                                                      |  |  |  |  |

|--------------------------------|----------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| DAT                            | Definition                                                                                                           |  |  |  |  |

| 0                              | 10-bit data sensor data transmitted. 8-bit Phase 2 configuration data left justified in 10-bit data frame (default). |  |  |  |  |

| 1                              | 8-bit sensor data transmitted.                                                                                       |  |  |  |  |

The sensor data coding is dependent on the configuration register bit settings. Either 8-bit or 10-bit sensor data can be transmitted. This 8-bit or 10-bit data range is either full range or reduced range. Whether the data range is full or reduced depends on the setting of the state vector disable and auto-zero enable configuration register bits. For more information, see Table 13.

Table 13. Full and Reduced Sensor and Device Data Ranges

| SVD <sup>1</sup> | AZE <sup>2</sup> | Data Range           |

|------------------|------------------|----------------------|

| 0                | 0                | Full                 |

| 0                | 1                | Reduced              |

| 1                | 0                | Reduced <sup>3</sup> |

| 1                | 1                | Reduced <sup>3</sup> |

<sup>&</sup>lt;sup>1</sup> SVD is the state vector disable configuration bit.

Table 14. 8-Bit Full Sensor Data Range Coding

| Decimal  | Hex  | Binary (Twos<br>Complement) | Description                            |

|----------|------|-----------------------------|----------------------------------------|

| +127     | 0x7F | 0111 1111                   | Most positive (+FS) acceleration value |

| +126     | 0x7E | 0111 1110                   |                                        |

| +125     | 0x7D | 0111 1101                   |                                        |

|          |      |                             |                                        |