# Phase Dimmable PSR LED Driver IC for LED Lighting

### Description

CY39C605 is a Primary Side Regulation (PSR) LED driver IC for LED lighting. Using the information of the primary peak current and the transformer-energy-zero time, it is able to deliver a well regulated current to the secondary side without using an opto-coupler in an isolated flyback topology. Operating in critical conduction mode, a smaller transformer is required. In addition, CY39C605 has a built-in phase dimmable circuit and can constitute the lighting system for phase dimming. It is most suitable for the general lighting applications, for example replacement of commercial and residential incandescent lamps.

### Features

- ■PSR topology in an isolated flyback circuit

- High efficiency (>80% : without dimmer) and low EMI by detecting transformer zero energy

- ■TRAIC Dimmable LED lighting

- ■Highly reliable protection functions

- □ Under voltage lock out (UVLO)

- □ Over voltage protection (OVP)

- □ Over current protection (OCP)

- □ Short circuit protection (SCP)

- □ Over temperature protection (OTP)

- Switching frequency setting : 30 kHz to 133 kHz

- ■Input voltage range VDD : 9V to 20V

- ■Input voltage for LED lighting applications : AC110V<sub>RMS</sub>, AC230V<sub>RMS</sub>

- ■Output power range for LED lighting applications : 5 W to 10 W

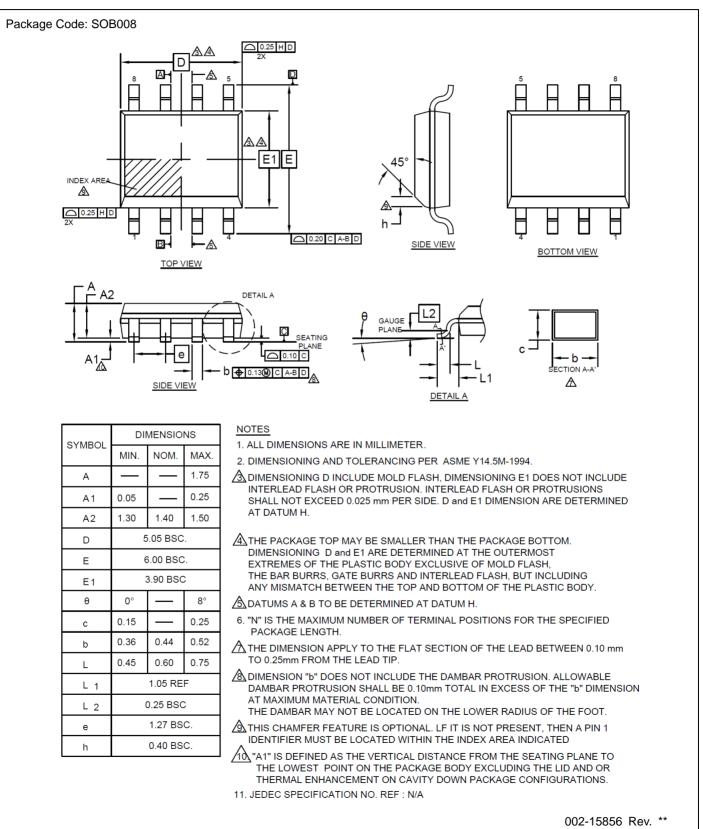

- ■Small Package : SOP-8 (3.9 mm × 5.05 mm × 1.75 mm [Max])

### Applications

- Phase dimmable (Leading/Trailing) LED lighting

- ■LED lighting

# Contents

| 1.  | Pin Assignment                           | 3  |

|-----|------------------------------------------|----|

| 2.  | Pin Descriptions                         | 3  |

| 3.  | Block Diagram                            | 4  |

| 4.  | Absolute Maximum Ratings                 | 5  |

| 5.  | Recommended Operating Conditions         | 6  |

| 6.  | Electrical Characteristics               | 7  |

| 7.  | Standard Characteristics                 | 9  |

| 8.  | Function Explanations                    | 10 |

| 8.1 | LED Current Control by PSR (Primary Side |    |

|     | Regulation)                              | 10 |

| 8.2 | Dimming Function                         | 11 |

| 8.3 | Power-On Sequence                        | 12 |

| 8.4 | Power-Off Sequence                       | 13 |

| 8.5 | IP_PEAK Detection Function               | 13 |

|     |                                          |    |

| 8.6                                       | Zero Voltage Switching Function     | 13 |  |  |  |

|-------------------------------------------|-------------------------------------|----|--|--|--|

| 8.7                                       | Protection Functions                | 14 |  |  |  |

| 9.                                        | I/O Pin Equivalent Circuit Diagram  | 15 |  |  |  |

| 10.                                       | Application Examples                | 17 |  |  |  |

| 10.1                                      | 5W Non-isolated Dimming Application | 17 |  |  |  |

| 11.                                       | Usage Precautions                   | 22 |  |  |  |

| 12.                                       | RoHS Compliance Information         | 22 |  |  |  |

| 13.                                       | Ordering Information                | 22 |  |  |  |

| 14.                                       | Package Dimensions                  | 23 |  |  |  |

| 15.                                       | Major Changes                       | 24 |  |  |  |

| Document History25                        |                                     |    |  |  |  |

| Sales, Solutions, and Legal Information26 |                                     |    |  |  |  |

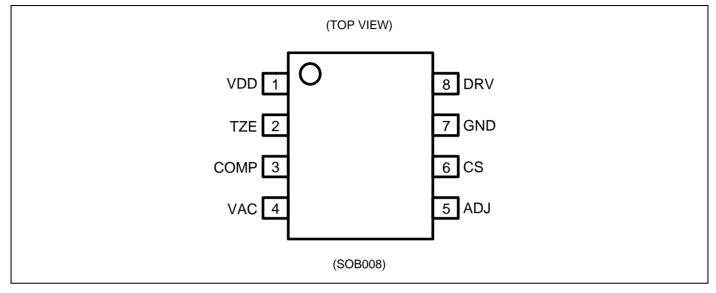

# 1. Pin Assignment

#### Figure 1-1. Pin Assignment

# 2. Pin Descriptions

#### Table 2-1. Pin Descriptions

| Pin No. | Pin Name | I/O | Description                                                    |

|---------|----------|-----|----------------------------------------------------------------|

| 1       | VDD      | -   | Power supply pin.                                              |

| 2       | TZE      | I   | Transformer Zero Energy detecting pin.                         |

| 3       | COMP     | 0   | External Capacitor connection pin for the compensation.        |

| 4       | VAC      | I   | Phase dimming control pin.                                     |

| 5       | ADJ      | 0   | Pin for adjusting the switch-on timing.                        |

| 6       | CS       | I   | Pin for detecting peak current of transformer primary winding. |

| 7       | GND      | -   | Ground pin.                                                    |

| 8       | DRV      | 0   | External MOSFET gate connection pin.                           |

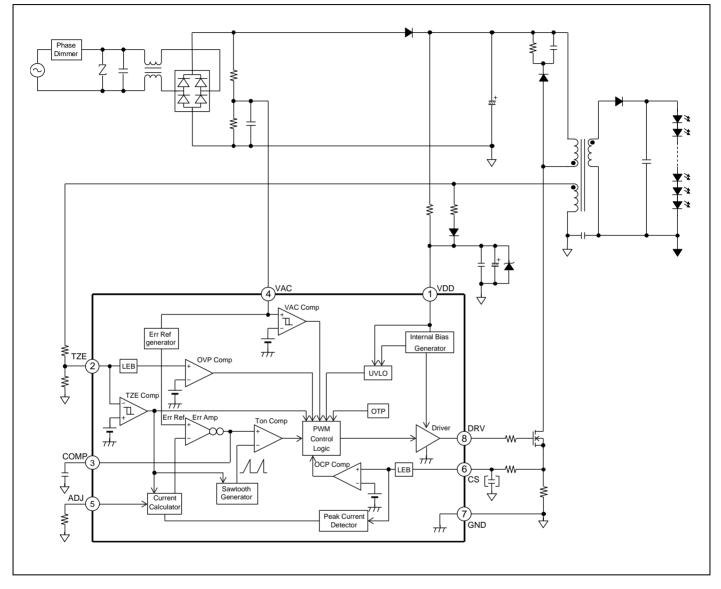

# 3. Block Diagram

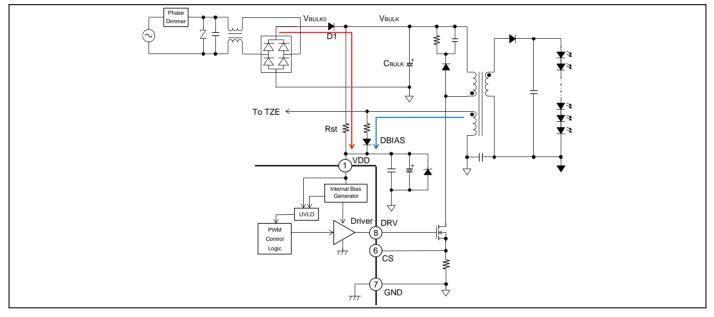

Figure 3-1. Block Diagram (Isolated Flyback Application)

# 4. Absolute Maximum Ratings

#### Table 4-1. Absolute Maximum Rating

| Parameter            | Symbol           | Condition            | Rating |          | Unit |

|----------------------|------------------|----------------------|--------|----------|------|

| Parameter            | Symbol           | Condition            | Min    | Max      | Unit |

| Power Supply Voltage | Vvdd             | VDD pin              | -0.3   | +25      | V    |

|                      | Vcs              | CS pin               | -0.3   | +6.0     | V    |

| Input Voltage        | V <sub>TZE</sub> | TZE pin              | -0.3   | +6.0     | V    |

|                      | VVAC             | VAC pin              | -0.3   | +6.0     | V    |

| Output Voltage       | Vdrv             | DRV pin              | -0.3   | +25      | V    |

| Output Current       | I <sub>ADJ</sub> | ADJ pin              | -1     | -        | mA   |

| Output Current       | I <sub>DRV</sub> | DRV pin DC level     | -50    | +50      | mA   |

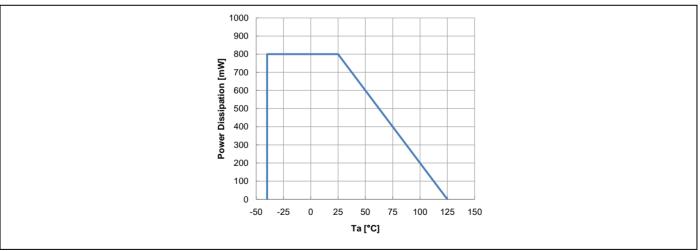

| Power Dissipation    | PD               | Ta≤+25°C             | -      | 800 (*1) | mW   |

| Storage temperature  | T <sub>STG</sub> | -                    | -55    | +125     | °C   |

| ESD Voltage 1        | Vesdh            | Human Body Model     | -2000  | +2000    | V    |

| ESD Voltage 2        | VESDC            | Charged Device Model | -1000  | +1000    | ۷    |

\*1: The value when using two layers PCB. Reference: θja (wind speed 0m/s): +125°C/W

#### Figure 4-1. Power Dissipation

#### WARNING:

1. Semiconductor devices may be permanently damaged by application of stress (including, without limitation, voltage, current or temperature) in excess of absolute maximum ratings. Do not exceed any of these ratings.

# 5. Recommended Operating Conditions

#### Table 5-1. Recommended Operating Conditions

| Parameter                         | Symbol           | Condition                       |     | Value |       | Unit |

|-----------------------------------|------------------|---------------------------------|-----|-------|-------|------|

| Faialleter                        | Symbol           | Condition                       | Min | Тур   | Max   | Unit |

| VDD pin Input Voltage             | VDD              | VDD pin                         | 9   | -     | 20    | V    |

| VAC pin Input Voltage             | Vvac             | VAC pin After UVLO release      | 0   | -     | 5     | V    |

| VAC pin Input Current             | Ivac             | VAC pin Before UVLO release     | 0   | -     | 2.5   | μA   |

| TZE pin Resistance                | R <sub>TZE</sub> | TZE pin                         | 50  | -     | 200   | kΩ   |

| ADJ pin Resistance                | Radj             | ADJ pin                         | 9.3 | -     | 185.5 | kΩ   |

| COMP pin Capacitance              | Ссомр            | COMP pin                        | -   | 0.01  | -     | μF   |

| VDD pin Capacitance               | C <sub>BP</sub>  | Set between VDD pin and GND pin | -   | 4.7   | -     | μF   |

| Operating Junction<br>Temperature | Тј               | -                               | -40 | -     | +125  | °C   |

#### WARNING:

- 1. The recommended operating conditions are required in order to ensure the normal operation of the semiconductor device. All of the device's electrical characteristics are warranted when the device is operated under these conditions.

- 2. Any use of semiconductor devices will be under their recommended operating condition.

- 3. Operation under any conditions other than these conditions may adversely affect reliability of device and could result in device failure.

- 4. No warranty is made with respect to any use, operating conditions or combinations not represented on this data sheet. If you are considering application under any conditions other than listed herein, please contact sales representatives beforehand.

# 6. Electrical Characteristics

#### Table 6-1 . Electrical Characteristics

| _                        |                                    |                    |            |                                                                                                                      |       | Value |       |      |

|--------------------------|------------------------------------|--------------------|------------|----------------------------------------------------------------------------------------------------------------------|-------|-------|-------|------|

| Para                     | ameter                             | Symbol             | Pin        | Condition                                                                                                            | Min   | Тур   | Max   | Unit |

| POWER                    | Power supply                       | IVDD(STATIC)       | VDD        | $V_{VDD} = 20V, V_{TZE} = 1V$                                                                                        | -     | 3     | 3.6   | mA   |

| SUPPLY<br>CURRENT        | current                            | IVDD(OPERATING)    | VDD        | $V_{VDD} = 20V, Qg = 20 nC,$<br>$f_{SW} = 133 \text{ kHz}$                                                           | -     | 5.6   | -     | mA   |

|                          | UVLO Turn-on<br>threshold voltage  | VTH                | VDD        | -                                                                                                                    | 12.25 | 13    | 13.75 | V    |

| UVLO                     | UVLO Turn-off<br>threshold voltage | V <sub>TL</sub>    | VDD        | -                                                                                                                    | 7.55  | 7.9   | 8.5   | V    |

|                          | Startup current                    | Istart             | VDD        | V <sub>VDD</sub> = 7V                                                                                                | -     | 65    | 160   | μA   |

|                          | Zero energy<br>threshold voltage   | Vtzetl             | TZE        | TZE = "H" to "L"                                                                                                     | -     | 20    | -     | mV   |

|                          | Zero energy<br>threshold voltage   | V <sub>TZETH</sub> | TZE        | TZE = "L" to "H"                                                                                                     | 0.6   | 0.7   | 0.8   | V    |

|                          | TZE clamp voltage                  | Vtzeclamp          | TZE        | Ι <sub>ΤΖΕ</sub> = -10 μΑ                                                                                            | -200  | -160  | -100  | mV   |

| ZERO ENERGY<br>DETECTION | OVP threshold voltage              | Vtzeovp            | TZE        | -                                                                                                                    | 4.15  | 4.3   | 4.45  | V    |

|                          | OVP blanking time                  | tovpblank          | TZE        | -                                                                                                                    | 0.6   | 1     | 1.7   | μs   |

|                          | TZE input current                  | Ітде               | TZE        | V <sub>TZE</sub> = 5V                                                                                                | -1    | -     | +1    | μA   |

| COMPENSATIO              | Source current                     | Iso                | COMP       | $\label{eq:VCOMP} \begin{array}{l} V_{COMP} = 2V, \ V_{CS} = 0V, \\ V_{VAC} = 1.85V \end{array}$                     | -     | -27   | -     | μA   |

| Ν                        | Trans conductance                  | gm                 | COMP       | V <sub>COMP</sub> = 2.5V, V <sub>CS</sub> = 1V                                                                       | -     | 96    | -     | µA/V |

|                          | VAC input current                  | Ivac               | VAC        | V <sub>VAC</sub> = 5V                                                                                                | -0.1  | -     | +0.1  | μA   |

| DIMMING                  | VACCMP<br>threshold voltage        | VVACCMPVTH         | VAC        | -                                                                                                                    | 135   | 150   | 165   | mV   |

|                          | VACCMP<br>hysteresis               | VVACCMPHYS         | VAC        | -                                                                                                                    | -     | 70    | -     | mV   |

|                          | ADJ voltage                        | V <sub>ADJ</sub>   | ADJ        | -                                                                                                                    | 1.81  | 1.85  | 1.89  | V    |

|                          | ADJ source current                 | ladj               | ADJ        | V <sub>ADJ</sub> = 0V                                                                                                | -650  | -450  | -250  | μA   |

| ADJUSTMENT               | ADJ time                           | T <sub>ADJ</sub>   | TZE<br>DRV | $ \begin{array}{l} T_{ADJ}\left(R_{ADJ}=51\;k\Omega\right) \\ T_{ADJ}\left(R_{ADJ}=9.1\;k\Omega\right) \end{array} $ | 490   | 550   | 610   | ns   |

|                          | Minimum switching period           | T <sub>SW</sub>    | TZE<br>DRV | -                                                                                                                    | 6.75  | 7.5   | 8.25  | μs   |

| $(1a = +25^{\circ}C, VVDD = 12V)$ |                       |                    |      |                                                |         |       |      |      |  |

|-----------------------------------|-----------------------|--------------------|------|------------------------------------------------|---------|-------|------|------|--|

|                                   | Parameter             | Symbol             | Pin  | Condition                                      |         | Value |      | Unit |  |

| Parameter                         |                       | Symbol             | FIII | Condition                                      | Min Typ |       | Max  | Unit |  |

|                                   | OCP threshold voltage | V <sub>OCPTH</sub> | CS   | -                                              | 1.9     | 2     | 2.1  | V    |  |

| CURRENT<br>SENSE                  | OCP delay time        | tocpdly            | CS   | -                                              | -       | 400   | 500  | ns   |  |

| SENSE                             | CS input current      | lcs                | CS   | Vcs = 5V                                       | -1      | -     | +1   | μA   |  |

|                                   | DRV high voltage      | V <sub>DRVH</sub>  | DRV  | VDD = 18V, I <sub>DRV</sub> = -30 mA           | 7.6     | 9.4   | -    | V    |  |

|                                   | DRV low voltage       | Vdrvl              | DRV  | VDD = 18V, I <sub>DRV</sub> = 30 mA            | -       | 130   | 260  | mV   |  |

|                                   | Rise time             | trise              | DRV  | VDD = 18V, CLOAD = 1 nF                        | -       | 94    | -    | ns   |  |

| DRV                               | Fall time             | t <sub>FALL</sub>  | DRV  | VDD = 18V, CLOAD = 1 nF                        | -       | 16    | -    | ns   |  |

| DRV                               | Minimum on time       | tonmin             | DRV  | TZE trigger                                    | 300     | 500   | 700  | ns   |  |

|                                   | Maximum on time       | tonmax             | DRV  | -                                              | 27      | 44    | 60   | μs   |  |

|                                   | Minimum off time      | toffmin            | DRV  | -                                              | 1       | 1.5   | 1.93 | μs   |  |

|                                   | Maximum off time      | toffmax            | DRV  | TZE = GND                                      | 270     | 320   | 370  | μs   |  |

| OTD                               | OTP threshold         | TOTP               | -    | Tj, temperature rising                         | -       | +150  | -    | °C   |  |

| OTP                               | OTP hysteresis        | TOTPHYS            | -    | Tj, temperature falling,<br>degrees below Totp | -       | +25   | -    | °C   |  |

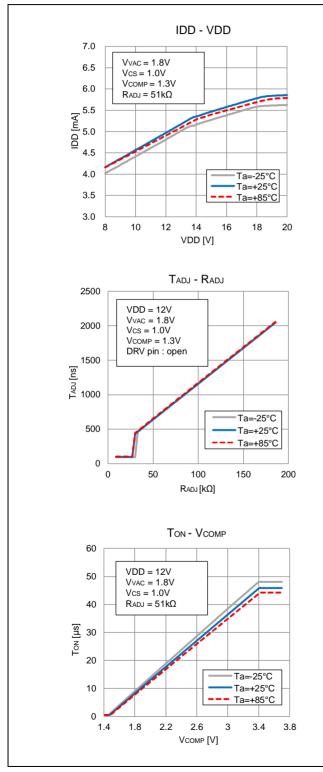

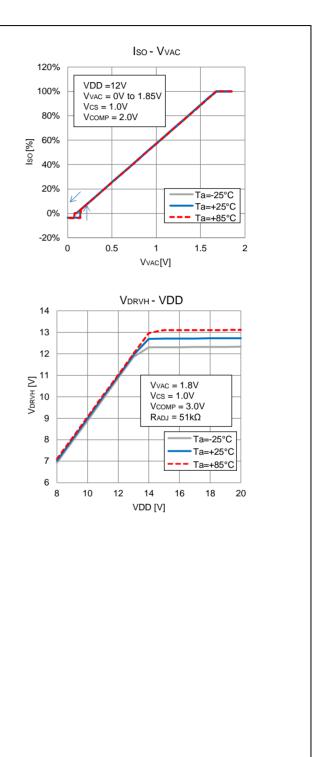

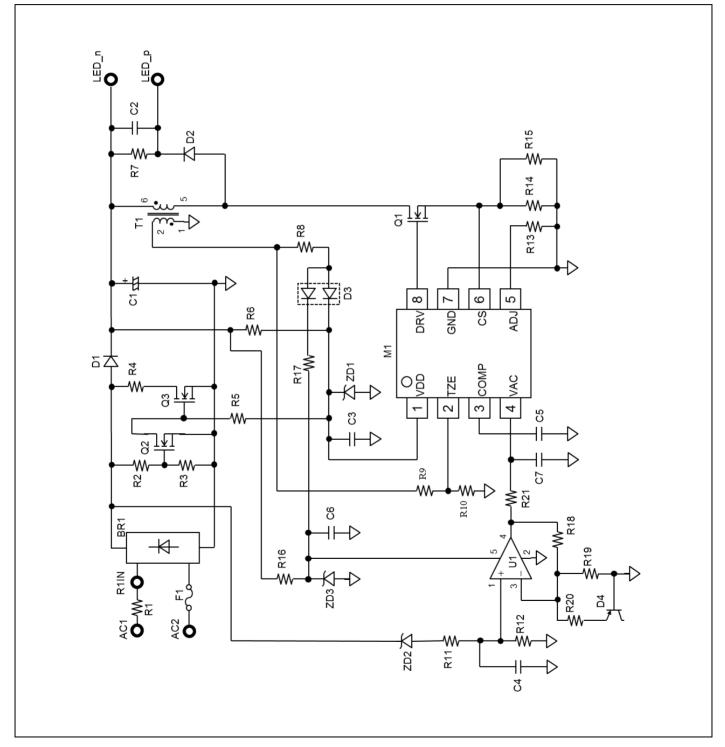

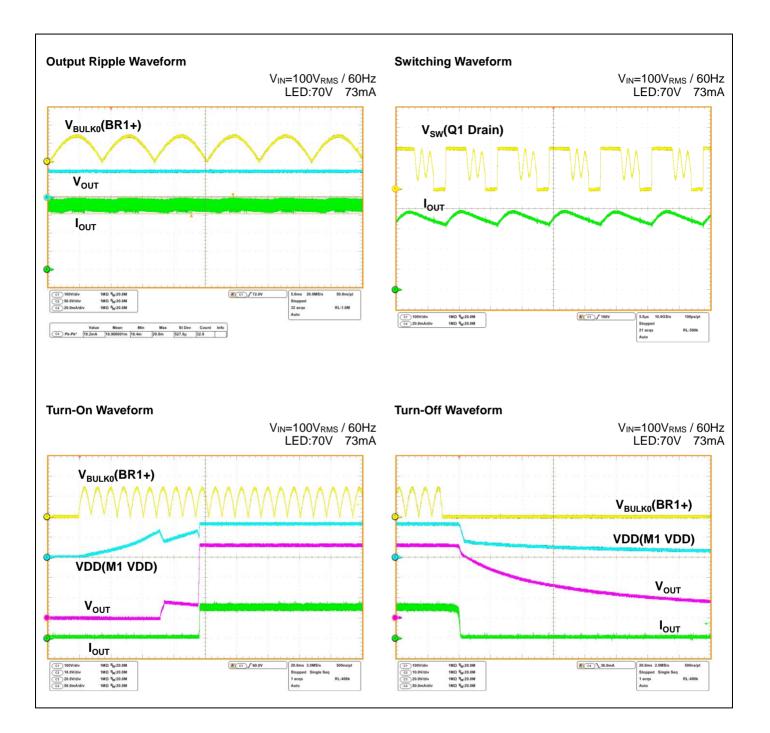

# 7. Standard Characteristics

### Figure 7-1. Standard Characteristics

### 8. Function Explanations

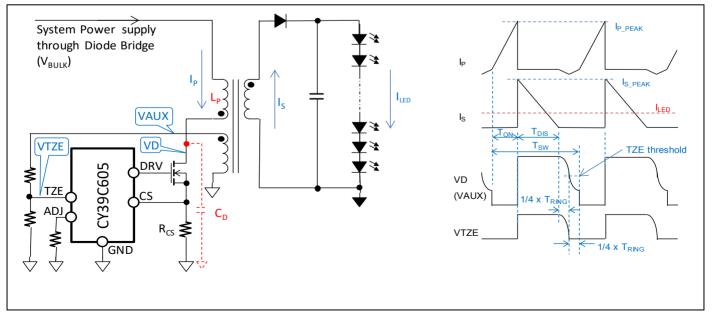

#### 8.1 LED Current Control by PSR (Primary Side Regulation)

CY39C605 regulates the average LED current ( $I_{LED}$ ) by feeding back the information based on Primary Winding peak current ( $I_{P_PEAK}$ ) and Secondary Winding energy discharge time ( $T_{DIS}$ ) and switching period ( $T_{SW}$ ). Figure 8-1 shows the operating waveform in steady state. I<sub>P</sub> is Primary Winding current and I<sub>S</sub> is Secondary Winding current. I<sub>LED</sub> as an average current of the Secondary Winding is described by the following equation.

$$I_{LED} = \frac{1}{2} \times I_{S\_PEAK} \times \frac{T_{DIS}}{T_{SW}}$$

Using I<sub>P\_PEAK</sub> and the transformer Secondary to Primary turns ratio (N<sub>P</sub>/N<sub>S</sub>), Secondary Winding peak current (I<sub>S\_PEAK</sub>) is described by the following equation.

$$I_{S}PEAK = \frac{N_P}{N_S} \times I_PPEAK$$

Therefore,

$$I_{\text{LED}} = \frac{1}{2} \times \frac{N_{\text{P}}}{N_{\text{S}}} \times I_{\text{P}_{\text{P}}\text{EAK}} \times \frac{T_{\text{DIS}}}{T_{\text{SW}}}$$

CY39C605 detects  $T_{DIS}$  by monitoring TZE pin and  $I_{P_PEAK}$  by monitoring CS pin. An internal Err Amp sinks gm current proportional to  $I_{P_PEAK}$  from COMP pin during  $T_{DIS}$  period. In steady state, since the average of the gm current is equal to internal reference current (Iso), the voltage on COMP pin (V<sub>COMP</sub>) is nearly constant.

$$I_{P\_PEAK} \times R_{CS} \times gm \times T_{DIS} = I_{SO} \times T_{SW}$$

In above equation, gm is transconductance of the Err Amp and  $R_{\mbox{\scriptsize CS}}$  is a sense resistance.

Eventually,  $I_{\text{LED}} \, \text{can}$  be calculated by the following equation.

$$I_{\text{LED}} = \frac{1}{2} \times \frac{N_{\text{P}}}{N_{\text{S}}} \times \frac{I_{\text{SO}}}{gm} \times \frac{1}{R_{\text{CS}}}$$

#### Figure 8-1. LED Current Control Waveform

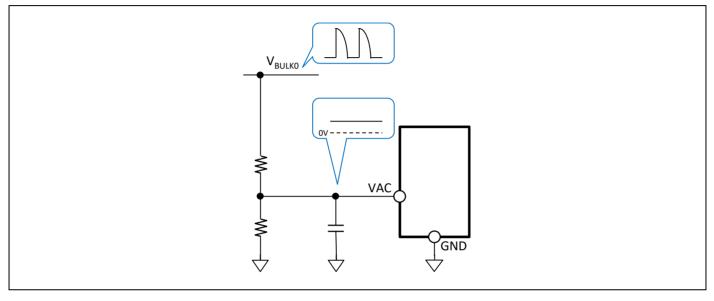

#### 8.2 Dimming Function

CY39C605 has the built-in Phase dimmable circuit to control I<sub>LED</sub> by changing a reference of Err Amp based on the input dimming control level on the VAC pin and realizes dimming. Figure 8-2 shows the input circuit to the VAC pin for phase dimming. V<sub>BULK0</sub> is divided and filtered into an analog voltage with RC network. It is possible to configurate phase dimmable system by inputting the voltage to the VAC pin.

#### Figure 8-2. VAC Pin Input Circuit

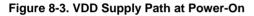

#### 8.3 Power-On Sequence

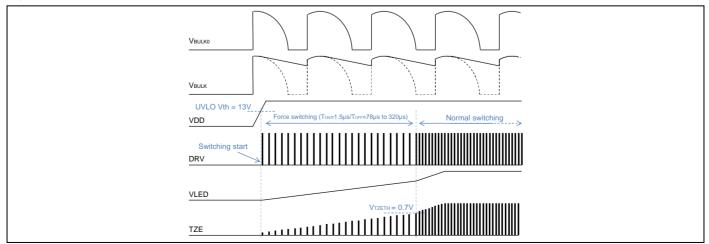

When the AC line voltage is supplied,  $V_{BULK}$  is powered from the AC line through a diode bridge and a diode (D1) with charging a capacitor ( $C_{BULK}$ ), and the VDD pin is charged from  $V_{BULK}$  through a start-up resistance (Rst). (Figure 8-3 red path)

When the VDD pin is charged up and the voltage on the VDD pin ( $V_{VDD}$ ) rises above the UVLO threshold voltage, an internal Bias circuit starts operating, and CY39C605 starts the dimming control. After the UVLO is released, this device enables switching and is operating in a forced switching mode ( $T_{ON} = 1.5 \mu$ s,  $T_{OFF} = 78 \mu$ s to 320  $\mu$ s). When the voltage on the TZE pin reaches the Zero energy threshold voltage ( $V_{TZETH} = 0.7V$ ), CY39C605 enters normal operation mode. After the switching begins, the VDD pin is also charged from Auxiliary Winding through an external diode (DBIAS). (Figure 8-3 blue path)

During start-up period  $V_{VDD}$  is not supplied from Auxiliary Winding, because the LED voltage is low.  $V_{VDD}$  decreases gradually until the LED voltage rises above enough high that the Auxiliary Winding voltage can exceed  $V_{VDD}$ . In this period, if  $V_{VDD}$  falls below the UVLO threshold voltage, the switching stops. When the VDD pin is charged up again and  $V_{VDD}$  rises above the UVLO threshold voltage, CY39C605 restarts the switching. This device repeats above operation until the LED voltage rises above enough high.  $V_{VDD}$  becomes stable after that.

#### Figure 8-4. Power-On Waveform

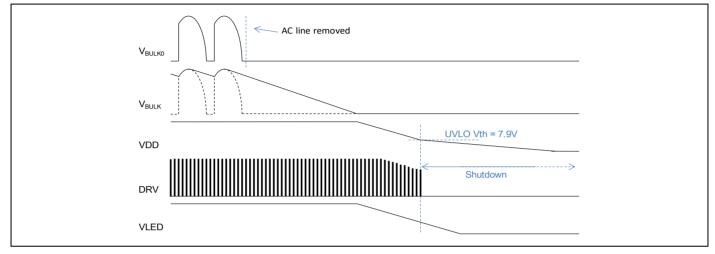

#### 8.4 Power-Off Sequence

After the AC line voltage is removed,  $V_{BULK}$  is discharged by switching operation. Since any Secondary Winding current does not flow,  $I_{LED}$  is supplied only from output capacitors and decreases gradually.  $V_{VDD}$  also decreases because there is no current supply from both Auxiliary Winding and  $V_{BULK}$ . When  $V_{VDD}$  falls below the UVLO threshold voltage, CY39C605 shuts down.

#### 8.5 IP\_PEAK Detection Function

CY39C605 detects Primary Winding peak current ( $I_{P_PEAK}$ ) of Transformer.  $I_{LED}$  is set by connecting a sense resistance (Rcs) between CS pin and GND pin. Maximum  $I_{P_PEAK}$  ( $I_{P_PEAKMAX}$ ) limited by Over Current Protection (OCP) can also be set with the resistance.

Using the Secondary to Primary turns ratio (NP/Ns) and ILED, RCs is set as the following equation (refer to 8.1)

$$R_{CS} = \frac{N_{P}}{N_{S}} \times \frac{0.14}{I_{LED}}$$

In addition, using the OCP threshold voltage (V<sub>OCPTH</sub>) and R<sub>CS</sub>, I<sub>P\_PEAKMAX</sub> is calculated with the following equation.

$$I_{P_{PEAKMAX}} = \frac{V_{OCPTH}}{R_{CS}}$$

#### 8.6 Zero Voltage Switching Function

CY39C605 has built-in zero voltage switching function to minimize switching loss of the external switching MOSFET. This device detects a zero crossing point through a resistor divider connected from TZE pin to Auxiliary Winding. A zero energy detection circuit detects a negative crossing point of the voltage on TZE pin to Zero energy threshold voltage ( $V_{TZETL}$ ). On-timing of switching MOSFET is decided with waiting an adjustment time ( $t_{ADJ}$ ) after the negative crossing occurs.

$t_{ADJ}$  is set by connecting an external resistance ( $R_{ADJ}$ ) between ADJ pin and GND pin. Using Primary Winding inductance ( $L_P$ ) and the parasitic drain capacitor of switching MOSFET ( $C_D$ ),  $t_{ADJ}$  is calculated with the following equation.

$$t_{ADJ} = \frac{\pi \sqrt{L_P \times C_D}}{2}$$

Using  $t_{ADJ}$ ,  $R_{ADJ}$  is expressed by the following calculation.

$R_{ADJ} [k\Omega] = 0.0927 \times t_{ADJ} [ns]$

#### 8.7 Protection Functions

#### **Under Voltage Lockout Protection (UVLO)**

The under voltage lockout protection (UVLO) prevents IC from a malfunction in the transient state during  $V_{VDD}$  startup and a malfunction caused by a momentary drop of  $V_{VDD}$ , and protects the system from destruction/deterioration. An UVLO comparator detects the voltage decrease below the UVLO threshold voltage on VDD pin, and then DRV pin is turned to "L" and the switching stops. CY39C605 automatically returns to normal operation mode when  $V_{VDD}$  increases above the UVLO threshold voltage.

#### **Over Voltage Protection (OVP)**

The over voltage protection (OVP) protects Secondary side components from an excessive voltage stress. If the LED is disconnected, the output voltage of Secondary Winding rises up. The output overvoltage can be detected by monitoring TZE pin. During Secondary Winding energy discharge time,  $V_{TZE}$  is proportional to  $V_{AUX}$  and the voltage of Secondary Winding (refer to 8.1). When  $V_{TZE}$  rises higher than the OVP threshold voltage for 3 continues switching cycles, DRV pin is turned to "L", and the switching stops (latch off). When  $V_{VDD}$  drops below the UVLO threshold voltage, the latch is removed.

#### **Over Current Protection (OCP)**

The over current protection (OCP) prevents inductor or transformer from saturation. The drain current of the external switching MOSFET is limited by OCP. When the voltage on CS pin reaches the OCP threshold voltage, DRV pin is turned to "L" and the switching cycle ends. After zero crossing is detected on TZE pin again, DRV pin is turned to "H" and the next switching cycle begins.

#### **Short Circuit Protection (SCP)**

The short circuit protection (SCP) protects the transformer and the Secondary side diode from an excessive current stress. When the short circuit between LED terminals occurs, output voltage decreases. If the voltage on TZE pin falls below SCP threshold voltage,  $V_{COMP}$  is discharged and fixed at 1.5V and then the switching enters a low frequency mode.( $T_{ON} = 1.5 \ \mu s \ /T_{OFF} = 78 \ \mu s$  to 320  $\mu s$ )

#### **Over Temperature Protection (OTP)**

The over temperature protection (OTP) protects IC from thermal destruction. When the junction temperature reaches +150°C, DRV pin is turned to "L", and the switching stops. It automatically returns to normal operation mode if the junction temperature falls back below +125°C.

| Function                                   | PIN Operation |               |        | Detection Condition | Return                    | Remarks         |  |

|--------------------------------------------|---------------|---------------|--------|---------------------|---------------------------|-----------------|--|

| runction                                   | DRV           |               |        | Condition           | Nemarks                   |                 |  |

| Normal Operation                           | Active        | Active        | Active | -                   | -                         | -               |  |

| Under Voltage Lockout<br>Protection (UVLO) | L             | L             | L      | VDD < 7.9V          | VDD > 13V                 | Auto<br>Restart |  |

| Over Voltage Protection<br>(OVP)           | L             | 1.5V<br>fixed | Active | TZE > 4.3V          | VDD < 7.9V<br>→ VDD > 13V | Latch off       |  |

| Over Current Protection (OCP)              | L             | Active        | Active | CS > 2V             | Cycle by cycle            | Auto<br>Restart |  |

| Short Circuit Protection (SCP)             | Active        | 1.5V<br>fixed | Active | TZE (peak) < 0.7V   | TZE (peak) > 0.7V         | Auto<br>Restart |  |

| Over Temperature<br>Protection (OTP)       | L             | 1.5V<br>fixed | Active | Tj> +150°C          | Tj< +125℃                 | Auto<br>Restart |  |

#### **Table 8-1. Protection Functions Table**

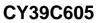

# 9. I/O Pin Equivalent Circuit Diagram

#### Figure 9-1. I/O Pin Equivalent Circuit Diagram

| Pin No. | Pin<br>Name | Equivalent Circuit Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|---------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5       | ADJ         | ADJ (5<br>GND (7)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 6       | CS          | CS 6 W VREF5V<br>GND 7 GND 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 8       | DRV         | VDD (1<br>GND (1)<br>GND (1)<br>GND (1)<br>(GND (1)<br>(GND (1))<br>(GND (1)) |

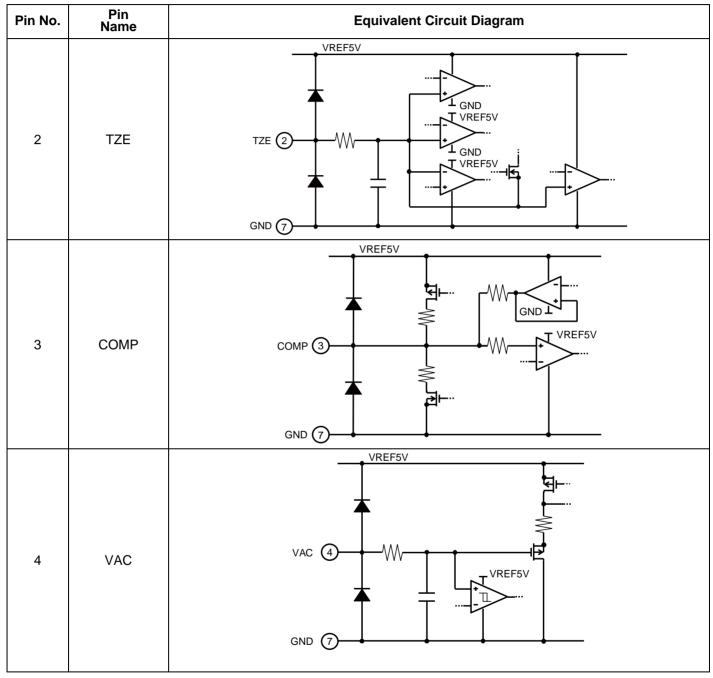

### **10. Application Examples**

### 10.1 5W Non-isolated Dimming Application

### Input: AC90V<sub>RMS</sub>~110V<sub>RMS</sub>, Output: 70mA/70V~76V, Ta = +25°C

#### Figure 10-1. 5W EVB Schematic

#### Table 10-1. 5W BOM List

| No. | Component | Description                                                       | Part No.           | Vendor           |

|-----|-----------|-------------------------------------------------------------------|--------------------|------------------|

| 1   | M1        | LED driver IC SOP-8                                               | CY39C605           | Cypress          |

| 2   | U1        | Op-Amp, Low voltage Rail-to-Rail, 130µA,<br>SOT-23-5              | LMV321             | TI               |

| 3   | T1        | Transformer, Lp = 550 µH Np/Na = 150/35                           | EE808              | -                |

| 4   | Q1        | MosFET N-CH 600V 2.8A I-PAK                                       | FQU5N60C           | Fairchild        |

| 5   | Q2        | MosFET N-CH 60V 115mA SOT-23                                      | 2N7002             | Fairchild        |

| 6   | Q3        | MosFET N-CH 600V 0.3A TO-92                                       | FQN1N60C           | Fairchild        |

| 7   | BR1       | Bridge Rectifiers, 0.5A, 600V, SOIC-4                             | MB6S               | Fairchild        |

| 8   | ZD1, ZD2  | Diode, Zener, 18V, 500mW, SOD-123                                 | MMSZ5248B          | Fairchild        |

| 9   | ZD3       | Diode, Zener, 5.1V, 500mW, SOD-123                                | MMSZ4689           | Fairchild        |

| 10  | D1, D2    | Diode, fast rectifier, 1A, 400V, SMA                              | ES1G               | Fairchild        |

| 11  | D3        | Diode, 200mA, 200V, SOT-23                                        | MMBD1405           | Fairchild        |

| 12  | D4        | PNP Bipolar Transistor 12V 3A CPH3                                | CPH3106            | On semiconductor |

| 13  | F1        | Fuse, chip, 2A, AC/DC125V, 1206                                   | 3410.0035.01       | Schurter Inc     |

| 14  | C1        | Capacitor, aluminum electrolytic, 8.2µF 200V<br>\$\$0 \times 11.0 | 200LLE8R2MEFC8X9   | Rubycon          |

| 15  | C2        | Capacitor Ceramic 2.2µF 100V 1206                                 | GRM31CR72A225KA73L | murata           |

| 16  | C3        | Capacitor Ceramic 4.7µF 35V 0603                                  | -                  | -                |

| 17  | C4, C7    | Capacitor Ceramic 10µF 25V 0603                                   | -                  | -                |

| 18  | C5        | Capacitor Ceramic 0.01µF 50V 0603                                 | -                  | -                |

| 19  | C6        | Capacitor Ceramic 0.1µF 50V 0603                                  | -                  | -                |

| 20  | R1        | Resistor, winding 10Ω 3W ±5%                                      | -                  | -                |

| 21  | R2, R11   | Resistor, chip, 240kΩ, 1/10W, 0603                                | -                  | -                |

| 22  | R3        | Resistor, chip, 10kΩ, 1/10W, 0603                                 | -                  | -                |

| 23  | R4        | Resistor, chip, 2kΩ, 1/4W, 1206                                   | -                  | -                |

| 24  | R5        | Resistor, chip, 470kΩ, 1/10W, 0603                                | -                  | -                |

| 25  | R6        | Resistorr, chip, 200kΩ 1/4W, 1206                                 | -                  | -                |

| 26  | R7        | Resistor, chip, 100kΩ, 1/10W, 0603                                | -                  | -                |

| 27  | R8        | Resistor, chip, 10Ω, 1/10W, 0603                                  | -                  | -                |

| 28  | R9        | Resistor, chip, 110kΩ, 1/10W, 0603                                | -                  | -                |

| 29  | R10       | Resistor, chip, 30kΩ, 1/10W, 0603                                 | -                  | -                |

| 30  | R12       | Resistor, chip, 3.0kΩ, 1/10W, 0603                                | -                  | -                |

| 31  | R13       | Resistor, chip, 24kΩ, 1/10W, 0603                                 | -                  | -                |

| 32  | R14       | Resistor, chip, 3.3Ω, 1/10W, 0603                                 | -                  | -                |

| 33  | R15       | Resistor, chip, 4.7Ω, 1/10W, 0603                                 | -                  | -                |

| 34  | R16       | Resistorr, chip, 150kΩ 1/4W, 1206                                 | -                  | -                |

| 35  | R17       | Resistor, chip, 5.1kΩ, 1/10W, 0603                                | -                  | -                |

| 36  | R18       | Resistor, chip, 36kΩ, 1/10W, 0603                                 | -                  | -                |

| 37  | R19       | Resistor, chip, 150kΩ, 1/10W, 0603                                | -                  | -                |

| 38  | R20       | Resistor, chip, 3.3kΩ, 1/10W, 0603                                | -                  | -                |

| 39  | R21       | Resistor, chip, 1kΩ, 1/10W, 0603                                  | -                  | -                |

#### ΤI

| : Texas Instruments Incorporated | orated |

|----------------------------------|--------|

|----------------------------------|--------|

| ••               | • |                                             |

|------------------|---|---------------------------------------------|

| Fairchild        | : | Fairchild Semiconductor International, Inc. |

| On Semiconductor | : | ON Semiconductor                            |

| Schurter Inc     | : | Schurter Holding AG                         |

| Rubycon          | : | Rubycon Corporation                         |

| muRata           | : | Murata Manufacturing Co., Ltd.              |

|                  |   |                                             |

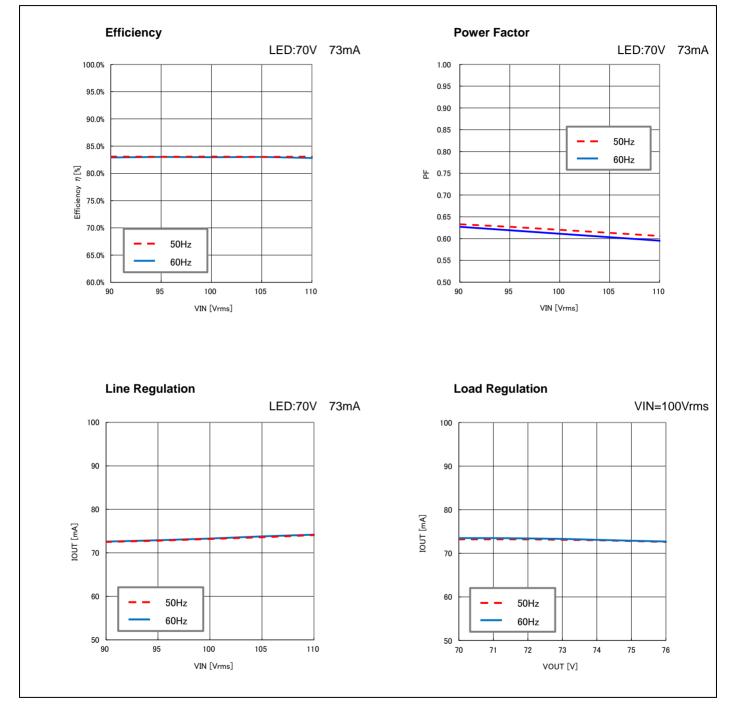

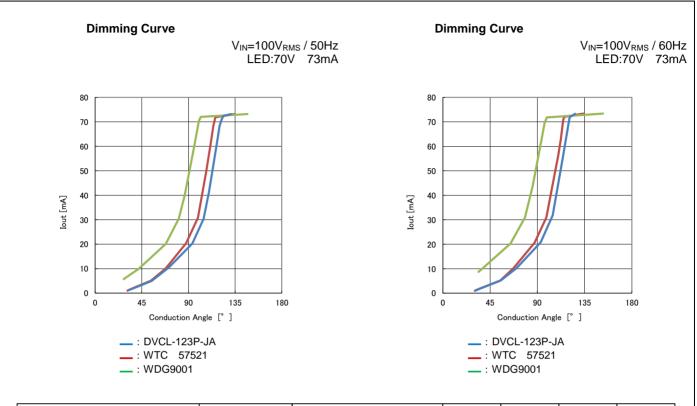

#### Figure 10-2. 5W Reference Data

| Dimmer    |              | Input          | Turne         | Minimum  | Minimum               | Maximum  | Maximum               |

|-----------|--------------|----------------|---------------|----------|-----------------------|----------|-----------------------|

| Vendor    | Parts Name   | Condition      | Туре          | Angle(°) | I <sub>OUT</sub> (mA) | Angle(°) | I <sub>OUT</sub> (mA) |

| LUTRON    | DVCL-123P-JA | VIN=100Vrms    | Leading Edge  | 32.8     | 1.3                   | 130.9    | 73.2                  |

| Panasonic | WTC 57521    | 50Hz           | Leading Edge  | 31.1     | 1.0                   | 134.1    | 73.2                  |

| TOSHIBA   | WDG9001      | (Japan Dimmer) | Trailing Edge | 27.5     | 5.7                   | 146.9    | 73.2                  |

| LUTRON    | DVCL-123P-JA | VIN=100Vrms    | Leading Edge  | 31.3     | 1.2                   | 126.1    | 73.3                  |

| Panasonic | WTC 57521    | 60Hz           |               | 30.5     | 1.0                   | 133.7    | 73.4                  |

| TOSHIBA   | WDG9001      | (Japan Dimmer) | Trailing Edge | 33.9     | 8.7                   | 152.5    | 73.4                  |

Total Harmonic Distortion(THD) LED:70V 73mA

Document Number: 002-08444 Rev. \*C

### **11. Usage Precautions**

#### Do not configure the IC over the maximum ratings.

If the IC is used over the maximum ratings, the LSI may be permanently damaged.

It is preferable for the device to normally operate within the recommended usage conditions. Usage outside of these conditions can have an adverse effect on the reliability of the LSI.

#### Use the device within the recommended operating conditions.

The recommended values guarantee the normal LSI operation under the recommended operating conditions.

The electrical ratings are guaranteed when the device is used within the recommended operating conditions and under the conditions stated for each item.

#### Printed circuit board ground lines should be set up with consideration for common impedance.

#### Take appropriate measures against static electricity.

Containers for semiconductor materials should have anti-static protection or be made of conductive material.

After mounting, printed circuit boards should be stored and shipped in conductive bags or containers.

Work platforms, tools, and instruments should be properly grounded.

**\blacksquare** Working personnel should be grounded with resistance of 250 k $\Omega$  to 1 M $\Omega$  in serial between body and ground.

#### Do not apply negative voltages.

The use of negative voltages below - 0.3 V may make the parasitic transistor activated to the LSI, and can cause malfunctions.

### **12. RoHS Compliance Information**

This product has observed the standard of lead, cadmium, mercury, Hexavalent chromium, polybrominated biphenyls (PBB), and polybrominated diphenyl ethers (PBDE).

# **13. Ordering Information**

#### Table 13-1. Ordering Information

| Part Number          | Package           | Shipping Form |  |  |

|----------------------|-------------------|---------------|--|--|

| CY39C605PNF-G-JNEFE1 | 8-pin plastic SOP | Emboss        |  |  |

| CY39C605PNF-G-JNE1   | (SOB008)          | Tube          |  |  |

# 14. Package Dimensions

# 15. Major Changes

#### Spansion Publication Number: MB39C605-DS405-00017

| Page       | Section                                                        | Descriptions                                                                                                      |  |

|------------|----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|--|

| Revision 1 | .0                                                             |                                                                                                                   |  |

| -          | -                                                              | Initial release                                                                                                   |  |

| Revision 2 | 0                                                              |                                                                                                                   |  |

| 16         | 11.6 Zero Voltage Switching Function                           | Corrected the RADJ formula                                                                                        |  |

| 20         | 13. Application Examples                                       | Added Application Examples                                                                                        |  |

| 26         | 15. Ordering Information                                       | Added Shipping in Table 15-1                                                                                      |  |

| -          | -                                                              | Rewrote entire document for improving the ease of understanding (the original intentions are remained unchanged). |  |

| Revision 3 | .0                                                             | · · · · · · · · · · · · · · · · · · ·                                                                             |  |

| 8          | 7. Absolute Maximum Ratings                                    | Removed ESD Voltage (Machine Model) from Table 7-1                                                                |  |

| -          | Labeling Sample                                                | Removed section of Labeling Sample                                                                                |  |

| 28         | 17. Recommended mounting condition<br>[JEDEC Level3] Lead Free | Changed Recommended Condition from three conditions to one condition "JEDEC LEVEL3"                               |  |

NOTE: Please see "Document History" about later revised information.

# **Document History**

### Document Title: CY39C605 Phase Dimmable PSR LED Driver IC for LED Lighting

Document Number: 002-08444

| Revision | ECN     | Orig. of<br>Change | Submission<br>Date | Description of Change                                                                                                                                                                                                                                                                                                                                                                         |

|----------|---------|--------------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| **       | -       | ΤΟΥΟ               | 02/20/2015         | Migrated to Cypress and assigned document number 002-08444.<br>No change to document contents or format.                                                                                                                                                                                                                                                                                      |

| *A       | 5211375 | ΤΟΥΟ               | 04/12/2016         | Updated to Cypress format.                                                                                                                                                                                                                                                                                                                                                                    |

| *В       | 5742349 | HIXT               | 05/22/2017         | Updated Pin Assignment:<br>Change the package name from FPT-8P-M02 to SOB008<br>Added RoHS Compliance Information<br>Updated Ordering Information:<br>Change the package name from FPT-8P-M02 to SOB008<br>Deleted "Marking Format"<br>Deleted "Marking Format"<br>Deleted "Recommended Mounting Condition [JEDEC Level3] Lead Free"<br>Updated Package Dimensions: Updated to Cypress format |

| *C       | 6437385 | ATTS               | 01/10/2019         | Changed part number to CY39C605<br>Remove Easy Designsim comments                                                                                                                                                                                                                                                                                                                             |

### Sales, Solutions, and Legal Information

#### Worldwide Sales and Design Support

Cypress maintains a worldwide network of offices, solution centers, manufacturer's representatives, and distributors. To find the office closest to you, visit us at Cypress Locations.

#### **Products**

| Arm <sup>®</sup> Cortex <sup>®</sup> Microcontrollers | cypress.com/arm        |

|-------------------------------------------------------|------------------------|

| Automotive                                            | cypress.com/automotive |

| Clocks & Buffers                                      | cypress.com/clocks     |

| Interface                                             | cypress.com/interface  |

| Internet of Things                                    | cypress.com/iot        |

| Memory                                                | cypress.com/memory     |

| Microcontrollers                                      | cypress.com/mcu        |

| PSoC                                                  | cypress.com/psoc       |

| Power Management ICs                                  | cypress.com/pmic       |

| Touch Sensing                                         | cypress.com/touch      |

| USB Controllers                                       | cypress.com/usb        |

| Wireless Connectivity                                 | cypress.com/wireless   |

PSoC<sup>®</sup> Solutions PSoC 1 | PSoC 3 | PSoC 4 | PSoC 5LP | PSoC 6 MCU

Cypress Developer Community Community | Projects | Videos | Blogs | Training | Components

Technical Support cypress.com/support

Arm and Cortex are registered trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere

© Cypress Semiconductor Corporation, 2014-2019. This document is the property of Cypress Semiconductor Corporation and its subsidiaries, including Spansion LLC ("Cypress"). This document, including any software or firmware included or referenced in this document ("Software"), is owned by Cypress under the intellectual property laws and treaties of the United States and other countries worldwide. Cypress reserves all rights under such laws and treaties and does not, except as specifically stated in this paragraph, grant any license under its patents, copyrights, trademarks, or other intellectual property rights. If the Software is not accompanied by a license agreement and you do not otherwise have a written agreement with Cypress governing the use of the Software provided in source code form, to modify and reproduce the Software solely for use with Cypress hardware products, only internally within your organization, and (b) to distribute the Software in binary code form externally to end users (either directly or indirectly through resellers and distributors), solely for use on Cypress hardware product units, and (2) under those claims of Cypress's patents that are infringed by the Software (as provided by Cypress, unmodified) to make, use, distribute, and import the Software solely for use with Cypress hardware product. Any other use, reproduction, modification, translation, or compilation of the Software is prohibited.

TO THE EXTENT PERMITTED BY APPLICABLE LAW, CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS DOCUMENT OR ANY SOFTWARE OR ACCOMPANYING HARDWARE, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. No computing device can be absolutely secure. Therefore, despite security measures implemented in Cypress hardware or software products, Cypress does not assume any liability arising out of any security breach, such as unauthorized access to or use of a Cypress product. In addition, the products described in these materials may contain design defects or errors known as errata which may cause the product to deviate from published specifications. To the extent permitted by applicable law, Cypress reserves the right to make changes to this document without further notice. Cypress does not assume any liability arising out of the application or use of any product or circuit described in this document. Any information provided only for reference purposes. It is the responsibility of the user of this document to properly design, program, and test the functionality and safety of any application made of this information and any resulting product. Cypress products are not designed, intended, or authorized for use as critical components in systems designed or intended for the operation of weapons, weapons systems, nuclear installations, life-support devices or system, other medical devices or system (including resuscitation equipment and surgical implants), pollution control or hazardous substances management, or other uses where the failure of the device or system (ould cause personal injury, death, or properly damage ("Unintended Uses"). A critical component is any component of a device or system whose failure to perform can be reasonably expected to cause the failure of the device or system, or to affect its safety or effectiveness. Cypress is not liable, in whole or in part, and you shall and hereby do release Cypress from any claim, damag

Cypress, the Cypress logo, Spansion, the Spansion logo, and combinations thereof, WICED, PSoC, CapSense, EZ-USB, F-RAM, and Traveo are trademarks or registered trademarks of Cypress in the United States and other countries. For a more complete list of Cypress trademarks, visit cypress.com. Other names and brands may be claimed as property of their respective owners.