# **☆TDK** Multilayer Ceramic Chip Capacitors

Page 1 of 2

Creation Date: July 10, 2013

### C5750X7R1H475K280KM

**Applications** Commercial Grade Feature Open Open Mode C5750 [EIA CC2220] Series

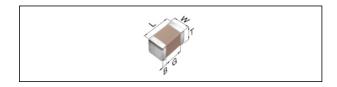

| Size                |                  |

|---------------------|------------------|

| Length(L)           | 5.70mm +/-0.40mm |

| Width(W)            | 5.00mm +/-0.40mm |

| Thickness(T)        | 2.80mm +/-0.30mm |

| Terminal Width(B)   | 0.20mm Min.      |

| Terminal Spacing(G) |                  |

| Electrical Characteristics |              |

|----------------------------|--------------|

| Capacitance                | 4.7uF +/-10% |

| Rated Voltage              | 50Vdc        |

| Temperature Characteristic | X7R(+/-15%)  |

| Dissipation Factor         | 3% Max.      |

| Insulation Resistance      | 106MΩ Min.   |

| Other            |                                      |

|------------------|--------------------------------------|

| Soldering Method | Reflow                               |

| AEC Q200         | No                                   |

| Packing          | Blister (Plastic)Taping [180mm Reel] |

| Package Quantity | 500 Pcs Min.                         |

<sup>•</sup>This PDF document was created based on the data listed on the TDK Corporation website.

<sup>•</sup>All specifications are subject to change without notice.

Creation Date: July 10, 2013

### C5750X7R1H475K280KM

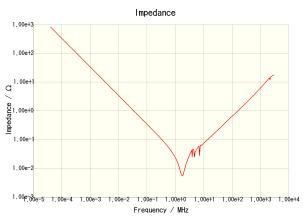

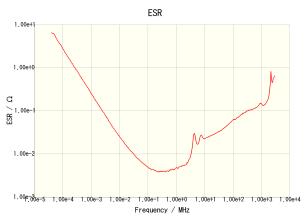

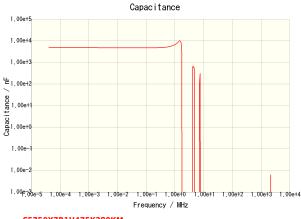

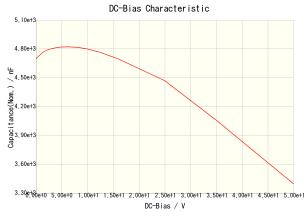

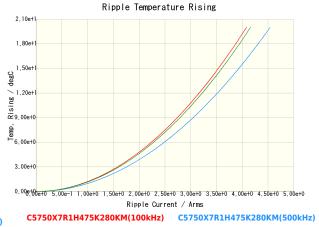

## **Characteristic Graphs**

C5750X7R1H475K280KM

C5750X7R1H475K280KM

C5750X7R1H475K280KM

C5750X7R1H475K280KM

C5750X7R1H475K280KM(DC Bias = 0V)750X7R1H475K280KM(DC Bias = 25V)

C5750X7R1H475K280KM(1MHz)

<sup>•</sup>This PDF document was created based on the data listed on the TDK Corporation website.

<sup>•</sup>All specifications are subject to change without notice.